# PCM1715U

# Dual Voltage Output CMOS Delta-Sigma DIGITAL-TO-ANALOG CONVERTER With On-Chip Digital Filter

# **FEATURES**

- DUAL MULTI-LEVEL NOISE SHAPING DAC WITH ON-CHIP DIGITAL FILTER

- HIGH PERFORMANCE: THD+N: 0.0025% (-92dB) typ Dynamic Range: 98dB typ S/N RATIO: 110dB typ

- ANALOG VOLTAGE OUTPUT: V<sub>o</sub> = 3.2Vp-p

- ON-CHIP ANALOG LOW PASS FILTER

- JITTER TOUGH AND LOW RADIO FREQUENCY INTERFERENCE ENERGY ARCHITECTURE

- SYSTEM CLOCK 256fs or 384fs

- ON-CHIP 8X OVERSAMPLING DIGITAL FILTER WITH: Lch/Rch Individual Attentuator Control Digital De-Emphasis (44.1kHz) Analog Output Mode Select

- SINGLE +5V POWER SUPPLY OPERATION

- SMALL 28-PIN SOIC PACKAGE

# DESCRIPTION

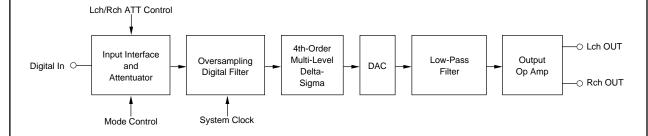

The PCM1715 is a low cost, dual voltage output CMOS digital-to-analog converter. Incorporated into the PCM1715 is a unique multi-level 4th-order delta-sigma architecture that eliminates influence from input clock jitter and RF interferance resulting in truly superior performance.

The PCM1715 has individual channel attenuator and analog output mode select function which is suitable for CD-ROM application.

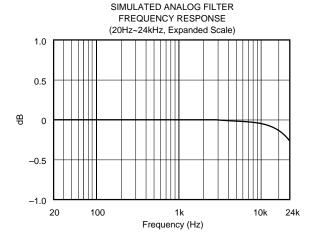

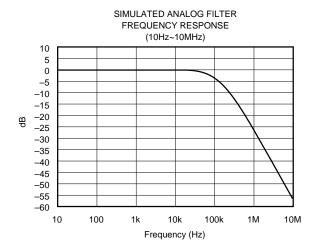

The on-chip digital filter of the PCM1715 has -62dB stop band attenuation and  $\pm 0.008dB$  ripple in the pass band.

The PCM1715 can be used in a wide variety of consumer audio applications. Its low cost, small size, and single +5V operation make it ideal for portable, automotive, CD players, CD-I, CD-ROM, VIDEO-CD, tuners, music instruments, and other digital audio applications.

International Airport Industrial Park

Mailing Address: PO Box 11400

Tel: (602) 746-1111

Twx: 910-952-1111

Cable: BBRCORP

Tel: (602) 746-1111

Twx: 910-952-1111

Mailing Address: PO Box 11400

Telex: 066-6491

FAX: (602) 889-1510

Immediate Product Info: (800) 548-6132

# **SPECIFICATIONS**

# **ELECTRICAL**

All specifications at +25°C, + $V_{CC}$  = + $V_{DD}$  = +5V, fs = 44.1kHz, SYSCLK = 384fs/256fs, and 16-bit data, unless otherwise noted.

|                                                                                                                                                |                                                                                        |              | PCM1715U                                  |                           |                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------|-------------------------------------------|---------------------------|--------------------------------------------------------------|

| PARAMETER                                                                                                                                      | CONDITIONS                                                                             | MIN          | TYP                                       | MAX                       | UNITS                                                        |

| RESOLUTION                                                                                                                                     |                                                                                        |              | 16                                        |                           | Bits                                                         |

| DIGITAL INPUT Logic Family Input Logic Level (except XTi)                                                                                      |                                                                                        |              |                                           |                           |                                                              |

| V <sub>IH</sub> V <sub>IL</sub> Input Logic Current (except XTi)                                                                               |                                                                                        | 2.0          |                                           | 0.8<br>-200               | VDC<br>VDC<br>μA                                             |

| Input Logic Level (XTi)  V <sub>IH</sub> V <sub>IL</sub> In the sign Courset (XTi)                                                             |                                                                                        | 3.2          |                                           | 1.4                       | VDC<br>VDC                                                   |

| Input Logic Current (XTi) Output Logic Level (CLKO): V <sub>OH</sub> V <sub>OL</sub>                                                           |                                                                                        | 4.5          |                                           | ±50<br>0.5                | μA<br>VDC<br>VDC                                             |

| Output Logic Current (CLRO) Data Format Sampling Frequency System Clock Frequency                                                              | 384fs                                                                                  | ±10<br>MSB F | <br>irst, Two's Com<br>  44.1<br>  16.934 | <br>plement<br>           | mA<br>kHz<br>MHz                                             |

| System Clock Frequency                                                                                                                         | 256fs                                                                                  |              | 11.2894                                   |                           | MHz                                                          |

| DC ACCURACY Gain Error Gain Mis-Match Channel-To-Channel Bipolar Zero Error Gain Drift Bipolar Gain Drift                                      | V <sub>o</sub> = 1/2V <sub>cc</sub> at Bipolar Zero                                    |              | ±1.0<br>±1.0<br>±20.0<br>±50<br>±20       | ±5.0<br>±5.0              | % of FSR<br>% of FSR<br>mV<br>ppm of FSR/°C<br>ppm of FSR/°C |

| DYNAMIC PERFORMANCE THD+N at F/S (0dB) <sup>(1)</sup> THD+N at -60dB <sup>(1)</sup> Dynamic Range S/N Ratio Channel Separation                 | $f_{ N} = 991Hz$ $f_{ N} = 991Hz$ $EIAJ A-weighted$ $EIAJ A-weighted$ $f_{ N} = 991Hz$ | 104<br>90    | -92<br>-36<br>98<br>110<br>94             | -88<br>-32                | dB<br>dB<br>dB<br>dB<br>dB                                   |

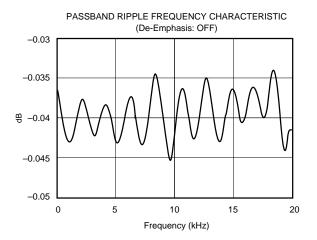

| DIGITAL FILTER PERFORMANCE Pass Band Ripple Stop Band Attenuation Pass Band Stop Band                                                          |                                                                                        | -62          | 0.4535<br>0.5465                          | ±0.008                    | dB<br>dB<br>fs<br>fs                                         |

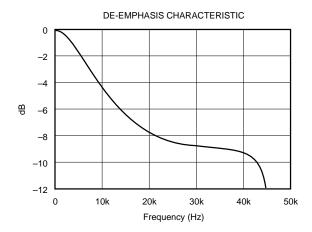

| De-emphasis Error                                                                                                                              | (fs = 44.1kHz)                                                                         |              |                                           | +0.03                     | dB                                                           |

| ANALOG OUTPUT Voltage Range Load Impedance Center Voltage                                                                                      | fs (0dB) OUT                                                                           | 5            | 3.2<br>+1/2V <sub>cc</sub>                |                           | Vp-p<br>kΩ<br>V                                              |

| POWER SUPPLY REQUIREMENTS  Voltage Range: +V <sub>cc</sub> +V <sub>DD</sub> Supply Current +I <sub>cc</sub> +I <sub>DD</sub> Power Dissipation | $+V_{CC} = +V_{DD} = +5.0V$<br>$+V_{CC} = +V_{DD} = +5.0V$                             | +4.5<br>+4.5 | +5.0<br>+5.0<br>45<br>225                 | +5.5<br>+5.5<br>70<br>350 | VDC<br>VDC<br>mA<br>mW                                       |

| TEMPERATURE RANGE Operation Storage                                                                                                            |                                                                                        | -25<br>-55   |                                           | +85<br>+100               | °C<br>°C                                                     |

NOTE: (1) 30kHz LPF, 400Hz HPF, Average Mode.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

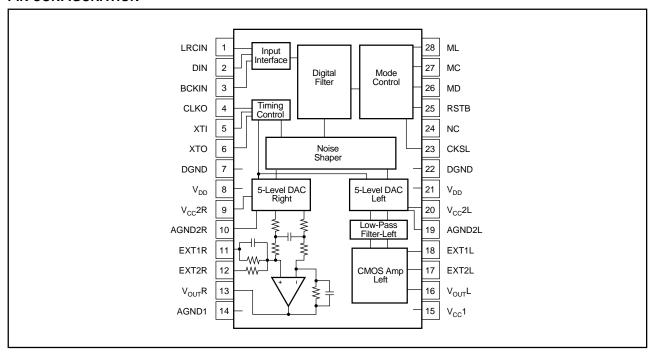

## **PIN CONFIGURATION**

# **PIN ASSIGNMENTS**

| PIN | NAME               | FUNCTION                                |

|-----|--------------------|-----------------------------------------|

| 1   | LRCIN              | Sample Rate Clock Input (fs)            |

| 2   | DIN                | Data Input                              |

| 3   | BCKIN              | Bit Clock Input                         |

| 4   | CLKO               | Buffered Output of Oscillator           |

| 5   | XTI                | Oscillator Input (External Clock Input) |

| 6   | XTO                | Oscillator Output                       |

| 7   | DGND               | Digital Ground                          |

| 8   | V <sub>DD</sub>    | Digital Power Supply (+5V)              |

| 9   | V <sub>cc</sub> 2R | Analog (DAC) +V <sub>cc</sub> , Rch     |

| 10  | AGND2R             | Analog (DAC) Ground, Rch                |

| 11  | EXT1R              | Output Amp Common, Rch                  |

| 12  | EXT2R              | Output Amp Bias, Rch                    |

| 13  | V <sub>OUT</sub> R | Rch Analog Output                       |

| 14  | AĞND               | Analog Ground                           |

| PIN | NAME               | FUNCTION                               |

|-----|--------------------|----------------------------------------|

| 15  | V <sub>cc</sub> 1  | Analog Power Supply (+5V)              |

| 16  | V <sub>OUT</sub> L | Lch Analog Output                      |

| 17  | EXT2L              | Output Amp Bias, Lch                   |

| 18  | EXT1L              | Output Amp Common, Lch                 |

| 19  | AGND2L             | Analog (DAC) Ground, Lch               |

| 20  | V <sub>cc</sub> 2L | Analog (DAC) +V <sub>cc</sub> , Lch    |

| 21  | V <sub>DD</sub>    | Digital Power Supply, (+5V)            |

| 22  | DGÑD               | Digital Ground                         |

| 23  | CKSL               | System Clock Select (H:384fs, L:256fs) |

| 24  | NC                 | No Connection                          |

| 25  | RSTB               | Reset                                  |

| 26  | MD                 | Mode Control                           |

| 27  | MC                 | Mode Control, BCK                      |

| 28  | ML                 | Mode Control, WDCK                     |

NOTE: All input pins require pull up resistors.

# **ABSOLUTE MAXIMUM RATINGS**

| ±6.5VDC                      |

|------------------------------|

| ±0.1V                        |

| 0.3V ~ V <sub>DD</sub> +0.3V |

| 400mW                        |

| 25°C to +85°C                |

| 55°C to +125°C               |

| +260°C                       |

|                              |

# PACKAGE INFORMATION(1)

| MODEL    | PACKAGE     | PACKAGE DRAWING<br>NUMBER |

|----------|-------------|---------------------------|

| PCM1715U | 28-Pin SOIC | 217-4J                    |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.

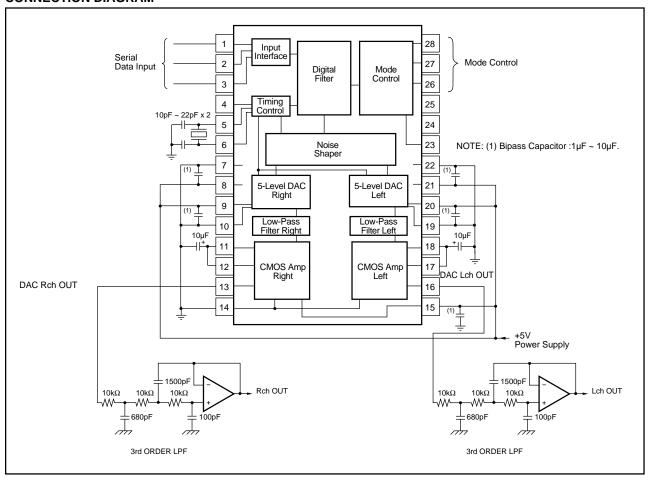

## **CONNECTION DIAGRAM**

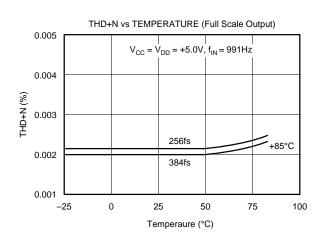

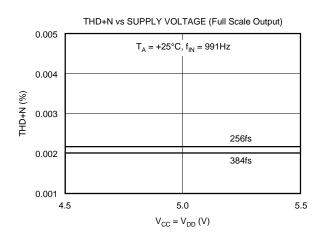

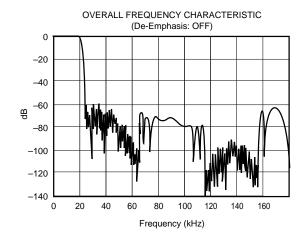

# **TYPICAL PERFORMANCE CURVES**

All specifications at  $+25^{\circ}\text{C}$ ,  $+\text{V}_{\text{CC}} = +\text{V}_{\text{DD}} = +5\text{V}$ , fs = 44.1kHz, SYSCLK = 384fs/256fs, and 16-bit data, unless otherwise noted.

# TYPICAL PERFORMANCE CURVES (CONT)

All specifications at +25°C, + $V_{CC}$  = + $V_{DD}$  = +5V, fs = 44.1kHz, SYSCLK = 384fs/256fs, and 16-bit data, unless otherwise noted.

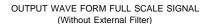

NOTES: (1) Measured at V<sub>OUT</sub> Pin (Pin 13 or 16). (2) The PCM1715 has internal analog low pass filter to reduce high frequency noise-shaped spectrum. Application of the PCM1715 requires external post analog low pass filter which has 2nd-Order or 3rd-Order attenuation performance to get low noise analog output.

# THEORY OF DELTA-SIGMA OPERATION

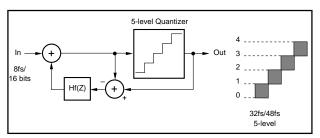

The delta-sigma section of the PCM1715 is based on a 5-level amplitude quantizer and a 4th-order filter. This converts the oversampled 16-bit input data to 5-level delta-sigma form. A block diagram of the 5-level modulator is shown in Figure 1.

FIGURE 1. Block Diagram of 5-Level Delta-Sigma Quantizer

This 5-level delta-sigma modulator has the advantage of stability of delta-sigma loop and jitter sensitivity over the typical 1-bit (2-level) delta-sigma modulator.

The combined oversampling rate of the delta-sigma modulator and the internal 8x oversampling digital filter is 48fs at a system clock speed of 384fs, 32fs at a system clock speed of 256fs.

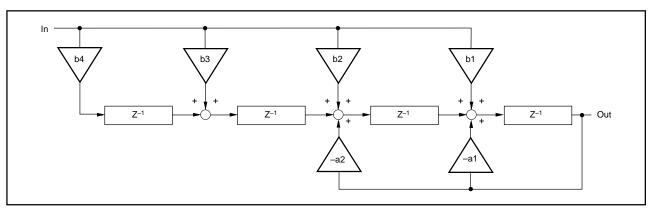

A block diagram of the 4th-order filter section Hf(z) in the delta-sigma modulator is shown in Figure 2.

In general, high order 1-bit delta-sigma modulators have disadvantages due to loop instability. The 5 level delta-sigma modulator of the PCM1715 uses phase compensation techniques to obtain stable operation. In Figure 2, the coefficients, b1 to b4, give the basic form of the filter and -a1 and -a2 are used for phase compensation of the feedback loop.

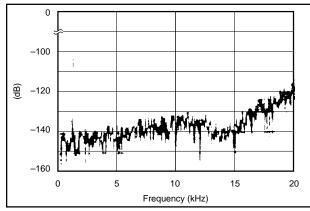

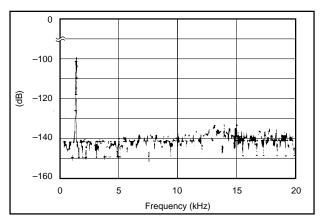

The theoretical quantization noise performance of the 5-level delta-sigma modulator is shown in Figures 3 and 4. In the audio band, the quantization noise floor level of the PCM1715 is less than -130dB (384fs).

# **MODE OF OPERATION**

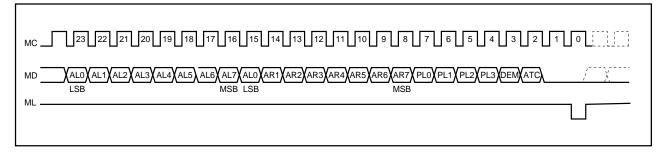

Serial inputs to MD, MC, and ML (Pins 26, 27 and 28) control the following functions:

(1) Digital Attenuator [AL0 ~ AL7, AR0 ~ AR7]

Attenuation data is constructed by 8-bit/Lch, 8-bit/Rch

(total 16-bit), can be controlled as 255 step attenuation

by individual channel. AL0 and AR0 are LSB, and AL7

and AR7 are MSB. Attenuation Level ATT is given by:

$ATT = 20LOG_{10} (ATT DATA/255) [dB]$

FIGURE 2. Block Diagram of the Hf(z).

FIGURE 3. Quantization Noise Spectrum (256fs).

FIGURE 4. Quantization Noise Spectrum (384fs).

At ATT DATA: 0XFF, output is 0dB. At ATT DATA 0X00, output is  $-\infty$ .

When "Muting" is chosen by output mode control, output goes to  $-\infty$  from the present ATT level.

Moving speed from 0dB to -∞ is 1024/f.

Initialized (RESET) ATT level is 0dB.

# (2) Versatile Output Mode [PL0 ~ PL3]

By using PL0  $\sim$  PL3 data, up to 16 different output modes (Lch/Rch/L+R/MUTE) can be selected to the output of Lch and Rch, as shown in Table I.

Initialized mode is STEREO mode.

## (3) De-emphasis Control (DEM)

De-emphasis function is controlled by DEM flag (H: ON, L: OFF)

De-emphasis is enabled only at 44.1kHzfs. At other fs frequencies, de-emphasis error is not guaranteed. Initialized mode is De-emphasis OFF.

# (4) Attenuator Control (ATC)

If common attenuator control of Lch and Rch is needed, use the ATC flag (ATC = "H"). Common attenuation can be controlled by Lch (AL0 ~ AL7) data. Initialized mode is individual.

## (5) Infinity-Zero Detection

The PCM1715 has an infinity-zero detect function which monitors the input data and bit clock. When the input

| PL0 | PL1 | PL2 | PL3 | Lch<br>OUTPUT | Rch<br>OUTPUT | NOTE    |

|-----|-----|-----|-----|---------------|---------------|---------|

| 0   | 0   | 0   | 0   | MUTE          | MUTE          | MUTE    |

| 0   | 0   | 0   | 1   | MUTE          | R             |         |

| 0   | 0   | 1   | 0   | MUTE          | L             |         |

| 0   | 0   | 1   | 1   | MUTE          | (L + R)/2     |         |

| 0   | 1   | 0   | 0   | R             | MUTE          |         |

| 0   | 1   | 0   | 1   | R             | R             |         |

| 0   | 1   | 1   | 0   | R             | L             | REVERSE |

| 0   | 1   | 1   | 1   | R             | (L + R)/2     |         |

| 1   | 0   | 0   | 0   | L             | MUTE          |         |

| 1   | 0   | 0   | 1   | L             | R             | STEREO  |

| 1   | 0   | 1   | 0   | L             | L             |         |

| 1   | 0   | 1   | 1   | L             | (L + R)/2     |         |

| 1   | 1   | 0   | 0   | (L + R)/2     | MUTE          |         |

| 1   | 1   | 0   | 1   | (L + R)/2     | R             |         |

| 1   | 1   | 1   | 0   | (L + R)/2     | L             |         |

| 1   | 1   | 1   | 1   | (L + R)/2     | (L + R)/2     | MONO    |

TABLE I. PCM1715 Output Mode Control.

data is continuously "zero" for 8192 cycles of the bit clock, the infinity zero detect occurs and the DAC outputs are set to bipolar zero  $(1/2V_{CC})$ .

### (6) Reset

Normally, internal initialize (reset) is done automatically at power on ( $V_{DD} > 3.5V$ ). The RSTB-pin (Pin 25) accepts external forced reset by RSTB=L. During RSTB=L, the output of the DAC is invalid, set to  $1/2V_{CC}$  after internal initialize (1024XTI clock count after RSTB=H).

## MODE CONTROL FORMAT

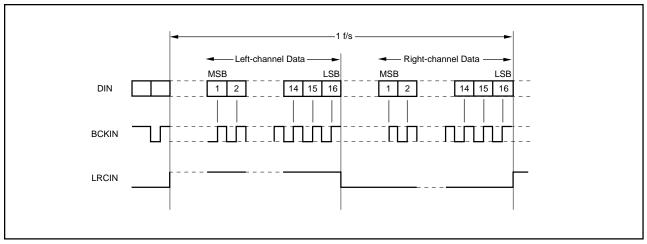

FIGURE 5. Data Input Timing, 16-Bit.

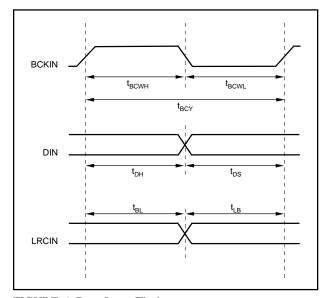

FIGURE 6. Data Input Timing.

| BCK Pulsewidth (H Level)    | t <sub>BCWH</sub> | 70ns (min)  |

|-----------------------------|-------------------|-------------|

| BCK Pulsewidth (L Level     | t <sub>BCWL</sub> | 70ns (min)  |

| BCK Pulse Cycle Time        | t <sub>BCY</sub>  | 140ns (min) |

| DIN Setup Time              | t <sub>DS</sub>   | 30ns (min)  |

| DIN Hold Time               | t <sub>DH</sub>   | 30ns (min)  |

| BCK Rising Edge → LRCI Edge | t <sub>BL</sub>   | 30ns (min)  |

| LRCI Edge → BCK Rising Edge | t <sub>LB</sub>   | 30ns (min)  |

TABLE II. Data Input Timing Specifications.

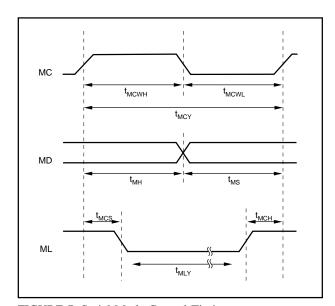

FIGURE 7. Serial Mode Control Timing.

|                         |                   | _                     |

|-------------------------|-------------------|-----------------------|

| MC Pulsewidth (H Level) | t <sub>MCWH</sub> | 50ns (min)            |

| MC Pulsewidth (L Level) | t <sub>MCWI</sub> | 50ns (min)            |

| MC Pulse Cycle Time     | t <sub>MCY</sub>  | 100ns (min)           |

| MD Setup Time           | t <sub>MS</sub>   | 30ns (min)            |

| MD Hold Time            | t <sub>MH</sub>   | 30ns (min)            |

| ML Setup Time           | t <sub>MCS</sub>  | 30ns (min)            |

| ML Hold Time            | t <sub>MCH</sub>  | 30ns (min)            |

| ML Low-Level Time       | t <sub>MLY</sub>  | 1/sysclk + 20ns (min) |

|                         |                   |                       |

TABLE III. Serial Mode Control Timing Specifications.

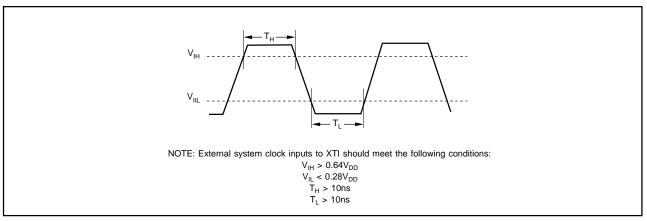

FIGURE 8. Operation Instruction For System Clock.

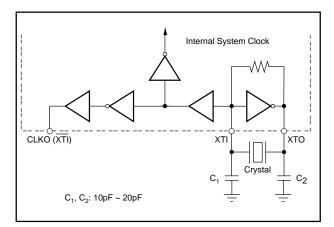

FIGURE 9. Oscillator Circuit Connection Diagram. Optional external crystal oscillator.

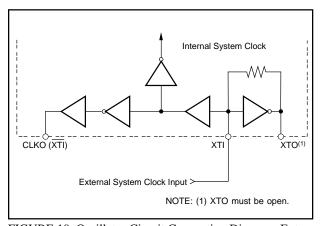

FIGURE 10. Oscillator Circuit Connection Diagram. External system clock.

# **EVALUATION BOARD**

Burr-Brown's DEM-PCM1710 evaluation board for the PCM1710 is capable of evaluation of the PCM1715 and PCM1710. Digital input signals for the evaluation board are LRCK, BCK, DATA, and system clock (256fs or 384fs). Power supply requirement is only +5V.

The DEM-PCM1710 has a pattern layout for an optional crystal oscillator. However, the crystal is not installed.