# INTEGRATED CIRCUITS

# DATA SHEET

**PCF8833** STN RGB - 132 × 132 × 3 driver

Objective specification

2003 Feb 14

**PCF8833**

| CONTEN            | TS                                                                                                    | 10                           | LIMITING VALUES                                                                  |

|-------------------|-------------------------------------------------------------------------------------------------------|------------------------------|----------------------------------------------------------------------------------|

| 1<br>2<br>3       | FEATURES GENERAL DESCRIPTION ORDERING INFORMATION                                                     | 11<br>12<br>13<br>14         | HANDLING DC CHARACTERISTICS AC CHARACTERISTICS APPLICATION INFORMATION           |

| 4<br>5<br>6       | BLOCK DIAGRAM PINNING INSTRUCTIONS                                                                    | 14.1<br>15                   | Supply and capacitor connection configuration MODULE MAKER PROGRAMMING           |

| 6.1<br>6.2<br>7   | Exit commands Function set FUNCTIONAL DESCRIPTION                                                     | 15.1<br>15.2<br>15.3<br>15.4 | V <sub>LCD</sub> calibration<br>Factory defaults<br>Seal bit<br>OTP architecture |

| 7.1<br>7.2<br>7.3 | MPU interfaces Display data RAM and access arbiter Command decoder                                    | 15.4<br>15.5<br>15.6         | Interface commands Suggestion on how to calibrate V <sub>LCD2</sub> using MMVOP  |

| 7.4<br>7.5<br>7.6 | Grey scale controller Timing generator Oscillator                                                     | 15.7<br>15.8<br>15.9         | Example of filling the shift register Programming flow Programming specification |

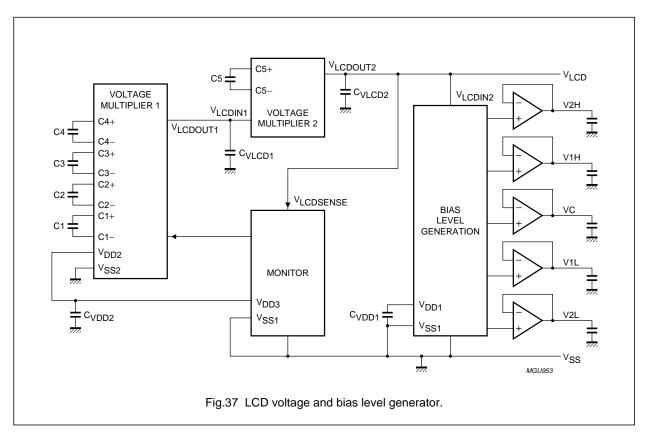

| 7.7<br>7.8<br>7.9 | Reset LCD voltage generator and bias level generator Column drivers, data processing and data latches | 16<br>17<br>18               | INTERNAL PROTECTION CIRCUITS BONDING PAD INFORMATION TRAY INFORMATION            |

| 7.10              | Row drivers                                                                                           | 19                           | DATA SHEET STATUS                                                                |

| 8.1               | PARALLEL INTERFACE 8080-series 8-bit parallel interface                                               | 20<br>21                     | DEFINITIONS DISCLAIMERS                                                          |

| 9<br>9.1<br>9.2   | SERIAL INTERFACE Write mode Read mode                                                                 |                              |                                                                                  |

# STN RGB - $132 \times 132 \times 3$ driver

PCF8833

### 1 FEATURES

- · Single chip LCD controller and driver

- 132 rows and 396 column outputs (132 × RGB)

- Low cross talk by Frame Rate Control (FRC)

- 4 kbyte colours (RGB) = 4 : 4 : 4 mode

- 256 colours (RGB) = 3:3:2 mode using the 209 kbit RAM and a Look-Up Table (LUT)

- 65 kbyte colours (RGB) = 5:6:5 mode using the 209 kbit RAM with dithering

- 8 colours Power-save mode

- Display data RAM 132 × 132 (RGB) (4 kbyte colour)

- · Interfaces:

- 3-line serial interface

- 8-bit 8080 Intel CPU interface.

- · Display features:

- Area scrolling

- 32-line partial Display mode

- Software programmable colour depth mode

- N-line inversion for low cross talk.

- On-chip:

- Oscillator for display system, requires no external components (external clock also possible)

- Generation of V<sub>LCD</sub>

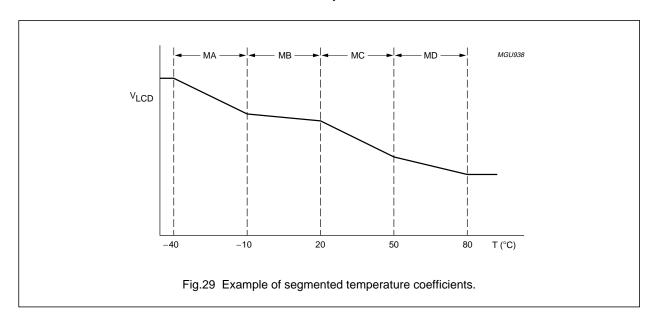

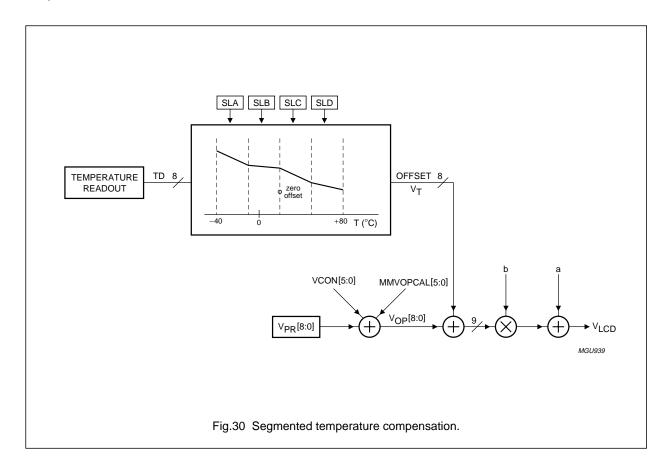

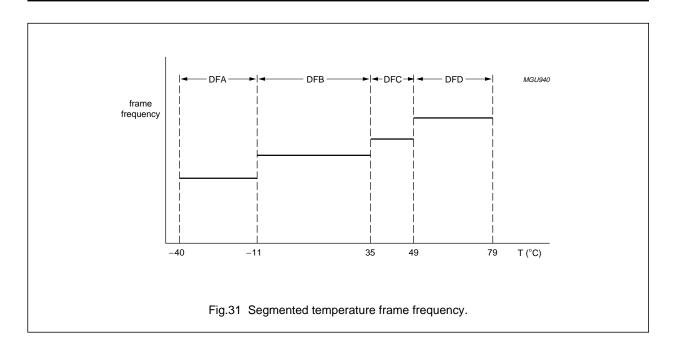

- Segmented temperature compensation of V<sub>LCD</sub> and frame frequency.

- Logic supply voltage range V<sub>DD1</sub> to V<sub>SS1</sub>:

- 1.5 to 3.3 V.

- Analog supply voltage range for V<sub>LCD</sub> generation V<sub>DD2</sub> to V<sub>SS2</sub>:

- 2.4 to 4.5 V.

- Analog supply voltage range for reference voltage generation V<sub>DD3</sub> to V<sub>SS1</sub>:

- 2.4 to 3.5 V.

- Display supply voltage range V<sub>LCD</sub> to V<sub>SS1</sub>:

- 3.8 to 20 V.

- Low power consumption; suitable for battery operated systems

- · CMOS compatible inputs

- · Manufactured in silicon gate CMOS process

- Optimized layout for COF, Chip On Glass (COG) and Transformer Coupled Plasma (TCP) assembly.

### 2 GENERAL DESCRIPTION

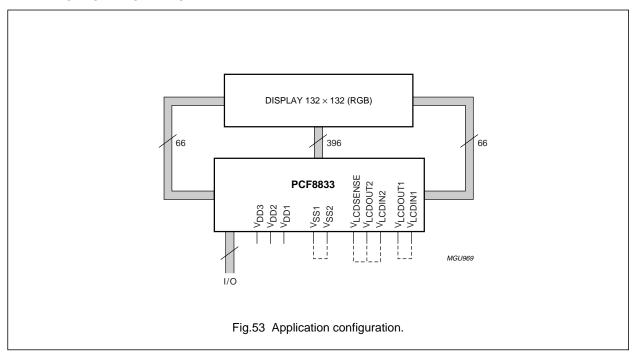

The PCF8833 is a single chip low power CMOS LCD controller driver, designed to drive colour Super-Twisted Nematic (STN) displays of 132 rows and 132 RGB columns. All necessary functions for the display are provided in a single chip, including display RAM which has a capacity of 209 kbit (132  $\times$  12-bit  $\times$  132). The PCF8833 uses the Multiple Row Addressing (MRA) driving technique in order to achieve the best optical performance at the lowest power consumption. The PCF8833 offers 2 types of microcontroller interfaces namely the 8080 system interface and the 3-line serial interface.

### 3 ORDERING INFORMATION

| TYPE NUMBER    | PACKAGE |                         |         |  |  |  |  |

|----------------|---------|-------------------------|---------|--|--|--|--|

| TIPE NOWIBER   | NAME    | DESCRIPTION             | VERSION |  |  |  |  |

| PCF8833U/2DA/1 | _       | chip with bumps in tray | _       |  |  |  |  |

PCF8833

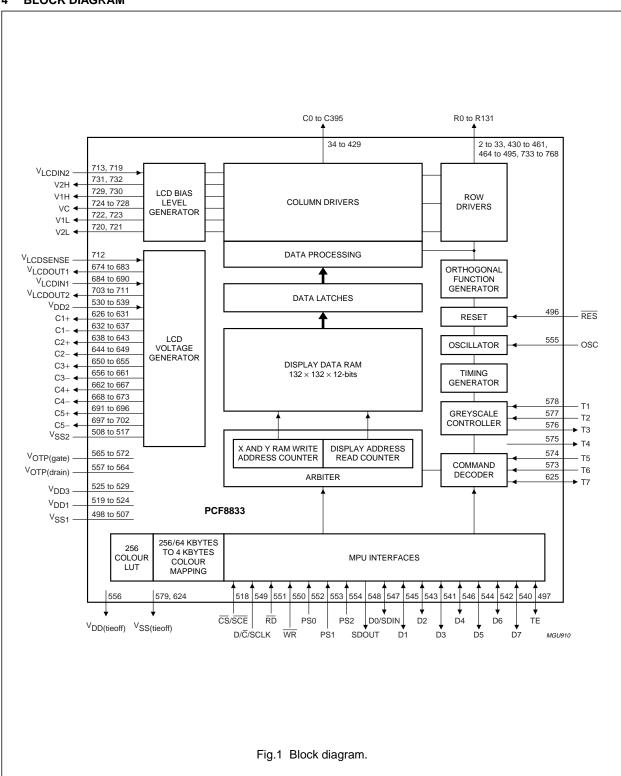

### 4 BLOCK DIAGRAM

PCF8833

# 5 PINNING

| SYMBOL           | PAD                      | TYPE     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|------------------|--------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| R95 to R64       | 2 to 33                  | 0        | LCD row driver outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| C0 to C395       | 34 to 429                | 0        | LCD column driver outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| R0 to R31        | 430 to 461               | 0        | LCD row driver outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| R63 to R32       | 464 to 495               | 0        | LCD row driver outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| RES              | 496                      | I        | external reset; this signal will reset the device and must be applied to properly initialize the chip (active LOW)                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| TE               | 497                      | O/I      | tearing line (in Normal mode it is always an output)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| V <sub>SS1</sub> | 498 to 507               | PS       | system ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| V <sub>SS2</sub> | 508 to 517               | PS       | system ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| CS/SCE           | 518                      | I        | chip select parallel interface or serial chip enable (active LOW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| V <sub>DD1</sub> | 519 to 524               | PS       | logic supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| V <sub>DD3</sub> | 525 to 529<br>530 to 539 | PS<br>PS | $V_{DD2}$ and $V_{DD3}$ are the supply voltage pins for the internal voltage generator including the temperature compensation circuits; $V_{DD2}$ and $V_{DD3}$ can be connected together but in this case care must be taken to respect the supply voltage range (see Chapter 13); $V_{DD1}$ is used as the supply for the rest of the chip. $V_{DD1}$ can be connected together with $V_{DD2}$ and $V_{DD3}$ but in this case care must also be taken to respect the supply voltage range; see Chapter 13. $V_{DD2}$ and $V_{DD3}$ must not be applied before $V_{DD1}$ . |  |  |  |  |

|                  |                          |          | If the internal voltage generator is not used, pins $V_{DD2}$ and $V_{DD3}$ must be connected to $V_{DD1}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| D7               | 540                      | I/O      | 8-bit parallel data; in Serial mode tie to V <sub>SS1</sub> or V <sub>DD1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| D3               | 541                      | I/O      | 8-bit parallel data; in Serial mode tie to V <sub>SS1</sub> or V <sub>DD1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| D6               | 542                      | I/O      | 8-bit parallel data; in Serial mode tie to V <sub>SS1</sub> or V <sub>DD1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| D2               | 543                      | I/O      | 8-bit parallel data; in Serial mode tie to V <sub>SS1</sub> or V <sub>DD1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| D5               | 544                      | I/O      | 8-bit parallel data; in Serial mode tie to V <sub>SS1</sub> or V <sub>DD1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| D1               | 545                      | I/O      | 8-bit parallel data; in Serial mode tie to V <sub>SS1</sub> or V <sub>DD1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| D4               | 546                      | I/O      | 8-bit parallel data; in Serial mode tie to V <sub>SS1</sub> or V <sub>DD1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| D0/SDIN          | 547                      | I/O      | 8-bit parallel data or serial data input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| SDOUT            | 548                      | 0        | serial data output; in Parallel mode tie to V <sub>DD1</sub> , V <sub>SS1</sub> or D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| D/C/SCLK         | 549                      | I        | data/command indicator parallel interface or serial clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| WR               | 550                      | I        | write clock parallel interface; in Serial mode tie to V <sub>DD1</sub> (active LOW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| RD               | 551                      | I        | read clock parallel interface; in Serial mode tie to V <sub>DD1</sub> (active LOW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| PS0              | 552                      | I        | set serial or parallel interface mode PS1 and PS2 must tied to either $V_{\text{SS1}}$ or $V_{\text{DD1}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| PS1              | 553                      | I        | set serial or parallel interface mode PS1 and PS2 must tied to either $V_{SS1}$ or $V_{DD1}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| PS2              | 554                      | I        | set serial or parallel interface mode PS1 and PS2 must tied to either $V_{\rm SS1}$ or $V_{\rm DD1}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

PCF8833

| SYMBOL                  | PAD        | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC                     | 555        | I    | oscillator input or external oscillator resistor connection; when the on-chip oscillator is used this input must be connected to $V_{DD1}$ ; an external clock signal, if used, is connected to this input and the internal oscillator must be switched off with a software command; if the oscillator and external clock are all inhibited by connecting pin OSC to $V_{SS1}$ , the display is not clocked and may be left in a DC state; to avoid this the chip should always be put into Power-down mode before stopping the clock. |

| V <sub>DD(tieoff)</sub> | 556        | 0    | can be used to tie inputs to V <sub>DD1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>OTP(drain)</sub> | 557 to 564 | PS   | supply voltage for OTP programming (write voltage), in Application mode must be tied to $V_{\rm SS1}$ or left open-circuit                                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>OTP(gate)</sub>  | 565 to 572 | PS   | supply voltage for OTP programming, in Application mode must be tied to $V_{\text{SS1}}$ or left open-circuit                                                                                                                                                                                                                                                                                                                                                                                                                          |

| T6                      | 573        | I    | test pin; not accessible to user; must be connected to V <sub>SS1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| T5                      | 574        | I    | test pin; not accessible to user; must be connected to V <sub>SS1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| T4                      | 575        | 0    | test pin; not accessible to user; must be left open-circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| T3                      | 576        | 0    | test pin; not accessible to user; must be left open-circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| T2                      | 577        | I/O  | test pin; not accessible to user; must be also connected to V <sub>SS1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| T1                      | 578        | I/O  | test pin; not accessible to user; must be also connected to V <sub>SS1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>SS(tieoff)</sub> | 579        | 0    | can be used to tie inputs to V <sub>SS1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>SS(tieoff)</sub> | 624        | 0    | can be used to tie inputs to V <sub>SS1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| T7                      | 625        | I/O  | test pin; not accessible to user; must be connected to V <sub>SS1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| C1+                     | 626 to 631 | I    | positive input pump capacitor voltage multiplier 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| C1-                     | 632 to 637 | I    | negative input pump capacitor voltage multiplier 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| C2+                     | 638 to 643 | I    | positive input pump capacitor voltage multiplier 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| C2-                     | 644 to 649 | I    | negative input pump capacitor voltage multiplier 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| C3+                     | 650 to 655 | I    | positive input pump capacitor voltage multiplier 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| C3-                     | 656 to 661 | I    | negative input pump capacitor voltage multiplier 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| C4+                     | 662 to 667 | I    | positive input pump capacitor voltage multiplier 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| C4-                     | 668 to 673 | I    | negative input pump capacitor voltage multiplier 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>LCDOUT1</sub>    | 674 to 683 | 0    | output voltage multiplier 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>LCDIN1</sub>     | 684 to 690 | PS   | LCD supply input voltage 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| C5+                     | 691 to 696 | I    | positive input pump capacitor voltage multiplier 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| C5-                     | 697 to 702 | I    | negative input pump capacitor voltage multiplier 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>LCDOUT2</sub>    | 703 to 711 | 0    | output voltage multiplier 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>LCDSENSE</sub>   | 712        | I    | voltage multiplier regulation input; must be connected to V <sub>LCDOUT2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>LCDIN2</sub>     | 713 to 719 | PS   | LCD supply input voltage 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V2L                     | 720, 721   | 0    | LCD bias level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V1L                     | 722, 723   | 0    | LCD bias level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VC                      | 724 to 728 | 0    | LCD bias level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V1H                     | 729, 730   | 0    | LCD bias level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# STN RGB - $132 \times 132 \times 3$ driver

PCF8833

| SYMBOL      | PAD                                | TYPE | DESCRIPTION            |

|-------------|------------------------------------|------|------------------------|

| V2H         | 731, 732                           | 0    | LCD bias level         |

| R96 to R131 | 733 to 768                         | 0    | LCD row driver outputs |

| Dummy       | 1, 462, 463,<br>580 to 623,<br>769 |      |                        |

### **6 INSTRUCTIONS**

The PCF8833 communicates with the host using an 8-bit parallel interface or a 3-line serial interface. Processing of instructions and data sent to the interface do not require the display clock. The display clock and interface clock are independent from each other. The display clock is derived from the built-in oscillator.

The PCF8833 has 2 types of accesses; those defining the operating mode of the device (instructions) and those filling the display RAM. Since writing to the RAM occurs more frequently, efficient data transfer is achieved by autoincrementing the RAM address pointers.

There are 3 types of instructions:

- 1. For defining display configuration

- 2. For setting X and Y addresses

- 3. Miscellaneous.

Commands in the range of 00H to AFH not defined in Table 1 and command DDH have the same effect as no operation (NOP).

All commands in range B0H to B9H and DEH to FFH are forbidden.

Table 1 Command table; note 1

2003 Feb 14

œ

| D/C | 7     | 6                 | 5                 | 4                 | 3                 | 2                 | 1                 | 0                 | DEFAULT | ОТР | DESCRIPTION                           | SECTION |

|-----|-------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------|-----|---------------------------------------|---------|

| 0   | 0     | 0                 | 0                 | 0                 | 0                 | 0                 | 0                 | 0                 | 00H     | -   | no operation (NOP)                    | 6.2.1   |

| 0   | 0     | 0                 | 0                 | 0                 | 0                 | 0                 | 0                 | 1                 | 01H     | _   | software reset (SWRESET)              | 6.2.3   |

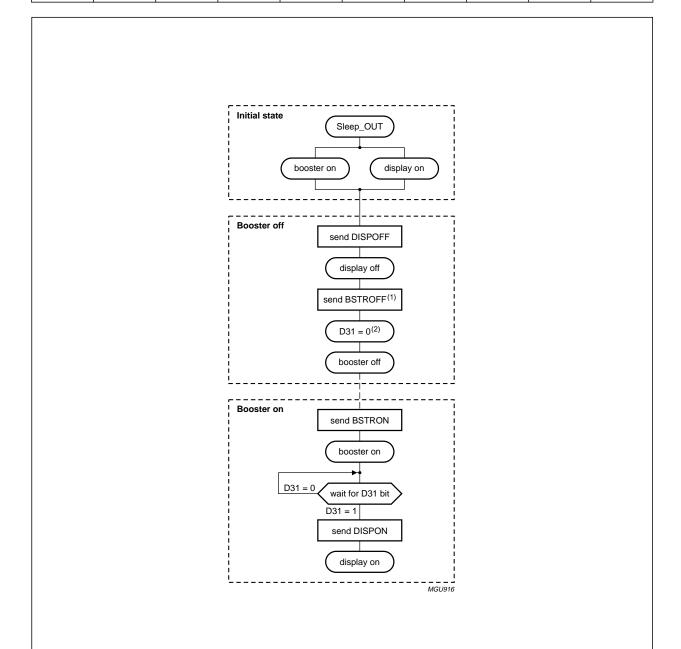

| 0   | 0     | 0                 | 0                 | 0                 | 0                 | 0                 | 1                 | 0                 | 02H     | -   | booster voltage off (BSTROFF)         | 6.2.4   |

| 0   | 0     | 0                 | 0                 | 0                 | 0                 | 0                 | 1                 | 1                 | 03H     | _   | booster voltage on (BSTRON)           | 6.2.5   |

| 0   | 0     | 0                 | 0                 | 0                 | 0                 | 1                 | 0                 | 0                 | 04H     | -   | read display identification (RDDIDIF) | 6.2.6   |

| 0   | 0     | 0                 | 0                 | 0                 | 1                 | 0                 | 0                 | 1                 | 09H     | -   | read display status (RDDST)           | 6.2.7   |

| 0   | 0     | 0                 | 0                 | 1                 | 0                 | 0                 | 0                 | 0                 | 10H     | -   | Sleep_IN                              | 6.2.8   |

| 0   | 0     | 0                 | 0                 | 1                 | 0                 | 0                 | 0                 | 1                 | 11H     | -   | Sleep_OUT                             | 6.2.9   |

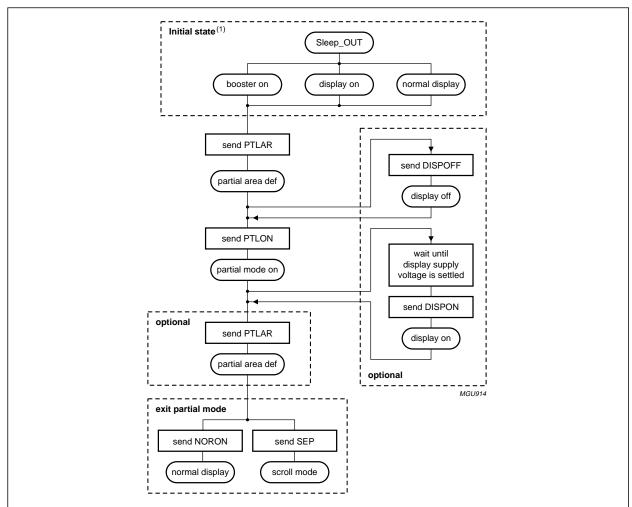

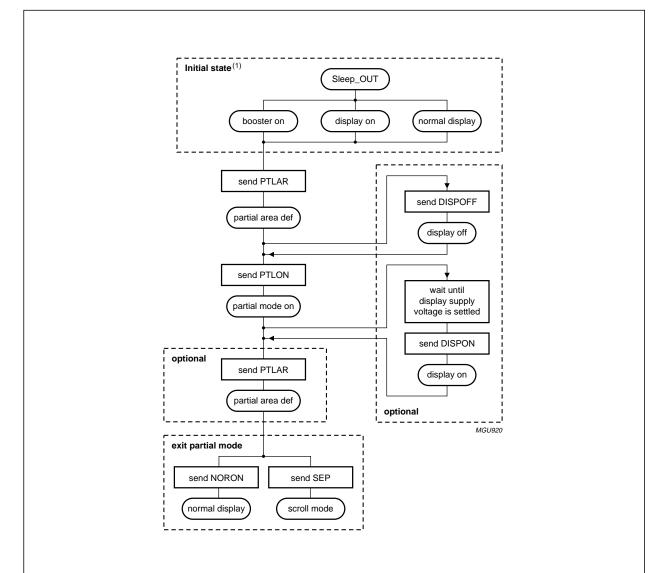

| 0   | 0     | 0                 | 0                 | 1                 | 0                 | 0                 | 1                 | 0                 | 12H     | -   | Partial mode on (PTLON)               | 6.2.10  |

| 0   | 0     | 0                 | 0                 | 1                 | 0                 | 0                 | 1                 | 1                 | 13H     | -   | normal Display mode on (NORON)        | 6.2.11  |

| 0   | 0     | 0                 | 1                 | 0                 | 0                 | 0                 | 0                 | 0                 | 20H     | _   | display inversion off (INVOFF)        | 6.2.12  |

| 0   | 0     | 0                 | 1                 | 0                 | 0                 | 0                 | 0                 | 1                 | 21H     | -   | display inversion on (INVON)          | 6.2.13  |

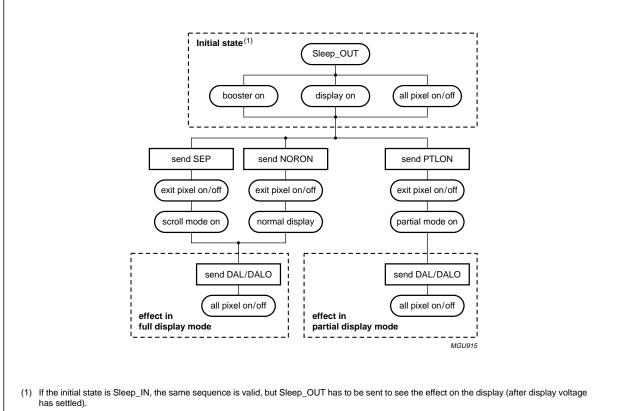

| 0   | 0     | 0                 | 1                 | 0                 | 0                 | 0                 | 1                 | 0                 | 22H     | _   | all pixel off (DALO)                  | 6.2.14  |

| 0   | 0     | 0                 | 1                 | 0                 | 0                 | 0                 | 1                 | 1                 | 23H     | -   | all pixel on (DAL)                    | 6.2.15  |

| 0   | 0     | 0                 | 1                 | 0                 | 0                 | 1                 | 0                 | 1                 | 25H     | _   | set contrast (SETCON)                 | 6.2.16  |

| 1   | Χ     | VCON <sub>6</sub> | VCON <sub>5</sub> | VCON <sub>4</sub> | VCON <sub>3</sub> | VCON <sub>2</sub> | VCON <sub>1</sub> | VCON <sub>0</sub> | 00H     | -   | set contrast                          | 6.2.16  |

| 0   | 0     | 0                 | 1                 | 0                 | 1                 | 0                 | 0                 | 0                 | 28H     | _   | display off (DISPOFF)                 | 6.2.17  |

| 0   | 0     | 0                 | 1                 | 0                 | 1                 | 0                 | 0                 | 1                 | 29H     | _   | display on (DISPON)                   | 6.2.18  |

| 0   | 0     | 0                 | 1                 | 0                 | 1                 | 0                 | 1                 | 0                 | 2AH     | _   | column address set (CASET)            | 6.2.19  |

| 1   | xs[7] | xs[6]             | xs[5]             | xs[4]             | xs[3]             | xs[2]             | xs[1]             | xs[0]             | 02H     | _   | X address start; $0 \le xs \le 83H$   | 6.2.19  |

| 1   | xe[7] | xe[6]             | xe[5]             | xe[4]             | xe[3]             | xe[2]             | xe[1]             | xe[0]             | 81H     | -   | X address end; xs ≤ xe ≤ 83H          | 6.2.19  |

| 0   | 0     | 0                 | 1                 | 0                 | 1                 | 0                 | 1                 | 1                 | 2BH     | -   | page address set (PASET)              | 6.2.20  |

| 1   | ys[7] | ys[6]             | ys[5]             | ys[4]             | ys[3]             | ys[2]             | ys[1]             | ys[0]             | 02H     | -   | Y address start; 0 ≤ ys ≤ 83H         | 6.2.20  |

| 1   | ye[7] | ye[6]             | ye[5]             | ye[4]             | ye[3]             | ye[2]             | ye[1]             | ye[0]             | 81H     | -   | Y address end; ys ≤ ye ≤ 83H          | 6.2.20  |

| 0   | 0     | 0                 | 1                 | 0                 | 1                 | 1                 | 0                 | 0                 | 2CH     | -   | memory write (RAMWR)                  | 6.2.21  |

| 1   | D7    | D6                | D5                | D4                | D3                | D2                | D1                | D0                | XXH     | -   | write data                            | 6.2.21  |

| 0   | 0     | 0                 | 1                 | 0                 | 1                 | 1                 | 0                 | 1                 | 2DH     | -   | colour set (RGBSET)                   | 6.2.22  |

| 1   | Х     | Х                 | Х                 | Х                 | R3                | R2                | R1                | R0                | 00H     | -   | red tone 000                          | 6.2.22  |

| 1   |       |                   |                   | 6 by              | tes for 6 r       | ed tones          |                   |                   |         | -   | 6 red tones                           | 6.2.22  |

PCF8833

| $D/\overline{C}$ | 7               | 6               | 5               | 4                | 3                | 2                | 1                | 0                | DEFAULT | ОТР   | DESCRIPTION                          | SECTION |

|------------------|-----------------|-----------------|-----------------|------------------|------------------|------------------|------------------|------------------|---------|-------|--------------------------------------|---------|

| 1                | Х               | Х               | Х               | Х                | R3               | R2               | R1               | R0               | 0FH     | -     | red tone 111                         | 6.2.22  |

| 1                | Х               | Х               | Х               | Х                | G3               | G2               | G1               | G0               | 00H     | -     | green tone 000                       | 6.2.22  |

| 1                |                 |                 |                 | 6 byte           | s for 6 gr       | een tones        | ;                |                  | •       | -     | 6 green tones                        | 6.2.22  |

| 1                | Х               | Х               | Х               | Х                | G3               | G2               | G1               | G0               | 0FH     | _     | green tone 111                       | 6.2.22  |

| 1                | Х               | Х               | Х               | Х                | В3               | B2               | B1               | B0               | 00H     | -     | blue tone 00                         | 6.2.22  |

| 1                |                 |                 |                 | 2 byt            | es for 2 b       | lue tones        |                  |                  |         | _     | 2 blue tones                         | 6.2.22  |

| 1                | Х               | Х               | Х               | Х                | В3               | B2               | B1               | B0               | 0FH     | -     | blue tone 11                         | 6.2.22  |

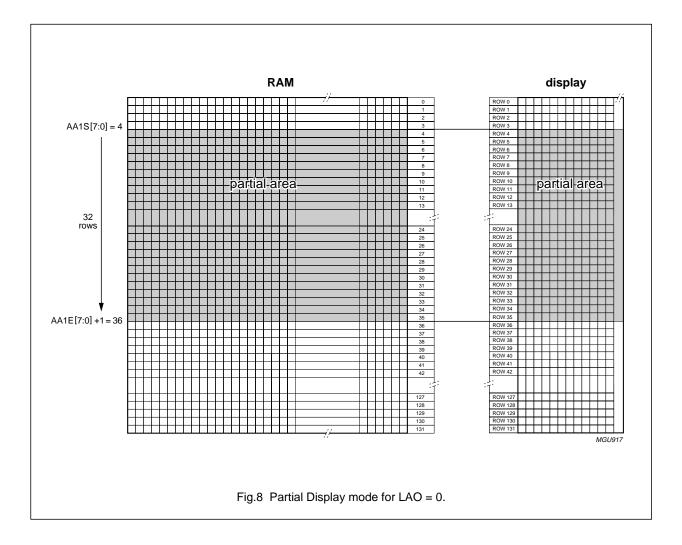

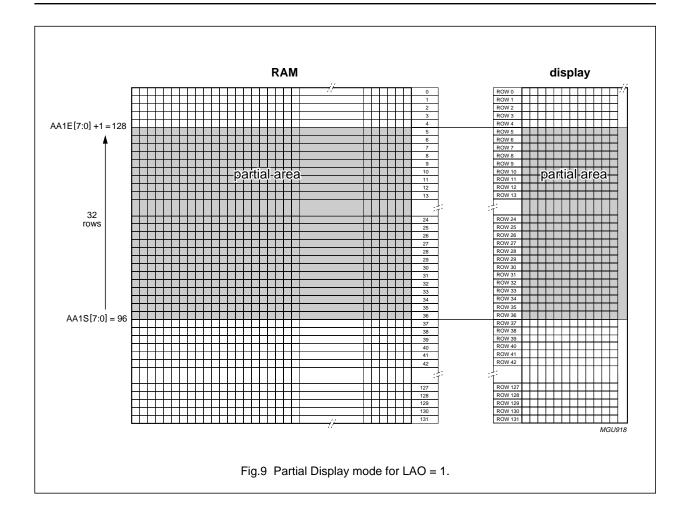

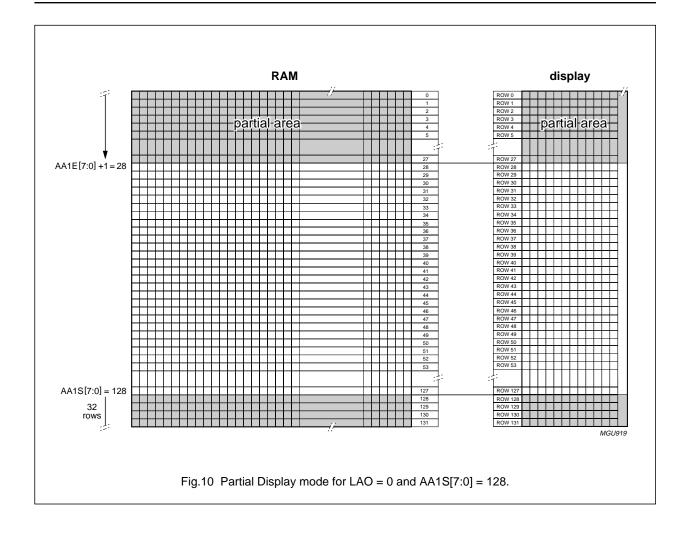

| 0                | 0               | 0               | 1               | 1                | 0                | 0                | 0                | 0                | 30H     | -     | partial area (PTLAR)                 | 6.2.23  |

| 1                | AA1S7           | AA1S6           | AA1S5           | AA1S4            | AA1S3            | AA1S2            | AA1S1            | AA1S0            | 00H     | -     | PTLAR active area start address      | 6.2.23  |

| 1                | AA1E7           | AA1E6           | AA1E5           | AA1E4            | AA1E3            | AA1E2            | AA1E1            | AA1E1            | 1FH     | -     | PTLAR active area end address        | 6.2.23  |

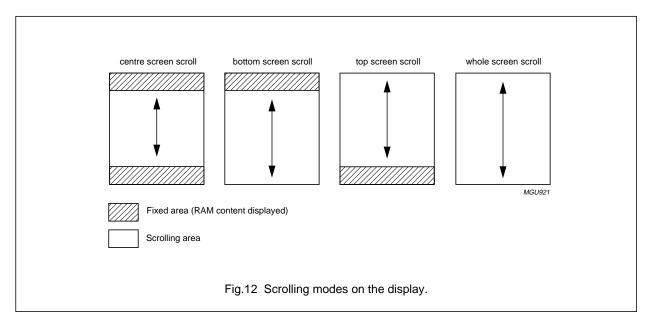

| 0                | 0               | 0               | 1               | 1                | 0                | 0                | 1                | 1                | 33H     | -     | vertical scroll definition (VSCRDEF) | 6.2.24  |

| 1                | TF <sub>7</sub> | TF <sub>6</sub> | TF <sub>5</sub> | TF <sub>4</sub>  | TF <sub>3</sub>  | TF <sub>2</sub>  | TF <sub>1</sub>  | TF <sub>0</sub>  | 00H     | -     | top fixed area                       | 6.2.24  |

| 1                | SA <sub>7</sub> | SA <sub>6</sub> | SA <sub>5</sub> | SA <sub>4</sub>  | SA <sub>3</sub>  | SA <sub>2</sub>  | SA <sub>1</sub>  | SA <sub>0</sub>  | 82H     | -     | scroll area                          | 6.2.24  |

| 1                | BF <sub>7</sub> | BF <sub>6</sub> | BF <sub>5</sub> | BF <sub>4</sub>  | BF <sub>3</sub>  | BF <sub>2</sub>  | BF <sub>1</sub>  | BF <sub>0</sub>  | 00H     | -     | bottom fixed area                    | 6.2.24  |

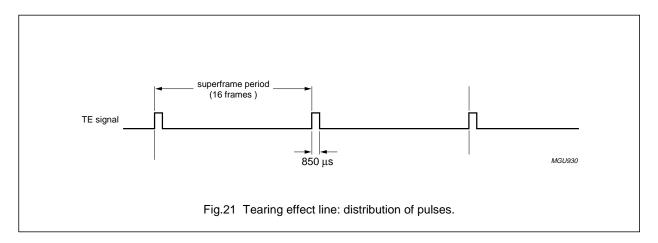

| 0                | 0               | 0               | 1               | 1                | 0                | 1                | 0                | 0                | 34H     | -     | tearing line off (TEOFF)             | 6.2.25  |

| 0                | 0               | 0               | 1               | 1                | 0                | 1                | 0                | 1                | 35H     | -     | tearing line on (TEON)               | 6.2.26  |

| 1                | Х               | Х               | Х               | Х                | Х                | Х                | Х                | Х                | 00H     | -     |                                      | 6.2.26  |

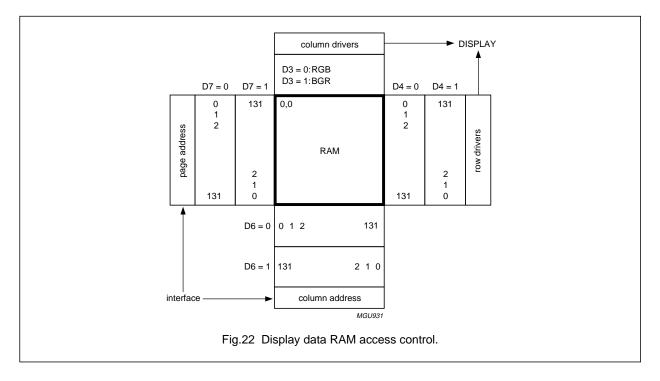

| 0                | 0               | 0               | 1               | 1                | 0                | 1                | 1                | 0                | 36H     | -     | memory data access control (MADCTL)  | 6.2.27  |

| 1                | MY              | MX              | V               | LAO              | RGB              | Х                | Х                | Х                | 00H     | -     | RAM data addressing/data control     | 6.2.27  |

| 0                | 0               | 0               | 1               | 1                | 0                | 1                | 1                | 1                | 37H     | _     | set Scroll Entry Point (SEP)         | 6.2.24  |

| 1                | SEP7            | SEP6            | SEP5            | SEP4             | SEP3             | SEP2             | SEP1             | SEP0             | 00H     | -     | scroll entry point                   | 6.2.24  |

| 0                | 0               | 0               | 1               | 1                | 1                | 0                | 0                | 0                | 38H     | _     | Idle mode off (IDMOFF)               | 6.2.28  |

| 0                | 0               | 0               | 1               | 1                | 1                | 0                | 0                | 1                | 39H     | _     | Idle mode on (IDMON)                 | 6.2.29  |

| 0                | 0               | 0               | 1               | 1                | 1                | 0                | 1                | 0                | 3AH     | _     | interface pixel format (COLMOD)      | 6.2.30  |

| 1                | Х               | Х               | Х               | Х                | Х                | P2               | P1               | P0               | 03H     | -     | colour interface format              | 6.2.30  |

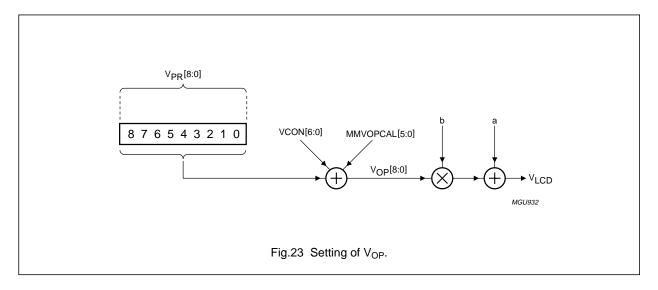

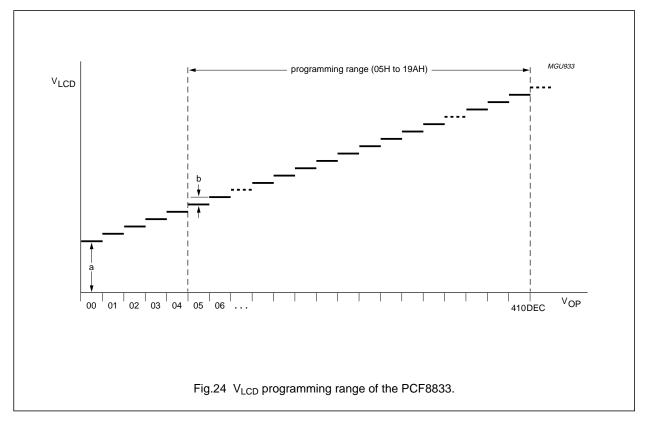

| 0                | 1               | 0               | 1               | 1                | 0                | 0                | 0                | 0                | ВОН     | x (2) | set V <sub>OP</sub> (SETVOP)         | 6.2.31  |

| 1                | Х               | Х               | Х               | Х                | VPR <sub>8</sub> | VPR <sub>7</sub> | VPR <sub>6</sub> | VPR <sub>5</sub> | 08H     | х     | V <sub>OP</sub>                      | 6.2.31  |

| 1                | Х               | Х               | Х               | VPR <sub>4</sub> | VPR <sub>3</sub> | VPR <sub>2</sub> | VPR <sub>1</sub> | VPR <sub>0</sub> | 01H     | х     | V <sub>OP</sub>                      | 6.2.31  |

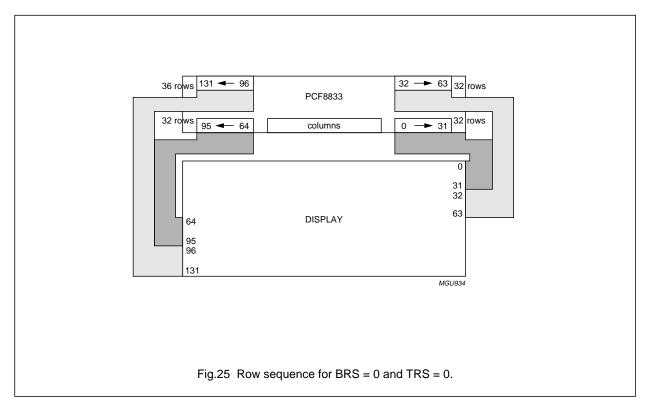

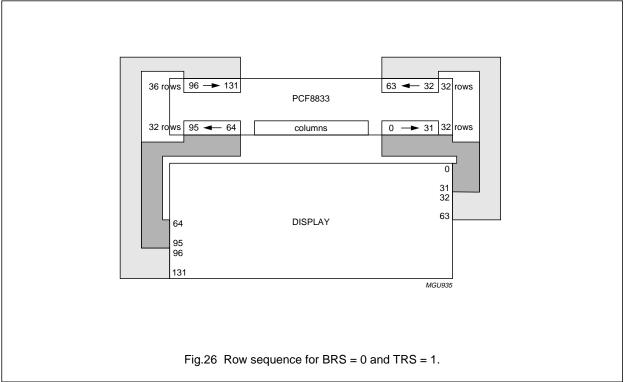

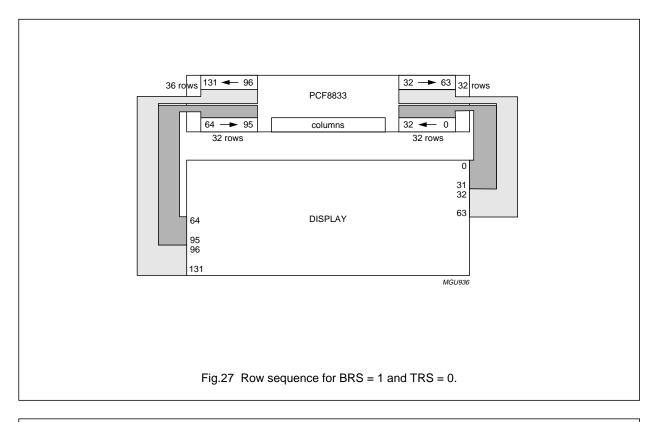

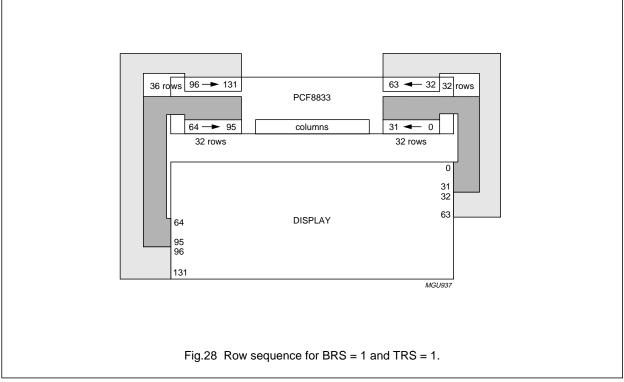

| 0                | 1               | 0               | 1               | 1                | 0                | 1                | 0                | BRS              | B4H     | х     | Bottom Row Swap (BRS)                | 6.2.32  |

2003 Feb 14

9

PCF8833

| D/C | 7                | 6                | 5                | 4                | 3                | 2                | 1                | 0                | DEFAULT | ОТР | DESCRIPTION                                          | SECTION |

|-----|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|---------|-----|------------------------------------------------------|---------|

| 0   | 1                | 0                | 1                | 1                | 0                | 1                | 1                | TRS              | В6Н     | х   | Top Row Swap (TRS)                                   | 6.2.33  |

| 0   | 1                | 0                | 1                | 1                | 1                | 0                | 0                | FINV             | В9Н     | -   | super Frame INVersion (FINV)                         | 6.2.34  |

| 0   | 1                | 0                | 1                | 1                | 1                | 0                | 1                | DOR              | BAH     | -   | Data ORder (DOR)                                     | 6.2.35  |

| 0   | 1                | 0                | 1                | 1                | 1                | 1                | 0                | TCDFE            | BDH     | -   | enable/disable DF temp comp (TCDFE)                  | 6.2.36  |

| 0   | 1                | 0                | 1                | 1                | 1                | 1                | 1                | TCVOPE           | BFH     | -   | enable or disable V <sub>OP</sub> temp comp (TCVOPE) | 6.2.37  |

| 0   | 1                | 1                | 0                | 0                | 0                | 0                | 0                | EC               | C0H     | -   | Internal or external oscillator (EC)                 | 6.2.38  |

| 0   | 1                | 1                | 0                | 0                | 0                | 0                | 1                | 0                | C2H     | х   | set multiplication factor (SETMUL)                   | 6.2.39  |

| 1   | Х                | Х                | Х                | Х                | Х                | Х                | S1               | S0               | 03H     | х   | multiplication factor                                | 6.2.39  |

| 0   | 1                | 1                | 0                | 0                | 0                | 0                | 1                | 1                | C3H     | x   | set TCVOP slopes A and B (TCVOPAB)                   | 6.2.40  |

| 1   | Х                | SLB <sub>2</sub> | SLB <sub>1</sub> | SLB <sub>0</sub> | Х                | SLA <sub>2</sub> | SLA <sub>1</sub> | SLA <sub>0</sub> | 34H     | х   |                                                      | 6.2.40  |

| 0   | 1                | 1                | 0                | 0                | 0                | 1                | 0                | 0                | C4H     | х   | set TCVOP slopes C and D (TCVOPCD)                   | 6.2.40  |

| 1   | Х                | SLD <sub>2</sub> | SLD <sub>1</sub> | SLD <sub>0</sub> | Х                | SLC <sub>2</sub> | SLC <sub>1</sub> | SLC <sub>0</sub> | 75H     | х   |                                                      | 6.2.40  |

| 0   | 1                | 1                | 0                | 0                | 0                | 1                | 0                | 1                | C5H     | х   | set divider frequency (TCDF)                         | 6.2.41  |

| 1   | Х                | DFA <sub>6</sub> | DFA <sub>5</sub> | DFA <sub>4</sub> | DFA <sub>3</sub> | DFA <sub>2</sub> | DFA <sub>1</sub> | DFA <sub>0</sub> | 56H     | х   | set divider factor in region A                       | 6.2.41  |

| 1   | Х                | DFB <sub>6</sub> | DFB <sub>5</sub> | DFB <sub>4</sub> | DFB <sub>3</sub> | DFB <sub>2</sub> | DFB <sub>1</sub> | DFB <sub>0</sub> | 35H     | х   | set divider factor in region B                       | 6.2.41  |

| 1   | Х                | DFC <sub>6</sub> | DFC <sub>5</sub> | DFC <sub>4</sub> | DFC <sub>3</sub> | DFC <sub>2</sub> | DFC <sub>1</sub> | DFC <sub>0</sub> | 30H     | х   | set divider factor in region C                       | 6.2.41  |

| 1   | Х                | DFD <sub>6</sub> | DFD <sub>5</sub> | DFD <sub>4</sub> | DFD <sub>3</sub> | DFD <sub>2</sub> | DFD <sub>1</sub> | DFD <sub>0</sub> | 25H     | х   | set divider factor in region D                       | 6.2.41  |

| 0   | 1                | 1                | 0                | 0                | 0                | 1                | 1                | 0                | C6H     | х   | set divider frequency 8-colour mode (DF8colour)      | 6.2.42  |

| 1   | Х                | DF8 <sub>6</sub> | DF8 <sub>5</sub> | DF8 <sub>4</sub> | DF8 <sub>3</sub> | DF8 <sub>2</sub> | DF8 <sub>1</sub> | DF8 <sub>0</sub> | 35H     | х   | set divider factor in 8-colour mode                  | 6.2.42  |

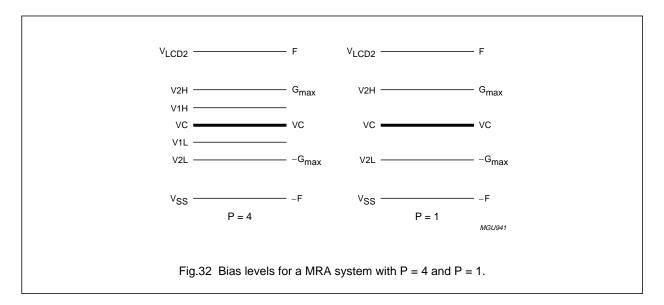

| 0   | 1                | 1                | 0                | 0                | 0                | 1                | 1                | 1                | C7H     | х   | set bias system (SETBS)                              | 6.2.43  |

| 1   | Х                | Х                | Х                | Х                | VB <sub>3</sub>  | VB <sub>2</sub>  | VB <sub>1</sub>  | VB <sub>0</sub>  | 0BH     | х   | bias systems                                         | 6.2.43  |

| 0   | 1                | 1                | 0                | 0                | 1                | 0                | 0                | 0                | C8H     | -   | temperature read back (RDTEMP)                       | 6.2.44  |

| 0   | 1                | 1                | 0                | 0                | 1                | 0                | 0                | 1                | C9H     | -   | N-Line Inversion (NLI)                               | 6.2.45  |

| 1   | NLI <sub>7</sub> | NLI <sub>6</sub> | NLI <sub>5</sub> | NLI <sub>4</sub> | NLI <sub>3</sub> | NLI <sub>2</sub> | NLI <sub>1</sub> | NLI <sub>0</sub> | 13H     | х   | after NLI time slots inversion                       | 6.2.45  |

| 0   | 1                | 1                | 0                | 1                | 1                | 0                | 1                | 0                | DAH     | х   | read ID1 (RDID1)                                     | 6.2.46  |

2003 Feb 14

6

PCF8833

| D/C | 7   | 6   | 5                | 4                | 3                | 2   | 1   | 0     | DEFAULT | ОТР | DESCRIPTION                                     | SECTION |

|-----|-----|-----|------------------|------------------|------------------|-----|-----|-------|---------|-----|-------------------------------------------------|---------|

| 0   | 1   | 1   | 0                | 1                | 1                | 0   | 1   | 1     | DBH     | х   | read ID2 (RDID2)                                | 6.2.46  |

| 0   | 1   | 1   | 0                | 1                | 1                | 1   | 0   | 0     | DCH     | х   | read ID3 (RDID3)                                | 6.2.46  |

| 0   | 1   | 1   | 1                | 0                | 1                | 1   | 1   | SFD   | EFH     | х   | select factory defaults(3)                      | 6.2.47  |

| 0   | 1   | 1   | 1                | 1                | 0                | 0   | 0   | 0     | F0H     | -   | enter Calibration mode                          | 15.5    |

| 1   | Х   | Х   | ORA <sub>2</sub> | ORA <sub>1</sub> | ORA <sub>0</sub> | Х   | OPE | CALMM | 00H     | -   | set calibration control settings                | 15.5    |

| 0   | 1   | 1   | 1                | 1                | 0                | 0   | 0   | 1     | F1H     | -   | shift data in OTP shift registers (OTPSHTIN)    | 15.5    |

| 1   | OS7 | OS6 | OS5              | OS4              | OS3              | OS2 | OS1 | OS0   | XX      | -   | multiple data byte; any number of bytes allowed | 15.5    |

### Notes

- 1. X = don't care.

- 2. This function can be set by OTP.

- 3. If the OTP bit Enable Factory Defaults (EFD) has been programmed to logic 1 (default value is logic 0), then the Set Factory Defaults (SFD) instruction is ignored and the device will always use the OTP default data.

2003 Feb 14

# STN RGB - $132 \times 132 \times 3$ driver

PCF8833

### 6.1 Exit commands

Table 2 Command description

| INPUT<br>COMMAND      | PARAMETERS                                                                                                                                                   | CONDITIONS                                                                                                          | EXIT<br>COMMAND                                 |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Sleep_IN<br>(SLPIN)   | Power-down mode: display off display voltage generation off                                                                                                  | power-down has priority over display and booster settings, but the setting is kept                                  | Sleep_OUT                                       |

| Sleep_OUT<br>(SLPOUT) | exit power-down:  display → DISPON/DISPOFF  display voltage generation → BSTRON/BSTROFF  (refresh from OTP cells if CALMM = 0)                               | after reset; BSTRON and DISPON is set, but become active only with Sleep_OUT                                        | Sleep_IN reset                                  |

| BSTROFF               | display voltage generation off                                                                                                                               | display is switched on or off by DISPON/DISPOFF                                                                     | BSTRON reset                                    |

| BSTRON                | display voltage generation on                                                                                                                                | display is switched on or off by DISPON/DISPOFF                                                                     | BSTROFF                                         |

| DISPOFF               | display off                                                                                                                                                  | rows and columns are tied to V <sub>SS1</sub>                                                                       | DISPON reset                                    |

| DISPON                | display on                                                                                                                                                   |                                                                                                                     | DISPOFF                                         |

| NORON                 | Normal mode on                                                                                                                                               | full display is driven by RAM data                                                                                  | PTLON SEP                                       |

| PTLON                 | Partial mode on                                                                                                                                              | partial display area is driven by RAM data; display area outside partial area is off                                | NORON SEP<br>reset                              |

| SEP                   | Scroll mode on                                                                                                                                               |                                                                                                                     | NORON<br>PTLON reset                            |

| PIXON (DAL)           | in full Display mode (NORON) all pixels<br>are on; in partial Display mode only<br>partial area pixels are driven on; pixels<br>outside partial area are off | command INVON is not effective when DAL is active                                                                   | PIXOFF<br>(DALO)<br>NORON<br>PTLON SEP<br>reset |

| PIXOFF<br>(DALO)      | all pixel off                                                                                                                                                | command INVON is not effective when DALO is active                                                                  | PIXON (DAL)<br>NORON<br>PTLON SEP<br>reset      |

| IDMOFF                | Idle mode off                                                                                                                                                | full colour resolution stored in the RAM is written to the display                                                  | IDMON                                           |

| IDMON                 | Idle mode on                                                                                                                                                 | 8-colour mode became active: The MSB of data stored in RAM is evaluated only                                        | IDMOFF reset                                    |

| INVOFF                | inverted display off                                                                                                                                         |                                                                                                                     | INVON                                           |

| INVON                 | inverted display on                                                                                                                                          | in Partial mode only pixels of partial area<br>are inverted; INVON is not effective;<br>when DAL or DALO are active | INVOFF reset                                    |

| TEOFF                 | tearing pulse disabled                                                                                                                                       |                                                                                                                     | TEON                                            |

| TEON                  | tearing pulse enabled                                                                                                                                        |                                                                                                                     | TEOFF reset                                     |

### STN RGB - $132 \times 132 \times 3$ driver

PCF8833

#### 6.2 Function set

### 6.2.1 NO OPERATION

No operation (NOP) has no effect on internal data or settings. However, it can be used to terminate data transfer (read and write).

Table 3 No operation command bits

| D/C | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | DEFAULT |

|-----|---|---|---|---|---|---|---|---|---------|

| 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 00H     |

### 6.2.2 RESET

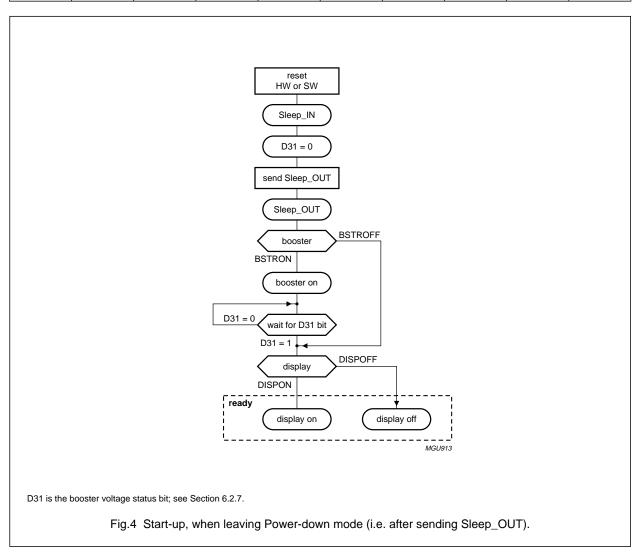

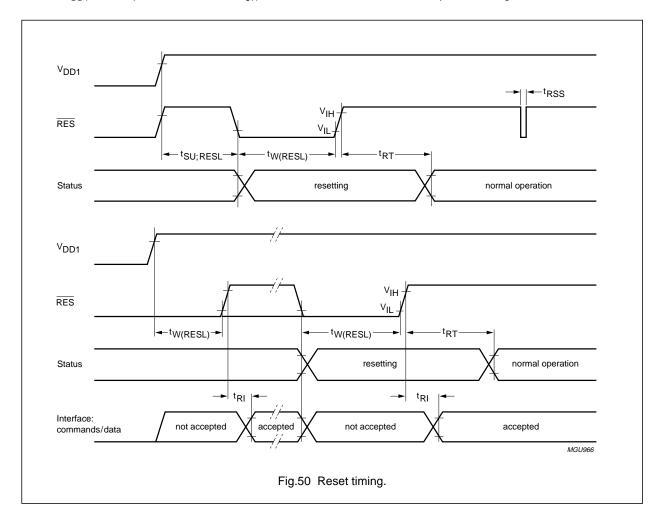

The PCF8833 has a hardware and a software reset. After power-up a hardware reset (pin RES) must be applied; see Fig.50. The hardware and software resets give the same results. After a reset, the chip has the following state:

- All LCD outputs are set to V<sub>SS</sub> (display off)

- RAM data unchanged

- Power-down mode (Sleep\_IN)

- Command register set to default states; see Table 4

- · Interface pins are set to inputs.

After a reset, care must be taken with respect to the reset timing constraints (see Fig.50) when the PCF8833 is powered-up. The power-up must be done by sending the Sleep\_OUT command.

After a power-up the display RAM content is undefined. Neither a hardware reset nor a software reset changes the data that is stored in the display RAM. Sending display data must stop 160 ns before issuing a hardware reset, otherwise the last word written to the display RAM may be corrupted. The row and column outputs are tied to V<sub>SS1</sub> with a reset because power-down (Sleep\_IN) is in the reset state.

Table 4 Reset state after hardware and software reset

| COMMAND  | DESCRIPTION                                                        | RESET STATE |

|----------|--------------------------------------------------------------------|-------------|

| Sleep_IN | PCF8833 is in Sleep_IN mode (booster and display are switched off) | -           |

| INVOFF   | display inversion is off                                           | _           |

| BSTRON   | when Sleep_OUT is active; booster is switched on                   | _           |

| DISPON   | when Sleep_OUT is active; display is turned on                     | _           |

| TEOFF    | tearing effect line pulse is turned off                            | _           |

| IDMOFF   | Idle mode is turned off (4 kbyte colour mode, not 8-colour mode)   | _           |

| NORON    | Normal mode is active, not Scroll or Partial mode                  | _           |

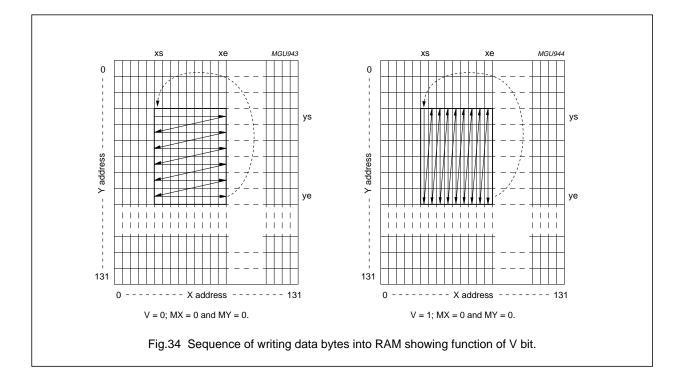

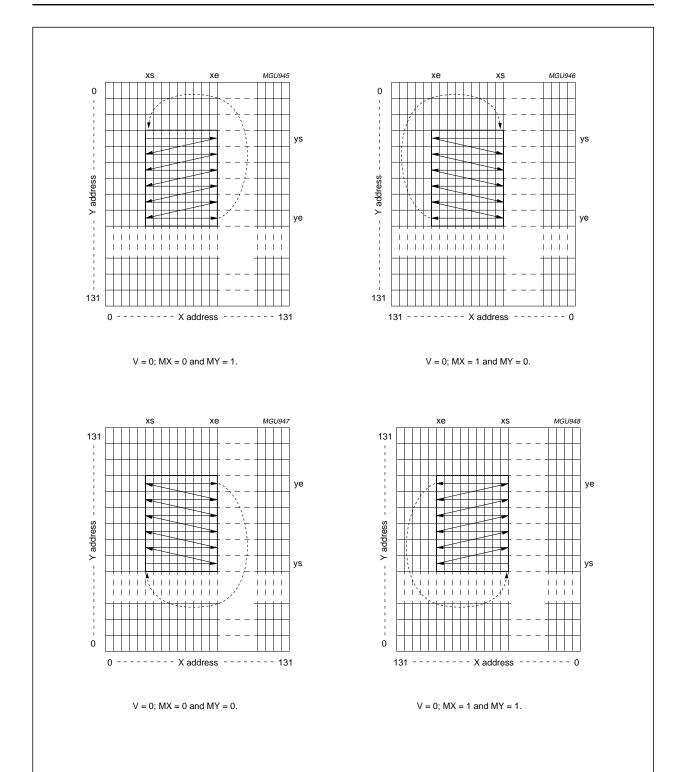

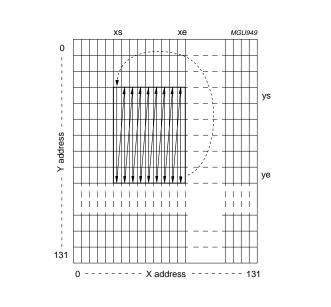

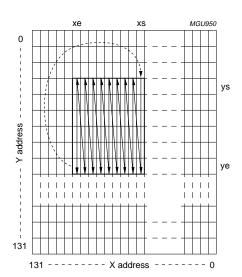

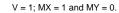

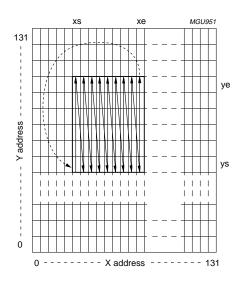

| V        | RAM write in X direction                                           | 0           |

| MY       | no mirror Y                                                        | 0           |

| RGB      | colour order is RGB                                                | 0           |

| MX       | no mirror X                                                        | 0           |

| LAO      | line address order (top to bottom)                                 | 0           |

| BRS      | bottom rows are not mirrored; note 1                               | 0           |

| TRS      | top rows are not mirrored; note 1                                  | 0           |

| FINV     | super frame inversion is on                                        | 1           |

| DOR      | normal data order                                                  | 0           |

| TCDFE    | DF temperature compensation switched on                            | 1           |

| TCVOPE   | VOP temperature compensation switched on                           | 1           |

| EC       | internal oscillator                                                | 0           |

# STN RGB - $132 \times 132 \times 3$ driver

PCF8833

| COMMAND   | DESCRIPTION                                                     | RESET STATE        |  |  |  |  |

|-----------|-----------------------------------------------------------------|--------------------|--|--|--|--|

| xs[7:0]   | x address start                                                 | 2DEC               |  |  |  |  |

| xe[7:0]   | x address end                                                   | 129DEC             |  |  |  |  |

| ys[7:0]   | y address start                                                 | 2DEC               |  |  |  |  |

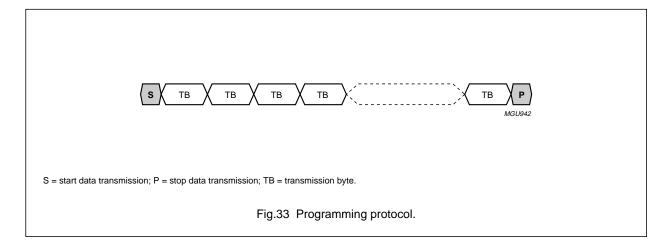

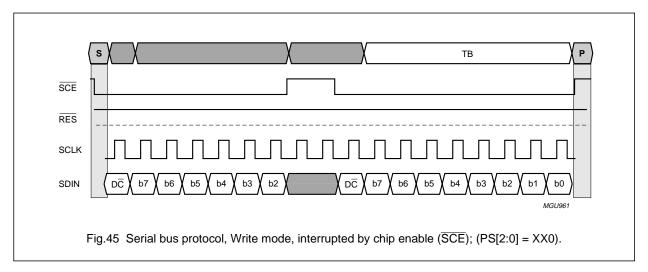

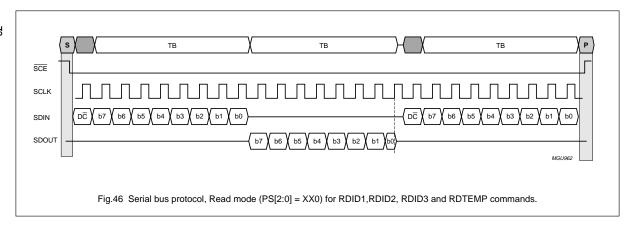

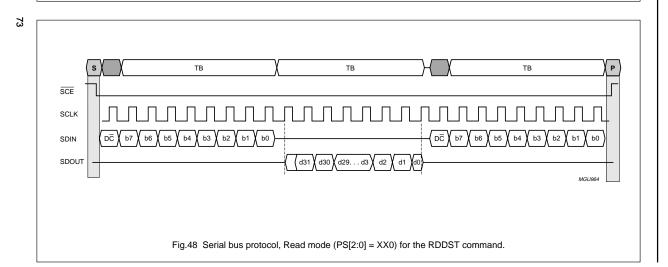

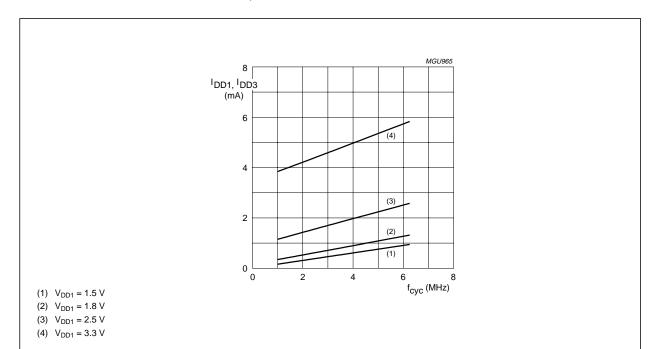

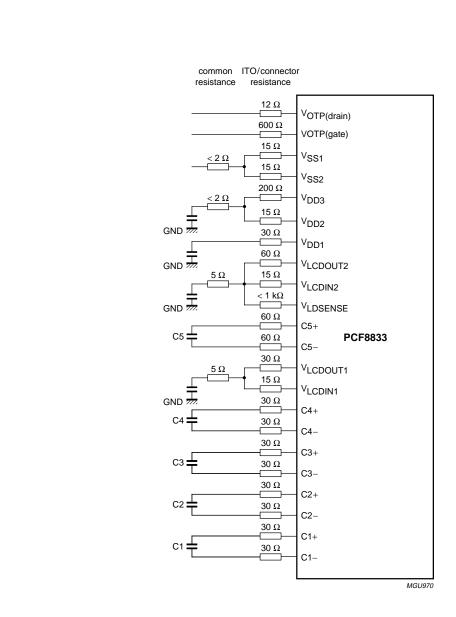

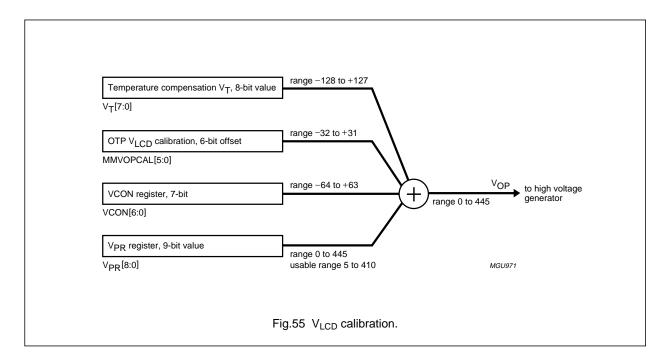

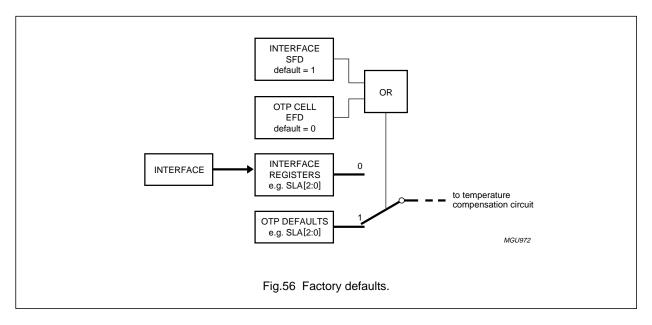

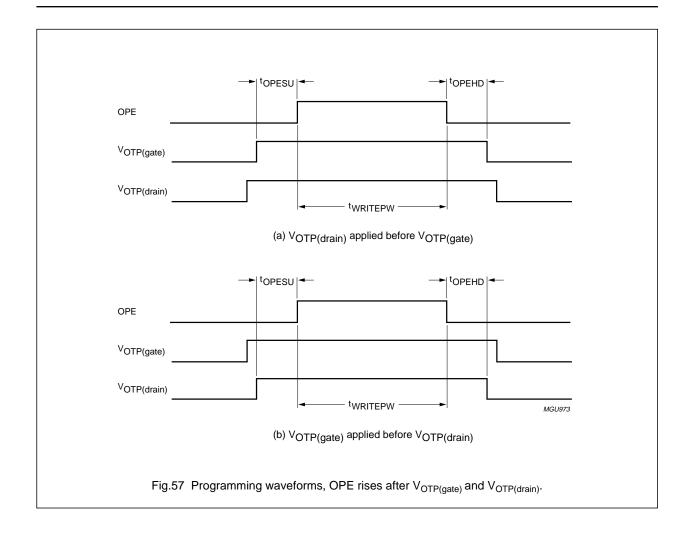

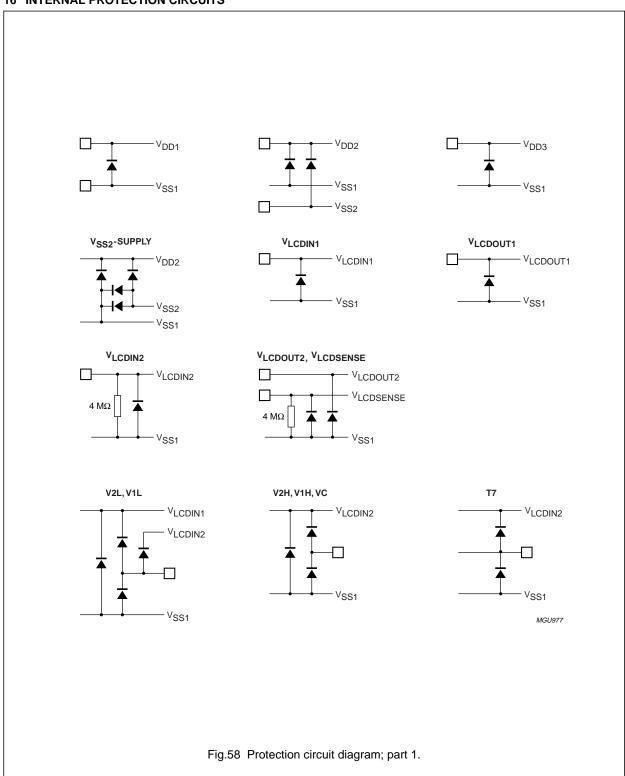

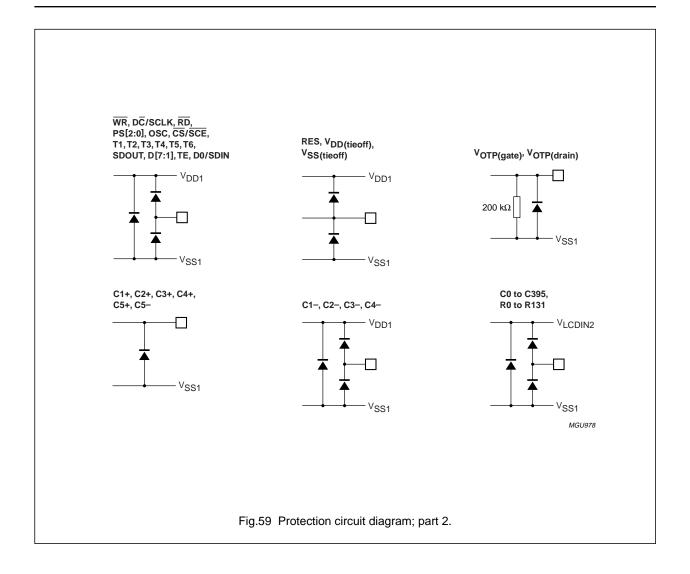

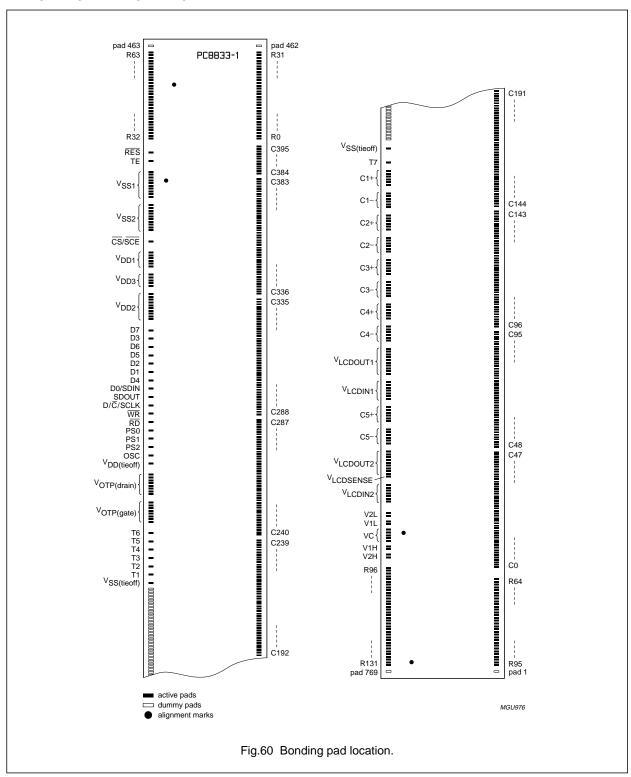

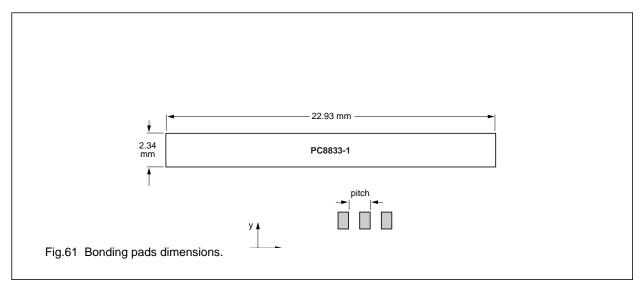

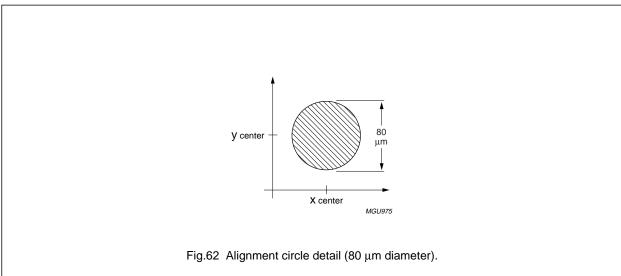

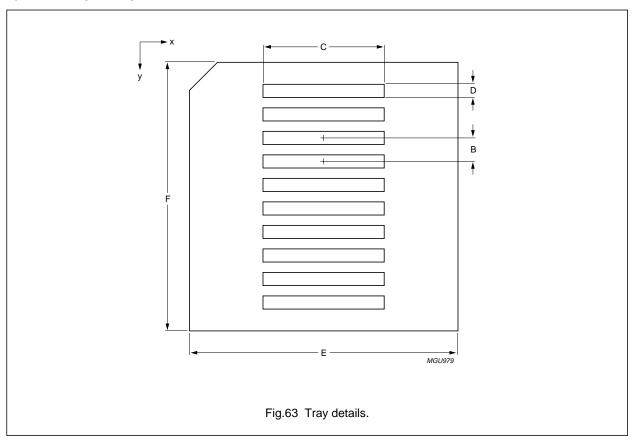

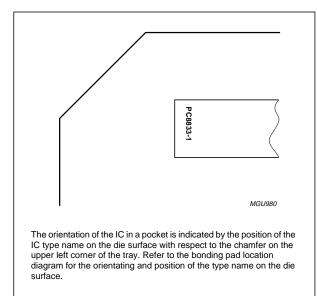

| ye[7:0]   | y address end                                                   | 129DEC             |  |  |  |  |