# 20-CHARACTER 2-LINE DOT MATRIX LCD CONTROLLER DRIVER

#### ■ GENERAL DESCRIPTION

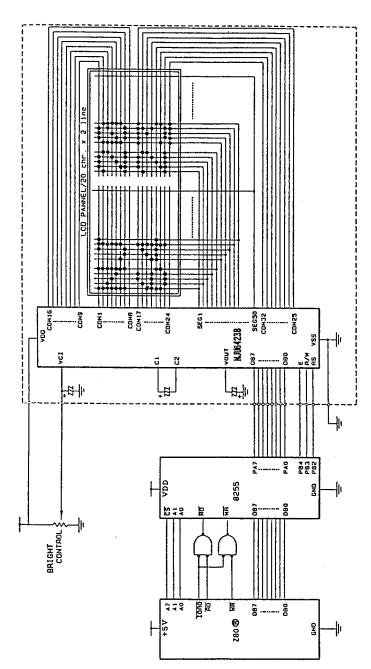

The NJU6423B is a 1 Chip Dot Matrix LCD controller driver for up to 20-character 2-line display.

It contains voltage converter, bleeder resistance, CR oscillator, microprocessor interface circuits, instruction decoder controller, character generator ROM/RAM and high voltage operation common and segment drivers.

The voltage converter and bleeder resistance generates about twofold voltage(10V or 6V) and bias voltage for LCD driving waveform internally from single power supply (5V or 3V). Consequently, high-contrast display can be performed though the simple power supply circuits.

The resistance and capacitance for CR oscillation circuits are incorporated, therefore no external components for the oscillation circuits are required.

The microprocessor interface circuits which operate by 2MHz frequency, can be connected directly to 4/8 bit microprocessor.

The character generator consists of 9,600bits ROM and 64 bytes RAM. The standard version ROM is coded with 240 characters including capital and small letter fonts and some of Japanese fonts.

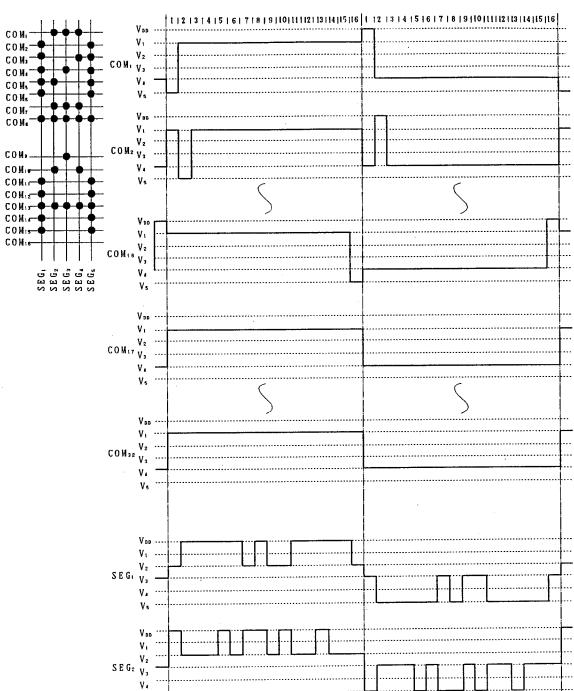

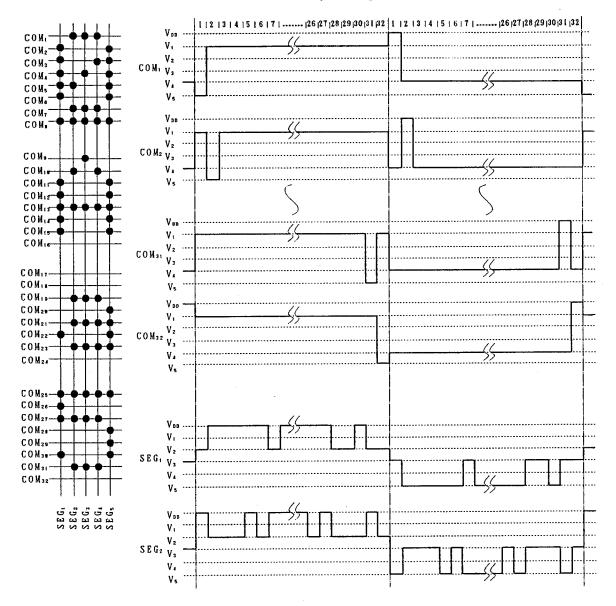

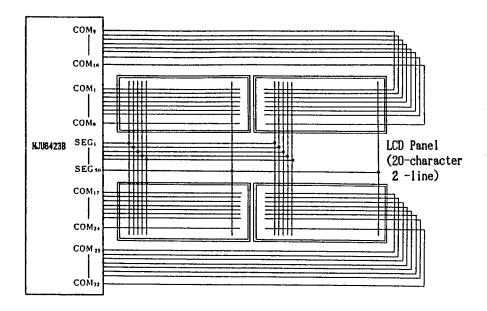

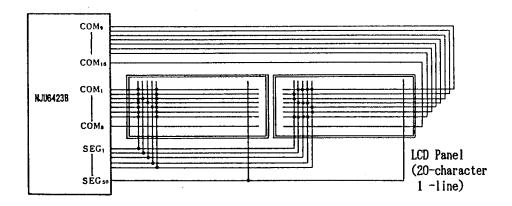

The high voltage operation 32-common and 50-segment drivers operate up to 13.5V or 7V, and drive up to 20-character 2-line LCD panels which divided four common electrode blocks.

# ■ PACKAGE OUTLINE

NJU6423BF

#### **FEATURES**

- 20-character 2-line Dot Matrix LCD Controller Driver

- 4/8 Bit Microprocessor Direct Interface

- Display Data RAM 80 x 8 bits ; Maximum 20-character 2-line Display

- Character Generator ROM 9,600 bits : 240 Characters for 5 x 7 Dots

- Character Generator RAM 64 x 8 bits ; 8 Patterns( 5 x 7 Dots )

- Microprocessor can access to Display Data RAM and Character Generator RAM

- High Voltage LCD Driver; 32-common / 50-segment

- Programmable Duty Ratio : 1/16 Duty for 5 x 7 Dots + Cursor, 1 Line 1/32 Duty for 5 x 7 Dots + Cursor, 2 Lines

- Number of Maximum Display Characters

| Display Line | Duty      | Font                | Max. Disp. Characters |

|--------------|-----------|---------------------|-----------------------|

| 1 Line       | 1/16 duty | 5 x 7 dots + cursor | 20-character 1-line   |

| 2 Lines      | 1/32 duty | 5 x 7 dots + cursor | 20-character 2-line   |

- Useful Instruction Set ; Clear Display, Return Home, Display ON/OFF Cont, Cursor ON/OFF Cont, Display Blink, Cursor Shift, Character Shift

- Power On Initialize Circuit On-chip

- Bleeder Resistance On-chip

- Voltage Converter On-chip

- Oscillation Circuit On-chip

- Low Power Consumption

- Operating Voltage --- 5 V / 3 V

- Package Outline --- Chip / QFP 100 / TCP

- C-MOS Technology

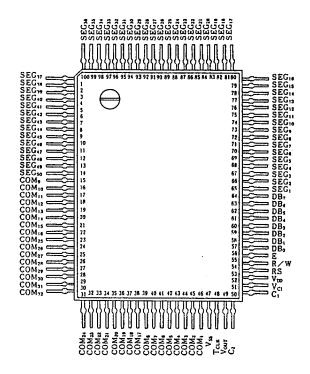

### ■ PIN CONFIGURATION ( NJU6423B )

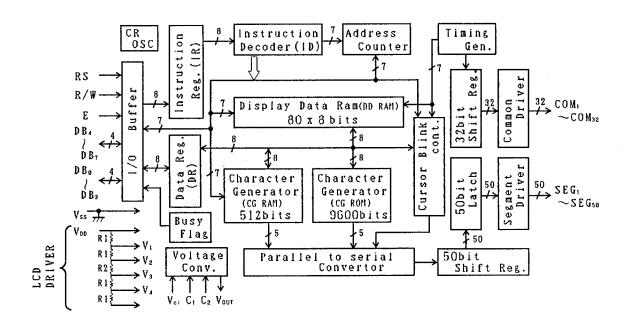

# 5 BLOCK DIAGRAM

# **TERMINAL DESCRIPTION**

| NO.                              | SYMBOL                                                                      | FUNCTION                                                                                                                                                                  |

|----------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 53                               | V <sub>DD</sub>                                                             | Power Source ( + 5V / + 3V )                                                                                                                                              |

| 47                               | Vss                                                                         | Power Source ( OV )                                                                                                                                                       |

| 54                               | RS                                                                          | Register selection signal input(Pull-up resistance On-chip) "0": Instruction Register (Writing) Busy Flag, Address Counter (Reading) "1": Data Register (Writing/Reading) |

| 55                               | R/W                                                                         | Read/Write selection signal input(Pull-up Resistance On-chip)<br>"O": Write , "1": Read                                                                                   |

| 56                               | E ·                                                                         | Read/Write activation signal input                                                                                                                                        |

| 61~64                            | DB₄∼DB <sub>7</sub>                                                         | 3-state Data Bus(Upper) to transfer the data between MPU and NJU6423B. DB7 is also used for the Busy Flag reading.                                                        |

| 57~60                            | DBo∼DB₃                                                                     | 3-state Data Bus(Lower) to transfer the data between MPU and NJU6423B. These bus are not used in the 4bit operation.                                                      |

| 15~22<br>23~30<br>31~38<br>39~46 | COM 9~COM16<br>COM25~COM32<br>COM24~COM17<br>COM 8~COM 1                    | LCD Common driving signal No use terminals output no-active signal, or COM <sub>17</sub> ~COM <sub>32</sub> output no-active signal in the 1/16 duty operation.           |

| 1~14<br>65~100                   | SEG <sub>37</sub> ~SEG <sub>50</sub><br>SEG <sub>1</sub> ~SEG <sub>36</sub> | LCD Segment driving signal                                                                                                                                                |

| 51<br>50                         | C <sub>1</sub><br>C <sub>2</sub>                                            | Capacitor for Voltage Doubler Connecting Terminal ( + ) Capacitor for Voltage Doubler Connecting Terminal ( - )                                                           |

| 52                               | Vci                                                                         | Input Terminal for Voltage Doubler (Normally V <sub>ci</sub> = V <sub>DD</sub> )                                                                                          |

| 49                               | Vout                                                                        | Voltage Doubler Output Terminal                                                                                                                                           |

| 48                               | Tclk                                                                        | Maker Testing Terminal ( Normally Open )                                                                                                                                  |

#### ■ FUNCTIONAL DESCRIPTION

#### (1) Description for each blocks

#### (1-1) Register

The NJU6423B incorporates two 8-bit registers, an Instruction Register(IR) and a Data Register(DR). The Register(IR) stores instruction codes such as "Clear Display" and "Return Home", and address data for Display Data RAM(DD RAM) and Character Generator RAM(CG RAM).

The MPU can write the instruction code and address data to the Register(IR), but it cannot read out from the Register(IR).

The Register(DR) is a temporary stored register, the data stored in the Register(DR) is written into the DD RAM or CG RAM and read out from the DD RAM or CG RAM.

The data in the Register(DR) written by the MPU is transferred automatically to the DD RAM or CG RAM by internal operation.

When the address data for the DD RAM or CG RAM is written into the Register(IR), the addressed data in the DD RAM or CG RAM is transferred to the Register(DR). By the MPU read out the data in the Register(DR), the data transmitting process is performed completely.

After reading the data in the Register(DR) by the MPU, the next address data in the DD RAM or CG RAM is transferred automatically to the Register(DR) to provide for the next MPU reading. These two registers are selected by the selection signal RS as shown below.

Table 1. shows register operation controlled by RS and R/W signals.

Table 1. Register Operation

| RS | R/W | Selected Register | Operation                                        |

|----|-----|-------------------|--------------------------------------------------|

| 0  | 0   |                   | Write                                            |

| 0  | 1   | IR                | Read busy flag(DB7) and address counter(DB0~DB6) |

| 1  | 0   | ND.               | Write (Register(DR) to DD RAM or CG RAM)         |

| 1  | 1   | DR                | Read (DD RAM or CG RAM to Register(DR))          |

#### (1-2) Busy Flag (BF)

When the internal circuits are in the operation mode, the busy flag(BF) is "1", and any instruction reading is inhibited.

The busy flag(BF) is output at  $DB_7$  when RS="0" and R/W="1" as shown in Table 1.

The next instruction should be written after the busy flag(BF) goes to "0".

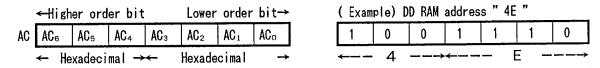

#### (1-3) Address Counter (AC)

The address counter(AC) addressing the DD RAM and CG RAM.

When the address setting instruction is written into the Register(IR), the address information is transferred from Register(IR) to the Counter(AC). The selection of either the DD RAM or CG RAM is also determined by this instruction.

After writing (or reading) the display data to (or from) the DD RAM or CG RAM, the Counter (AC) increments (or decrements) automatically.

The address data in the Counter(AC) is output from  $DB_6 \sim DB_0$  when RS="0" and R/W="1" as shown in Table 1.

#### (1-4) Display Data RAM (DD RAM)

The display data RAM (DD RAM) consists of 80 x 8 bits stores up to 80-character display data represented in 8-bit code.

The unused display data memory area in the DD RAM can be used as a general data memory area. The DD RAM address data set in the address counter(AC) is represented in Hexadecimal.

# (1-4-1) 20-character 1-line Display (Function set code N=0)

The relation between DD RAM address and display position on the LCD is shown below.

When the display shift is performed, the DD RAM address changes as follows:

# (1-4-2) 20-character 2-line Display (Function set code N=1)

The relation between DD RAM address and display position on the LCD is shown below.

|             | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | ←Display<br>Position |

|-------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----------------------|

| lst<br>Line | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | OB | 0C | OD | 0E | 0F | 10 | 11 | 12 | 13 | ← DD RAM Address     |

| 2nd<br>Line | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 4A | 4B | 4C | 4D | 4E | 4F | 50 | 51 | 52 | 53 | ← (Hexadecimal)      |

Note: In the 2-line display mode, the 1st and 2nd line address are defined as (00)<sub>H</sub> to (27)<sub>H</sub> and (40)<sub>H</sub> to (67)<sub>H</sub>. Please note that the end of 1st line address and the beginning of 2nd line address are not consecutive.

When the display shift is performed, the DD RAM address changes as follows:

|                                                                                                                                                                           | (Le  | ft S | hift | Dis  | play | )   |    |    |    |    |    |    |    |     |    |    |    |    |     |    | 1             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|-----|----|----|----|----|----|----|----|-----|----|----|----|----|-----|----|---------------|

| (00)←                                                                                                                                                                     | 01   | 02   | 03   | 04   | 05   | 06  | 07 | 08 | 09 | 0A | OB | 0C | 0D | 0E  | 0F | 10 | 11 | 12 | 13  | 14 |               |

| (40)←                                                                                                                                                                     | 41   | 42   | 43   | 44   | 45   | 46  | 47 | 48 | 49 | 4A | 48 | 4C | 4D | 4E  | 4F | 50 | 51 | 52 | 53. | 54 |               |

| (40) ← 41   42   43   44   43   46   47   46   49   44   46   40   40   41   41   30   31   32   30   34   34   46   47   46   47   48   48   40   40   40   40   40   40 |      |      |      |      |      |     |    |    |    |    |    |    |    |     |    |    |    |    |     |    |               |

|                                                                                                                                                                           | ( Ri | ght  | Shit | t Di | spia | y ) |    | ,  |    |    |    |    |    |     |    |    |    |    | 1   |    |               |

|                                                                                                                                                                           | 27   | 00   | 01   | 02   | 03   | 04  | 05 | 06 | 07 | 08 | 09 | 0A | 0B | OC. | OD | 0E | 0F | 10 | 11  | 12 | <b>→</b> (13) |

|                                                                                                                                                                           | 67   | 40   | 41   | 42   | 43   | 44  | 45 | 46 | 47 | 48 | 49 | 4A | 48 | 4C  | 4D | 4E | 4F | 50 | 51  | 52 | <b>→</b> (53) |

# (1-5) Character Generator ROM (CG ROM)

The Character Generator ROM(CG ROM) generates  $5 \times 7$  dots character pattern represented in 8-bit character codes.

The storage capacity is up to 240 kinds of  $5 \times 7$  dots character pattern.

The correspondence between character code and standard character pattern of NJU6423B is shown in Table 2-1 to 2-3.

User-defined character patterns ( Custom Font ) are also available by mask option.

5

Table 2-1. CG ROM Character Pattern ( ROM version -01 )

|               |   |                   |   |            |                                         | <del> </del> | Up  | per 4 | bit (    | ( Hexa | decin | nal)  | , , , , , , , , , , , , , , , , , , , |       |              |               |       |

|---------------|---|-------------------|---|------------|-----------------------------------------|--------------|-----|-------|----------|--------|-------|-------|---------------------------------------|-------|--------------|---------------|-------|

| `             |   | 0                 | 1 | 2          | 3                                       | 4            | 5   | 6     | 7        | 8      | 9     | A     | В                                     | С     | D            | E             | F     |

|               | 0 | CG<br>RAM<br>(01) |   |            |                                         | ::::         | :   | •.    |          |        |       |       | ••••                                  | :::   | :::.         |               | :::   |

|               | 1 | (02)              |   | •          | <b></b> ;                               |              |     |       | -:::     |        |       | :::   |                                       |       | :            |               | :::   |

|               | 2 | (03)              |   | ::         |                                         |              |     |       | <b>:</b> |        |       |       | •••                                   | • ;   | .:: <b>:</b> | <b>::::</b> : |       |

|               | 3 | 104)              |   |            | •:                                      |              | ::  | :     | :::.     |        |       | :     |                                       |       | ::::         | :::.          | ::-;: |

|               | 4 | (05)              |   | ::::       | :::                                     |              | -   |       | <b>:</b> |        |       | ٠.    |                                       |       | :::          |               | ::::  |

|               | 5 | (06)              |   |            | :                                       |              | !   | ::::  |          |        |       | ::    | .:                                    | :     |              | ::::          | 1     |

| (Hexadecimal) | 6 | 1071              |   |            | ::::                                    |              |     |       | ٠,,٠     |        |       |       |                                       | ••••  |              | ::            | ::    |

| l .           | 7 | (08)              |   | :          | ::                                      |              |     | :!    | 11       |        |       | :::   | :::::                                 | :::   |              | ::::          | .:    |

| er 4 bit      | 8 | (01)              |   | ÷.         |                                         |              | ::: |       | :::      |        |       | ·:    | ·:::                                  |       | .:           | :"            | :::   |

| Lower         | 9 | 1021.             |   | <u>;</u> : | • • • • • • • • • • • • • • • • • • • • |              | ::: | :     | ·!       |        |       | ::::  | ::                                    | ,.    | : ::-        | :             | ••    |

|               | A | (03)              |   | ::::       | ::                                      |              | :   |       |          |        |       |       |                                       | : :   |              |               |       |

|               | В | (04)              |   |            | ::                                      |              |     |       | :        |        |       | :::   |                                       |       |              | <b>∷:</b>     |       |

|               | С | (05)              |   | :          | ::                                      |              |     |       |          |        |       | ::::  | <b></b> :                             |       | :::          | 1             |       |

|               | D | (06)              |   |            | •••••                                   |              |     |       |          |        |       |       | .·:                                   | ••••  | 1            |               |       |

|               | E | (07)              |   | ::         | ···                                     |              |     | :::   |          |        |       |       |                                       | : : : | •••          |               |       |

|               | F | (08)              |   |            |                                         |              |     | ::    |          |        |       | : : : | ·                                     | ::    |              |               |       |

Table 2-2. CG ROM Character Pattern ( ROM version -02 )

|               |   |                   | <del></del> | -    |      | ·   |              | Uppe | r 4 b      | its ( | Hexa | decim | al)      |       |               |              |              |

|---------------|---|-------------------|-------------|------|------|-----|--------------|------|------------|-------|------|-------|----------|-------|---------------|--------------|--------------|

|               |   | 0                 | 1           | 2    | 3    | 4   | 5            | 6    | 7          | 8     | 9    | A     | В        | С     | D             | E            | F            |

|               | 0 | CG<br>RAM<br>(01) |             |      |      |     | :            | ٠.   |            | ::::  | :::: |       | ****     | :::   | :::.          | ::::         | <b>!:</b> •  |

|               | 1 | (02)              |             |      | ::.  |     |              | •::: | •:::       | 1     |      | :::   | .:       | :::-  | i;            | ::::         | :::          |

|               | 2 | (03)              |             | ::   |      |     |              |      |            | ::::: |      |       | ::       | • ; • | .:·: <b>·</b> | ::::         |              |

|               | 3 | (04)              |             |      | :    | i   | ::           | :    | :::.       |       | ::   | :     | :::      | ::    | ::::          | :::.         | ::::         |

|               | 4 | (05)              | ::::        | :::  | :::  |     |              |      |            | •     | :::: | ٠.    |          | •     | :::           | <b></b> :    | :::          |

|               | 5 | (06)              |             | ::.: |      |     |              | :::: |            |       | ::   | ::    |          |       |               | :::.         | ii           |

| ( Hexadecimal | 6 | (07)              |             |      |      |     |              |      | i.,:       |       |      | :::   |          | ••••  |               | <b>:</b> ::: | ::           |

| ( Hexa        | 7 | (08)              |             | •    |      |     |              | •    | ii         | :::-  |      | :::   |          |       | :             | •            |              |

| 4 bits        | 8 | (01)              |             |      |      |     | ::: <u>:</u> |      | <b>:::</b> | ::::  | •::: | ·: •  | •        |       | ·.!           |              | ::: <u>.</u> |

| Lower         | 9 | (02)              | •           |      | :::: | ••• | ii           |      | ·!         | ::    | :::: | ::::  |          |       | : ::          | ••           | ::           |

|               | A | (03)              | ÷·          | :•:  | ::   |     | :            | :::  |            |       |      |       |          | •     |               | ::           |              |

|               | В | (04)              | :           |      | :    |     |              |      |            |       | :::. | :::   | .:       |       |               | <b>∷</b> :   |              |

|               | С | (05)              | :           | ።    | •••  |     |              |      |            | ::-   |      | :::   | <b>:</b> | :     | ·.:           | :::-         |              |

|               | D | (06)              |             | •••• |      |     |              |      |            |       |      | .::.  |          | •••   | <b>:</b>      | ::           |              |

|               | Е | (07)              | ·:::        | ::   |      |     | •••          | •    | ••         |       |      | :::   |          |       | •••           | •            |              |

|               | F | (08)              | :::         | .••  |      |     | •••••        |      | •          |       |      | :::   |          | ::    | :::           |              |              |

Table 2-3. CG ROM Character Pattern ( ROM version -03 )

|               |   |                   |       |      |       |   | Up   | per 4 | bits         | ( Hex | adeci      | mal)  |      |          |      |             |            |

|---------------|---|-------------------|-------|------|-------|---|------|-------|--------------|-------|------------|-------|------|----------|------|-------------|------------|

|               |   | 0                 | 1.    | 2    | 3     | 4 | 5    | 6     | 7            | 8     | 9          | Α     | В    | С        | D    | Е           | F          |

|               | 0 | CG<br>RAM<br>(01) |       |      |       |   |      | ::    |              | ::::  |            | .:::  | •    |          |      |             |            |

|               | 1 | (02)              | ••••• | •    | :     |   |      |       | •:::         | •     | ::::       |       | • •  |          |      |             | i:         |

|               | 2 | (03)              |       | ::   | •     |   |      | :::   |              | ::::  |            | ::::: | •:•  | ::::     |      |             |            |

|               | 3 | (04)              | .: .  |      |       |   | :    | ·     | •            | :::   | ::::       | • •   | •    |          |      | ::::        | ::         |

|               | 4 | (05)              |       |      |       |   | •    |       |              | •:::  | ::::       |       | •    |          |      | ••••        |            |

|               | 5 | (06)              | :.    | **;  | ••    |   |      | ::::  | <b>i</b>     | •:::  | ::::       |       |      |          | :::  |             |            |

| cimal)        | 6 | (07)              | 7     |      | ::::: |   |      |       | i.,.i        | -:::  | : <b>:</b> |       |      | •        |      |             | <b>!!!</b> |

| ( Hexadecimal | 7 | (08)              | .:    | ::   |       |   |      |       | 1,.,1        | ::::  | :i         |       | :::  | •::•     | : 1  | <b>i.</b> . | •==        |

| 4 bits        | 8 | (01)              | ·     |      |       |   |      |       | <b>:::</b> : | ::::  | ••         |       |      | ••••     |      | <b>i</b> :: |            |

| Lower         | 9 | (02)              | •     | .:   | •     |   | ••   |       | ·i           |       |            |       | ::   |          |      | .:.         | ***        |

|               | A | (03)              |       |      | ::    |   |      |       |              |       |            |       | ::   |          | ::.  |             | ****       |

|               | В | (04)              |       |      | ::    |   |      |       | :            |       |            |       | ·::: | <b>!</b> | 1    |             |            |

|               | С | (05)              |       | :    | •:    | i | •••  |       |              |       |            |       | ::-  |          |      | :           |            |

|               | D | (06)              | ::::  | •••• | ***** |   | }    |       | :            |       |            | ::::  | :::  | l .      | •    | 311.        |            |

|               | Е | (07)              |       | ::   | :     |   | İ    | :":   | ••••         |       |            |       |      |          | :::  | ::          |            |

|               | F | (08)              |       |      | •     |   | •••• | ::    | ::::         |       | :          |       |      |          | :::: |             |            |

#### (1-6) Character Generator RAM ( CG RAM )

The character generator RAM ( CG RAM ) can store any kind of character pattern in 5 x 7 dots written by the user program to display user's original character pattern. The CG RAM can store 8 kinds of character in 5 x 7 dots mode.

To display user's original character pattern stored in the CG RAM, the address data (00) H -(07)<sub>H</sub> or (08)<sub>H</sub> - (0F)<sub>H</sub> should be written to the DD RAM as shown in Table 2-1 to 2-3.

Table 3. shows the correspondence among the character pattern, CG RAM address and Data. Unused memory area of the CG RAM can also be used as the general data memory area.

Table 3. Correspondence of CG RAM address, DD RAM character code and CG RAM character pattern ( 5 x 7 dots ).

| Character Code<br>(DD RAM Data) | CG RAM<br>Address                       | Character Pattern<br>(CG RAM Data)            |                                                      |

|---------------------------------|-----------------------------------------|-----------------------------------------------|------------------------------------------------------|

| 76543210                        | 5 4 3 2 1 0                             | 765 43210                                     |                                                      |

| Upperbit Lowerbit               | Upper Lower                             | Upperbit Lowerbit                             |                                                      |

| 0000*000                        | 0 0 0 0 0 0 0 0 0 1 0 1 0 1 0 1 1 1 1 1 | * * *   1   0   0   0   0   0   0   0   0   0 | Character Pattern<br>Example (1)<br>←Cursor Position |

| 0000*001                        | 0 0 1 0 0 0 1 0 1 0 1 0 1 0 1 0 1 1 1 1 | * * * * * * * * * * * * * * * * * * *         | Character Pattern<br>Example (2)<br>←Cursor Position |

|                                 | 0 0 0                                   | 1 1                                           |                                                      |

| 1                               |                                         |                                               | * : Don't Care                                       |

| 0 0 0 0 * 1 1 1                 | 1 1 1 1 0 1 1 1 1 0 0 0 1 1 0 1 1 1 1 1 | * * * *                                       |                                                      |

Notes: 1. Character code bit 0 to 2 correspond to the CG RAM add. 3 to 5(3bits:8 patterns). 2. CG RAM address 0 to 2 designate character pattern line position. The 8th line is

the cursor position and the display is performed by logical OR with cursor. Therefore, in case of the cursor display, the 8th line should be "0". If there is "1" in the 8th line, the bit "1" is always displayed on the cursor position regardless of cursor existence.

Character pattern row position correspond to the CG RAM data bits 0 to 4 are shown above. The bits 5 to 7 of the CG RAM are not appear on the display (no meaning for the display), but memory elements are existing, therefore it can be used as the general purpose RAM.

CG RAM character patterns are selected when character code bits 4 to 7 are all "0" and it is addressed by character code bits 0 to 2. Therefore, the address  $(00)_{\rm H}$  and  $(08)_{\rm H}$ ,  $(01)_{\rm H}$  and  $(09)_{\rm H}$ , -----,  $(07)_{\rm H}$  and  $(0F)_{\rm H}$  select the same character pattern as shown in Table 2-1 to 2-3 and Table 3. "1" for CG RAM data corresponds to display On and "0" to display Off.

New Japan Radio Co., Ltd.

#### (1-7) Timing Generator

The timing generator generates a timing signals for the DD RAM, CG RAM, CG ROM and other internal circuits operation.

RAM read timing for the display and internal operation timing for MPU access are separately generated, so that they may not interfere with each other

Therefore, when the data write to the DD RAM for example, there will be no undesirable influence, such as flickering, in areas other than the display area.

#### (1-8) LCD Driver

LCD driver consist of 32-common driver and 50-segment driver.

When the line number is selected by a program, the required common drivers output the common driving waveform and the other common drivers output non-selection waveform automatically.

The 50 bits of character pattern data are shifted in the shift-register and latched when the 50 bits shift performed completely. This latched data controls display driver to output LCD driving waveform.

# (1-9) Cursor Blinking Control Circuit

This circuits controls cursor On/Off and cursor position character blinks.

The cursor or blinks appear in the digit residing at the DD RAM address set in the address counter (AC).

When the address counter is (08) H, a cursor position is shown as follows:

| (AC)              | AC <sub>6</sub> | ACs<br>O | AC₄<br>0 | AC₃<br>1 | AC <sub>2</sub> | AC <sub>1</sub> | AC <sub>o</sub> |    |        |          |          |            |     |                                                         |

|-------------------|-----------------|----------|----------|----------|-----------------|-----------------|-----------------|----|--------|----------|----------|------------|-----|---------------------------------------------------------|

| 1-line<br>Display | 1 00            | 2 01     | 3        | 4<br>03  | 5               | 6               | 7 06            | 8  | 9      | 10<br>09 | 11<br>0A | 12<br>0B   |     | ← Display position<br>← DD RAM address<br>(Hexadecimal) |

|                   | 1               | 2        | .3       | 4        | 5               | 6               | 7               | 8  | †<br>9 | Curs     | or p     | osit<br>12 | ion | (Hexadecimal) ← Display position                        |

| 2-line            | 00              | 01       | 02       | 03       | 04              | 05              | 06              | 07 | 08     | 09       | OA       | OB         |     | ←<br>DD RAM address                                     |

| Display           | 40              | 41       | 42       | 43       | 44              | 45              | 46              | 47 | 48     | 49       | 4A       | 4B         |     | ← DD RAM address<br>← (Hexadecimal)                     |

|                   |                 |          |          |          |                 |                 |                 |    | 1      | Curs     | or p     | osit       | ion |                                                         |

(Note) The cursor or blinks also appear when the address counter (AC) selects the CG RAM.

But the displayed cursor and blink are meaningless.

If the AC storing the CG RAM address data, the cursor and blink are displayed in the meaningless position.

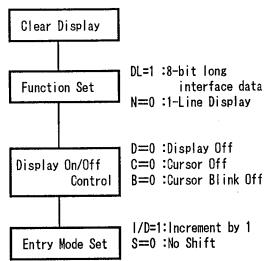

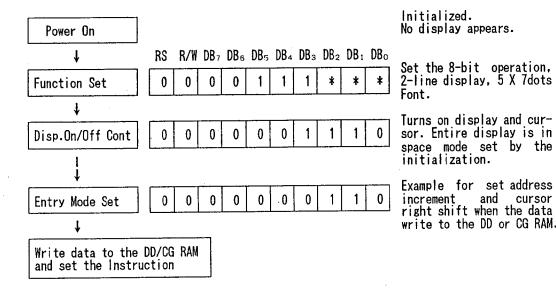

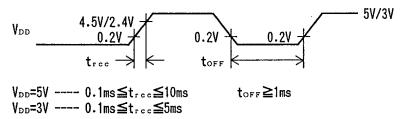

#### (2) Power on Initialization by internal circuits

The NJU6423B is automatically initialized by internal power on initialization circuits when the power is turned on. In the internal power on initialization, following instructions are executed. During the Internal power on initialization, the busy flag (BF) is "1" and this status is kept 10 ms after  $V_{\rm DD}$  rises to 4.5V.

Initialization flow is shown below:

If the condition of power supply rise time described in the Electrical Characteristics is not satisfied, the internal Power On Initialization Circuits will not operate and initialization will not be performed. In this case the initialization by MPU software is required.

19

# (3) Instructions

The NJU6423B incorporates two registers, an Instruction Register(IR) and a Data Register(DR). These two registers store control information temporarily to allow interface between NJU6423B and MPU or peripheral ICs operating different cycles. The operation of NJU6423B is determined by this control signal from MPU. The control information includes register selection signals (RS), read/write signals (R/W) and data bus signals (DBo to DB7).

Table 4. shows each instruction and its operating time.

Note) The execution time mentioned in Table 4. based on fcp or fosc=290kHz.

If the oscillation frequency is changed, the execution time is also changed.

Table 4. Table of Instructions

|                                | T   |     |             |                 |                      |          |          |                 |                 |       | T                                                                                                                                                            |              |

|--------------------------------|-----|-----|-------------|-----------------|----------------------|----------|----------|-----------------|-----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| INSTRUCTIONS                   | RS  | R/W | DB 7        | DB <sub>e</sub> | 0<br>DB <sub>5</sub> | D<br>DB₄ | E<br>DB₃ | DB <sub>2</sub> | DB <sub>1</sub> | DBo   | DESCRIPTION                                                                                                                                                  | EXEC<br>TIME |

| Maker Testing                  | 0   | 0   | 0           | 0               | 0                    | 0        | 0        | 0               | 0               | 0     | All "O" code is using for maker testing.                                                                                                                     |              |

| Clear Display                  | 0   | 0   | 0           | 0               | 0                    | 0        | 0        | 0               | 0               | 1     | Display clear and sets DD RAM address 0 in AC.                                                                                                               | 1.42ms       |

| Return Home                    | .0  | 0   | 0           | 0               | 0                    | 0        | 0        | 0               | 1               | *     | Sets DD RAM address 0 in AC and<br>returns display being shifted to<br>original position.<br>DD RAM contents remain unchanged                                | 1.42ms       |

| Entry Mode Set                 | 0   | 0   | 0           | 0               | 0                    | 0        | 0        | 1               | I/D             | S     | Sets cursor move direction and specifies shift of display are performed in data read/write. I/D=1:Increment, I/D=0:Decrement S=1:Accompanies display shift   | 35us         |

| Display On/Off<br>Control      | 0   | 0   | 0           | 0               | 0                    | 0        | 1        | D               | C               | В     | Sets of display On/Off(D),<br>cursor On/Off(C) and blink of<br>cursor position character(B).                                                                 | 35us         |

| Cursor or<br>Display Shift     | 0   | 0   | 0           | 0               | 0                    | 1        | S/C      | R/L             | *               | *     | Moves cursor and shifts display without changing DD RAM contents S/C=1: Display shift S/C=0: Cursor shift R/L=1: Shift to the right R/L=0: Shift to the left | 52us         |

| Function Set                   | 0   | 0   | 0           | 0               | 1                    | DL       | N        | *               | *               | *     | Sets interface data length(DL),<br>number of display lines(N).<br>Sets 5x7 character font.<br>DL=1 : 8 bits , DL=0 : 4 bits<br>N=1 : 2 lines , N=0 : 1 line  | 35us         |

| Set CG RAM<br>Address          | 0   | 0   | 0           | 1               | <b>4-</b>            |          | A        | eg.             |                 | >     | Sets CG RAM address. After this instruction, the data is transferred to/from CG RAM.                                                                         | 35us         |

| Set DD RAM<br>Address          | 0   | 0   | 1           | <b>←</b>        |                      |          | ADD      |                 |                 | -→    | Sets DD RAM address. After this instruction, the data is transferred to/from DD RAM.                                                                         | 35us         |

| Read Busy Flag<br>& Address    | 0   | 1   | BF          | <b>←</b>        |                      |          | AC       |                 |                 | >     | Reads busy flag and AC contents.<br>BF=1 : Internally operating<br>BF=0 : Can accept instruction                                                             | 0us          |

| Write Data to<br>CG & DD RAM   | 1   | 0   | <b>~</b>    |                 | 1                    | #rit     | e Da     | ta              |                 |       | Writes data into DD or CG RAMs.                                                                                                                              | 35us         |

| Read Data from<br>CG or DD RAM | 1   | 1   | <del></del> |                 |                      | Read     | Data     | 3               |                 | >     | Reads data from DD or CG RAMs.                                                                                                                               | 52us         |

| Explanation of<br>Abbreviation | Acg | : C | G RAI       | I ad            | dres                 | s , i    | ADD      | : DD            | RAM             | addre | racter generator RAM<br>ess, Corresponds to cursor address<br>and CG RAMs                                                                                    |              |

#### (3-1) Description of each instructions

# (a) Maker Testing

|      | RS | R/W | DB7 | DBe | DB <sub>5</sub> | DB₄ | DB3 | DB <sub>2</sub> | DB 1 | DBo |

|------|----|-----|-----|-----|-----------------|-----|-----|-----------------|------|-----|

| Code | 0  | 0   | 0   | 0   | .0              | 0   | 0   | 0               | 0    | 0   |

All "0" code in 4 bit length is using for device testing mode (only for maker). Therefore, please avoid all "0" input or no meaning Enable signal input at data "0". (Especially please pay attention the output condition of Enable signal when the power turns on)

#### (b) Clear Display

|      | RS | R/W | DB7 | DB <sub>6</sub> | DB <sub>5</sub> | DB4 | DB₃ | DB2 | DB <sub>1</sub> | DBo |

|------|----|-----|-----|-----------------|-----------------|-----|-----|-----|-----------------|-----|

| Code | 0  | 0   | 0   | 0 .             | 0               | 0   | 0   | 0   | 0               | 1   |

Clear display instruction is executed when the code "1" is written into  $DB_0$ . When this instruction is executed, the space code  $(20)_{\rm H}$  is written into every DD RAM address, the DD RAM address 0 is set into the address counter and entry mode is set increment.

If the cursor or blink are displayed, they are returned to the left end of the LCD (the left end of the 1st line in the 2-line display mode).

The S of entry mode does not change.

Note: The character pattern for character code (20) must be blank code in the user-defined character pattern (Custom font).

# (c) Return Home

|      |   | R/W |   |   |   |   |   |   |   | $DB_{o}$ |                |

|------|---|-----|---|---|---|---|---|---|---|----------|----------------|

| Code | 0 | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 1 | *        | * = Don't care |

Return home instruction is executed when the code "1" is written into DB<sub>1</sub>. When this instruction is executed, the DD RAM address 0 is set into the address counter. Display is returned its original position if shifted, the cursor or blink are returned to the left end of the LCD (the left end of the 1st line in the 2-line display mode) if the cursor or blink are on the display.

The DD RAM contents do not change.

(d) Entry Mode Set

|      | RS | R/W | DB7 | DBe | DBs | DB₄ | DВз | DB2 | DB <sub>1</sub> | $DB_o$ |

|------|----|-----|-----|-----|-----|-----|-----|-----|-----------------|--------|

| Code | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 1   | I/D             | S      |

Entry mode set instruction which sets the cursor moving direction and display shift On/Off, is executed when the code "1" is written into  $DB_2$  and the codes of (I/D) and (S) are written into  $DB_1(I/D)$  and  $DB_0(S)$ , as shown below.

(1/D) sets the address increment or decrement, and the (S) sets the entire display shift in the DD RAM writing.

| I/D | Function                                                                                                                             |

|-----|--------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Address increment: The address of the DD RAM or CG RAM increment (+1) whe the read/write, and the cursor or blink move to the right. |

| 0   | Address decrement: The address of the DD RAM or CG RAM decrement (-1) whe the read/write, and the cursor or blink move to the left.  |

|     |                                                                                                                                      |

| S   | Function                                                                                                                             |

| S | Function                                                                                                                                                                                                                                                                                                                                           |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | Entire display shift.  The shift direction is determined by I/D: shift to the left at I/D=1 and shift to the right at the I/D=0. The shift is operated only for the character, so that it looks as if the cursor stands still and the display moves. The display does not shift when reading from the DD RAM and writing/reading into/from CG RAM. |

| 0 | The display does not shifting.                                                                                                                                                                                                                                                                                                                     |

# (e) Display On/Off Control

|      | RS | R/W | DB7 | DB6 | DB <sub>5</sub> | DB₄ | DВз | DB <sub>2</sub> | DB 1 | DBo |

|------|----|-----|-----|-----|-----------------|-----|-----|-----------------|------|-----|

| Code | 0  | 0   | 0   | 0   | 0               | 0   | 1   | D               | C    | В   |

Display On/Off control instruction which controls the whole display On/Off, the cursor On/Off and the cursor position character blink, is executed when the code "1" is written into  $DB_3$  and the codes of (D), (C) and (B) are written into  $DB_2(D)$ ,  $DB_1(C)$  and  $DB_0(B)$ , as shown below.

| D | Function                                                                                                                                                                                                                                  |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | Display On.                                                                                                                                                                                                                               |

| 0 | Display Off. In this mode, the display data remains in the DD RAM so that it is retrieved immediately on the display when the D change to 1.                                                                                              |

|   |                                                                                                                                                                                                                                           |

| C | Function                                                                                                                                                                                                                                  |

| 1 | Cursor On. The cursor is displayed by 5 dots on the 8th line.                                                                                                                                                                             |

| 0 | Cursor Off. Even if the display data write, the I/D etc does not change.                                                                                                                                                                  |

|   |                                                                                                                                                                                                                                           |

| В | Function                                                                                                                                                                                                                                  |

| 1 | The cursor position character is blinking. Blinking rate is 508.7ms at fos =290kHz. The blink is displayed alternatively with all on (it means al black) and characters display. The cursor and the blink can be displaye simultaneously. |

| n | The character does not blink.                                                                                                                                                                                                             |

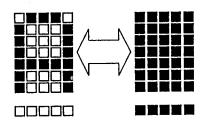

Character Font 5 x 7 dots

(1) Cursor display example

Alternating display

(2) Blink display example

#### (f) Cursor/Display Shift

|      | RS | R/W | DB <sub>7</sub> | DB6 | DB <sub>5</sub> | DB₄ | DΒ₃ | $DB_2$ | DB 1 | $DB_{o}$ |                |

|------|----|-----|-----------------|-----|-----------------|-----|-----|--------|------|----------|----------------|

| Code | 0  | 0   | 0               | 0   | 0               | 1   | S/C | R/L    | *    | *        | * = Don't care |

The Cursor/Display shift instruction shifts the cursor position or display to the right or left without writing or reading display data. This function is used to correct or search the display. In the 2-line display, the cursor moves to the 2nd line when it passes the 40th digit of the 1st line. Notice that the 1st and 2nd line displays will shift at the same time. When the displayed data is shifted repeatedly, each line moves only horizontally.

The 2nd line display does not shift into the 1st line position.

The contents of address counter(AC) does not change by operation of the display shift only. This instruction is executed when the code "1" is written into DB<sub>4</sub> and the codes of (S/C) and (R/L) are written into DB<sub>3</sub>(S/C) and DB<sub>2</sub>(R/L), as shown below.

| S/C | R/L         | Function                                                                                                                                                                                                                                                                |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0<br>1<br>0 | Shifts the cursor position to the left ((AC) is decremented by 1) Shifts the cursor position to the right ((AC) is incremented by 1) Shifts the entire display to the left and the cursor follows it. Shifts the entire display to the right and the cursor follows it. |

#### (g) Function Set

|      | RS | R/W | DB <sub>7</sub> | $DB^e$ | DB5 | DB₄ | $DB_3$ | DB <sub>2</sub> | DB 1 | $DB_{\rm o}$ |                |

|------|----|-----|-----------------|--------|-----|-----|--------|-----------------|------|--------------|----------------|

| Code | 0  | 0 - | 0               | 0      | 1   | DL  | N      | *               | *    | *            | * = Don't care |

Function set instruction which sets the interface data length and number of display lines, is executed when the code "1" is written into DB $_5$  and the codes of (DL) and (N) are written into DB $_4$ (DL) and DB $_3$ (N), as shown below (character font is fixed 5 x 7 dots).

(DL) sets the interface data length and (N) sets the number of display lines either the 1-line or 2-line.

This function set instruction must be performed at the head of the program prior to all other existing instructions(except Busy flag/Address read). This function set in-

struction can not be executed afterwards unless the interface data length change.

| DL | Function                                                                                                 |

|----|----------------------------------------------------------------------------------------------------------|

| 1  | Set the interface data length to 8-bit (DB7 to DB0)                                                      |

| 0  | Set the interface data length to 4-bit (DB, to DB, The data must be sent or received twice in this mode. |

| N | Display lines | Character Font | Duty ratio | Note |

|---|---------------|----------------|------------|------|

| 0 | 1             | 5 x 7 dots     | 1/16       |      |

| 1 | 2             | 5 x 7 dots     | 1/32       |      |

5

#### (h) Set CG RAM Address

Set CG RAM address set instruction is executed when the code "1" is written into  $DB_6$  and the address is written into  $DB_5$  to  $DB_0$  as shown above.

The address data mentioned by binary code "AAAAAA" is written into the address counter (AC) together with the CG RAM addressing condition. After this instruction execution, the data writing/reading is performed into/from the CG RAM.

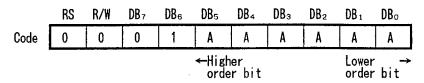

# (i) Set DD RAM Address

|      | RS | R/W | DB7 | DBe   | DB <sub>5</sub> | DB₄     | DВз | DB2   | DB 1 | DBo    | _ |

|------|----|-----|-----|-------|-----------------|---------|-----|-------|------|--------|---|

| Code | 0  | 0   | 1   | A     | A               | Α       | Α   | A     | A    | A      |   |

| '    |    |     |     | ←Higl | ner ord         | ler bit |     | Lower | orde | r bit→ |   |

Set DD RAM address instruction is executed when the code "1" is written into DB $_7$  and the address is written into DB $_6$  to DB $_0$  as shown above.

The address data mentioned by binary code "AAAAAAA " is written into the address counter (AC) together with the DD RAM addressing condition. After this instruction execution, the data writing/reading is performed into/from the DD RAM.

Note: In case of the 1-line display, the address data is (00)<sub>H</sub> to (4F)<sub>H</sub>, and during the 2-line display, the address is (00)<sub>H</sub> to (27)<sub>H</sub> for the 1st line and (40)<sub>H</sub> to (67)<sub>H</sub> for the 2nd line.

#### (j) Read Busy Flag & Address

|      | RS | R/W | DB7                                   | DBe  | DB5    | DB₄    | DВз | DB <sub>2</sub> | DB 1   | DBo    |          |

|------|----|-----|---------------------------------------|------|--------|--------|-----|-----------------|--------|--------|----------|

| Code | 0  | 1   | BF                                    | A    | A      | A      | Α   | A               | A      | A      | ]        |

|      |    |     | · · · · · · · · · · · · · · · · · · · | ←Hig | ner or | der bi | t   | Lower           | r orde | r bit→ | <u> </u> |

This instruction reads out the internal status of the NJU6423B. When this instruction is executed, the busy flag (BF) which indicate internal operation is read out from DB<sub>7</sub> and the address of the CG RAM or DD RAM is read out from DB<sub>6</sub> to DB<sub>0</sub> (the address for the CG RAM or DD RAM is determined by the previous instruction).

(BF)="1" indicates that internal operation is in progress. The next instruction is inhibited when (BF)="1". Check the (BF) status before the next write operation.

#### (k) Write Data to CG RAM or DD RAM

|      | RS | R/W | DB7   | DBe    | DB <sub>5</sub> | DB₄ | DВз | DB <sub>2</sub> | DB <sub>1</sub> | DBo    | _        |

|------|----|-----|-------|--------|-----------------|-----|-----|-----------------|-----------------|--------|----------|

| Code | 1  | 0   | D     | D      | D               | D   | D   | D               | D               | D      | ]        |

| '    |    |     | ←Higl | ner or | der bi          | t   |     | Lowe            | r orde          | r bit- | <b>-</b> |

Write Data to CG RAM or DD RAM instruction is executed when the code "1" is written into (RS) and code "0" is written into (R/W).

By the execution of this instruction, the binary 8 bit data DDDDDDDD are written into the CG RAM or DD RAM. The selection of the CG RAM or DD RAM is determined by the previous instruction. After this instruction execution, the address increment (+1) or decrement (-1) is performed automatically according to the entry mode set. And the display shift is also executed according to the previous entry mode set.

#### (1) Read Data from CG RAM or DD RAM

|      | RS | R/W | DB7  | $DB^e$ | DB5    | DB₄ | DВз | DB <sub>2</sub> | DB 1   | DBo    |

|------|----|-----|------|--------|--------|-----|-----|-----------------|--------|--------|

| Code | 1  | 1   | D    | D      | D      | D   | D   | D               | D      | D      |

|      |    |     | ←Hig | her or | der bi | t   |     | Lowe            | r orde | r bit→ |

Read Data from CG RAM or DD RAM instruction is executed when the code "1" is written into (RS) and (R/W).

By the execution of this instruction, the binary 8 bit data "DDDDDDDD" are read out from the CG RAM or DD RAM. The selection of the CG RAM or DD RAM is determined by the previous instruction.

Before executing this instruction, either the CG RAM address set or DD RAM address set must be executed, otherwise the first read out data are invalidated.

When this instruction is serially executed, the next address data is normally read from the second read.

The address set instruction is not required if the cursor shift instruction is executed just beforehand(only DD RAM reading).

The cursor shift instruction has same function as the DD RAM address set, so that after reading the DD RAM, the address increment or decrement is executed automatically according to the entry mode.

But display shift does not occur regardless of the entry mode.

Note: The address counter (AC) is automatically incremented or decremented by 1 after write instructions to either of the CG RAM or DD RAM. Even if the read instruction is executed after this instruction, the addressed data can not be read out correctly. For a correct data read out, either the address set instruction or cursor shift instruction (only with DD RAM) must be implemented just before this instruction or from the second time read out instruction execution if the read out instruction is executed 2 times consecutively.

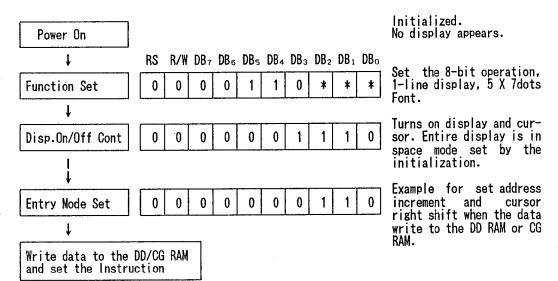

#### (3-2) Initialization using the internal reset circuits

(a) 20-character 1-line display in 8-bit operation (Using internal reset circuits).

At the 20-character 1-line display, the Function set, Display On/Off Control and Entry Set Instruction must be executed before the data input, as shown below.

The DD RAM of the NJU6423B can store up to 80 characters, as explained before, therefore the advertising moving display is available when combined with the display shift operation. Since the display shift operation changes only display position and the DD RAM contents remain unchanged, display data which are entered first can be output when the return home operation is performed.

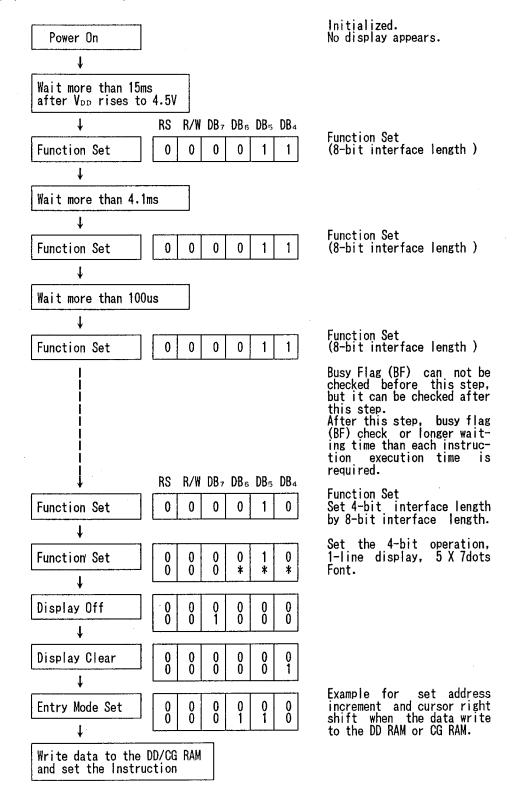

(b) 20-character 1-line in 4-bit operation (Using internal reset circuits).

In the 4-bit operation, the function set must be performed by the user programming.

When the power is turned on, 8-bit operation is selected automatically, therefore the first input is performed under 8-bit operation. In this operation, full instruction can not input because of terminals  $DB_0$  to  $DB_3$  are no connection. Therefore, same instruction must be rewritten on the RS, R/W and  $DB_7$  to  $DB_4$ , as shown below. Since one operation is completed by the two accesses in the 4-bit operation mode, rewrite is required to set the instruction code in full.

20-character 1-line in 4-bit operation is shown as follows:

Power On

Initialized. No display appears.

Set the 4-bit operation. This step is executed in 8-bit mode set by the initialization.

Set the 4-bit operation, 1-line display, 5 X 7dots Font. The 4-bit operation starts from this step.

Turn on display and cursor. Entire display is in space mode set by the initialization.

Example for set address increment and cursor right shift when the data write to the DD RAM or CG RAM.

(c) 20-character 2-line in 8-bit operation (Using internal reset circuits).

In the 2-line display, the cursor moves automatically from the 1st to the 2nd line after the 40th character of the first line has been written. Therefore, if the display character is only 20 characters in the 1st line, the DD RAM address must be set by the user programing to change the cursor position to the 2nd line.

The 1st and 2nd line displays will shift at the same time.

When the displayed data is shifted repeatedly, each line moves only horizontally. The 2nd line display does not shift into the 1st line position.

5

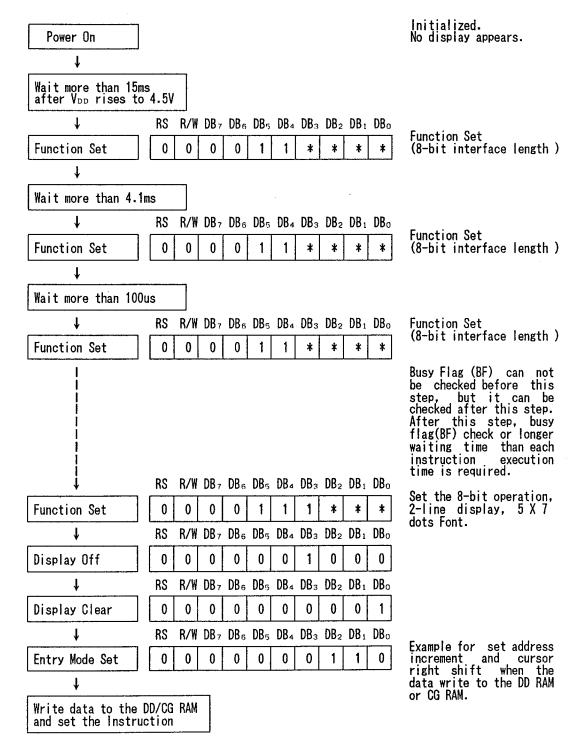

#### (3-3) Initialization by instruction

If the power supply conditions for the correct operation of the internal reset circuits are not met, the NJU6423B must be initialized by the instruction.

(a) Initialization by Instruction in 8-bit interface length.

### (b) Initialization by Instruction in 4-bit interface length

#### (4) LCD DISPLAY

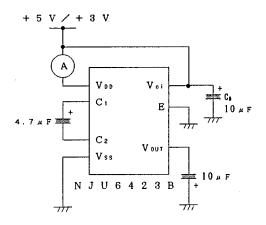

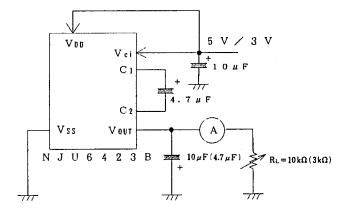

#### (4-1) Power Supply for LCD Driving

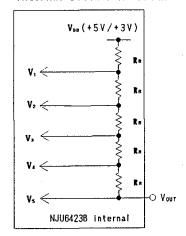

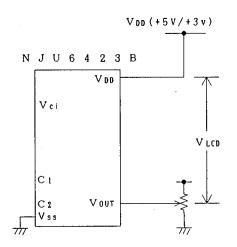

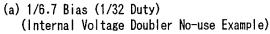

NJU6423B incorporate voltage doubler to generate LCD driving high voltage and bleeder resistance. The voltage doubler generate about twofold voltage from the  $V_{\text{c}i}$  input voltage. ( 9.5V typ at lout=2mA and  $V_{\text{c}i}$ =5V ) and bleeder resistance generate each LCD driving voltage. The bleeder resistance is set 1/6.7 bias suitable for 1/32 duty ratio and each resistance value are 1k $\Omega$  typ for  $R_1$ ,  $R_2$ ,  $R_4$  and  $R_5$ , and 2.7k $\Omega$  typ for  $R_3$ .

LCD Driving Voltage vs Duty Ratio

| Power supply | Duty Ratio | 1/32        |

|--------------|------------|-------------|

| Supply       | Bias       | 1/6.7       |

| v            | LCD        | VDD to VOUT |

#### Internal Bleeder Resistance

(b) 1/6.7 Bias (1/32 Duty)

(Internal Voltage Doubler Using Example)

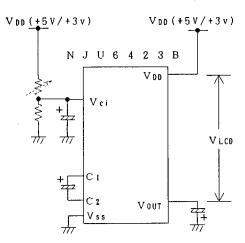

# (4-2) Relation between oscillation frequency and LCD frame frequency.

As the NJU6423B incorporate oscillation capacitor and resistance for CR oscillation, 290kHz oscillation is available without any external components.

The LCD frame frequency example mentioned below is based on 290kHz oscillation.

$(1 \operatorname{clock} = 3.4 \operatorname{us})$

### (a) 1/32 duty

1 frame =  $3.4(us) \times 100 \times 32 = 10.880(us) = 10.9(ms)$ Frame frequency = 1/10.9(ms) = 91.7(Hz)

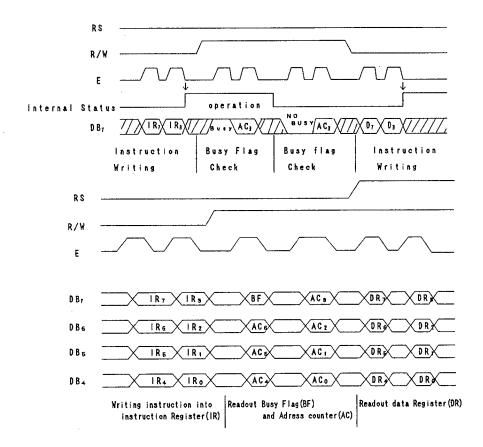

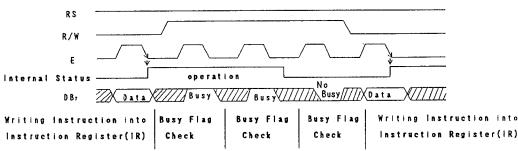

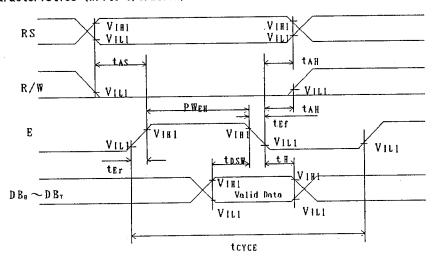

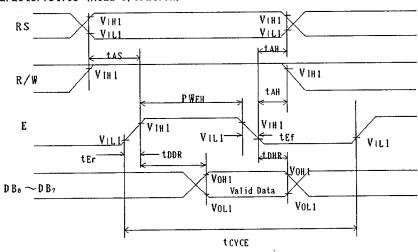

#### (5) Interface with MPU

NJU6423B can be interfaced with both of 4/8 bit MPU and the two-time 4-bit or one-time 8-bit data transfer is available.

#### (5-1) 4-bit MPU interface

When the interface length is 4-bit, the data transfer is performed by 4 lines connected to  $DB_4$  to  $DB_7$  ( $DB_0$  to  $DB_3$  are not used). The data transfer with the MPU is completed by the two-time 4-bit data transfer.

The data transfer is executed in the sequence of upper 4-bit (the data DB<sub>4</sub> to DB<sub>7</sub> at 8-bit length) and lower 4-bit (the data DB<sub>0</sub> to DB<sub>3</sub> at 8-bit length).

The busy flag check must be executed after two-time 4-bit data transfer (1 instruction execution). In this case the data of busy flag and address counter are also output twice.

# (5-2) 8-bit MPU interface

#### ■ ABSOLUTE MAXIMUM RATINGS

( Ta=25℃ )

| PARAMETER             | SYMBOL          | RATINGS                      | UNIT |

|-----------------------|-----------------|------------------------------|------|

| Supply Voltage (1)    | V <sub>DD</sub> | - 0.3 ~ + 7.0                | ٧    |

| Input Voltage         | Vr              | - 0.3 ~ V <sub>DD</sub> +0.3 | ٧    |

| Operating Temperature | Topr            | - 30 ~ + 80                  | °C   |

| Storage Temperature   | Tstg            | - 55 ~ + 125                 | င    |

Note 1) If the LSI are used on condition above the absolute maximum ratings, the LSI may be destroyed.

Using the LSI within electrical characteristics is strongly recommended for normal

Use beyond the electric characteristics conditions will cause malfunction and poor reliability.

Note 2) All voltage values are specified as  $V_{ss} = 0 \text{ V}$

Note 3) The relation :  $V_{DD} \ge V_{ci} > V_{OUT}$ ,  $V_{DD} > V_{SS} \ge V_{OUT}$ ,  $V_{SS} = 0V$  must be maintained.

Note 4) Decoupling capacitor (C<sub>D</sub>) should be connected between V<sub>c1</sub> and V<sub>ss</sub> due to the stabilized operation for the voltage doubler.

#### ■ ELECTRICAL CHARACTERISTICS

(  $V_{\text{DD}}=5V\pm10\%$  ,  $Ta=-20\sim+75\%$  )

| PARA      | METE         | R     | SYMBOL                                                             | CONDITIONS                                                      | MIN  | TYP               | MAX                   | UNIT | NOTE |

|-----------|--------------|-------|--------------------------------------------------------------------|-----------------------------------------------------------------|------|-------------------|-----------------------|------|------|

| Operating | Voltage      |       | <b>V</b> <sub>DD</sub>                                             |                                                                 | 4.5  | 5.0               | 5.5                   | ٧    |      |

| Input Vol | tage         |       | V <sub>1H1</sub>                                                   | All Input and Input/Output<br>Terminals except OSC<br>Terminals | 2.3  |                   | V <sub>DD</sub> 0.8   | ٧    | 5    |

| Output Vo | Itage        |       | V <sub>OH1</sub>                                                   | Input/Output -loH=0.205mA<br>Terminals   OL=1.6mA               | 2.4  |                   | 0.4                   | ٧    | 6    |

| Driver On |              |       | Rсом                                                               | ±ld=0.05mA(All com.term.)                                       |      |                   | 20                    | kΩ   | 7    |

| Driver On |              |       | Rseg                                                               | ±ld=0.05mA(All seg.term.)                                       | ļ    |                   | 30                    |      |      |

| Input Lea |              |       | ILI                                                                | V <sub>IN</sub> =0 ~ V <sub>DD</sub>                            | - 1  |                   | 1                     | uA   | 8    |

| Pull-up R | esist Cu     | rrent | -  <sub>P</sub>                                                    | V <sub>DD</sub> =5V, RS, R/W, DB                                | 50   | 125               | 250                   |      |      |

| Operating | Current      |       | DD1<br>DD2                                                         | V <sub>DD</sub> =5V NJU6423B NJU6423BL 内蔵CR発振 NJU6423BS         |      | 1.9<br>1.2<br>0.8 | 3.3<br>2.1<br>1.5     | mA   | 9    |

|           | Output Volt. |       | Vup                                                                | Vci=5V, Ta=25°C, Voue                                           | -4.0 | -4.6              |                       | V    | 10   |

| Vol tage  | Conv.Ef      |       | Ver                                                                | R <sub>L</sub> =∞                                               | 95   | 99.9              |                       | %    |      |

| Doubler   | Input V      |       | Vci                                                                |                                                                 | 2.5  |                   | 5.5                   | ٧    |      |

|           |              | В     | R <sub>1</sub> , R <sub>2</sub><br>R <sub>4</sub> , R <sub>5</sub> | Ta=25℃                                                          |      | 1.00              |                       |      |      |

| Built-in  | Bleeder      |       | Rэ                                                                 |                                                                 |      | 2.70              |                       |      |      |

| res       | istance      | ВL    | B <sub>1</sub> , B <sub>2</sub><br>R <sub>4</sub> , R <sub>5</sub> | Ta=25℃                                                          |      | 2.00              |                       | kΩ   |      |

| (For LCD  | Driving      |       | Rз                                                                 |                                                                 |      | 5.40              |                       |      |      |

| V         | oltage)      | BS    | R <sub>1</sub> , R <sub>2</sub><br>R <sub>4</sub> , R <sub>5</sub> | Ta=25℃                                                          |      | 4.00              |                       |      |      |

|           |              |       | Rз                                                                 |                                                                 |      | 10.80             |                       |      |      |

| Oscillati | on Frequ     | ency  | fosc                                                               | V <sub>DD</sub> =5V, Ta=25℃                                     | 190  | 290               | 350                   | kHz  | 11   |

| LCD Drivi | ng Volta     | ge    | VLCD                                                               | V <sub>DD</sub> - V <sub>5</sub> 1/6.7 Bias                     | 0    |                   | V <sub>DD</sub> -13.5 | ٧    | 12   |

# **■** ELECTRICAL CHARACTERISTICS

(  $V_{\text{DD}}\text{=}3V\pm20\%$  , Ta=-20  $\sim$  +75°C )

| PARA      | METE     | R     | SYMBOL                                                             | CONDI                               | TIONS                      | MIN                | ТҮР      | MAX                     | UNIT                                  | NOTE  |

|-----------|----------|-------|--------------------------------------------------------------------|-------------------------------------|----------------------------|--------------------|----------|-------------------------|---------------------------------------|-------|

| Operating | Voltage  |       | <b>V</b> <sub>DD</sub>                                             |                                     |                            | 2.4                | 3.0      | 3.6                     | V                                     |       |

|           |          |       | V <sub>1H1</sub>                                                   | All Input an                        | d Input/Output             | 0.8V <sub>DD</sub> |          | VDD                     | v                                     | 5     |

| Input Vol | tage     | 1     | Vili                                                               | lerminals ex<br>Terminals           | d Input/Output<br>cept OSC |                    |          | 0.2                     | ٧                                     | 5     |

| 0 1 1 1   |          |       | V <sub>OH1</sub>                                                   | Input/Output<br>Terminals           | -lон=0.205mA               | 2.0                |          |                         | v                                     | 6     |

| Output Vo | ITage    |       | Voli                                                               | lerminais                           | lor=1.6mA                  |                    |          | 0.5                     | ٧                                     | U     |

| Driver On | -resist. | (COM) | Rсом                                                               | ±1d=0.05mA(                         | All com.term.)             |                    |          | 20                      | kΩ                                    | 7     |

| Driver On | -resist. | (SEG) | Rsec                                                               | ±1d=0.05mA(                         | Ali seg.term.)             |                    |          | 30                      | K 75                                  | ,<br> |

| Input Lea | kage Cur | rent  | Li                                                                 | $V_{IN}=0 \sim V_{DD}$              |                            | - 1                |          | 1                       | uА                                    | 8     |

| Pull-up R | esist Cu | rrent | -  P                                                               | V <sub>DD</sub> =3V, RS,            | R/W, DB                    | 10                 | 25       | 50                      | un                                    |       |

|           |          |       | וממ                                                                | V <sub>DD</sub> =5V                 | NJU6423B                   |                    | 0.75     | 2.0<br>1.3              | 4                                     |       |

| Operating | Current  |       | DD2<br>  DD3                                                       | <br>  内蔵CR発振                        | NJU6423BL<br>NJU6423BS     |                    | 0.5<br>* | 1.3                     | mA                                    | 9     |

|           | Output   | Vol+  | Vup                                                                | Vci=3V. Ta=2                        |                            | -2.4               | -2.8     |                         | ٧                                     | 10    |

| Voltage   | Conv. E  |       | Vup                                                                | $R_{t}=\infty$                      | JO, Yout                   | 95                 | 99.9     |                         | %                                     | 10    |

| Doubler   |          |       |                                                                    | ur-m                                |                            | 1.8                | 33.3     | V <sub>DD</sub>         | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |       |

|           | Input V  | oit.  | Vei                                                                | T -05°0                             |                            | 1.0                | 1.00     | <b>V</b> DD             |                                       |       |

|           |          | В     | R <sub>1</sub> , R <sub>2</sub><br>R <sub>4</sub> , R <sub>5</sub> | Ta=25°C                             |                            |                    | 1.00     |                         |                                       |       |

| Built-in  | Bleeder  |       | Rз                                                                 |                                     |                            |                    | 2.70     |                         |                                       |       |

| res       | istance  | ВL    | R <sub>1</sub> , R <sub>2</sub><br>R <sub>4</sub> , R <sub>5</sub> | Ta=25°C                             |                            |                    | 2.00     |                         | kΩ                                    |       |

| (For LCD  | Driving  |       | Rз                                                                 |                                     |                            |                    | 5.40     |                         |                                       |       |

| V         | ol tage) | BS    | B <sub>1</sub> , B <sub>2</sub><br>R <sub>4</sub> , R <sub>5</sub> | Ta=25℃                              |                            |                    | 4.00     |                         |                                       |       |

|           |          |       | Rз                                                                 |                                     |                            |                    | 10.80    |                         |                                       |       |

| Oscillati | on Frequ | ency  | fosc                                                               | V <sub>DD</sub> =3V, Ta=2           | .5℃                        | 160                | 260      | 320                     | kHz                                   | 11    |

| LCD Drivi | ng Volta | ge    | VLCD                                                               | V <sub>DD</sub> - V <sub>5</sub> 1/ | 6.7 Bias                   | 0                  |          | V <sub>DD</sub><br>-7.0 | ٧                                     | 12    |

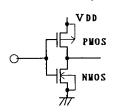

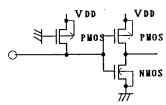

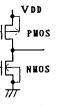

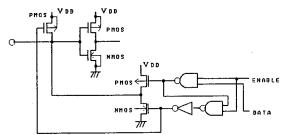

Note 5) Input/Output structure except LCD driver are shown below:

Input Terminal Structure

E Terminal

RS, R/W Terminal

Input/Output Terminal Structure

DBo to DB7 Terminal

- Note 6) Apply to the Output and Input/Output Terminal.

- Note 7)  $R_{COM}$  and  $R_{SEG}$  are the resistance values between power supply terminals( $V_{DD}$ ,  $V_1$ ,  $V_4$ ,  $V_5$ ) and each common terminal ( $COM_1$  to  $COM_{32}$ ), and supply voltage ( $V_{DD}$ ,  $V_2$ ,  $V_3$ ,  $V_5$ ) and each segment terminal( $SEG_1$  to  $SEG_{50}$ ) respectively, and measured when the current ld is flown on every common and segment terminals at a same time.

- Note 8) Except pull-up resistance current and output driver current.

- Note 9) Except Input/output current but including the current flow on bleeder resistance.

If the input level is medium, current consumption will increase due to the penetration current. Therefore, the input level must be fixed to "H" or "L".

Note 10) Voltage Doubler Characteristics Measuring Circuit.

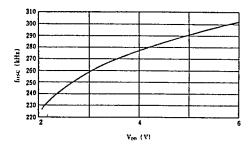

Note 11) Supply Voltage vs Oscillating Frequency