# 16-BIT CMOS MICROPROCESSOR SLICE

IDT 49C402 **IDT 49C402A IDT 49C402B**

MICROSLICE™ PRODUCT

# **FEATURES:**

- Functionally equivalent to four 2901s and one 2902

- IDT49C402B 55% faster than four 2901Cs and one 2902A

- Expanded two-address architecture with independent, simultaneous access to two 64 x 16 register files

- Expanded destination functions with 8 new operations allowing Direct Data to be loaded directly into the dual-port RAM and Q

- Clamp diodes on all inputs provide noise suppression

- Fully cascadable

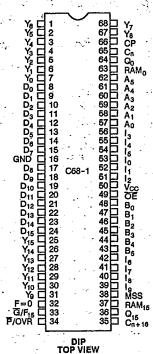

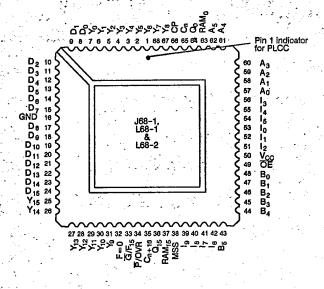

- 68-pin plastic and ceramic PGA, Shrink-DIP (600 mil, 70 mil centers), LCC (25 and 50 mil centers) and Ceramic Quad Flatpack

- Military product compliant to MIL-STD-883, Class B

# **DESCRIPTION:**

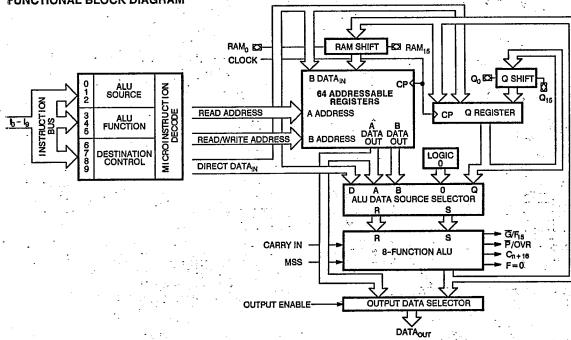

The IDT49C402s are high-speed, fully cascadable 16-bit CMOS microprocessor slice units which combine the standard functions of four 2901s and a 2902 with additional control features aimed at enhancing the performance of bit-slice microprocessor designs.

The IDT49C402s include all of the normal functions associated with standard 2901 bit-slice operation: (a) a 3-bit instruction field (lo, I, I<sub>2</sub>) which controls the source operand selection for the ALU; (b) a 3-bit microinstruction field (I<sub>3</sub>, I<sub>4</sub>, I<sub>5</sub>) used to control the eight possible functions of the ALU; (c) eight destination control functions which are selected by the microcode inputs (I<sub>6</sub>, I<sub>7</sub>, I<sub>9</sub>); and (d) a tenth microinstruction input, is, offering eight additional destination control functions. This is input, in conjunction with is, it and is, allows for shifting the Q Register up and down, loading the RAM or Q Register directly from the D inputs without going through the ALU and new combinations of destination functions with the RAM A port output available at the Y output pins of the device.

Also featured is an on-chip dual-port RAM that contains 64 words

by 16 bits—four times the number of working registers in a 2901. The IDT49C402s are fabricated using CEMOS, a CMOS technology designed for high performance and high reliability. These performance enhanced devices feature both bipolar speed and bipolar output drive capabilities while maintaining exceptional microinstruction speeds at greatly reduced CMOS power levels.

CEMOS and MICROSLICE are trademarks of Integrated Device Technology, Inc.

MILITARY AND COMMERCIAL TEMPERATURE RANGES

1989 Integrated Device Technology, Inc.

S8-1

MILITARY AND COMMERCIAL TEMPERATURE RANGES

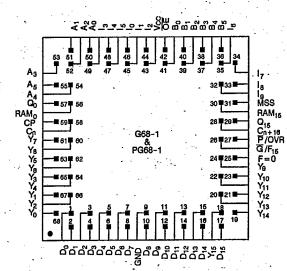

# PIN CONFIGURATIONS

60 59 58 57 58 55 54 53 52 61 50 48 47 48 45 44

PIN 1 IDENTIFICATION

CERQUAD TOP VIEW

S8-2

MILITARY AND COMMERCIAL TEMPERATURE RANGES

# T-49-17-51

# PIN DESCRIPTIONS

| . PIN NAME                           | 1/0     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> -A <sub>5</sub>       | . 1     | Six address inputs to the register file which selects one register and displays its contents through the A port.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| B <sub>0</sub> -B <sub>5</sub>       | 1       | Six address inputs to the register file which selects one of the registers in the file, the contents of which is displayed through the B port. It also selects the location into which new data can be written when the clock goes LOW.                                                                                                                                                                                                                                                                                                     |

| I <sub>0</sub> -I <sub>9</sub>       | .       | Ten instruction control lines which determine what data source will be applied to the ALU I (0, 1, 2), what function the ALU will perform I(3, 4, 5) and what data is to be deposited in the Q Register or the register file I (6, 7, 8, 9). Original 2901 destinations are selected if I g is disconnected. In this mode, proper I g blas is controlled by an internal pullup resistor to V <sub>CC</sub> .                                                                                                                                |

| D <sub>0</sub> -D <sub>15</sub>      | 1       | Sixteen-bit direct data inputs which are the data source for entering external data into the device ALU, $\Omega$ Register or RAM. $D_0$ is the LSB.                                                                                                                                                                                                                                                                                                                                                                                        |

| Y <sub>0</sub> -Y <sub>15</sub>      | Ò       | Sixteen three-state output lines which, when enabled, display either the sixteen outputs of the ALU or the data on the A port of the register stack. This is determined by the destination code I(8, 7, 8, 9).                                                                                                                                                                                                                                                                                                                              |

| ਰ/F <sub>15</sub>                    | 0       | A multipurpose pin which indicates the carry generate $(\overline{Q})$ function at the least significant and intermediate slices or as $F_{15}$ the most significant ALU output (sign bit). $\overline{G}/F_{15}$ selection is controlled by the MSS pin. If MSS $\Rightarrow$ HIGH, $F_{16}$ is enabled. If MSS $\Rightarrow$ LOW, $\overline{G}$ is enabled.                                                                                                                                                                              |

| F = 0                                | O       | Open drain output which goes HIGH if the F <sub>0</sub> -F <sub>15</sub> ALU outputs are all LOW. This indicates that the result of an ALU operation is zero (positive logic).                                                                                                                                                                                                                                                                                                                                                              |

| Cn .                                 | -1      | Carry-in to the Internal ALU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Cn+16                                | 0       | Carry-out of the internal ALU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Q <sub>15</sub><br>RAM <sub>15</sub> | 1/0     | Bidirectional lines controlled by I <sub>(0, 7, 6, 9)</sub> . Both are three-state output drivers connected to the TTL-compatible inputs. When the destination code on I <sub>(0, 7, 8, 9)</sub> indicates an up shift, the three-state outputs are enabled, the MSB of the O Register Is available on the Q <sub>15</sub> pin and the MSB of the ALU output is available on the RAM <sub>15</sub> pin. When the destination code indicates a down shift, the pins are the data inputs to the MSB of the Q Register and the MSB of the RAM. |

| Q <sub>0</sub><br>RAM <sub>0</sub>   | .1/0    | Both bidirectional lines function identically to Q <sub>15</sub> and RAM <sub>15</sub> lines except they are the LSB of the Q Register and RAM.                                                                                                                                                                                                                                                                                                                                                                                             |

| OE                                   | I       | Output enable. When pulled HIGH, the Youtputs are OFF (high impedance). When pulled LOW, the Youtputs are enabled.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P/OVR                                | 0       | A multipurpose pin which indicates the carry propagate (P) output for performing a carry lookahead operation or overflow (OVR) the Exclusive-OR of the carry-in and carry-out of the ALU MSB. OVR, at the most significant end of the word, indicates that the result of an arithmetic two's complement operation has overflowed into the sign bit. P/OVR selection is controlled by the MSS pin. If MSS = HIGH, OVR is enabled. If MSS = LOW, P is enabled.                                                                                |

| CP                                   | ı<br>.: | The clock input. LOW-to-HIGH clock transitions will change the Q Register and the register file outputs, Clock LOW time is internally the write enable time for the 64 x 16 RAM which compromises the master latches of the register file. While the clock is LOW, the slave latches on the RAM outputs are closed, storing the data previously on the RAM outputs. Synchronous MASTER-SLAVE operation of the register file is achieved by this.                                                                                            |

| MSS                                  | ı       | When HIGH, enables OVR and $F_{15}$ on the $\overline{F}/OVR$ and $\overline{G}/F_{15}$ pins. When LOW, enables $\overline{G}$ and $\overline{F}$ on these pins. If left open internal pullup resistor to $V_{CC}$ provides declaration that the device is the most significant slice.                                                                                                                                                                                                                                                      |

tem ber beking a train.

# **DEVICE ARCHITECTURE:**

The IDT49C402 CMOS bit-silice microprocessor is configured sixteen bits wide and is cascadable to any number of bits (16, 32, 48, 64). Key elements which make up this 16-bit microprocessor slice are the (1) register file (64 x 16 dual-port RAM) with shifter, (2) ALU and (3) O Register and shifter.

and (3) Q Register and shifter.

REGISTER FILE—A 16-bit data word from one of the 64 RAM registers can be read from the A port as selected by the 6-bit A address field. Simultaneously, the same data word, or any other word from the 64 RAM registers, can be read from the B port as selected by the 6-bit B address field. New data is written into the RAM register location selected by the B address field during the clock (CP) LOW time. Two sixteen-bit latches hold the RAM A port and B port during the clock (CP) LOW time, eliminating any data races. During clock HIGH these latches are transparent, reading the data selected by the A and B addresses. The RAM data input field is driven from a four-input multiplexer that selects the ALU output or the D inputs. The ALU output can be shifted up one position, down one position or not shifted. Shifting data operations involve the RAM<sub>15</sub> and RAM<sub>0</sub> I/O pins. For a shift up operation, the RAM shifter MSB is connected to an enabled RAM<sub>15</sub> I/O output while the RAM<sub>0</sub> I/O input is selected as the input to the LSB. During a shift down operation, the RAM shifter LSB is connected to an enabled RAM<sub>0</sub> I/O output while the RAM<sub>15</sub> I/O input is selected as the input to the MSB.

ALU — The ALU can perform three binary arithmetic and five logic operations on the two 16-bit Input words S and R. The S input field is driven from a 3-input multiplexer and the R input field is driven from a 2-input multiplexer with both having a zero source operand. Both multiplexers are controlled by the  $I_{(0,1,2)}$  inputs. This multiplexer configuration enables the user to select various pairs of the A, B, D, Q and "0" inputs as source operands to the ALU. Microinstruction inputs  $I_{(0,4,5)}$  are used to select the ALU function. This high-speed ALU cascades to any word length, providing carry-in  $(C_n)$ , carry-out  $(C_{n+10})$  and an open-drain (F=0) output. When all bits of the ALU are zero, the pull-down device of F=0 is off, allowing a wire-OR of this pin over all cascaded devices. Multipurpose pins  $\overline{G}/F_{16}$  and  $\overline{P}/OVR$  are aimed at accelerating arithmetic operations. For intermediate and least significant slices, the MSS pin is programmed LOW, selecting the carry-generate  $(\overline{G})$  and carry-propagate  $(\overline{P})$  output functions to be used by carry lookahead logic. For the most significant slice, MSS is programmed high, selecting the sign-bit  $(F_{15})$  and the two's complement overflow (OVR) output functions. The sign bit  $(F_{15})$  allows the ALU sign bit to be monitored without enabling the three-state ALU outputs. The overflow (OVR) output is high when the two's complement arithmetic operation has overflowed into the sign bit as logically determined from the Exclusive-OR of the carry-in and carry-out of the most significant bit of the ALU. The ALU data outputs are available at the three-state outputs  $V_{(0-16)}$  or as

MILITARY AND COMMERCIAL TEMPERATURE RANGES T-49-17-51

inputs to the RAM register file and Q Register under control of the I(8, 7, 8, 9) instruction inputs.

two ports,  $Q_0$  and  $Q_{15}$ , which operate comparably to the RAM shifter.

I(6,7,6,9) Instruction inputs.

Q REGISTER—The Q Register is a separate 16-bit file intended for multiplication and division routines and can also be used as an accumulator or holding register for other types of applications. It is driven from a 4-input multiplexer. In the no-shift mode, the multiplexer enters the ALU F output or Direct Data into the Q Register. In either the shift up or shift down mode, the multiplexer selects the Q Register data appropriately shifted up or down. The Q shifter has Register data appropriately shifted up or down. The Q shifter has

two ports,  $Q_0$  and  $Q_{15}$ , which operate comparably to the HAM shifter. They are controlled by the  $I_{(6,7,8,9)}$  inputs.

The clock input of the IDT49C402 controls the RAM, Q Register and A and B data latches. When enabled, the data is clocked into the Q Register on the LOW-to-HIGH transition. When the clock is HIGH, the A and B latches are open and pass data that is present at the RAM outputs. When the clock is LOW, the latches are closed and retain the last data entered. When the clock is LOW and  $I_{(6,7,8,9)}$  define the RAM as the destination, new data will be written into the RAM like defined by the B address field. file defined by the B address field.

# **ALU SOURCE OPERAND CONTROL**

|          |                | WIC            | ROCOD | E             | ALU SO<br>OPER | OURCE<br>ANDS |

|----------|----------------|----------------|-------|---------------|----------------|---------------|

| MNEMONIC | l <sub>2</sub> | l <sub>1</sub> | · Io  | OCTAL<br>CODE | R              | S             |

| AQ       | Ţ.             | L              | L     | 0             | Α              | Q             |

| AB       | F.             | L              | H     | 1             | Α              | В             |

| ZQ       | L H            |                | L     | 2             | . 0            | Q             |

| ZB       | L              | H.             | н     | 3.            | Ò              | В             |

| ZA       | Н.             | L              | L     | 4             | 0              | A             |

| DA       | Н              | L              | ٠н    | 5             | Ď              | . A           |

| DQ       | н              | н              | L     | 6             | D              | ٥             |

| DZ       | Н              | Н              | Н     | 7             | D              | 0             |

# **ALU FUNCTION CONTROL**

|          |   | MIC | ROC           | ODE      | ALU        |              |

|----------|---|-----|---------------|----------|------------|--------------|

| MNEMONIC |   |     | OCTAL<br>CODE | FUNCTION | SYMBOL     |              |

| ADD      | L | L   | L             | 0        | R Plus S   | R + S        |

| SUBR     | L | L   | н             | 1        | S Minus R  | S - R        |

| SUBS     | L | н   | L             | 2        | R Minus S  | R - S        |

| OR       | L | н   | н             | <b>3</b> | RORS       | RVS          |

| AND      | Н | L   | Ĺ             | 4        | RANDS      | RAS          |

| NOTES    | н | L   | Н             | 5        | RANDS      | Ñ۸S          |

| EXOR     | н | н   | L             | 6        | R EX-OR S  | R∕VS         |

| EXNOR    | н | н   | н             | 7        | R EX-NOR S | R <b>∕</b> S |

# **ALU ARITHMETIC MODE FUNCTIONS**

wnloaded from Elcodis.com electronic components distributor

| ALU A                           | 10111                                |                         | ODE FUN                                                                                              |                         |                                                  |

|---------------------------------|--------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------|-------------------------|--------------------------------------------------|

| ОСТ                             | 'AL                                  | C <sub>n</sub> =        | : L                                                                                                  | C <sub>n</sub>          | = H                                              |

| 15, 4, 3,                       |                                      | GROUP                   | FUNCTION                                                                                             | GROUP                   | FUNCTION                                         |

| 0 0                             | 0<br>1<br>5<br>6                     | ADD                     | A + Q<br>A + B<br>D + A<br>D + Q                                                                     | ADD<br>plus one         | A + Q + 1<br>A + B + 1<br>D + A + 1<br>D + Q + 1 |

| 0 0 0                           | 2<br>3<br>4<br>7                     | PASS                    | OB 4 D                                                                                               | Increment               | Q + 1<br>B + 1<br>A + 1<br>D + 1                 |

| 1 1 1 2                         | 2<br>3<br>4<br>7                     | Decrement               | Q - 1<br>B - 1<br>A - 1<br>D - 1                                                                     | PASS                    | QB & D                                           |

| 2<br>2<br>2<br>1                | 2<br>3<br>4<br>7                     | 1's Comp.               | -Q - 1<br>-B - 1<br>-A - 1<br>-D - 1                                                                 | 2's Comp.<br>(Negate)   | 9840                                             |

| 1<br>1<br>1<br>2<br>2<br>2<br>2 | 0<br>1<br>5<br>6<br>0<br>1<br>5<br>6 | Subtract<br>(1's Comp.) | Q - A - 1<br>B - A - 1<br>A - D - 1<br>Q - D - 1<br>A - Q - 1<br>A - B - 1<br>D - A - 1<br>D - Q - 1 | Subtract<br>(2's Comp.) | Q B A Q Q A A D D                                |

# ALU LOGIC MODE FUNCTIONS

| OCT.             | AL .                          | GROUP  | FUNCTION                         |

|------------------|-------------------------------|--------|----------------------------------|

| 15, 4, 3,        | 1 <sub>2, 1, 0</sub>          | GROUP  |                                  |

| 4<br>4<br>4<br>4 | 0<br>1<br>5<br>6              | AND    | AAQ<br>AAB<br>DAA<br>DAQ         |

| 3<br>3<br>3<br>3 | 0<br>1<br>5<br>6              | OR     | AVQ<br>AVB<br>DVA<br>DVQ         |

| 6<br>6<br>6      | 0<br>1<br>5<br>6              | EX-OR  | A ଫ G<br>A ଫ B<br>D ଫ A<br>D ଫ G |

| 7<br>7<br>7<br>7 | 0<br>1<br>5<br>6              | EX-NOR | ΑΦΒ<br>ΔΦΑ<br>ΔΦΟ<br>ΔΦΟ         |

| 7<br>7<br>7<br>7 | 2<br>3<br>4<br>7              | INVERT | IGI⊠I≺ID                         |

| 6<br>6<br>6      | 2<br>3<br>4<br>7              | PASS   | Q<br>B<br>A<br>D                 |

| 3<br>3<br>3<br>3 | 2<br>3<br>4<br>7              | PASS   | <b>G</b><br>В<br>А<br>D          |

| 4<br>4<br>4<br>4 | 2 <sup>°</sup><br>3<br>4<br>7 | "ZERO" | 0<br>0<br>0<br>0                 |

| 5<br>5<br>5      | 0<br>1<br>5<br>6              | MASK   | Ā A Q<br>Ā A B<br>D A A<br>D A Q |

MILITARY AND COMMERCIAL TEMPERATURE RANGES

T-49-17-51

|          |                                  | İ         |           | 1.5    | 12, 1, 0 | OCTAL  |       | 3.50  |       |

|----------|----------------------------------|-----------|-----------|--------|----------|--------|-------|-------|-------|

| OCTAL    | ALU                              | 0         | 1         | 2      | 3        | . 4    | . 5   | 6     | 7     |

| 15, 4, 3 | FUNCTION                         | • :       |           |        | ALU SOUR | CE     |       | - :   |       |

|          | •                                | A, Q      | A, B      | 0, Q   | 0, B     | 0, A   | D, A  | D, Q  | D, 0  |

| 0        | C <sub>n</sub> = L<br>R Plus S   | A + Q     | A + B     | o      | В.       | A      | D + A | D + Q | D     |

|          | $C_n = H$                        | A + Q + 1 | A + B + 1 | Q + 1· | B + 1    | A + 1, | D+A+1 | D+Q+1 | D+1   |

| 1        | C <sub>n</sub> = L<br>S Minus R  | Q-A-1     | B-A-1     | Q-1    | B-1      | A-1    | A-D-1 | Q-D-1 | -D -  |

| ٠        | C <sub>n</sub> = H               | Q-A       | B-A       | Q      | В        | A      | A-D   | O-D   | D     |

| 2        | C <sub>rr</sub> = L<br>R Minus S | A-Q-1     | A-B-1     | -Q - 1 | -B - 1   | -A - 1 | D-A-1 | D-Q-1 | D - 1 |

| -        | C <sub>n</sub> = H               | A-Q       | A - B     | -Q     | В        | -À     | D-A   | D-Q   | D     |

| 3        | RORS                             | AVQ       | AVB       | Q      | В        | A      | DVA   | DVQ   | D     |

| 4        | R AND S                          | AAQ       | АЛВ       | 0      | . 0      | 0      | DAA   | DAG   | 0     |

| 5        | R AND S                          | ÃΛQ       | Ā٨B       | Q      | В        | Α      | ÐΛΑ   | Ē٨Q   | -0    |

| 6        | R EX-OR S                        | A∕PQ      | A∜B       | Q      | В        | ·A     | D∕PA  | DTQ   | D     |

| 7        | R EX-NOR S                       | ĀŶQ       | ĀŶB       | ō      | B        | Ā      | DŶĀ   | D∕₽Q  | Ď     |

NOTE:

1. += Plus; - = Minus; A = AND; **1** = EX-OR; V = OR

# **ALU DESTINATION CONTROL®**

|          |                | N  | IICRO | COE | E           | FUNC  | AM<br>OTION |       | GISTER<br>CTION | γ      |                  | AM<br>FTER        | SHI            | TER              |                        |

|----------|----------------|----|-------|-----|-------------|-------|-------------|-------|-----------------|--------|------------------|-------------------|----------------|------------------|------------------------|

| MNEMONIC | l <sub>9</sub> | 1, | 17    | 18  | HEX<br>CODE | SHIFT | LOAD        | SHIFT | LOAD            | OUTPUT | RAM <sub>o</sub> | RAM <sub>15</sub> | Q <sub>0</sub> | Q <sub>15</sub>  |                        |

| OREG     | Н              | L  | L     | L   | 8           | Х     | NONE        | NONE  | F→Q             | F      | X                | х                 | X              | . X              |                        |

| NOP      | Н              | L  | L     | Н   | 9           | Х     | NONE        | Х     | NONE            | F      | Х                | х                 | Х              | Х                |                        |

| RAMA     | Н              | L  | Н     | L   | Α           | NONE  | F-→B        | Х     | NONE            | A      | х                | х                 | Х              | Х                |                        |

| RAMF     | Н              | L  | Н     | Н   | В           | NONE  | F→B         | Х     | NONE            | F      | Х                | х                 | х              | Х                | Existina 2901          |

| RAMOD    | Н              | Н  | L     | L   | С           | DOWN  | F/2→B       | DOWN  | Q/2→Q           | F      | Fo               | IN <sub>15</sub>  | Q <sub>o</sub> | IN <sub>15</sub> | Functions              |

| RAMD     | Н              | H  | L     | Н   | D           | DOWN  | F/2-→B      | Х     | NONE            | F      | F <sub>0</sub>   | IN <sub>15</sub>  | Q <sub>0</sub> | Х                |                        |

| RAMQU    | Н              | Н  | Ŧ     | L   | E           | UP    | 2F→B        | · UP  | 2Q- <b>→</b> Q  | F      | IN <sub>0</sub>  | F <sub>15</sub>   | INo            | Q <sub>15</sub>  |                        |

| RAMU     | Н              | H  | Н     | Η   | F           | UP    | 2F—+B       | Х     | NONE            | F      | INo              | F <sub>15</sub>   | Х              | Q <sub>15</sub>  | ,                      |

| DFF      | L              | L  | L     | L   | 0           | NONE  | D→B         | NONE  | F→Q             | F      | Х                | х                 | Х              | χ.               |                        |

| DFA      | L              | L  | ٦     | Н   | 1           | NONE  | D→B         | NONE  | F→Q             | Α      | Х                | . х               | Х              | X                | ,                      |

| FDF      | L              | L  | Н     | L   | 2           | NONE  | F→B         | NONE  | D→Q             | · F    | Х                | ×                 | Х              | Х                | ٠.                     |

| FDA      | L              | L  | Н     | Н   | 3           | NONE  | F→B         | NONE  | D-+Q            | Α      | Х                | х                 | Х              | Х                | New Added              |

| XQDF     | Г              | Н  | L     | ٦   | 4           | Х     | NONE        | DOWN  | Q/2-→Q          | F      | Х                | х                 | Q <sub>0</sub> | IN <sub>15</sub> | IDT49C402<br>Functions |

| DXF      | L              | Н  | Ĺ     | Н   | 5           | NONE  | D→B         | Х     | NONE            | F      | Х                | х                 | Q <sub>0</sub> | X                | , unouona              |

| XQUF     | L              | Н  | Н     | L   | 6           | х     | NONE        | UP    | 2Q-→Q           | F      | Х                | х                 | INo            | Q <sub>15</sub>  |                        |

| XDF      | L              | н  | н     | Н   | 7           | х     | NONE        | NONE  | D→Q             | F      | X                | х                 | Х              | Q <sub>15</sub>  | · _                    |

X = Don't Care. Electrically, the shift pin is a TTL input internally connected to a three-state output which is in the high-impedance state.

B = Register Addressed by B inputs.

UP is toward MSB; DOWN is toward LSB.

S8-5

# MILITARY AND COMMERCIAL TEMPERATURE RANGES 7-49-17-51

CONDITIONS

$V_{iN} = 0V$

UNIT

рF

pF.

ABSOLUTE MAXIMUM RATINGS (1)

| SYMBOL            | RATING                                     | COMMERCIAL   | MILITARY     | UNIT |

|-------------------|--------------------------------------------|--------------|--------------|------|

| V <sub>TERM</sub> | Terminal Voltage<br>with Respect to<br>GND | -0.5 to +7.0 | -0.5 to +7.0 | ٧    |

| TA                | Operating<br>Temperature                   | 0 to +70     | -55 to +125  | °C   |

| TBIAS             | Temperature<br>Under Bias                  | -55 to +125  | -65 to +135  | °C   |

| T <sub>STG</sub>  | Storage<br>Temperature                     | -55 to +125  | -65 to +150  | °C   |

| P <sub>T</sub>    | Power Dissipation                          | 1.5          | 1.5          | W    |

| юл                | DC Output Current                          | 50           | 50           | mA   |

# Cour NOTE:

SYMBOL

CIN

1. This parameter is sampled and not 100% tested.

CAPACITANCE (TA = +25°C, f = 1.0MHz)

PARAMETER(1)

Input Capacitance

**Output Capacitance**

# NOTE:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# DC ELECTRICAL CHARACTERISTICS

$T_A = 0$ °C to +70°C T<sub>A</sub> = -55°C to + 125°C  $V_{CC} = 5.0V \pm 5\%$  (Commercial)  $V_{CC} = 5.0V \pm 10\%$  (Military)

| SYMBOL           | PARAMETER                    | TES                                          | T CONDITIONS (1)               | MIN.            | TYP. <sup>(2)</sup> | MAX.            | UNIT |

|------------------|------------------------------|----------------------------------------------|--------------------------------|-----------------|---------------------|-----------------|------|

| V <sub>iH</sub>  | Input HIGH Level             | Guaranteed Logic High                        | ı Level <sup>(4)</sup>         | 2.0             | _                   | _               | ·v   |

| V <sub>IL</sub>  | Input LOW Level              | Guaranteed Logio Low                         | Level (4)                      |                 |                     | 0.8             | ٧    |

| l <sub>tet</sub> | Input HIGH Current           | Vcc = Max., VIN = Vcc                        | )                              |                 | 0.1                 | 5               | μΑ   |

| I <sub>R</sub>   | Input LOW Current            | V <sub>CC</sub> = Max., V <sub>IN</sub> = GN | -                              | -0.1            | -5                  | μA              |      |

| <u></u>          |                              |                                              | loн = -300µA                   | V <sub>HC</sub> | Vcc                 | _               |      |

| Vou              | VoH Output HIGH Voltage      | V <sub>CC</sub> = Min.                       | I <sub>OH</sub> = -12mA MIL.   | 2.4             | 4.3                 | .   –           | ٧    |

| · On             |                              | $V_{IN} = V_{IH} \text{ or } V_{IL}$         | I <sub>OH</sub> = -15mA COM'L. | 2.4             | 4.3                 | _               | · .  |

|                  |                              |                                              | lot = 300µA                    | -               | GND                 | V <sub>LC</sub> |      |

| V <sub>OL</sub>  | Output LOW Voltage           | V <sub>CC</sub> = Min.                       | lot = 20mA Mil.                | _               | 0.3                 | 0.5             | V    |

| *OL              | -                            | $V_{iN} = V_{iH} \text{ or } V_{iL}$         | I <sub>OL</sub> = 24mA COM'L.  | _               | 0.3                 | 0.5             |      |

|                  | Off State (High Impedance)   | <del></del>                                  | Vo = 0V                        |                 | -0.1                | -10             |      |

| loz              | Output Current               | V <sub>CC</sub> = Max.                       | Vo = Vcc (Max.)                |                 | 0.1                 | 10              | μA   |

| los              | Output Short Circuit Current | Vcc = Min., Vout = 0                         | V (3)                          | -15             | -30                 | _               | mA   |

# NOTES:

- 1. For conditions shown as max. or min. use appropriate value specified under Electrical Characteristics.

- 2. Typical values are at  $V_{CO}$  = 5.0V, +25°C ambient and maximum loading.

- 3. Not more than one output should be shorted at one time. Duration of the short circuit test should not exceed one second.

- 4. These input levels provide zero noise immunity and should only be static tested in a noise-free environment. Guaranteed by design.

**MILITARY AND COMMERCIAL TEMPERATURE RANGES**

# DC ELECTRICAL CHARACTERISTICS (Cont'd)

$T_A = 0$ °C to +70°C  $T_A = -55$ °C to +125°C V<sub>CC</sub> = 5.0V ±5% (Commercial)

V<sub>CC</sub> = 5.0V ±10% (Military)

$V_{LC} = 0.2V$

$V_{HC} = V_{CC} - 0.2V$

| SYMBOL | PARAMETER                                 | TEST CONDITIONS (1)                                                                             | MIN.   | TYP. <sup>(2)</sup> | MAX. | UNIT |            |

|--------|-------------------------------------------|-------------------------------------------------------------------------------------------------|--------|---------------------|------|------|------------|

|        | Quiescent Power Supply Current            | V <sub>CC</sub> = Max.                                                                          | MIL.   |                     | 150  | 265  | mA         |

| ГССОН  | CP = H (CMOS Inputs)                      | $V_{HC} \leq V_{H}$ , $V_{IL} \leq V_{LC}$<br>$f_{CP} = 0$ , $CP = H$                           | COM'L. | -                   | 150  | 215  | ША         |

|        | Quiescent Power Supply Current            | V <sub>CC</sub> = Max,<br>V <sub>HC</sub> ≤ V <sub>IH</sub> , V <sub>IL</sub> ≤ V <sub>LC</sub> | MIL.   | _                   | 80   | 135  |            |

| locar  | CP = L (CMOS Inputs)                      | f <sub>CP</sub> = 0, CP = L                                                                     | COM'L. | -                   | 80   | 110  | mA         |

| ,      | Quiescent Input Power Supply (5)          | V <sub>CC</sub> = Max. V <sub>IH</sub> = 3.4V, f <sub>CP</sub> = 0                              | MIL.   | -                   | 0.3  | 0.6  | mA/        |

| †cct   | Current (per Input @ TTL High)            | V <sub>CC</sub> = Max. V <sub>IH</sub> = 3.4V, t <sub>CP</sub> = 0                              | COM'L. |                     | 0.3  | 0.5  | Input      |

|        | D                                         | V <sub>CC</sub> = Max.                                                                          | MIL.   | •                   | 2.0  | 3.0  | mA/<br>MHz |

| (ccp   | Dynamic Power Supply Current              | V <sub>HO</sub> ≤ V <sub>IH</sub> , V <sub>L</sub> ≤ V <sub>LC</sub><br>Outputs Open, OE = L    | COM'L. | 1                   | 2.0  | 2.5  | MHZ        |

|        |                                           | V <sub>CC</sub> = Max., f <sub>CP</sub> = 10MHz<br>Outputs Open, OE = L                         | MIL.   | -                   | 135  | 255  |            |

| laa    | Total Power Supply Current <sup>(6)</sup> | CP = 50% Duty cycle<br>V <sub>HC</sub> ≤ V <sub>IH</sub> , V <sub>IL</sub> ≤ V <sub>LC</sub>    | COM'L. | 1                   | 135  | 190  | mA         |

|        | Total Power Supply Current                | V <sub>CC</sub> = Max., f <sub>CP</sub> = 10MHz<br>Outputs Open, OE = L<br>CP = 50% Duty cycle  | MIL.   | -                   | 145  | 265  | 11115      |

|        |                                           | $V_{iH} = 3.4V, V_{iL} = 0.4V$                                                                  | COM'L. | _                   | 145  | 200  |            |

## NOTES:

- 5. Icor is derived by measuring the total current with all the inputs tied together at 3.4V, subtracting out Iccoh, then dividing by the total number of inputs.

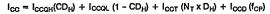

- Total Supply Current is the sum of the Quiescent current and the Dynamic current (at either CMOS or TTL input levels). For all conditions, the Total Supply Current can be calculated by using the following equation:

CD<sub>H</sub> = Clock duty cycle high period

$D_H$  = Data duty cycle TTL high period ( $V_{IN}$  = 3.4V)

N<sub>T</sub> = Number of dynamic inputs driven at TTL levels

fcp = Clock Input frequency

# **CMOS TESTING CONSIDERATIONS**

Special test board considerations must be taken into account when applying high-speed CMOS products to the automatic test environment. Large output currents are being switched in very short periods and proper testing demands that test set-ups have minimized inductance and guaranteed zero voltage grounds. The techniques listed below will assist the user in obtaining accurate testing results:

- All input pins should be connected to a voltage potential during testing. If left floating, the device may oscillate, causing improper device operation and possible latchup.

- 2) Placement and value of decoupling capacitors is critical. Each physical set-up has different electrical characteristics and it is recommended that various decoupling capacitor sizes be experimented with. Capacitors should be positioned using the minimum lead lengths. They should also be distributed to decouple power supply lines and be placed as close as possible to the DUT power pins.

- 3) Device grounding is extremely critical for proper device testing. The use of multi-layer performance boards with radial decoupling between power and ground planes is necessary. The ground plane must be sustained from the performance board to the DUT interface board and wiring unused interconnect plns to the ground plane is recommended. Heavy gauge stranded wire should be used for power wiring, with twisted pairs being recommended for minimized inductance.

- 4) To guarantee data sheet compliance, the input thresholds should be tested per input pin in a static environment. To allow for testing and hardware-induced noise, IDT recommends using V<sub>IL</sub> ≤ 0V and V<sub>IH</sub> ≥ 3V for AC tests.

MILITARY AND COMMERCIAL TEMPERATURE RANGES

T-49-17-51

# IDT49C402B AC ELECTRICAL CHARACTERISTICS (Military and Commercial Temperature Ranges)

The tables below specify the guaranteed performance of the IDT49C402B overthe -55°C to +125°C and 0°C to +70°C temperature ranges. All times are in nanoseconds and are measured at the 1.5V signal level. The inputs switch between 0V and 3V with signal transition rates of 1V per nanosecond. All outputs have maximum DC current loads.

| YCLE TIME AND CLOCK (                                                            | CHARAC  | CTERIST   | <u>rics</u> |

|----------------------------------------------------------------------------------|---------|-----------|-------------|

|                                                                                  | MIL.(6) | COM'L     | UNIT        |

| Read-Modify-Write Cycle (from<br>selection of A, B registers to end<br>of cycle) | 23      | 19        | ns          |

| Maximum Clock Frequency to shift Q (50% duty cycle, i = C32 or E32)              | 42      | <b>49</b> | MHz         |

| Minimum Clock LOW Time                                                           | 11      | 9         | ns          |

| Minimum Clock HIGH Time                                                          | 11      | 9         | ns          |

| Minimum Clock Period                                                             | 24      | 20        | กร          |

# COMBINATIONAL PROPAGATION DELAYS (1) CL = 50pF

|                                        |             | <b>.</b> ; |      |        | •                                |        | ٠.   | TO OI  | JTPUT |              | •    | . '''                                 |     | <u> </u>                          | 1.   |       |    |

|----------------------------------------|-------------|------------|------|--------|----------------------------------|--------|------|--------|-------|--------------|------|---------------------------------------|-----|-----------------------------------|------|-------|----|

| FROMINPUT                              | Y (MSS = L) |            |      |        | (MSS = H)<br>F <sub>15</sub> OVR |        |      | Cn+16  |       | F = 0        |      | RAM <sub>0</sub><br>RAM <sub>15</sub> |     | Q <sub>0</sub><br>Q <sub>15</sub> |      | UNIT  |    |

| le .                                   | MIL         | COM'L.     | MIL. | COM'L. | MIL                              | COM'L. | MIL. | COM'L. | MIL.  | COM'L.       | MIL. | COM'L.                                | MIL | COM'L.                            | MIL. | COM'L |    |

| A, B Address                           | 31          | 28         | 29   | 26     | 31                               | 28     | 31   | 28     | 28    | 26           | 31   | 28                                    | .32 | 29                                |      |       | ns |

| D                                      | 26          | 23         | 23   | 21     | 23                               | 21     | 25   | 22     | 22    | 20           | 26   | 23                                    | 24  | 23                                |      | -     | ns |

| Cn                                     | 22          | 20         | _    |        | 20                               | 18     | 19   | 17     | 15    | //14         | 22   | > 20                                  | 18  | 17                                |      |       | ns |

| lo, 1, 2                               | 28          | 26         | 24   | 22     | 28                               | 26     | 27   | 25     | 23    | 21           | 28   | 26                                    | 26  | 24                                |      |       | ns |

| 13, 4, 5                               | 28          | 26         | 22   | 21     | 27                               | 25     | 27   | 25     | 22    | 20           | 28   | 26                                    | 25  | 23                                |      |       | ns |

| 18, 7, 8, 9                            | 20          | 18         | -    |        | _                                | -      | -    |        |       | <i>≫</i> -`` |      | -                                     | 16  | 14                                | 16   | 14    | ns |

| A Bypass<br>ALU (I = AXX,<br>1XX, 3XX) | 24          | 22         |      | -      | -                                | -      | -    |        |       | 3            | -    | _                                     | 7   | -                                 | 1    | -     | ns |

| Cłock _                                | 27          | 25         | 25   | 22     | 26                               | 24     | 27   | .25    | 25    | 23           | 27   | 25                                    | 27  | 25                                | 20   | 18    | ns |

# SET-UP AND HOLD TIMES RELATIVE TO CLOCK (CP INPUT)

|                                           | CP:  |                   |                  |                   |                      |                     |               |               | • ;  |

|-------------------------------------------|------|-------------------|------------------|-------------------|----------------------|---------------------|---------------|---------------|------|

| INPUT                                     |      | P TIME<br>RE H-→L |                  | D TIME<br>ER'H'→L | SET-UP<br>BEFOR      |                     | HOLD<br>AFTER | TIME<br>₹ L→H | UNIT |

| 1113 01                                   | MIL, | COM'L             | MIL              | COM'L             | MIL.                 | COM'L               | MIL           | COM'L.        |      |

| A, B Source Address                       | 10   | 9 🐇               | 2 <sup>(3)</sup> | 1 <sup>(3)</sup>  | 20, 9 +              | TPWL <sup>(4)</sup> | 2             | 1             | ns   |

| B Destination Address                     | - 10 | 9                 |                  | Do not o          | hange <sup>(2)</sup> |                     | 2             | 1             | ns   |

| D                                         | (1)  | -200              |                  |                   | 12/22 <sup>(5)</sup> | 10/20 (5)           | 2             | 11            | ns   |

| Cn .                                      | -    | 4//               |                  |                   | 16                   | 14                  | 0             | 0             | ns   |

| lo, 1, 2                                  | _    | 0                 | <i>///</i> -     | _                 | 26                   | 24                  | 0             | 0             | ns   |

| 13, 4, 5                                  | -    | 40-20-            | <b>y</b> -       | _                 | 26                   | 24                  | 0             | 0             | ns   |

| 18, 7, 8, 9                               | 10   |                   |                  | Do not o          | hange (2)            |                     | 0             | 0             | ns   |

| RAM <sub>0, 15</sub> , Q <sub>0, 15</sub> |      | - 🔻               |                  |                   | 12                   | 10                  | 0             | 0             | ns   |

# NOTES

- 1, A dash indicates a propagation delay or set-up time constraint does not exist.

- 2. Certain signals must be stable during the entire clock LOW time to avoid erroneous operation.

- 3. Source addresses must be stable prior to the H → L transition to allow time to access the source data before the latches close. The A address may then be changed. The B address could be changed if it is not a destination; i.e., if data is not being written back into the RAM. Normally A and B are not changed during the clock LOW time.

- 4. The set-up time prior to the clock L→ H transition is to allow time for data to be accessed, passed through the ALU and returned to the RAM. It includes all the time from stable A and B addresses to the clock L→ H transition, regardless of when the H→L transition occurs. TPWL is the minimum clock Low time.

- 5. First value is direct path (DATA<sub>IN</sub>  $\rightarrow$  RAM/Q Register). Second value is indirect path (DATA<sub>IN</sub>  $\rightarrow$  ALU  $\rightarrow$  RAM/Q Register).

- 6. Guaranteed by design.

wnloaded from Elcodis.com electronic components distributor

IDT49C402A

# **AC ELECTRICAL CHARACTERISTICS** (Military and Commercial Temperature Ranges)

IDT49C402/A/B 16-BIT CMOS MICROPROCESSOR SLICE

The tables below specify the guaranteed performance of the IDT49C402A overthe -55°C to +125°C and 0°C to +70°C temperature ranges. All times are in nanoseconds and are measured at the 1.5V signal level. The inputs switch between 0V and 3V with signal transition rates of 1V per nanosecond. All outputs have maximum processes. mum DC current loads.

# MILITARY AND COMMERCIAL TEMPERATURE RANGES 7-49-17-51 CYCLE TIME AND CLOCK CHARACTERISTICS

|                                                                            | MIL.(8) | COM'L | UNIT |

|----------------------------------------------------------------------------|---------|-------|------|

| Read-Modify-Write Cycle (from selection of A, B registers to end of cycle) | 28      | 24    | ns   |

| Maximum Clock Frequency to<br>shift Q (50% duty cycle,<br>I = C32 or E32)  | 35      | 41    | MHz  |

| Minimum Clock LOW Time                                                     | 13      | 11    | ns   |

| Minimum Clock HIGH Time                                                    | 13      | 11    | ns   |

| Minimum Clock Period                                                       | 36      | 31    | ns   |

|                                        | l    |              |      |                |                                  | • .    |                  | TO OI  | JTPUT | •      |     |                                     |      |                                     |      |        |    |

|----------------------------------------|------|--------------|------|----------------|----------------------------------|--------|------------------|--------|-------|--------|-----|-------------------------------------|------|-------------------------------------|------|--------|----|

| FROM INPUT                             |      | Y (MSS<br>G, |      | S = L)<br>G, P | (MSS = H)<br>F <sub>15</sub> OVR |        | · C <sub>r</sub> | 1+18   | ı     | F = 0  |     | AM <sub>0</sub><br>AM <sub>15</sub> |      | Q <sub>o</sub><br>Q <sub>t5</sub> U |      |        |    |

|                                        | MIL. | COM'L.       | MIL. | COM'L.         | MIL.                             | COM'L. | MIL.             | COM'L. | MIL.  | COM'L. | MIL | COM'L.                              | MIL. | COM'L.                              | MIL. | COM'L. |    |

| A, B Address                           | 41   | 37           | 39   | 35             | 41                               | 37     | 41               | 37     | 37    | 34     | 41  | 37                                  | 40   | 36                                  | 1    |        | ns |

| D                                      | 32   | 29           | 29   | 26             | 29                               | 26     | 31               | · 28   | 27    | 25     | 32  | 29                                  | 28   | 26                                  | · =  | _      | ns |

| Cn                                     | 28   | 25           | -    | -              | 26                               | 24     | 25               | 23     | 20    | 18     | 29  | 26                                  | 23   | 21                                  | _    | -      | ns |

| 10, 1, 2                               | 35   | 32           | 30   | 27             | 35                               | 32     | 34               | 31     | 29    | 26     | 35  | 32                                  | 30   | 27                                  | _    |        | ns |

| 13, 4, 5                               | 35   | 32           | 28   | 26             | 34                               | 31     | 34               | 31     | 27    | 25     | 35  | 32                                  | 28   | 26                                  | _    | _      | ns |

| 18, 7, 8, 9                            | 25   | 23           | -    | -              | _                                | _      | -                | _      | -     | -      | -   | _                                   | 20   | 18                                  | 20   | 18     | ns |

| A Bypass<br>ALU (I = AXX,<br>1XX, 3XX) | 30   | 27           | _    | -              | _                                | _      | -                | -      | _     | -      | -   |                                     | -    | -                                   | _    | ı      | ns |

| Clock _                                | 34   | 31           | 31   | 28             | 33                               | 30     | 34               | 31     | 30    | 27     | 34  | 31                                  | 34   | 31                                  | 25   | 23     | ns |

SET-UP AND HOLD TIMES RELATIVE TO CLOCK (CP INPUT)

|                                           | CP:          |                  |       |                   |                 |                      | _    | -      |        |

|-------------------------------------------|--------------|------------------|-------|-------------------|-----------------|----------------------|------|--------|--------|

| INPUT                                     | SET-U        | P TIME<br>RE H→L |       | O TIME<br>ER H-→L | SET-UP<br>BEFOR |                      | HOLD | UNIT   |        |

|                                           | MIL.         | COM'L.           | MIL.  | COM'L.            | MIL.            | COM'L.               | MIL. | COM'L. | 0,,,,, |

| A, B Source Address                       | 11           | 10               | 2 (3) | 1 <sup>(3)</sup>  | 21, 10 +        | TPWL <sup>(4)</sup>  | 2    | 1      | ns     |

| B Destination Address                     | 11           | 10               |       | Do not c          | hange (2)       |                      | 2    | 1      | ns     |

| D                                         | <b>→ (1)</b> | _                | _     | _                 | 12/22 (5)       | 10/20 <sup>(5)</sup> | 2    | 1      | ns     |

| Cn                                        | _            | _                | -     | -                 | 17              | 15                   | 0    | 0      | ns     |

| l <sub>0, 1, 2</sub>                      | _· .         |                  | _     |                   | 28              | 25                   | 0    | 0      | ns     |

| 13, 4, 5                                  | _ ``         | _                |       | -                 | 28              | 25                   | 0    | 0      | ns     |

| 8, 7, 8, 9                                | 11           | 10               |       | Do not c          | hange (2)       |                      | 0    | 0      | ns     |

| RAM <sub>0, 15</sub> , Q <sub>0, 15</sub> |              | _                | -     | _                 | 12              | 11                   | 0    | 0      | ns     |

# HOTES:

- 1. A dash indicates a propagation delay or set-up time constraint does not exist.

- 2 Certain signals must be stable during the entire clock LOW time to avoid erroneous operation.

- Source addresses must be stable prior to the H → L transition to allow time to access the source data before the latches close. The A address may then be changed. The B address could be changed if it is not a destination; i.e., if data is not being written back into the RAM. Normally A and B are not changed during the clock LOW time.

- 4. The set-up time prior to the clock L→ H transition is to allow time for data to be accessed, passed through the ALU and returned to the RAM. It includes all the time from stable A and B addresses to the clock  $L \rightarrow H$  transition, regardless of when the  $H \rightarrow L$  transition occurs.

- First value is direct path (DATA<sub>IN</sub> → RAM/Q Register). Second value is indirect path (DATA<sub>IN</sub> → ALU → RAM/Q Register).

- 8. Guaranteed by design.

MILITARY AND COMMERCIAL TEMPERATURE RANGES

T-49-17-51

# IDT49C402

# AC ELECTRICAL CHARACTERISTICS (Military and Commercial Temperature Ranges)

IDT49C402/A/B 16-BIT CMOS MICROPROCESSOR SLICE

The tables below specify the guaranteed performance of the IDT49C402 over the -55°C to +125°C and 0°C to +70°C temperature ranges. All times are in nanoseconds and are measured at the 1.5V signal level. The inputs switch between 0V and 3V with signal transition rates of 1V per nanosecond. All outputs have maximum DC current loads.

| CYCLE | TIME A | ND CLO | CK | C  | HARAC   | CTERIS | <b>TICS</b> |

|-------|--------|--------|----|----|---------|--------|-------------|

|       |        |        |    | -[ | MII (8) | COMI   | UNIT        |

|                                                                                  | MIL(8) | COM'L. | UNIT |

|----------------------------------------------------------------------------------|--------|--------|------|

| Read-Modify-Write Cycle (from<br>selection of A, B registers to end<br>of cycle) | 50     | 48     | ns   |

| Maximum Clock Frequency to shift Q (50% duty cycle, I = C32 or E32)              | 20     | 21     | MHz  |

| Minimum Clock LOW Time                                                           | 30     | 30     | ns   |

| Minimum Clock HIGH Time                                                          | 20     | 20     | ns   |

| Minimum Clock Period                                                             | 50     | 48     | ns   |

|                                        |      |       |            |          |      |                                  |      | TO OU  | TPUT |        |      |        |                                     |                                   |      |        | · · . |

|----------------------------------------|------|-------|------------|----------|------|----------------------------------|------|--------|------|--------|------|--------|-------------------------------------|-----------------------------------|------|--------|-------|

| FROM INPUT                             |      | Υ     | (MS        | S = L)   |      | (MSS = H)<br>F <sub>15</sub> OVR |      | Cr     | 1+18 |        | = 0  |        | AM <sub>0</sub><br>AM <sub>15</sub> | Q <sub>0</sub><br>Q <sub>15</sub> |      | UNIT   |       |

| <del></del>                            | MIL. | COM'L | MIL.       | COM'L.   | MIL. | COM'L.                           | MIL. | COM'L. | MIL  | COM'L. | MIL. | COM'L. | MIL.                                | COM'L                             | MIL. | COM'L. |       |

| A. B Address                           | 52   | 47    | 47         | 42       | 52   | 47                               | 47.  | 42     | 38   | 34     | 52   | 47     | .44                                 | 40                                | -    |        | ns    |

| D                                      | 35   | 32    | 34         | 31       | 35   | 32                               | 34   | 31     | 27   | 25     | 35   | 32     | 28                                  | 26                                |      | -      | ns    |

| C <sub>n</sub>                         | 29   | 26    |            | ·        | 29   | 26                               | 27   | 25     | 20   | 18     | 29   | 26     | 23                                  | 21                                | _    |        | ns    |

| lo, 1, 2                               | 41   | 37    | 30         | 27       | 41   | 37                               | 38   | 35     | 29   | 26     | 41   | 37     | 30                                  | 27                                |      |        | ns    |

| 13, 4, 5                               | 40   | 36    | 28         | 26       | 40   | 36                               | 37   | 34     | 27   | 25     | 40   | 36     | 28                                  | 26                                | _    | · -    | ns    |

| l <sub>6, 7, 8, 9</sub>                | 26   | 24    | -          | <u> </u> | -    | _                                | -    | -      | -    |        | -    | -      | 20                                  | 18                                | 20   | 18     | ns    |

| A Bypass<br>ALU (I = AXX,<br>1XX, 3XX) | 30   | 27    | <u>-</u> . | -        | -,   | _                                | -    |        | -    | -      | -    |        | -                                   | _                                 | -    | _      | ns    |

| Clock 4                                | 42   | 38    | 41         | 37       | 42   | 38                               | 4.1  | 37     | 30   | 27     | 42   | 38     | 41                                  | 37                                | 25   | 23     | ns    |

# SET-UP AND HOLD TIMES RELATIVE TO CLOCK (CP INPUT)

|                       | CP:   |                  |                  |                  |                      |                      |               |              |      |  |  |  |  |

|-----------------------|-------|------------------|------------------|------------------|----------------------|----------------------|---------------|--------------|------|--|--|--|--|

| INPUT                 | SET-U | P TIME<br>RE H→L |                  | D TIME<br>ER H→L | SET-UP<br>BEFOR      |                      | HOLD<br>AFTER | TIME<br>RL→H | UNIT |  |  |  |  |

| INPUT                 | MIL.  | COM'L.           | MIL              | COM'L.           | MIL                  | COM'L.               | MIL.          | COM'L.       |      |  |  |  |  |

| A, B Source Address   | 20    | 18               | 2 <sup>(3)</sup> | 1 <sup>(3)</sup> | 50, 20 +             | TPWL <sup>(4)</sup>  | 2             | 1            | ns   |  |  |  |  |

| B Destination Address | 20    | 18               | • .              | Do not o         | hange <sup>(2)</sup> |                      | 2             | 1            | ns   |  |  |  |  |

| D                     | _ (1) | _                |                  | _ 1              | 30/40 <sup>(5)</sup> | 26/36 <sup>(5)</sup> | 2             | 1            | ns   |  |  |  |  |

| Cn                    |       | _                | ·                | · =              | 35                   | 32                   | . 0           | 0            | ns   |  |  |  |  |

| ĺo, 1, 2              | _     | _                | _                |                  | 45                   | 41                   | 0             | 0            | ns   |  |  |  |  |

| 13, 4, 5              | _     | -                | _                | _                | 45                   | . 41                 | 0             | . 0          | ns   |  |  |  |  |

| 18, 7, 8, 9           | 12    | 11               |                  | Do not o         | hange (2)            |                      | 0             | . 0          | ns   |  |  |  |  |

| RAMo, 15, Qo, 15      | _     | _                |                  | · _              | 12                   | 11                   | 0             | 0            | ns   |  |  |  |  |

- 1. A dash indicates a propagation delay or set-up time constraint does not exist.

- 2. Certain signals must be stable during the entire clock LOW time to avoid erroneous operation.

- Source addresses must be stable prior to the H → L transition to allow time to access the source data before the latches close. The A address may then be changed. The B address could be changed if it is not a destination; i.e., if data is not being written back into the RAM. Normally A and B are not changed during the clock LOW time.

- 4. The set-up time prior to the clock L→ H transition is to allow time for data to be accessed, passed through the ALU and returned to the RAM. It includes all the time from stable A and B addresses to the clock L→ H transition, regardless of when the H→L transition occurs.

- First value is direct path (DATA<sub>IN</sub> → RAM/Q Register). Second value is indirect path (DATA<sub>IN</sub> → ALU → RAM/Q Register).

- 6. Guaranteed by design.

**MILITARY AND COMMERCIAL TEMPERATURE RANGES**

IDT49C402/A/B 16-BIT CMOS MICROPROCESSOR SLICE

# IDT49C402B

OUTPUT ENABLE/DISABLE TIMES

(C<sub>L</sub> = 5pF, measured to 0.5V change of V<sub>out</sub> in nanoseconds)

|       |        | EN   | ABLE  | DISABLE |           |  |

|-------|--------|------|-------|---------|-----------|--|

| INPUT | OUTPUT | MIL. | COM'L | MIL     | COM'L.    |  |

| Ø OE® | wyc    | 20   | 18    | ₩18.W   | <b>16</b> |  |

## **AC TEST CONDITIONS** Input Pulse Levels GND to 3 0V Input Rise/Fall Times 1V/ns Input Timing Reference Levels 1.5V Output Reference Levels : 1.5V Output Load See Figure 1

# IDT49C402A

# **OUTPUT ENABLE/DISABLE TIMES**

(C<sub>L</sub> = 5pF, measured to 0.5V change of V<sub>OUT</sub> in nanoseconds)

|       |        | EN  | ENABLE |      | ISABLE |  |  |

|-------|--------|-----|--------|------|--------|--|--|

| INPUT | OUTPUT | MIL | COM'L. | MIL. | COM'L. |  |  |

| ŌĒ    | Υ      | 22  | 20     | 20   | 18     |  |  |

# IDT49C402

# **OUTPUT ENABLE/DISABLE TIMES**

(C<sub>L</sub> = 5pF, measured to 0.5V change of V<sub>OUT</sub> In nanoseconds)

| INPUT ( |        | EN   | ABLE   | DISABLE |        |  |  |

|---------|--------|------|--------|---------|--------|--|--|

| INPUT   | OUTPUT | MIL. | COM'L. | MIL     | COM'L. |  |  |

| ŌĒ      | Y      | 25   | 23     | 25      | 23     |  |  |

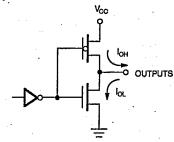

# **TEST LOAD CIRCUIT**

Figure 1. Switching Test Circuit (All Outputs)

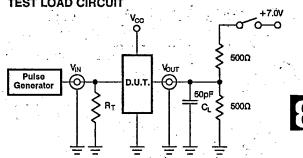

# INPUT/OUTPUT INTERFACE CIRCUIT

Figure 2. Input Structure (All Inputs)

Downloaded from Elcodis.com electronic components distributor

Figure 3. Output Structure (All Outputs Except F = 0)

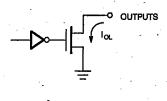

Figure 4. Output Structure (F = 0)

MILITARY AND COMMERCIAL TEMPERATURE RANGES

# T=49-17-51

# IDT49C402/A/B 16-BIT CMOS MICROPROCESSOR SLICE

# **CRITICAL SPEED PATH ANALYSIS**

Critical speed paths are for the IDT49C402A versus the equivalent bipolar circuit implementation using four 2901Cs and one 2902A is shown below.

The IDT49C402A operates faster than the theoretically achievable values of the discrete bipolar implementation. Actual speed values for the discrete bipolar circuit will increase due to on-chip/off-chip circuit board delays.

# TIMING COMPARISON: IDT49C402A vs 2901C w/2902A

| 16-BIT              | DAT             | A PATH<br>DM'L)                | DAT/                                   | DATA PATH<br>(MIL)             |      |  |

|---------------------|-----------------|--------------------------------|----------------------------------------|--------------------------------|------|--|

| µP SYSTEM           | AB ADDR → F = 0 | AB ADDR → RAM <sub>0, 15</sub> | AB ADDR $\rightarrow$ $\mathbf{F} = 0$ | AB ADDR → RAM <sub>0, 15</sub> |      |  |

| Four 2901Cs + 2902A | ≥71             | ≥71                            | ≥83.5                                  | ≥83.5                          | ns   |  |

| IDT49C402A          | 37              | 36                             | 41                                     | 40                             | ns · |  |

| Speed Savings       | 34              | 35                             | 42.5                                   | 43.5                           | ns   |  |

# TIMING COMPARISON: IDT49C402 vs 2901C w/2902A

| 16-BIT<br>µP SYSTEM | DATA PATH<br>(COM'L.) |                                | DATA PATH<br>(MIL)            |                                | UNIT |

|---------------------|-----------------------|--------------------------------|-------------------------------|--------------------------------|------|

|                     | AB ADDR → F = 0       | AB ADDR → RAM <sub>0, 15</sub> | AB ADDR $\rightarrow$ $F = 0$ | AB ADDR → RAM <sub>0, 15</sub> |      |

| Four 2901Cs + 2902A | ≥71                   | ≥71                            | ≥83.5                         | ≥83.5                          | ns   |

| IDT49C402           | ··· . ··. 47 ·        | - 40                           | 52                            | 44                             | ns   |

| Speed Savings       | 24                    | 31                             | - 31.5                        | 39.5                           | ns   |

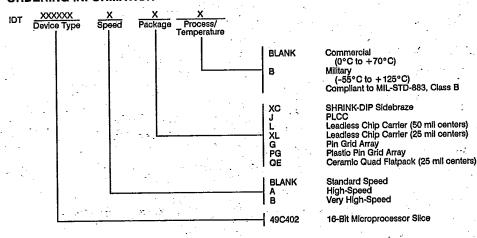

# **ORDERING INFORMATION**