# 6-BIT UNIVERSAL UP/DOWN COUNTER

SY10E136 SY100E136

#### **FEATURES**

- **■** 550MHz count frequency

- Extended 100E VEE range of -4.2V to -5.5V

- Look-ahead-carry input and output

- Fully synchronous up and down counting

- Asynchronous Master Reset

- Internal 75K $\Omega$  input pull-down resistors

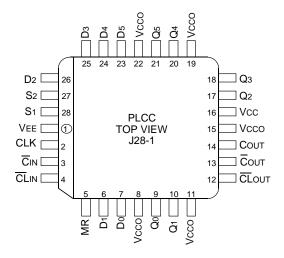

- Available in 28-pin PLCC package

#### PIN CONFIGURATION

#### **PIN NAMES**

| Pin        | Function                      |

|------------|-------------------------------|

| D0-D5      | Preset Data Inputs            |

| Q0-Q5      | Differential Data Outputs     |

| S1, S2     | Mode Control Pins             |

| MR         | Master Reset                  |

| CLK        | Clock Input                   |

| Couт, Сouт | Carry Out Output (Active LOW) |

| CLOUT      | Look-Ahead-Carry Output       |

| CIN        | Carry-In Input (Active LOW)   |

| CLIN       | Look-Ahead-Carry Input        |

| Vcco       | Vcc to Output                 |

#### **DESCRIPTION**

The SY10/100E136 are 6-bit synchronous, presettable, cascadable universal counters. These devices generate a look-ahead-carry output and accept a look-ahead-carry input. These two features allow for the cascading of multiple E136s for wider bit width counters that operate at very nearly the same frequency as the stand-alone counter.

The CLOUT output will pulse LOW for one clock cycle one count before the E136 reaches terminal count. The COUT output will pulse LOW for one clock cycle when the counter reaches terminal count. For more information on utilizing the look-ahead-carry features of the device, please refer to the applications section of this data sheet. The differential Cout output facilitates the E136's use in programmable divider and self-stopping counter applications.

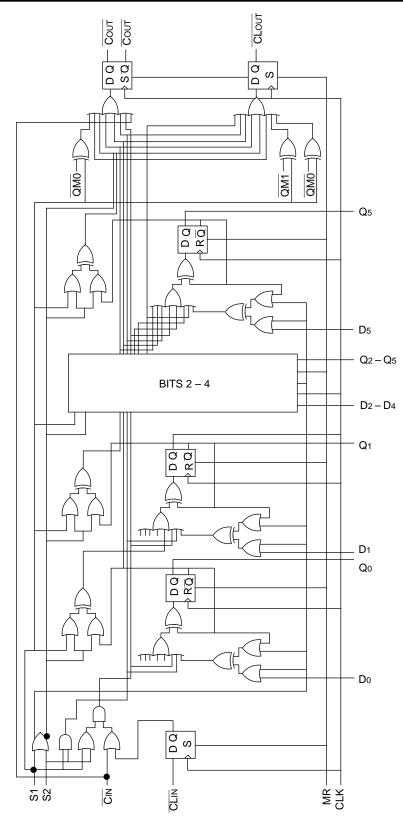

Unlike the H136 and other similar universal counter designs, the E136 carry-out and look-ahead-carry-out signals are registered on chip. This design alleviates the glitch problem seen on many counters where the carry-out signals are merely gated. Because of this architecture, there are some minor functional differences between the E136 and H136 counters. The user, regardless of familiarity with the H136, should read this data sheet carefully. Note specifically (see block diagram) the operation of the carry-out outputs and the look-ahead-carry-in input when utilizing the Master Reset.

When left open, all of the input pins will be pulled LOW via an input pulldown resistor. The Master Reset is an asynchronous signal which, when asserted, will force the Q outputs LOW.

The Q outputs need not be terminated for the E136 to function properly. In fact, if these outputs will not be used in a system, it is recommended that they be left open to save power and minimize noise. This practice will minimize switching noise which can reduce the maximum count frequency of the device, or significantly reduce margins against other noise in the system.

# BLOCK DIAGRAM<sup>(1)</sup>

E136 Universal Up/Down Counter Logic Diagram

#### NOTE:

1. This diagram is provided for understanding of logic operation only. It should not be used for propagation delays as many gate functions are achieved internally without incurring a full gate delay.

# TRUTH TABLE(1)

| S <sub>1</sub> | S <sub>2</sub> | Cin | MR | CLK | Function                      |  |  |  |

|----------------|----------------|-----|----|-----|-------------------------------|--|--|--|

| L              | L              | Χ   | L  | Z   | Preset Parallel Data Inputs   |  |  |  |

| L              | Н              | L   | L  | Z   | Increment (Count Up)          |  |  |  |

| L              | Н              | Н   | L  | Z   | Hold Count                    |  |  |  |

| Н              | L              | L   | L  | Z   | Decrement (Count Down)        |  |  |  |

| Н              | L              | Н   | L  | Z   | Hold Count                    |  |  |  |

| Н              | Н              | Х   | L  | Z   | Hold Count                    |  |  |  |

| X              | Х              | Х   | Н  | Х   | Reset (Qn = LOW; Cout = HIGH) |  |  |  |

#### NOTE:

# EXPANDED TRUTH TABLE(1)

| Function                                   | S <sub>1</sub>    | S <sub>2</sub>             | MR               | CIN                        | CLIN                            | CLK                                       | D5                                   | D4                                   | Dз                                   | D2                                   | D1                              | D <sub>0</sub>                  | Q5                | Q4                              | Q3                              | Q2                         | Q1                    | Q <sub>0</sub>             | Соит        | CLOUT            |

|--------------------------------------------|-------------------|----------------------------|------------------|----------------------------|---------------------------------|-------------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|---------------------------------|---------------------------------|-------------------|---------------------------------|---------------------------------|----------------------------|-----------------------|----------------------------|-------------|------------------|

| Preset                                     | L                 | L                          | L                | Χ                          | Χ                               | Z                                         | L                                    | L                                    | L                                    | L                                    | Н                               | Н                               | L                 | L                               | L                               | L                          | Н                     | Н                          | Н           | Н                |

| Down                                       | ннн               | L<br>L<br>L                | L<br>L<br>L      | L<br>L<br>L                | L<br>L<br>L                     | Z<br>Z<br>Z<br>Z                          | X<br>X<br>X                          | X<br>X<br>X                          | X<br>X<br>X                          | X<br>X<br>X                          | X<br>X<br>X                     | X<br>X<br>X                     | L<br>L<br>H       | L<br>L<br>H                     | L<br>L<br>H                     | L<br>L<br>L                | H<br>L<br>L<br>H      | L<br>H<br>L                | エエーエ        | H<br>L<br>H<br>H |

| Preset                                     | L                 | L                          | L                | Χ                          | Χ                               | Z                                         | Н                                    | Н                                    | Н                                    | Н                                    | L                               | L                               | Н                 | Н                               | Н                               | Н                          | L                     | L                          | Н           | Н                |

| Up                                         |                   | H H H H H                  | L<br>L<br>L<br>L | L<br>L<br>L<br>L           | L<br>L<br>L<br>L                | Z<br>Z<br>Z<br>Z<br>Z                     | X<br>X<br>X<br>X                     | X<br>X<br>X<br>X                     | X<br>X<br>X<br>X                     | X<br>X<br>X<br>X                     | X<br>X<br>X<br>X                | X<br>X<br>X<br>X                | H H H L L L       | H<br>H<br>L<br>L                | H<br>H<br>L<br>L                | H<br>H<br>L<br>L           | L<br>H<br>L<br>L      | H<br>L<br>H<br>L           | I I I I I I | IIII             |

| Hold                                       | H<br>H            | H<br>H                     | L<br>L           | X<br>X                     | X<br>X                          | Z<br>Z                                    | X<br>X                               | X<br>X                               | X<br>X                               | X<br>X                               | X<br>X                          | X<br>X                          | L<br>L            | L<br>L                          | L<br>L                          | L<br>L                     | H<br>H                | L<br>L                     | H           | Н                |

| Down<br>Hold<br>Down<br>Hold               |                   |                            |                  | LHLHHLL                    | L<br>L<br>L<br>H<br>H<br>L      | Z<br>Z<br>Z<br>Z<br>Z<br>Z<br>Z           | X<br>X<br>X<br>X<br>X<br>X           | X<br>X<br>X<br>X<br>X<br>X           | X<br>X<br>X<br>X<br>X<br>X           | X<br>X<br>X<br>X<br>X<br>X           | X<br>X<br>X<br>X<br>X<br>X      | X<br>X<br>X<br>X<br>X<br>X      |                   |                                 |                                 |                            |                       | HLLLLLL                    | 1111111     |                  |

| Hold<br>Preset<br>Up<br>Hold<br>Up<br>Hold | H L L L L L L L L | H<br>H<br>H<br>H<br>H<br>H |                  | L<br>X<br>L<br>H<br>H<br>L | L<br>X<br>L<br>L<br>L<br>H<br>L | Z<br>Z<br>Z<br>Z<br>Z<br>Z<br>Z<br>Z<br>Z | X<br>H<br>X<br>X<br>X<br>X<br>X<br>X | X<br>H<br>X<br>X<br>X<br>X<br>X<br>X | X<br>H<br>X<br>X<br>X<br>X<br>X<br>X | X<br>H<br>X<br>X<br>X<br>X<br>X<br>X | X<br>L<br>X<br>X<br>X<br>X<br>X | X<br>L<br>X<br>X<br>X<br>X<br>X | L H H H H H H H H | L<br>H<br>H<br>H<br>H<br>H<br>H | L<br>H<br>H<br>H<br>H<br>H<br>H | L<br>H<br>H<br>H<br>H<br>H | L<br>L<br>H<br>H<br>H | L<br>H<br>L<br>H<br>H<br>H |             | H H H H H H H    |

| Up                                         | L<br>L<br>L       | H<br>H<br>H                | L<br>L<br>L      | L<br>L<br>L                | L<br>L<br>L                     | Z<br>Z<br>Z<br>Z                          | X<br>X<br>X                          | X<br>X<br>X                          | X<br>X<br>X                          | X<br>X<br>X                          | X<br>X<br>X                     | X<br>X<br>X                     | L<br>L<br>L       | L<br>L<br>L                     | L<br>L<br>L                     | L<br>L<br>L                | L<br>L<br>H<br>H      | L<br>H<br>L                | IIII        | ппп              |

| Reset                                      | Χ                 | Χ                          | Н                | Χ                          | Χ                               | Χ                                         | Χ                                    | Χ                                    | Χ                                    | Χ                                    | Χ                               | Χ                               | L                 | L                               | L                               | L                          | L                     | L                          | Н           | Н                |

#### NOTE:

1. Z = LOW-to-HIGH transition

<sup>1.</sup> Expanded truth table included on following pages.

### DC ELECTRICAL CHARACTERISTICS

VEE = VEE (Min.) to VEE (Max.); VCC = VCCO = GND

|        |                                     | TA = 0°C |            |            | TA = +25°C |            |            | TA = +85°C |            |            |      |           |

|--------|-------------------------------------|----------|------------|------------|------------|------------|------------|------------|------------|------------|------|-----------|

| Symbol | Parameter                           | Min.     | Тур.       | Max.       | Min.       | Тур.       | Max.       | Min.       | Тур.       | Max.       | Unit | Condition |

| Іін    | Input HIGH Current                  | _        | _          | 150        | _          | _          | 150        | _          | _          | 150        | μΑ   |           |

| lee    | Power Supply Current<br>10E<br>100E | _        | 125<br>125 | 150<br>150 | _          | 125<br>125 | 150<br>150 | _          | 125<br>140 | 150<br>170 | mA   | _         |

### **AC ELECTRICAL CHARACTERISTICS**

VEE = VEE (Min.) to VEE (Max.); VCC = VCCO = GND

|              |                                                                       | TA = 0°C                  |                              | TA = +25°C                   |                           |                              | T                            | 4 = +85°                  | C                            |                              |      |           |

|--------------|-----------------------------------------------------------------------|---------------------------|------------------------------|------------------------------|---------------------------|------------------------------|------------------------------|---------------------------|------------------------------|------------------------------|------|-----------|

| Symbol       | Parameter                                                             | Min.                      | Тур.                         | Max.                         | Min.                      | Тур.                         | Max.                         | Min.                      | Тур.                         | Max.                         | Unit | Condition |

| fCOUNT       | Maximum Count Frequency                                               | 550                       | 650                          | _                            | 550                       | 650                          | _                            | 550                       | 650                          |                              | MHz  | _         |

| tPLH<br>tPHL | Propagation Delay to Output CLK to Q MR to Q CLK to COUT CLK to CLOUT | 850<br>850<br>800<br>825  | 1150<br>1150<br>1150<br>1150 | 1450<br>1450<br>1300<br>1400 | 850<br>850<br>800<br>825  | 1150<br>1150<br>1150<br>1150 | 1450<br>1450<br>1300<br>1400 | 850<br>850<br>800<br>825  | 1150<br>1150<br>1150<br>1150 | 1450<br>1450<br>1300<br>1400 | ps   | _         |

| ts           | Set-up Time<br>S1, S2<br>D<br>CLIN<br>CIN                             | 1500<br>800<br>150<br>800 | 650<br>400<br>0<br>400       |                              | 1500<br>800<br>150<br>800 | 650<br>400<br>0<br>400       |                              | 1500<br>800<br>150<br>800 | 650<br>400<br>0<br>400       | 1111                         | ps   | _         |

| tH           | Hold Time<br>S1, S2<br>D<br>CLIN<br>CIN                               | 150<br>150<br>300<br>150  | -200<br>-250<br>0<br>-250    | _<br>_<br>_<br>_             | 150<br>150<br>300<br>150  | -200<br>-250<br>0<br>-250    | _<br>_<br>_<br>_             | 150<br>150<br>300<br>150  | -200<br>-250<br>0<br>-250    |                              | ps   | _         |

| trr          | Reset Recovery Time                                                   | 1000                      | 700                          | _                            | 1000                      | 700                          | _                            | 1000                      | 700                          |                              | ps   | _         |

| tpw          | Minimum Pulse Width CLK, MR                                           | 700                       | 400                          | _                            | 700                       | 400                          | _                            | 700                       | 400                          | _                            | ps   | _         |

| tr<br>tf     | Rise/Fall Times<br>20% to 80%<br>COUT<br>Other                        | 275<br>300                | _                            | 600<br>700                   | 275<br>300                | _                            | 600<br>700                   | 275<br>300                | _                            | 600<br>700                   | ps   | _         |

### **PRODUCT ORDERING CODE**

| Ordering<br>Code | Package<br>Type | Operating<br>Range |

|------------------|-----------------|--------------------|

| SY10E136JC       | J28-1           | Commercial         |

| SY10E136JCTR     | J28-1           | Commercial         |

| SY100E136JC      | J28-1           | Commercial         |

| SY100E136JCTR    | J28-1           | Commercial         |

#### **APPLICATIONS INFORMATION**

#### Overview

The SY10E/100E136 are 6-bit synchronous, presettable, cascadable universal counters. Using the S1 and S2 control pins, the user can select between preset, count up, count down and hold count. The Master Reset pin will reset the internal counter and set the COUT, CLOUT and CLIN flipflops. Unlike previous 136-type counters, the carry-out outputs will go to a high state during the preset operation. In addition, since the carry-out outputs are registered, they will not go low if terminal count is loaded into the register. The look-ahead-carry-out output functions similarly.

Note from the schematic the use of the master information from the least significant bits for control of the two carry-out functions. This architecture not only reduces the carry-out delay, but is essential to incorporate the registered carry-out functions. In addition to being faster, the resulting carry-out signals are stable and glitch free because these functions are registered.

#### **Cascading Multiple E136 Devices**

Many applications require counters significantly larger than the 6 bits available with the E136. For these applications, several E136 devices can be cascaded to increase the bit width of the counter to meet the needs of the application.

In the past, cascading several 136-type universal counters necessarily impacted the maximum count frequency of the resulting counter chain. This performance impact was the result of the terminal count signal of the lower order counters having to ripple through the entire counter chain. As a result, past counters of this type were not widely used in large bit counter applications.

An alternative counter architecture similar to the E016 binary counter was implemented to alleviate the need to ripple propagate the terminal count signal. Unfortunately, these types of counters require external gating for cascading designs of more than two devices. In addition to requiring additional components, these external gates limit the cascaded count frequency to a value less than the free running count frequency of a single counter. Although there is a performance impact with this type of architecture, it is minor compared to the impact of the ripple propagate designs. As a result, the E016-type counters have been used extensively in applications requiring very high speed, wide bit width synchronous counters.

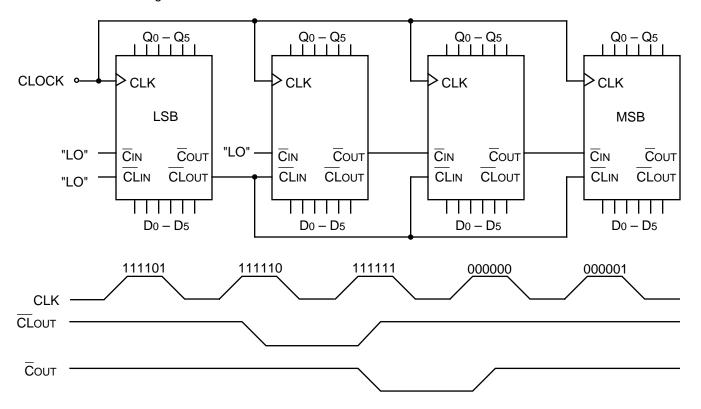

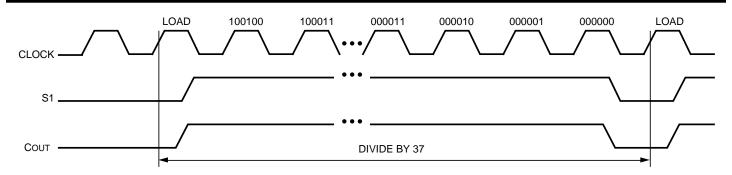

Several improvements have been incorporated to past universal counter designs in the E136 universal counter. These enhancements make the E136 the unparalleled leader in its class. With the addition of look-ahead-carry features on the terminal count signal, very large counter chains can be designed which function at very nearly the same clock frequency as a single free running device. More importantly, these counter chains require no external gating. Figure 1 below illustrates the interconnect scheme for using the look-ahead-carry features of the E136 counter.

Figure 1. 24-bit Cascaded E136 Counter

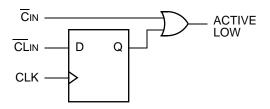

Figure 2. Look-Ahead-Carry Input Structure

Note from the waveforms that the look-ahead-carry output  $(\overline{CL}OUT)$  pulses low one clock pulse before the counter reaches terminal count. Also note that both  $\overline{CL}OUT$  and the carry-out pin  $(\overline{C}OUT)$  of the device pulse low for only one clock period. The input structure for look-ahead-carry-in  $(\overline{CL}IN)$  and carry-in  $(\overline{CIN})$  is pictured in Figure 2.

The  $\overline{\text{CLin}}$  input is registered and then OR'ed with the  $\overline{\text{Cin}}$  input. From the truth table one can see that both the  $\overline{\text{Cin}}$  and the  $\overline{\text{CLin}}$  inputs must be in a LOW state for the E136 to be enabled to count (either count up or count down). The  $\overline{\text{CLin}}$  inputs are driven by the  $\overline{\text{CLout}}$  output of the lower order E136 and, therefore, are only asserted for a single clock period. Since the  $\overline{\text{CLin}}$  input is registered, it must be asserted one clock period prior to the  $\overline{\text{Cin}}$  input.

If the counter previous to a given counter is at terminal count, its  $\overline{\text{C}\text{OUT}}$  output, and thus the  $\overline{\text{C}\text{IN}}$  input of the given counter will be in the "LOW" state. This signals the given counter that it will need to count one upon the next terminal count of the least significant counter (LSC). The  $\overline{\text{C}\text{L}\text{OUT}}$  output of the LSC will pulse low one clock period before it reaches terminal count. This  $\overline{\text{C}\text{L}\text{OUT}}$  signal will be clocked into the  $\overline{\text{C}\text{L}\text{IN}}$  input of the higher order counters on the following positive clock transition. Since both  $\overline{\text{C}\text{IN}}$  and  $\overline{\text{C}\text{L}\text{IN}}$  are in the LOW state, the next clock pulse will cause the least significant counter to roll over and all higher order counters, if signaled by the  $\overline{\text{C}\text{IN}}$  inputs, to count by one.

During the clock pulse in which the higher order counter is counting by one, the  $\overline{\text{CL}}\text{IN}$  is clocking in the high signal presented by the  $\overline{\text{CL}}\text{OUT}$  of the LSC. The  $\overline{\text{CINS}}$  in the higher order counter will ripple through the chain to update the

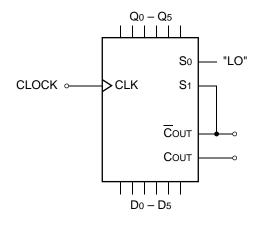

Figure 3. 6-bit Programmable Divider

count status for the next occurrence of terminal count on the LSC. This ripple propagation will not affect the count frequency as it has 2<sup>6</sup>-1 or 63 clock pulses to ripple through without affecting the count operation of the chain.

The only limiting factor which could reduce the count frequency of the chain as compared to a free running single device will be the set-up time of the  $\overline{\text{CL}}\textsc{in}$  input. This limit will consist of the CLK to  $\overline{\text{CL}}\textsc{out}$  delay of the E136, plus the  $\overline{\text{CL}}\textsc{in}$  set-up time, plus any path length differences between the  $\overline{\text{CL}}\textsc{out}$  output and the clock.

#### **Programmable Divider**

Using external feedback of the Cout pin, the E136 can be configured as a programmable divider. Figure 3 illustrates the configuration for a 6-bit count-down programmable divider. If for some reason a count-up divider is preferred, the  $\overline{\text{Cout}}$  signal is simply fed back to S2 rather than S1. Examination of the truth table for the E136 shows that when both S1 and S2 are LOW, the counter will parallel load on the next positive transition of the clock. If the S2 input is low and the S1 input is high, the counter will be in the count-down mode and will count towards an all zero state upon successive clock pulses. Knowing this and the operation of the  $\overline{\text{Cout}}$  output, it becomes a trivial matter to build programmable dividers.

For a programmable divider, one must to load a predesignated number into the counter and count to terminal count. Upon terminal count, the counter should automatically reload the divide number. With the architecture shown in Figure 3, when the counter reaches terminal count, the COUT output, and thus the S1 input, will go LOW. This, combined with the low on S2 will cause the counter to load the inputs present on D0–D5. Upon loading the divide value into the counter, COUT will go HIGH as the counter is no longer at terminal count, thereby placing the counter back into the count mode.

| Divide |    | P  | reset Da | ata Inputs |    |    |

|--------|----|----|----------|------------|----|----|

| Ratio  | D5 | D4 | D3       | D2         | D1 | D0 |

| 2      | L  | L  | L        | L          | L  | Н  |

| 3      | L  | L  | L        | L          | Н  | L  |

| 4      | L  | L  | L        | L          | Н  | Н  |

| 5      | L  | L  | L        | Н          | L  | L  |

| *      | *  | *  | *        | *          | *  | *  |

| *      | *  | *  | *        | *          | *  | *  |

| 36     | Н  | L  | L        | L          | Н  | Н  |

| 37     | Н  | L  | L        | Н          | L  | L  |

| 38     | Н  | L  | L        | Н          | L  | Н  |

| *      | *  | *  | *        | *          | *  | *  |

| *      | *  | *  | *        | *          | *  | *  |

| 62     | Н  | Н  | Н        | Н          | L  | Н  |

| 63     | Н  | Н  | Н        | Н          | Н  | L  |

| 64     | Н  | Н  | Н        | Н          | Н  | Н  |

Table 1. Preset Inputs Versus Divide Ratio

Figure 4. Programmable Divider Waveforms

The exercise of building a programmable divider then becomes simply determining what value to load into the counter to accomplish the desired division. Since the load operation requires a clock pulse, to divide by N, N-1 must be loaded into the counter. A single E136 device is capable of divide ratios of 2 to 64, inclusive. Table 1 outlines the load values for the various divide ratios. Figure 4 presents the waveforms resulting from a divide by 37 operation. Note that the availability of the Cout complimentary output (Cout) allows the user to choose the polarity of the divide by output.

For single device programmable counters, the E016 counter is probably a better choice than the E136. The E016 has an internal feedback to control the reloading of the counter. This not only simplifies board design, but also will result in a faster maximum count frequency.

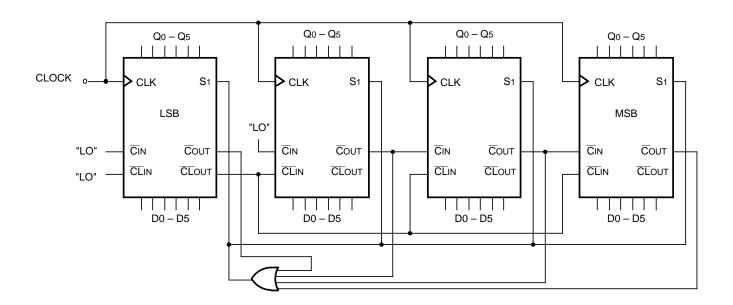

For programmable dividers of larger than 8 bits, the

benefits of the E016 diminishes and, in fact, for very wide dividers, the E136 will provide the capability of a faster count frequency. Figure 5 shows the architecture of a 24-bit programmable divider implemented using E136 counters. Note the need for one external gate to control the loading of the entire counter chain. An ideal device for the external gating of this architecture would be the 4-input OR function in the 8-lead SOIC ECLinPS Lite™ family. However, the final decision as to what device to use for external gating requires a balancing of performance needs, cost and available board space. Note that because of the need for external gating, the maximum count frequency of a given sized programmable divider will be less than that of a single cascaded counter.

Figure 5. 24-bit Programmable Divider Architecture

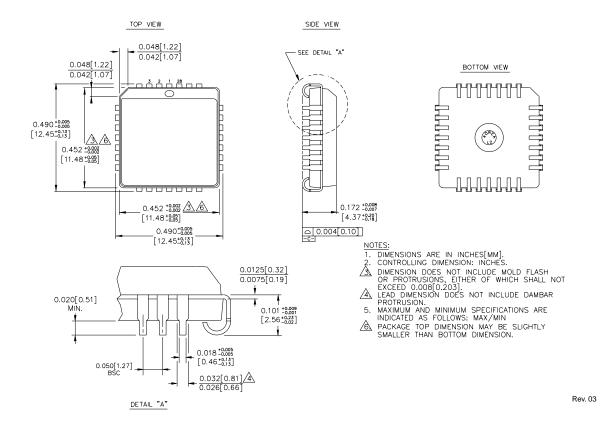

#### 28 LEAD PLCC (J28-1)

MICREL-SYNERGY 3250 SCOTT BOULEVARD SANTA CLARA CA 95054 USA

TEL + 1 (408) 980-9191 FAX + 1 (408) 914-7878 WEB http://www.micrel.com

This information is believed to be accurate and reliable, however no responsibility is assumed by Micrel for its use nor for any infringement of patents or other rights of third parties resulting from its use. No license is granted by implication or otherwise under any patent or patent right of Micrel Inc.

© 2000 Micrel Incorporated