### <sup>Y</sup> 600mA Low V<sub>IN</sub> Buck Regulator in 3mm × 3mm DFN

### FEATURES

- 1.6V to 5.5V Input Voltage Range

- Internal Soft-Start

- Selectable 1.7MHz or 2.6MHz Constant Frequency Operation

- Internal Oscillator can be Synchronizable to an External Clock, 1MHz to 3MHz Range

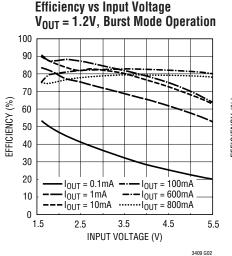

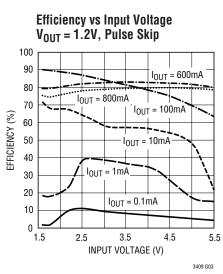

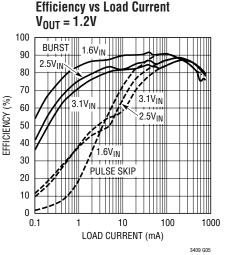

- High Efficiency: Up to 95%

- Very Low Quiescent Current: Only 65µA During Burst Mode<sup>®</sup> Operation

- 600mA Output Current (V<sub>IN</sub> = 1.8V, V<sub>OUT</sub> = 1.2V)

- 750mA Peak Inductor Current

- No Schottky Diode Required

- Low Dropout Operation: 100% Duty Cycle

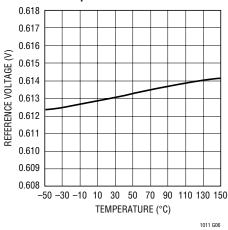

- 0.613V Reference Voltage

- Stable with Ceramic Capacitors

- Shutdown Mode Draws <1µA Supply Current</p>

- Current Mode Operation for Excellent Line and Load Transient Response

- Overtemperature Protection

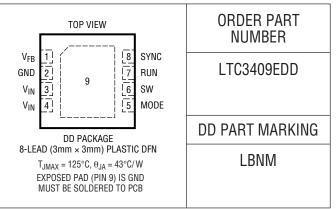

- Available in a Low Profile (0.75mm) 8-Lead (3mm × 3mm) DFN Package

# **APPLICATIONS**

- Cellular Phones

- Digital Cameras

- MP3 Players

# DESCRIPTION

The LTC<sup>®</sup>3409 is a high efficiency, monolithic synchronous buck regulator using a constant frequency, current mode architecture. The output voltage is adjusted via an external resistor divider.

Fixed switching frequencies of 1.7MHz and 2.6MHz are supported. Alternatively, an internal PLL will synchronize to an external clock in the frequency range of 1MHz to 3MHz. This range of switching frequencies allows the use of small surface mount inductors and capacitors, including ceramics.

Supply current during Burst Mode operation is only  $65\mu$ A dropping to  $<1\mu$ A in shutdown. The 1.6V to 5.5V input voltage range makes the LTC3409 ideally suited for single cell Li-Ion, Li-Metal and 2-cell alkaline, NiCd or NiMH battery-powered applications. 100% duty cycle capability provides low dropout operation, extending battery life in portable systems. Burst Mode operation can be user-enabled, increasing efficiency at light loads, further extending battery life.

The internal synchronous switch increases efficiency and eliminates the need for an external Schottky diode. Internal soft-start offers controlled output voltage rise time at start-up without the need for external components.

∠7, LTC and LT are registered trademarks of Linear Technology Corporation. Burst Mode is a registered trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents, including 5481178, 6580258, 6304066, 6127815, 6498466, 6611131.

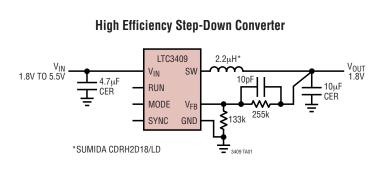

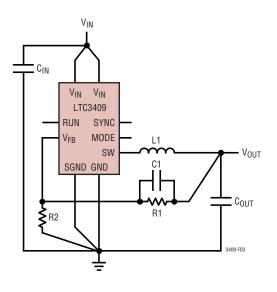

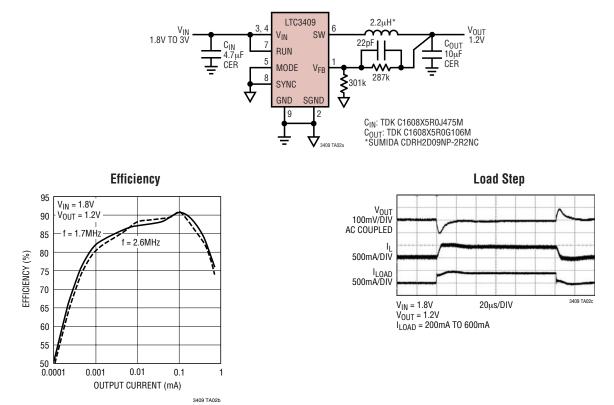

# TYPICAL APPLICATION

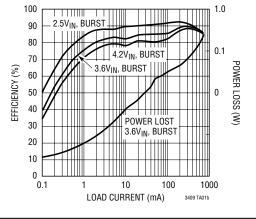

#### Burst Mode Efficiency, 1.8V<sub>OUT</sub>

### **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

# PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges.

### **ELECTRICAL CHARACTERISTICS**

The  $\bullet$  denotes specifications which apply over the full operating temperature range, otherwise specifications are T<sub>A</sub> = 25°C. V<sub>IN</sub> = 2.2V unless otherwise specified.

| SYMBOL                | PARAMETER                                                      | CONDITIONS                                                                                                                       |   | MIN                        | ТҮР                        | MAX                        | UNITS          |

|-----------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---|----------------------------|----------------------------|----------------------------|----------------|

| V <sub>RUN</sub>      | RUN Threshold                                                  |                                                                                                                                  |   | 0.3                        | 0.65                       | 1.1                        | V              |

| I <sub>RUN</sub>      | RUN Leakage Current                                            |                                                                                                                                  |   |                            | 0.01                       | 1                          | μA             |

| V <sub>MODE</sub>     | MODE Threshold                                                 |                                                                                                                                  | • | 0.3                        | 0.65                       | 1.1                        | V              |

| I <sub>MODE</sub>     | MODE Leakage Current                                           |                                                                                                                                  |   |                            | 0.01                       | 1                          | μA             |

| V <sub>SYNCTH</sub>   | SYNC Threshold                                                 |                                                                                                                                  | • | 0.3                        | 0.65                       | 1.1                        | V              |

| ISYNC                 | SYNC Leakage Current                                           |                                                                                                                                  |   |                            | 0.01                       | 1                          | μA             |

| V <sub>FB</sub>       | Regulated Feedback Voltage                                     | (Note 4) $T_A = 25^{\circ}C$<br>(Note 4) $0^{\circ}C \le T_A \le 85^{\circ}C$<br>(Note 4) $-40^{\circ}C \le T_A \le 85^{\circ}C$ | • | 0.6007<br>0.5992<br>0.5977 | 0.6130<br>0.6130<br>0.6130 | 0.6252<br>0.6268<br>0.6283 | V<br>V<br>V    |

| I <sub>VFB</sub>      | Feedback Current                                               |                                                                                                                                  |   |                            |                            | ±30                        | nA             |

| $\Delta V_{OVL}$      | ΔV <sub>FBOVL</sub> Overvoltage Lockout                        | $\Delta V_{OVL} = \Delta V_{FBOVL} - V_{FB}$ (Note 6)                                                                            |   | 35                         | 61                         | 85                         | mV             |

| $\Delta V_{FB}$       | Reference Voltage Line Regulation                              | (Note 4)                                                                                                                         | • |                            | 0.04                       | 0.4                        | %/V            |

| $\Delta V_{OUT}$      | Output Voltage Line Regulation                                 | I <sub>OUT</sub> = 100mA, 1.6V < V <sub>IN</sub> < 5.5V                                                                          |   |                            | 0.04                       | 0.4                        | %/V            |

| I <sub>PK</sub>       | Peak Inductor Current                                          | $V_{IN} = 2.2V, V_{FB} = 0.5V \text{ or } V_{OUT} = 90\%, \\ Duty \ Cycle < 35\%$                                                |   | 0.75                       | 1                          | 1.3                        | A              |

| VLOADREG              | Output Voltage Load Regulation                                 |                                                                                                                                  |   |                            | 0.5                        |                            | %              |

| VIN                   | Input Voltage Range                                            |                                                                                                                                  | • | 1.6                        |                            | 5.5                        | V              |

| Is                    | Input DC Bias Current<br>Active Mode<br>Sleep Mode<br>Shutdown | (Note 5)<br>$V_{OUT} = 90\%$ , $I_{LOAD} = 0A$<br>$V_{OUT} = 103\%$ , $I_{LOAD} = 0A$<br>$V_{RUN} = 0V$ , $V_{IN} = 5.5V$        |   |                            | 350<br>65<br>0.1           | 475<br>120<br>5            | μΑ<br>μΑ<br>μΑ |

| f <sub>OSC</sub>      | Nominal Oscillator Frequency                                   | SYNC = GND<br>SYNC = V <sub>IN</sub>                                                                                             | • | 0.9<br>1.8                 | 1.7<br>2.6                 | 2.1<br>3.0                 | MHz<br>MHz     |

| SYNC TH               | SYNC Threshold                                                 | When SYNC Input is Toggling (Note 7)                                                                                             |   |                            | 0.63                       |                            | V              |

| SYNC f <sub>MIN</sub> | Minimum SYNC Pin Frequency                                     |                                                                                                                                  |   |                            | 1                          |                            | MHz            |

| SYNC f <sub>MAX</sub> | Maximum SYNC Pin Frequency                                     |                                                                                                                                  |   |                            | 3                          |                            | MHz            |

| SYNC PW               | Minimum SYNC Pulse Width                                       |                                                                                                                                  |   |                            | 100                        |                            | ns             |

| t <sub>SS</sub>       | Soft-Start Period                                              | RUN↑                                                                                                                             |   |                            | 1                          |                            | ms             |

3409f

### **ELECTRICAL CHARACTERISTICS**

The  $\bullet$  denotes specifications which apply over the full operating temperature range, otherwise specifications are T<sub>A</sub> = 25°C. V<sub>IN</sub> = 2.2V unless otherwise specified.

| SYMBOL            | PARAMETER                            | CONDITIONS                                                                       | MIN | ТҮР          | MAX | UNITS  |

|-------------------|--------------------------------------|----------------------------------------------------------------------------------|-----|--------------|-----|--------|

| SYNC to           | SYNC Timeout                         | Delay from Removal of EXT CLK Until Fixed<br>Frequency Operation Begins (Note 7) |     | 30           |     | μS     |

| R <sub>PFET</sub> | R <sub>DS(ON)</sub> of P-Channel FET | I <sub>SW</sub> = 100mA, Wafer Level<br>I <sub>SW</sub> = 100mA, DD Package      |     | 0.33<br>0.35 |     | Ω<br>Ω |

| R <sub>NFET</sub> | R <sub>DS(ON)</sub> of N-Channel FET | I <sub>SW</sub> = 100mA, Wafer Level<br>I <sub>SW</sub> = 100mA, DD Package      |     | 0.22<br>0.25 |     | Ω<br>Ω |

| I <sub>LSW</sub>  | SW Leakage                           | $V_{RUN} = 0V, V_{SW} = 0V \text{ or } 5V, V_{IN} = 5V$                          |     | ±0.1         | ±3  | μA     |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** The LTC3409E is guaranteed to meet performance specifications from 0°C to 70°C. Specifications over the –40°C to 85°C operating temperature range are assured by design, characterization and correlation with statistical process controls.

**Note 3:**  $T_J$  is calculated from the ambient temperature  $T_A$  and power dissipation  $P_D$  according to the following formula:

LTC3409:  $T_J = T_A + (P_D)(43^{\circ}C/W)$

This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. Overtemperature protection becomes active at a junction temperature greater than the maximum operating junction temperature. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

**Note 4:** The LTC3409 is tested in a proprietary test mode that connects  $V_{FB}$  to the output of the error amplifier.

**Note 5:** Dynamic supply current is higher due to the gate charge being delivered at the switching frequency.

Note 6:  $\Delta V_{OVL}$  is the amount  $V_{FB}$  must exceed the regulated feedback voltage.

Note 7: Determined by design, not production tested.

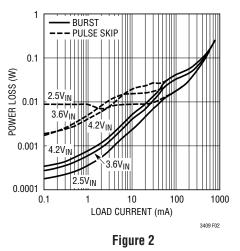

6: 4.2VIN, PULSE SKIP

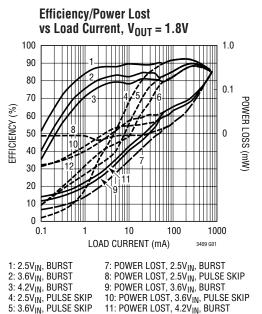

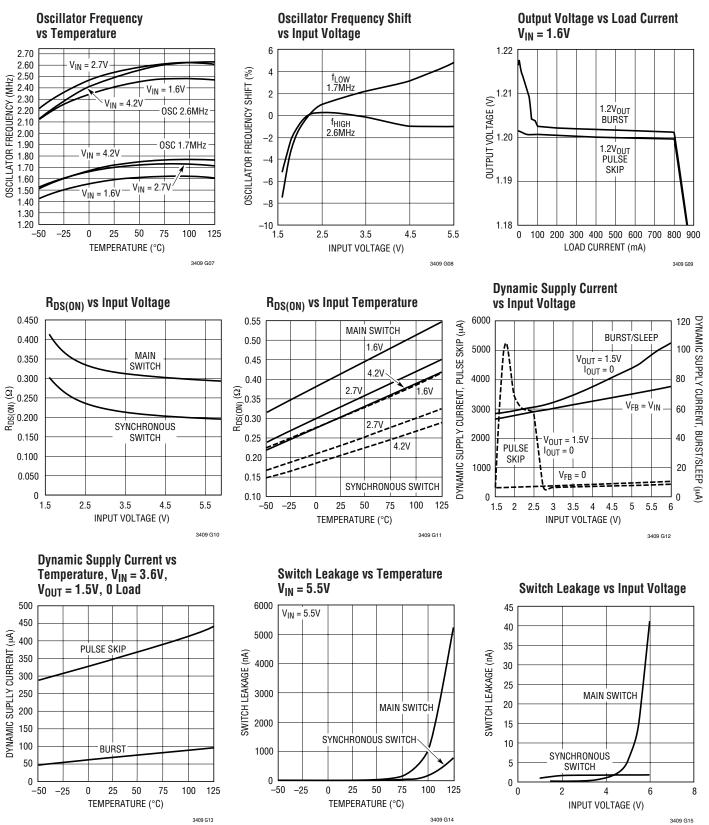

## TYPICAL PERFORMANCE CHARACTERISTICS

(From Typical Application on the front page except for the resistive divider resistor values)

12: POWER LOST, 4.2VIN, PULSE SKIP

#### **Efficiency vs Load Current** $V_{OUT} = 2.5V$ 100 BURST 90 2.7V<sub>1</sub> 80 4.2V<sub>IN</sub> 70 3.6V<sub>IN</sub> EFFICIENCY (%) 60 ⊹3.6V<sub>IN</sub> 50 4.2V<sub>IN</sub> 2.7V<sub>IN</sub> 40 PULSE SKIP 30 20 10 0 0.1 10 100 1000 LOAD CURRENT (mA) 3409 G04

#### Reference Voltage vs Temperature

34091

### **TYPICAL PERFORMANCE CHARACTERISTICS**

(From Typical Application on the front page except for the resistive divider resistor values)

TECHNOLOGY

Downloaded from Elcodis.com electronic components distributor

### TYPICAL PERFORMANCE CHARACTERISTICS

(From Typical Application on the front page except for the resistive divider resistor values)

3409f

### **PIN FUNCTIONS**

**V<sub>FB</sub> (Pin 1):** Feedback Pin. Receives the feedback voltage from an external resistive divider across the output.

GND (Pin 2): Ground Pin.

$V_{IN}$  (Pins 3, 4): Main Supply Pins. Must be closely decoupled to GND, Pin 2 and Pin 9, with a 4.7  $\mu$ F or greater ceramic capacitor.

**MODE (Pin 5):** Mode Select Input. To select pulse skipping mode, force this pin above 1.1V. Forcing this pin below 0.3V selects Burst Mode operation. Do not leave MODE floating.

**SW (Pin 6):** Switch Node Connection to Inductor. This pin connects to the drains of the internal main and synchronous power MOSFET switches.

**RUN (Pin 7):** Run Control Input. Forcing this pin above 1.1V enables the part. Forcing this pin below 0.3V shuts down the device. In shutdown, all functions are disabled drawing  $<1\mu$ A supply current. Do not leave RUN floating.

**SYNC (Pin 8):** External CLK Input/Fixed Switching Frequency Selection. Forcing this pin above 1.1V for greater than  $30\mu$ s selects 2.6MHz switching frequency. Forcing this pin below 0.3V for greater than  $30\mu$ s selects 1.7MHz switching frequency.

External clock input, 1MHz to 3MHz frequency range. When the SYNC pin is clocked in this frequency range the SYNC threshold is nominally 0.63V. To allow for good noise immunity, SYNC signal should swing at least 0.3V below and above this nominal value (0.33V to 0.93V). Do not leave SYNC floating.

**GND (Pin 9):** Exposed Pad. The Exposed Pad is ground. It must be soldered to PCB ground to provide both electrical contact and optimum thermal performance.

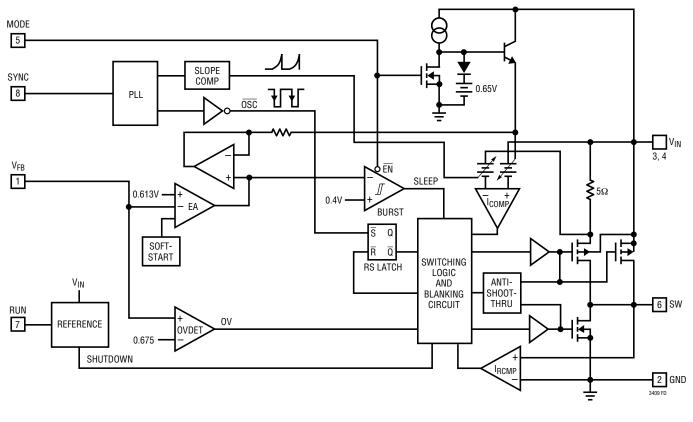

# FUNCTIONAL DIAGRAM

# OPERATION

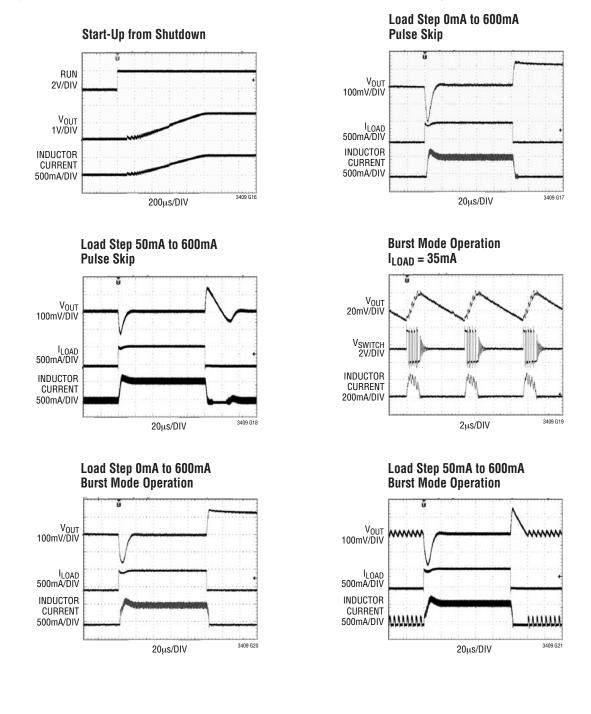

### Main Control Loop

The LTC3409 uses a constant frequency, current mode step-down architecture. Both the main (P-channel MOSFET) and synchronous (N-channel MOSFET) switches are internal. During normal operation, the internal top power MOSFET is turned on each cycle when the oscillator sets the RS latch, and turned off when the current comparator, I<sub>COMP</sub>, resets the RS latch. The peak inductor current at which I<sub>COMP</sub> resets the RS latch is controlled by the output of error amplifier EA. The V<sub>FB</sub> pin, described in the Pin Functions section, allows EA to receive an output feedback voltage from an external resistive divider. When the load current increases, it causes a slight decrease in the feedback voltage relative to the 0.613V reference, which in turn, causes the EA amplifier's output voltage to increase until the average inductor current matches the new load current. While the top MOSFET is off, the bottom MOSFET is turned on until either the inductor current starts to reverse, as indicated by the current reversal comparator  $I_{\text{RCMP}},$  or the beginning of the next clock cycle.

Comparator OVDET guards against transient overshoots >10% by turning the main switch off and keeping it off until the transient has ended.

### **Burst Mode Operation**

The LTC3409 is capable of Burst Mode operation in which the internal power MOSFETs operate intermittently based on load demand. To enable Burst Mode operation, simply connect the MODE pin to GND. To disable Burst Mode operation and enable PWM pulse skipping mode, connect the MODE pin to V<sub>IN</sub> or drive it with a logic high (V<sub>MODE</sub> >1.1V). In this mode, the efficiency is lower at light loads, but becomes comparable to Burst Mode operation when the output load exceeds 30mA. The advantage of pulse

### OPERATION

skipping mode is lower output ripple and less interference to audio circuitry. When the converter is in Burst Mode operation, the minimum peak current of the inductor is set to approximately 200mA regardless of the output load. Each burst event can last from a few cycles at light loads to almost continuously cycling with short sleep intervals at moderate loads. In between these burst events, the power MOSFETs and any unneeded circuitry are turned off, reducing the quiescent current to  $65\mu$ A. In this sleep state, the load current is being supplied solely from the output capacitor. As the output voltage droops, the EA amplifier's output rises above the sleep threshold signaling the BURST comparator to trip and turn the top MOSFET on. This process repeats at a rate that is dependent on the load demand.

### **Short-Circuit Protection**

When the output is shorted to ground the LTC3409 limits the synchronous switch current to 1.5A. If this limit is exceeded, the top power MOSFET is inhibited from turning on until the current in the synchronous switch falls below 1.5A.

### **Dropout Operation**

As the input supply voltage decreases to a value approaching the output voltage, the duty cycle increases toward the maximum on-time. Further reduction of the supply voltage forces the main switch to remain on for more than one cycle.

### **Slope Compensation**

Slope compensation provides stability in constant frequency architectures by preventing subharmonic oscillations at high duty cycles. It is accomplished internally by adding a compensating ramp to the inductor current signal at duty cycles in excess of 40%.

#### **User Controlled Switching Frequency**

The internal oscillator of the LTC3409 can be synchronized to a user-supplied external clock applied to the SYNC pin. Alternately, when this pin is held at a fixed High or Low level for more than  $30\mu$ s, the internal oscillator will revert to fixed-frequency operation; where the frequency may be selected as 1.7MHz (SYNC Low) or 2.6MHz (SYNC High).

#### **Internal Soft-Start**

At start-up when the RUN pin is brought high, the internal reference is linearly ramped from 0V to 0.613V in 1ms. The regulated feedback voltage will follow this ramp resulting in the output voltage ramping from 0% to 100% in 1ms. The current in the inductor during soft-start will be defined by the combination of the current needed to charge the output capacitance and the current provided to the load as the output voltage ramps up. The start-up waveform, shown in the Typical Performance Characteristics, shows the output voltage start-up from 0V to 1.5V with a 2.5 $\Omega$  load and V<sub>IN</sub> = 2.2V. The 2.5 $\Omega$  load results in an output of 600mA at 1.5V.

The basic LTC3409 application circuit is shown on the first page of this data sheet. External component selection is driven by the load requirement and begins with the selection of L followed by  $C_{\rm IN}$  and  $C_{\rm OUT}$ .

#### **Inductor Selection**

For most applications, the value of the inductor will fall in the range of  $1\mu$ H to  $10\mu$ H. Its value is chosen based on the desired ripple current. Large value inductors lower ripple current and small value inductors result in higher ripple currents. Higher V<sub>IN</sub> or V<sub>OUT</sub> also increases the ripple current as shown in Equation 1. A reasonable starting point for setting ripple current is  $\Delta I_L = 240$ mA (40% of 600mA).

$$\Delta I_{L} = \frac{1}{f \bullet L} V_{OUT} \left( 1 - \frac{V_{OUT}}{V_{IN}} \right)$$

(1)

The DC current rating of the inductor should be at least equal to the maximum load current plus half the ripple current to prevent core saturation. Thus, a 720mA rated inductor should be enough for most applications (600mA + 120mA). For better efficiency, choose a low DC resistance inductor. The inductor value also has an effect on Burst Mode operation. The transition to low current operation begins when the inductor current peaks fall to approximately 200mA. Lower inductor values (higher  $\Delta I_L$ ) will cause this to occur at lower load currents, which can cause a dip in efficiency in the upper range of low current operation. In Burst Mode operation, lower inductance values will cause the burst frequency to increase.

#### **Inductor Core Selection**

Different core materials and shapes will change the size/ current and price/current relationship of an inductor. Toroid or shielded pot cores in ferrite or permalloy materials are small and don't radiate much energy, but generally cost more than powdered iron core inductors with similar electrical characteristics. The choice of which style inductor to use often depends more on the price vs size requirements and any radiated field/EMI requirements than on what the LTC3409 requires to operate. Table 1 shows some typical surface mount inductors that work well in LTC3409 applications.

| PART        | VALUE | DCR     | MAX DC      | SIZE $W \times L \times H \ (mm^3)$ |

|-------------|-------|---------|-------------|-------------------------------------|

| Number      | (μΗ)  | (Ω MAX) | CURRENT (A) |                                     |

| Sumida      | 2.2   | 0.041   | 0.85        | 3.2 × 3.2 × 2.0                     |

| CDRH3D18/LD | 3.3   | 0.054   | 0.75        |                                     |

| Sumida      | 1.5   | 0.068   | 0.90        | 3.2 × 3.2 × 1.2                     |

| CDRH2D11    | 2.2   | 0.170   | 0.78        |                                     |

| Sumida      | 2.2   | 0.116   | 0.950       | 4.4 × 5.8 × 1.2                     |

| CMD4D11     | 3.3   | 0.174   | 0.770       |                                     |

| Murata      | 1.0   | 0.060   | 1.00        | 2.5 × 3.2 × 2.0                     |

| LQH32CN     | 2.2   | 0.097   | 0.79        |                                     |

| Toko        | 2.2   | 0.060   | 1.08        | 2.5 × 3.2 × 2.0                     |

| D312F       | 3.3   | 0.260   | 0.92        |                                     |

| Panasonic   | 3.3   | 0.17    | 1.00        | 4.5 × 5.4 × 1.2                     |

| ELT5KT      | 4.7   | 0.20    | 0.95        |                                     |

#### Table 1. Representative Surface Mount Inductors

### $C_{\text{IN}}$ and $C_{\text{OUT}}$ Selection

In continuous mode, the source current of the top MOS-FET is a square wave of duty cycle  $V_{OUT}/V_{IN}$ . To prevent large voltage transients, a low ESR input capacitor sized for the maximum RMS current must be used. The maximum RMS capacitor current is given by:

$$C_{IN}$$

Required  $I_{RMS} \approx I_{OUT(MAX)} \frac{\left[V_{OUT}(V_{IN} - V_{OUT})\right]^{1/2}}{V_{IN}}$

This formula has a maximum at  $V_{IN} = 2V_{OUT}$ , where  $I_{RMS} = I_{OUT}/2$ . This simple worst-case condition is commonly used for design because even significant deviations do not offer much relief. Note that the capacitor manufacturer's ripple current ratings are often based on 2000 hours of life. This makes it advisable to further derate the capacitor, or choose a capacitor rated at a higher temperature than required. Always consult the manufacturer if there is any question. The selection of  $C_{OUT}$  is driven by the required effective series resistance (ESR). Typically, once the ESR requirement for  $C_{OUT}$  has been met, the RMS current rating generally far exceeds the  $I_{RIPPLE(P-P)}$  requirement. The output ripple DV<sub>OUT</sub> is determined by:

$$\Delta V_{\text{OUT}} = \Delta I_{\text{L}} \left( \text{ESR} + \frac{1}{8 \bullet f \bullet C_{\text{OUT}}} \right)$$

where f = operating frequency,  $C_{OUT}$  = output capacitance and  $\Delta I_L$  = ripple current in the inductor. For a fixed output voltage, the output ripple is highest at maximum input voltage since  $\Delta I_L$  increases with input voltage. Aluminum electrolytic and dry tantalum capacitors are both available in surface mount configurations. In the case of tantalum, it is critical that the capacitors are surge tested for use in switching power supplies. An excellent choice is the AVX TPS series of surface mount tantalum. These are specially constructed and tested for low ESR so they give the lowest ESR for a given volume. Other capacitor types include Sanyo POSCAP, Kemet T510 and T495 series, and Sprague 593D and 595D series. Consult the manufacturer for other specific recommendations.

#### **Using Ceramic Input and Output Capacitors**

Higher value, lower cost ceramic capacitors are now available in smaller case sizes. Their high ripple current, high voltage rating and low ESR make them ideal for switching regulator applications. Because the LTC3409's control loop does not depend on the output capacitor's ESR for stable operation, ceramic capacitors can be used to achieve very low output ripple and small circuit size.

However, care must be taken when these capacitors are used at the input and the output. When a ceramic capacitor is used at the input and the power is supplied by a wall adapter through long wires, a load step at the output can induce ringing at the input,  $V_{IN}$ . At best, this ringing can couple to the output and be mistaken as loop instability. At worst, a sudden inrush of current through the long wires can potentially cause a voltage spike at  $V_{IN}$ , large enough to damage the part.

When choosing the input and output ceramic capacitors, choose the X5R or X7R dielectric formulations. These dielectrics have the best temperature and voltage characteristics of all the ceramics for a given value and size.

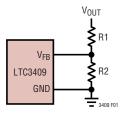

#### **Output Voltage Programming**

The output voltage is set by a resistive divider according to the following formula:

$$V_{OUT} = 0.613V \left(1 + \frac{R1}{R2}\right)$$

The external resistive divider is connected to the output, allowing remote voltage sensing as shown in Figure 1.

Figure 1

### **Efficiency Considerations**

The efficiency of a switching regulator is equal to the output power divided by the input power times 100%. It is often useful to analyze individual losses to determine what is limiting the efficiency and which change would produce the most improvement. Efficiency can be expressed as:

Efficiency = 100% - (L1 + L2 + L3 + ...)

where L1, L2, etc. are the individual losses as a percentage of input power.

Although all dissipative elements in the circuit produce losses, two main sources usually account for most of the losses in LTC3409 circuits:  $V_{IN}$  quiescent current and  $I^2R$  losses. The  $V_{IN}$  quiescent current loss dominates the efficiency loss at very low load currents whereas the  $I^2R$  loss dominates the efficiency loss at medium to high load currents. In a typical efficiency plot, the efficiency curve at very low load currents can be misleading since the actual power lost is of no consequence as illustrated in Figure 2.

- 1. The V<sub>IN</sub> quiescent current is due to two components: the DC bias current as given in the Electrical Characteristics and the internal main switch and synchronous switch gate charge currents. The gate charge current results from switching the gate capacitance of the internal power MOSFET switches. Each time the gate is switched from high to low to high again, a packet of charge, dQ, moves from V<sub>IN</sub> to ground. The resulting dQ/dt is the current out of V<sub>IN</sub> that is typically larger than the DC bias current. In continuous mode, I<sub>GATECHG</sub> = (Q<sub>T</sub> + Q<sub>B</sub>) where Q<sub>T</sub> and Q<sub>B</sub> are the gate charges of the internal top and bottom switches. Both the DC bias and gate charge losses are proportional to V<sub>IN</sub> and thus their effects will be more pronounced at higher supply voltages.

- 2. I<sup>2</sup>R losses are calculated from the resistances of the internal switches,  $R_{SW}$ , and external inductor  $R_L$ . In continuous mode, the average output current flowing through inductor L is "chopped" between the main switch and the synchronous switch. Thus, the series resistance looking into the SW pin is a function of both top and bottom MOSFET  $R_{DS(ON)}$  and the duty cycle (DC) as follows:

$$R_{SW} = (R_{DS(ON)TOP})(DC) + (R_{DS(ON)BOT})(1 - DC)$$

The  $R_{DS(ON)}$  for both the top and bottom MOSFETs can be obtained from the Typical Performance Characteristics. Thus, to obtain  $I^2R$  losses, simply add  $R_{SW}$  to  $R_L$  and multiply the result by the square of the average output current.

Other losses including  $C_{\rm IN}$  and  $C_{\rm OUT}$  ESR dissipative losses and inductor core losses generally account for less than 2% total additional loss.

#### **Thermal Considerations**

In most applications the LTC3409 does not dissipate much heat due to its high efficiency. But, in applications where the LTC3409 is running at high ambient temperature with low supply voltage and high duty cycles, such as in dropout, the heat dissipated may exceed the maximum junction temperature of the part. If the junction temperature reaches approximately 150°C, both power switches will be turned off and the SW node will become high impedance.

To avoid the LTC3409 from exceeding the maximum junction temperature, the user will need to do a thermal analysis. The goal of the thermal analysis is to determine whether the operating conditions exceed the maximum junction temperature of the part. The temperature rise is given by:

$T_{R} = (P_{D})(\theta_{JA})$

where  $P_D$  is the power dissipated by the regulator and  $\theta_{JA}$  is the thermal resistance from the junction of the die to the ambient temperature.

The junction temperature, T<sub>J</sub>, is given by:

$$T_J = T_A + T_R$$

where  $T_A$  is the ambient temperature.

As an example, consider the LTC3409 in dropout at an input voltage of 1.6V, a load current of 600mA and an ambient temperature of 75°C. From the typical performance graph of switch resistance, the  $R_{DS(ON)}$  of the P-channel switch at 75°C is approximately 0.48 $\Omega$ . Therefore, power dissipated by the part is:

$$P_{D} = I_{LOAD}^{2} \bullet R_{DS(ON)} = 172.8 \text{mW}$$

For the DD8 package, the  $\theta_{JA}$  is 43°C/W. Thus, the junction temperature of the regulator is:

$T_J = 75^{\circ}C + (0.1728)(43) = 82.4^{\circ}C$

which is well below the maximum junction temperature of 125°C.

Note that at higher supply voltages, the junction temperature is lower due to reduced switch resistance  $(R_{DS(ON)})$ .

#### **Checking Transient Response**

The regulator loop response can be checked by looking at the load transient response. Switching regulators take several cycles to respond to a step in load current. When a load step occurs,  $V_{OUT}$  immediately shifts by an amount equal to ( $\Delta I_{LOAD} \bullet ESR$ ), where ESR is the effective series resistance of  $C_{OUT}$ .  $\Delta I_{LOAD}$  also begins to charge or discharge  $C_{OUT}$ , which generates a feedback error signal. The regulator loop then acts to return  $V_{OUT}$  to its steady state value. During this recovery time  $V_{OUT}$  can be monitored for overshoot or ringing that would indicate a stability problem. For a detailed explanation of switching control loop theory, see Application Note 76.

A second, more severe transient is caused by switching in loads with large (>1µF) supply bypass capacitors. The discharged bypass capacitors are effectively put in parallel with  $C_{OUT}$ , causing a rapid drop in  $V_{OUT}$ . No regulator can deliver enough current to prevent this problem if the load switch resistance is low and it is driven quickly. The only solution is to limit the rise time of the switch drive so that the load rise time is limited to approximately (25 •  $C_{LOAD}$ ). Thus, a 10µF capacitor charging to 3.3V would require a 250µs rise time, limiting the charging current to about 130mA.

#### **Board Layout Considerations**

When laying out the printed circuit board, the following checklist should be used to ensure proper operation of the LTC3409. These items are also illustrated graphically in the layout diagram of Figure 3. Check the following in your layout.

1. Does the capacitor  $C_{IN}$  connect to the power  $V_{IN}$  (Pins 3, 4) and GND (Exposed Pad) as close as possible? This capacitor provides the AC current to the internal power MOSFETs and their drivers.

- 2. Are the  $C_{OUT}$  and L1 closely connected? The (–) plate of  $C_{OUT}$  returns current to GND and the (–) plate of  $C_{IN}$ .

- 3. The resistor divider, R1 and R2, must be connected between the (+) plate of  $C_{OUT}$  and a ground sense line terminated near GND (Exposed Pad). The feedback signals V<sub>FB</sub> should be routed away from noisy components and traces, such as the SW line (Pins 6), and its trace should be minimized.

- 4. Keep sensitive components away from the SW pins. The input capacitor  $C_{\rm IN}$  and the resistors R1 and R2 should be routed away from the SW traces and the inductors.

- 5. A ground plane is preferred, but if not available, keep the signal and power grounds segregated with small signal components returning to the GND pin at one point. They should not share the high current path of  $C_{IN}$  or  $C_{OUT}$ .

- 6. Flood all unused areas on all layers with copper. Flooding with copper will reduce the temperature rise of power components. These copper areas should be connected to  $V_{\text{IN}}$  or GND.

Figure 3

3409

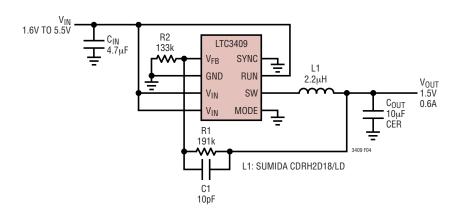

#### **Design Example**

As a design example, assume the LTC3409 is used in a 2-alkaline cell battery-powered application. The  $V_{IN}$  will be operating from a maximum of 3.2V down to about 1.8V. The load current requirement is a maximum of 600mA but most of the time it will be in standby mode, requiring only 2mA. Efficiency at both low and high load currents is important. Output voltage is 1.5V. With this information we can calculate L using Equation 2:

$$L = \frac{1}{f \bullet \Delta I_L} V_{OUT} \left( 1 - \frac{V_{OUT}}{V_{IN}} \right)$$

(2)

Substituting V<sub>OUT</sub> = 1.5V, V<sub>IN</sub> = 3.2V,  $\Delta I_L$  = 240mA and f = 1.7MHz in Equation 2 gives:

$$L = \frac{1}{1.7 \text{MHz} \bullet 240 \text{mA}} 1.5 \left( 1 - \frac{1.5}{3.2} \right) \approx 2.2 \mu \text{H}$$

For best efficiency choose a 750mA or greater inductor with less than  $0.3\Omega$  series resistance.  $C_{IN}$  will require an RMS current rating of at least  $0.3A \cong I_{LOAD(MAX)}/2$  at temperature.

For the feedback resistors, choose R2 = 133k. R1 can then be calculated from Equation 2 at 191K. Figure 4 shows the complete circuit along with its efficiency curve.

Table 2 below gives 1% resistor values for selected output voltages.

| V <sub>OUT</sub> | R1    | R2   |

|------------------|-------|------|

| 0.85V            | 51.1k | 133k |

| 1.2V             | 127k  | 133k |

| 1.5V             | 191k  | 133k |

| 1.8V             | 255k  | 133k |

.8V<sub>IN</sub>

100

90

80

70

60

50

40

30

20 10

0

0.1

EFFICIENCY (%)

Burst Mode Efficiency, 1.5V<sub>OUT</sub>

3.2V<sub>IN</sub>

10

LOAD CURRENT (mA)

2.5V<sub>IN</sub>

Figure 4

100

1000

3409 F04b

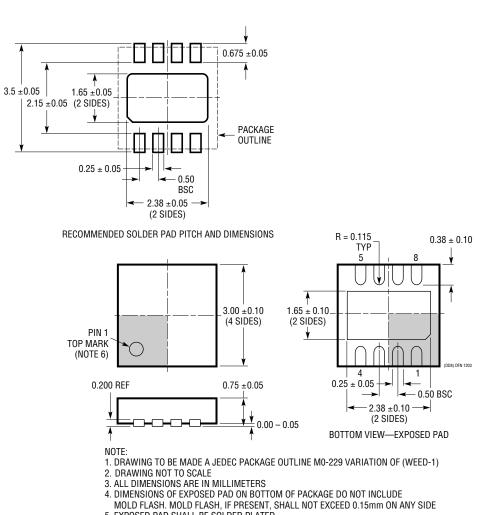

### PACKAGE DESCRIPTION

**DD Package** 8-Lead Plastic DFN (3mm × 3mm) (Reference LTC DWG # 05-08-1698)

5. EXPOSED PAD SHALL BE SOLDER PLATED

6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION

ON TOP AND BOTTOM OF PACKAGE

### TYPICAL APPLICATION

#### 2-Cell to 1.2V/600mA Regulator for High Efficiency and Low Profile

### **RELATED PARTS**

| PART NUMBER                                                                                 | DESCRIPTION                                                                                                                                                                                        | COMMENTS                                                                                                                                                                                       |  |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LTC1878                                                                                     | 600mA (I <sub>OUT</sub> ), 550kHz, Synchronous Step-Down<br>DC/DC Converter                                                                                                                        | 96% Efficiency, V <sub>IN</sub> : 2.7V to 6V, V <sub>OUT(MIN)</sub> = 0.8V, I <sub>Q</sub> = 10µA, I <sub>SD</sub> < 1µA, MS8 Package                                                          |  |

| LTC1879                                                                                     | 1.20A (I <sub>OUT</sub> ), 550kHz, Synchronous Step-Down<br>DC/DC Converter                                                                                                                        | 95% Efficiency, V <sub>IN</sub> : 2.7V to 10V, V <sub>OUT(MIN)</sub> = 0.8V, I <sub>Q</sub> = 15 $\mu$ A, I <sub>SD</sub> < 1 $\mu$ A, 16-Lead TSSOP                                           |  |

| LT3020                                                                                      | 100mA, Low Voltage VLDO™                                                                                                                                                                           | $ \begin{array}{l} V_{IN}: \ 0.9V \ to \ 10V, \ V_{OUT(MIN)} = 0.20V, \ Dropout \ Voltage = 0.15V, \\ I_Q = 120 \mu A, \ I_{SD} < 3 \mu A, \ V_{OUT} = ADJ, \ DFN/MS8 \ Packages \end{array} $ |  |

| LTC3025                                                                                     | 100mA, Low Voltage VLDO                                                                                                                                                                            | $V_{IN}$ : 0.9V to 5.5V, $V_{OUT(MIN)}$ = 0.40V, Dropout Voltage = 0.05V, $I_Q$ = 54µA, $I_{SD}$ < 1µA, $V_{OUT}$ = ADJ, DFN Package                                                           |  |

| LTC3404                                                                                     | 600mA (I <sub>OUT</sub> ), 1.4MHz, Synchronous Step-Down<br>DC/DC Converter                                                                                                                        | 96% Efficiency, V <sub>IN</sub> : 2.7V to 6V, V <sub>OUT(MIN)</sub> = 0.8V, I <sub>Q</sub> = 10µA, I <sub>SD</sub> < 1µA, MS8 Package                                                          |  |

| TC3405/LTC3405A 300mA (I <sub>OUT</sub> ), 1.5MHz, Synchronous Step-Down<br>DC/DC Converter |                                                                                                                                                                                                    | 95% Efficiency, V <sub>IN</sub> : 2.5V to 5.5V, V <sub>OUT(MIN)</sub> = 0.8V, I <sub>Q</sub> = 20 $\mu$ A, I <sub>SD</sub> < 1 $\mu$ A, ThinSOT <sup>TM</sup> Package                          |  |

| LTC3406/LTC3406B 600mA (I <sub>OUT</sub> ), 1.5MHz, Synchronous Step-Down DC/DC Converter   |                                                                                                                                                                                                    | 96% Efficiency, V <sub>IN</sub> : 2.5V to 5.5V, V <sub>OUT(MIN)</sub> = 0.6V, I <sub>Q</sub> = 20 $\mu$ A, I <sub>SD</sub> < 1 $\mu$ A, ThinSOT Package                                        |  |

| LTC3407                                                                                     | 3407 Dual, 600mA (I <sub>OUT</sub> ), 1.5MHz, Synchronous Step-Down DC/DC Converter 95% Efficiency, V <sub>IN</sub> : 2.5V to 5.5V, $V_{OUT(MIN)} = 0.6V$ , $I_{SD} < 1\mu$ A, 10-Lead MSE Package |                                                                                                                                                                                                |  |

| LTC3411                                                                                     | 1.25A (I <sub>OUT</sub> ), 4MHz, Synchronous Step-Down<br>DC/DC Converter                                                                                                                          | 95% Efficiency, VIN: 2.5V to 5.5V, $V_{OUT(MIN)}$ = 0.8V, $I_Q$ = 60µA, $I_{SD} < 1\mu$ A, 10-Lead MS Package                                                                                  |  |

VLDO and ThinSOT are trademarks of Linear Technology Corporation.