# LTC1686/LTC1687

### 52Mbps Precision Delay RS485 Fail-Safe Transceivers

### FEATURES

- Precision Propagation Delay Over Temperature: Receiver/Driver: 18.5ns ±3.5ns

- High Data Rate: 52Mbps

- Low t<sub>PLH</sub>/t<sub>PHL</sub> Skew: Receiver/Driver: 500ps Typ

- -7V to 12V RS485 Input Common Mode Range

- Guaranteed Fail-Safe Operation Over the Entire Common Mode Range

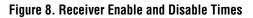

- High Input Resistance: ≥22k, Even When Unpowered

- Short-Circuit Protected

- Thermal Shutdown Protected

- Driver Maintains High Impedance in Three-State or with Power Off

- Single 5V Supply

- Pin Compatible with LTC490/LTC491

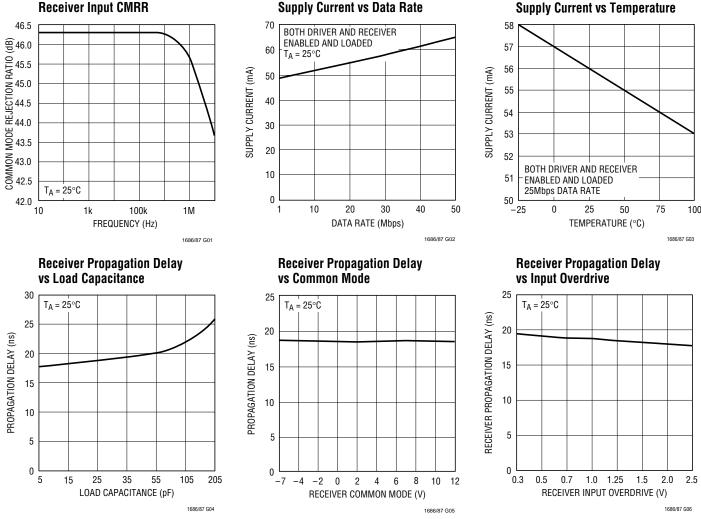

- 45dB CMRR at 26MHz

### **APPLICATIONS**

- High Speed RS485/RS422 Full Duplex Transceivers

- Level Translator

- Backplane Transceiver

- STS-1/OC-1 Data Transceiver

- Signal Repeaters

### DESCRIPTION

The LTC<sup>®</sup>1686/LTC1687 are high speed, precision delay, full-duplex RS485 transceivers that can operate at data rates as high as 52Mbps. The devices also meet the requirements of RS422.

A unique architecture provides very stable propagation delays and low skew over a wide common mode and ambient temperature range.

The driver and receiver feature three-state outputs, with disabled driver outputs maintaining high impedance over the entire common mode range. A short-circuit feature detects shorted outputs and substantially reduces driver output current. A similar feature also protects the receiver output from short circuits. Thermal shutdown circuitry protects from excessive power dissipation.

The receiver has a fail-safe feature that guarantees a high output state when the inputs are shorted or are left floating. The LTC1686/LTC1687 RS485 transceivers guarantee receiver fail-safe operation over the *entire* common mode range (-7V to 12V). Receiver input resistance remains  $\geq$  22k when the device is unpowered or disabled.

The LTC1686/LTC1687 operate from a single 5V supply and draw only 7mA of supply current.

T, LTC and LT are registered trademarks of Linear Technology Corporation.

### ABSOLUTE MAXIMUM RATINGS

#### (Note 1)

| Supply Voltage (V <sub>DD</sub> ) | 10V                             |

|-----------------------------------|---------------------------------|

| Control Input Currents            | 100mA to 100mA                  |

| Control Input Voltages            | -0.5V to V <sub>DD</sub> + 0.5V |

| Driver Input Voltages             | $-0.5V$ to $V_{DD} + 0.5V$      |

| Driver Output Voltages            | +12V/-7V                        |

| Receiver Input Voltages           | +12V/-7V                        |

| Receiver Output Voltages          | -0.5V to V <sub>DD</sub> + 0.5V |

| Receiver Input Differential       | 10V                             |

| Driver Short-Circuit Duration               |                |

|---------------------------------------------|----------------|

| (V <sub>OUT</sub> : -7V to 10V)             | Indefinite     |

| Receiver Short-Circuit Duration             |                |

| (V <sub>OUT</sub> : 0V to V <sub>DD</sub> ) | Indefinite     |

| Operating Temperature Range                 | 0°C to 70°C    |

| Storage Temperature Range                   | -65°C to 150°C |

| Lead Temperature (Soldering, 10 sec)        | 300°C          |

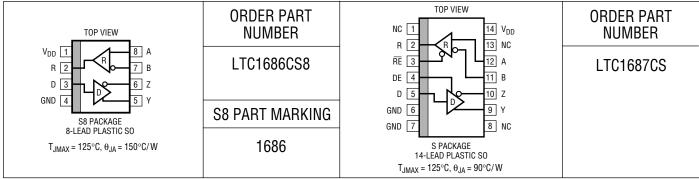

# PACKAGE/ORDER INFORMATION

Consult factory for Industrial and Military grade parts.

# DC ELECTRICAL CHARACTERISTICS VDD

$V_{DD}$  = 5V  $\pm$  5% unless otherwise noted (Notes 2, 3).

| SYMBOL            | PARAMETER                                                                                       | CONDITIONS                                                                                         |   | MIN        | ТҮР | MAX             | UNITS    |

|-------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---|------------|-----|-----------------|----------|

| V <sub>OD1</sub>  | Differential Driver Output (Unloaded)                                                           | I <sub>OUT</sub> = 0                                                                               | • |            |     | V <sub>DD</sub> | V        |

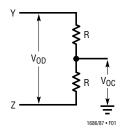

| V <sub>0D2</sub>  | Differential Driver Output (With Load)                                                          | R = 50Ω (RS422)<br>R = 27Ω (RS485), Figure 1                                                       | • | 2.0<br>1.5 |     | V <sub>DD</sub> | V<br>V   |

| $\Delta V_{0D}$   | Change in Magnitude of Driver Differential<br>Output Voltage for Complementary<br>Output States | R = $27\Omega$ or $50\Omega$ , Figure 1                                                            | • |            |     | 0.2             | V        |

| V <sub>OC</sub>   | Driver Common Mode Output Voltage                                                               | R = $27\Omega$ or $50\Omega$ , V <sub>DD</sub> = 5V, Figure 1                                      | • | 2          |     | 3               | V        |

| $\Delta  V_{0C} $ | Change in Magnitude of Driver Common<br>Mode Output Voltage for Complementary<br>Output States  | R = $27\Omega$ or $50\Omega$ , Figure 1                                                            | • |            |     | 0.2             | V        |

| V <sub>IH</sub>   | Input High Voltage                                                                              | D, DE, RE                                                                                          | • | 2          |     |                 | V        |

| V <sub>IL</sub>   | Input Low Voltage                                                                               | D, DE, RE                                                                                          | • |            |     | 0.8             | V        |

| I <sub>IN1</sub>  | Input Current                                                                                   | D, DE, RE                                                                                          | • | -1         |     | 1               | μA       |

| I <sub>IN2</sub>  | Input Current (A, B)                                                                            | $V_A, V_B = 12V, V_{DD} = 0V \text{ or } 5.25V$<br>$V_A, V_B = -7V, V_{DD} = 0V \text{ or } 5.25V$ | • | -500       |     | 500             | μA<br>μA |

| V <sub>TH</sub>   | Differential Input Threshold Voltage for Receiver                                               | $-7V \le V_{CM} \le 12V$                                                                           | • | -0.3       |     | 0.3             | V        |

| $\Delta V_{TH}$   | Receiver Input Hysteresis                                                                       | V <sub>CM</sub> = 0V                                                                               |   |            | 25  |                 | mV       |

| V <sub>OH</sub>   | Receiver Output High Voltage                                                                    | $I_{OUT} = -4mA$ , $V_{ID} = 300mV$                                                                | • | 3.5        | 4.8 |                 | V        |

2

### **DC ELECTRICAL CHARACTERISTICS** $V_{DD} = 5V \pm 5\%$ unless otherwise noted (Notes 2, 3).

| SYMBOL            | PARAMETER                                                  | CONDITIONS                                            |   | MIN  | ТҮР | MAX | UNITS |

|-------------------|------------------------------------------------------------|-------------------------------------------------------|---|------|-----|-----|-------|

| V <sub>OL</sub>   | Receiver Output Low Voltage                                | $I_{OUT} = 4mA$ , $V_{ID} = -300mV$                   |   |      |     | 0.4 | V     |

| I <sub>OZR</sub>  | Three-State (High Impedance) Output<br>Current at Receiver | $0.4V \le V_{OUT} \le 2.4V$                           | • | -1   |     | 1   | μA    |

| I <sub>OZD</sub>  | Three-State (High Impedance) Output<br>Current at Driver   | $V_{OUT} = -7V$ to 12V                                | • | -200 |     | 200 | μA    |

| C <sub>LOAD</sub> | Receiver and Driver Output Load Capacitance                | (Note 4)                                              |   |      |     | 500 | pF    |

| I <sub>DD</sub>   | Supply Current                                             | No Load, Pins D, DE, $\overline{RE} = 0V$ or $V_{DD}$ |   |      | 7   | 12  | mA    |

| I <sub>OSD1</sub> | Driver Short-Circuit Current, V <sub>OUT</sub> = HIGH      | V <sub>OUT</sub> = -7V or 10V (Note 5)                |   |      |     | 20  | mA    |

| I <sub>OSD2</sub> | Driver Short-Circuit Current, V <sub>OUT</sub> = LOW       | V <sub>OUT</sub> = -7V or 10V (Note 5)                |   |      |     | 20  | mA    |

| I <sub>OSR</sub>  | Receiver Short-Circuit Current                             | V <sub>OUT</sub> = 0V or V <sub>DD</sub> (Note 5)     | ٠ |      |     | 20  | mA    |

| R <sub>IN</sub>   | Input Resistance                                           | $-7V \le V_{CM} \le 12V$                              | ٠ | 22   |     |     | kΩ    |

| C <sub>IN</sub>   | Input Capacitance                                          | A, B, D, DE, RE Inputs (Note 4)                       |   |      | 3   |     | pF    |

|                   | Open-Circuit Input Voltage                                 | V <sub>DD</sub> = 5V (Note 4), Figure 5               | ٠ | 3.2  | 3.3 | 3.4 | V     |

| Fail-Safe<br>Time | Time to Detect Fail-Safe Condition                         |                                                       |   |      | 2   |     | μs    |

| CMRR              | Receiver Input Common Mode<br>Rejection Ratio              | V <sub>CM</sub> = 2.5V, f = 26MHz                     |   |      | 45  |     | dB    |

# **SWITCHING CHARACTERISTICS** $V_{DD} = 5V$ , unless otherwise noted (Notes 2, 3).

| SYMBOL                              | PARAMETER                                          | CONDITIONS                                                           |   | MIN | ТҮР  | MAX  | UNITS |

|-------------------------------------|----------------------------------------------------|----------------------------------------------------------------------|---|-----|------|------|-------|

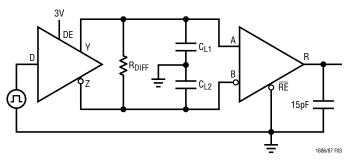

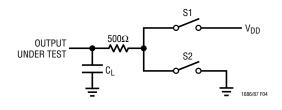

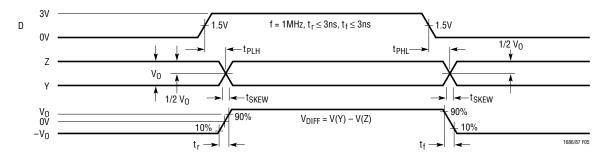

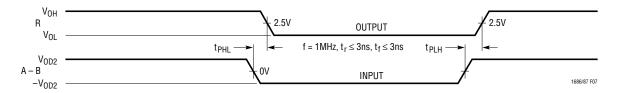

| t <sub>PLH</sub> , t <sub>PHL</sub> | Driver Input-to-Output Propagation Delay           | $R_{DIFF}$ = 54 $\Omega,C_{L1}$ = $C_{L2}$ = 100 pF, Figures 3, 5    | • | 15  | 18.5 | 22   | ns    |

| t <sub>SKEW</sub>                   | Driver Output A-to-Output B Skew                   | $R_{DIFF}$ = 54 $\Omega$ , $C_{L1}$ = $C_{L2}$ = 100pF, Figures 3, 5 |   |     | 500  |      | ps    |

| t <sub>r</sub> , t <sub>f</sub>     | Driver Rise/Fall Time                              | $R_{DIFF}$ = 54 $\Omega,C_{L1}$ = $C_{L2}$ = 100 pF, Figures 3, 5    |   |     | 3.5  |      | ns    |

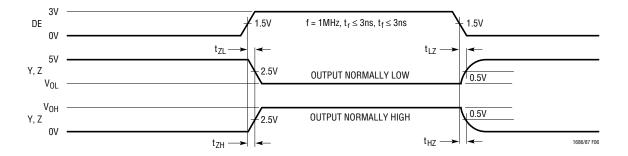

| t <sub>ZH</sub>                     | Driver Enable to Output High                       | C <sub>L</sub> = 100pF, S2 Closed, Figures 4, 6                      | ٠ |     | 25   | 50   | ns    |

| t <sub>ZL</sub>                     | Driver Enable to Output Low                        | C <sub>L</sub> = 100pF, S1 Closed, Figures 4, 6                      | ٠ |     | 25   | 50   | ns    |

| t <sub>LZ</sub>                     | Driver Disable from Low                            | C <sub>L</sub> = 15pF, S1 Closed, Figures 4, 6                       | ٠ |     | 25   | 50   | ns    |

| t <sub>HZ</sub>                     | Driver Disable from High                           | C <sub>L</sub> = 15pF, S2 Closed, Figures 4, 6                       | ٠ |     | 25   | 50   | ns    |

| t <sub>PLH</sub> , t <sub>PHL</sub> | Receiver Input-to-Output Propagation Delay         | C <sub>L</sub> = 15pF, Figures 3, 7                                  | ٠ | 15  | 18.5 | 22   | ns    |

| t <sub>SQD</sub>                    | Receiver Skew  t <sub>PLH</sub> - t <sub>PHL</sub> | C <sub>L</sub> = 15pF, Figures 3, 7                                  |   |     | 500  |      | ps    |

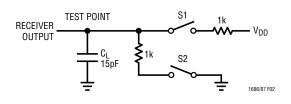

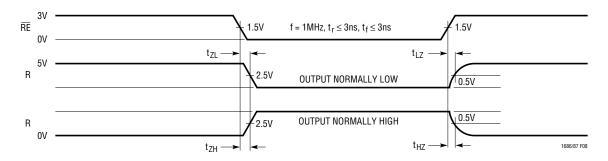

| t <sub>ZL</sub>                     | Receiver Enable to Output Low                      | C <sub>L</sub> = 15pF, S1 Closed, Figures 2, 8                       | ٠ |     | 25   | 50   | ns    |

| t <sub>ZH</sub>                     | Receiver Enable to Output High                     | C <sub>L</sub> = 15pF, S2 Closed, Figures 2, 8                       | • |     | 25   | 50   | ns    |

| t <sub>LZ</sub>                     | Receiver Disable from Low                          | C <sub>L</sub> = 15pF, S1 Closed, Figures 2, 8                       | • |     | 25   | 50   | ns    |

| t <sub>HZ</sub>                     | Receiver Disable from High                         | C <sub>L</sub> = 15pF, S2 Closed, Figures 2, 8                       | ٠ |     | 25   | 50   | ns    |

|                                     | Maximum Receiver Input<br>Rise/Fall Times          | (Note 4)                                                             | • |     |      | 2000 | ns    |

| t <sub>PKG-PKG</sub>                | Package-to-Package Skew                            | C <sub>L</sub> = 15pF, Same Temperature (Note 4)                     |   |     | 1.5  |      | ns    |

|                                     | Minimum Input Pulse Width                          | V <sub>DD</sub> = 5V ±5% (Note 4)                                    | • |     | 17   | 19.2 | ns    |

|                                     | Maximum Data Rate                                  | V <sub>DD</sub> = 5V ±5% (Note 4)                                    |   | 52  | 60   |      | Mbps  |

|                                     | Maximum Input Frequency                            | V <sub>DD</sub> = 5V ±5% (Note 4)                                    |   | 26  | 30   |      | MHz   |

# **ELECTRICAL CHARACTERISTICS**

The • denotes specifications which apply over the full operating temperature range.

Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

Note 2: All currents into the device pins are positive; all currents out of the device pins are negative.

**Note 3:** All typicals are given for  $V_{DD} = 5V$ ,  $T_A = 25^{\circ}C$ . Note 4: Guaranteed by design, but not tested.

Note 5: Short-circuit current does not represent output drive capability. When the output detects a short-circuit condition, output drive current is significantly reduced (from hundreds of mA to 20mA max) until the short is removed.

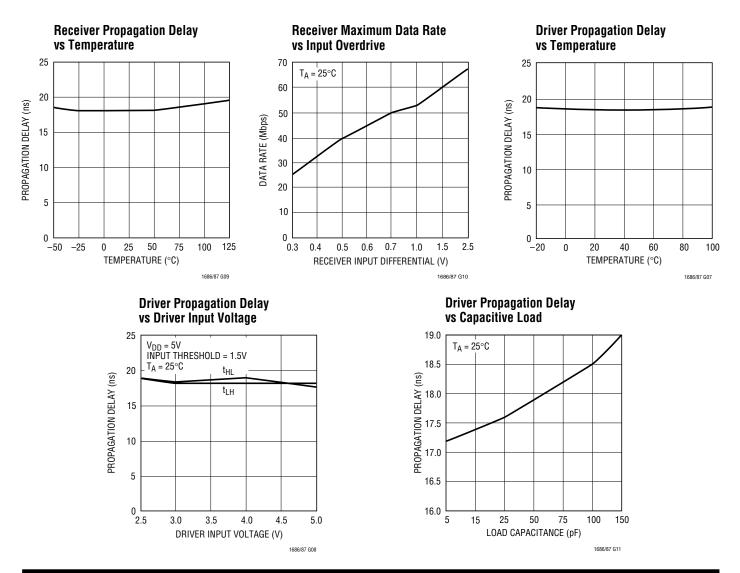

# TYPICAL PERFORMANCE CHARACTERISTICS

## **TYPICAL PERFORMANCE CHARACTERISTICS**

### PIN FUNCTIONS

#### LTC1686

$V_{DD}$  (Pin 1): Positive Supply, 5V to  $\pm 5\%.$  Bypass with 0.1µF ceramic capacitor.

**R (Pin 2):** Receiver Output. If  $A \ge B$  by 300mV, then R will be high. If  $A \le B$  by 300mV, then R will be low.

**D** (**Pin 3**): Driver Input. Controls the states of the Y and Z outputs. Do not float.

#### GND (Pin 4): Ground.

Y (Pin 5): Noninverting Driver Output.

Z (Pin 6): Inverting Driver Output.

Downloaded from Elcodis.com electronic components distributor

B (Pin 7): Inverting Receiver Input.

A (Pin 8): Noninverting Receiver Input.

#### LTC1687

NC (Pins 1, 8, 13): No Connection.

**R (Pin 2):** Receiver Output. If  $A \ge B$  by 300mV, then R will be high. If  $A \le B$  by 300mV, then R will be low.

$\overline{\text{RE}}$  (Pin 3): Receiver Enable.  $\overline{\text{RE}}$  = low enables the receiver.  $\overline{\text{RE}}$  = high forces receiver output into high impedance state. Do not float.

### PIN FUNCTIONS

**DE (Pin 4):** Driver Enable. DE = high enables the driver. DE = low will force the driver output into a high impedance state. Do not float.

**D** (**Pin 5**): Driver Input. Controls the states of the Y and Z outputs when DE = high. Do not float.

GND (Pins 6, 7): Ground.

Y (Pin 9): Noninverting Driver Output.

Z (Pin 10): Inverting Driver Output.

B (Pin 11): Inverting Receiver Input.

A (Pin 12): Noninverting Receiver Input.

$V_{DD}$  (Pin 14): Positive Supply, 5V to  $\pm 5\%.$  Bypass with 0.1µF ceramic capacitor.

## FUNCTION TABLES (LTC1687)

Transmitting

|    | INPUTS |   | LINE      | OUT   | PUTS            |

|----|--------|---|-----------|-------|-----------------|

| RE | DE     | D | CONDITION | Z     | Y               |

| Х  | 1      | 1 | No Fault  | 0     | 1               |

| Х  | 1      | 0 | No Fault  | 1     | 0               |

| Х  | 0      | Х | Х         | Hi- Z | Hi- Z           |

| Х  | 1      | Х | Fault     |       | Current<br>urce |

| INP | UTS |                                               | OUTPUT |

|-----|-----|-----------------------------------------------|--------|

| RE  | DE  | A – B                                         | R      |

| 0   | Х   | ≥ 300mV                                       | 1      |

| 0   | Х   | ≤-300mV                                       | 0      |

| 0   | Х   | Inputs Open                                   | 1      |

| 0   | Х   | Inputs Shorted Together<br>A = B = -7V to 12V | 1      |

| 1   | Х   | Х                                             | Hi- Z  |

### **TEST CIRCUITS**

Figure 1. Driver DC Test Load

Figure 2. Driver DC Test Load

### SWITCHING TIME WAVEFORMS

Figure 5. Driver Propagation Delays

Figure 6. Driver Enable and Disable Times

# EQUIVALENT INPUT NETWORKS

# **APPLICATIONS INFORMATION**

#### THEORY OF OPERATION

Unlike typical CMOS transceivers whose propagation delay can vary by as much as 500% from package to package and show significant temperature drift, the LTC1686/LTC1687 employ a novel architecture that produces a tightly controlled and temperature compensated propagation delay. The differential timing skew is also minimized between rising and falling output edges of the receiver output and the complementary driver outputs.

The precision timing features of the LTC1686/LTC1687 reduce overall system timing constraints by providing a narrow  $\pm 3.5$ ns window during which valid data appears at the receiver/driver output. The driver and receiver will have propagation delays that typically match to within 1ns.

In clocked data systems, the low skew minimizes duty cycle distortion of the clock signal. The LTC1686/LTC1687 can be used at data rates of 52Mbps with less than 5% duty cycle distortion (depending on cable length). When a clock signal is used to retime parallel data, the maximum recommended data transmission rate is 26Mbps to avoid timing errors due to clock distortion.

### FAIL-SAFE FEATURES

The LTC1686/LTC1687 have a fail-safe feature that guarantees the receiver output to be in a logic HIGH state when the inputs are either shorted or left open (note that when inputs are left open, large external leakage currents might override the fail-safe circuitry). In order to maintain good high frequency performance, it is necessary to slow down the transient response of the fail-safe feature. When a line fault is detected, the output will go HIGH typically in  $2\mu$ s. Note that the LTC1686/LTC1687 guarantee receiver failsafe performance over the *entire* (-7V to 12V) common mode range!

When the inputs are accidentally shorted (by cutting through a cable, for example), the short circuit fail-safe feature will guarantee a high output logic level. Note also that if the line driver is removed and the ground terminated resistors are left in place, the receiver will see this as a "short" and output a logic HIGH. Both of these fail-safe features will keep the receiver from outputting false data pulses under line fault conditions.

Thermal shutdown and short-circuit protection prevent latchup damage to the LTC1686/LTC1687 during fault conditions.

#### **OUTPUT SHORT-CIRCUIT PROTECTION**

The LTC1686/LTC1687 employ voltage sensing shortcircuit protection at the output terminals of both the driver and receiver. For a given input polarity, this circuitry determines what the correct output level should be. If the output level is different from the expected, it shuts off the big output devices. For example, if the driver input is >2V, it expects the "A" output to be >3.25V and the "B" output to be <1.75V. If the "A" output is subsequently shorted to a voltage below V<sub>DD</sub>/2, this circuitry shuts off the big output devices and turns on a smaller device in its place

### **APPLICATIONS INFORMATION**

(the converse applies for the "B" output). The outputs then appear as  $\pm 10$ mA current sources. Note that under normal operation, the output drivers can sink/source > 50mA. A time-out period of about 50ns is used in order to maintain normal high frequency operation, even under heavy capacitive loads.

If the cable is shorted at a large distance from the device outputs, it is possible for the short to go unnoticed at the driver outputs due to parasitic cable resistance. Additionally, when the cable is shorted, it no longer appears as a simple transmission line impedance, and the parasitic L's and C's might give rise to ringing and even oscillation. All these conditions disappear once the device comes out of short-circuit mode.

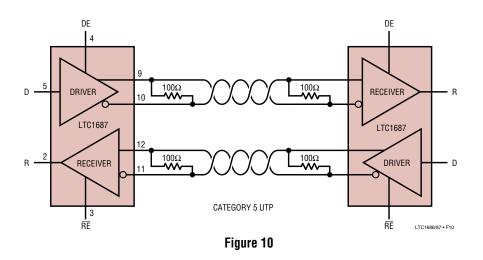

For cables with the typical RS485 termination (no DC bias on the cable, such as Figure 10), the LTC1686/LTC1687 will automatically come out of short-circuit mode once the physical short has been removed.

#### **Cable Termination**

The recommended cable termination for the LTC1686/ LTC1687 is a single resistor across the two wires at each end of the twisted-pair line (see Figure 10). The LTC1687 can also be used with cable terminations with a DC bias (such as Fast-20 and Fast-40 differential SCSI terminators). When using a biased termination with the LTC1687, however, the DE pin must be held low for at least 200ns after the part has been powered up. This ensures proper start-up into the DC load of the biased termination. Furthermore, when the LTC1687 output is shorted, the DE pin should be pulsed low for at least 200ns after the short has been removed. Since the LTC1686 driver is always enabled, the LTC1686 should only be used with single resistor termination, as shown in Figure 10.

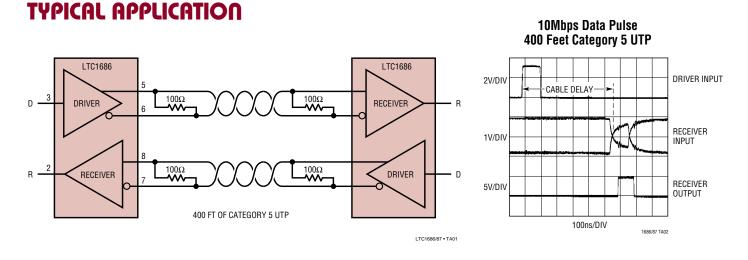

#### HIGH SPEED TWISTED-PAIR TRANSMISSION

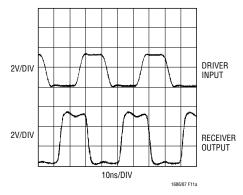

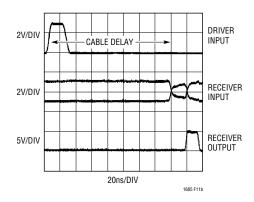

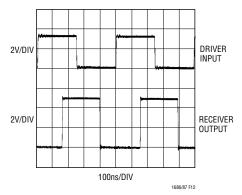

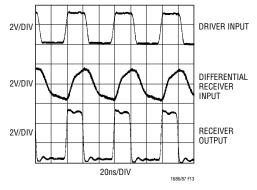

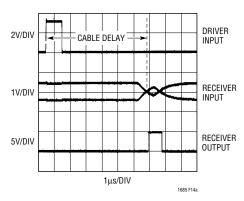

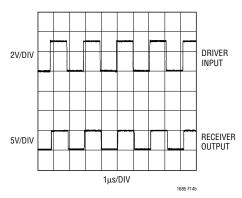

Data rates up to 52Mbps can be transmitted over 100 feet of category 5 twisted pair. Figure 10 shows the LTC1687 receiving differential data from another LTC1687 transceiver. Figure 11a shows a 26MHz (52Mbps) square wave propagated over 100 feet of category 5 UTP. Figure 11b shows a more stringent case of propagating a 20ns pulse over 100 feet of category 5 UTP. Figure 12 shows a 2MHz (4Mbps) square wave propagated over 1000 feet of category 5 unshielded twisted pair. Note that the LTC1686/ LTC1687 can still perform reliably at this distance and speed. Very inexpensive unshielded telephone grade twisted pair is shown in Figure 13. Despite the noticeable loss at the receiver input, the LTC1686/LTC1687 can still transfer at 30Mbps over 100 feet of telephone grade UTP. Note that under all these conditions, the LTC1686/LTC1687 can pass through a single data pulse equal to the inverse of the data rate (e.g., 20ns for 50Mbps data rate).

#### TRANSMISSION OVER LONG DISTANCES

#### 1Mbps Over 4000 Feet Category 5 UTP

The LTC1685/LTC1686/LTC1687 family of high speed transceivers is capable of 1Mbps transmission over 4000 feet of category 5 UTP. High quality cable provides lower

# APPLICATIONS INFORMATION

Figure 11a. 100 Feet of Category 5 UTP: 50Mbps

Figure 11b. 100 Feet of Category 5 UTP: 20ns Pulse

Figure 12. 1000 Feet of Category 5 UTP: 4Mbps

DC and AC attenuation over long distances. Figure 14a shows a 1 $\mu$ s pulse propagated down 4000 feet of category 5 UTP. Notice the significant attenuation at the receiver input and the clean pulse at the receiver output. The DC attenuation is due to the parasitic resistance of the cable. Figure 14b shows a 1Mbps square wave over the same 4000 feet of cable.

Figure 13. 100 Feet of Telephone Grade UTP: 30Mbps

Figure 14a. 4000 Feet of Category 5 UTP 1 $\mu s$  Pulse

Figure 14b. 4000 Feet of Category 5 UTP 1Mbps Square Wave

#### 1.6Mbps Over 8000 Feet (1.5 Miles) Category 5 UTP Using Repeaters

The LTC1686/LTC1687 can be used as repeaters to extend the effective length of a high speed twisted-pair line. Figure 15a shows a three repeater configuration using 2000 feet segments of category 5 UTP. Figure 15b shows the

#### **APPLICATIONS INFORMATION** LTC1687 LTC1687 LTC1687 2000 FT LTC1687 2000 FT LTC1687 2000 FT 2000 FT D REPEATER REPEATER REPEATER Figure 15a. 1.6Mbps, 8000 Feet (1.5 Miles) Using Three Repeaters DRIVER 1 DRIVER 1 2V/DIV DELAY OF 8000 FT 2V/DIV INPUT INPLIT OF CABLE **RECEIVER 2** 1V/DIV INPUT **BECEIVER 5** 5V/DIV **RECEIVER 3** OUTPUT 1V/DIV INPUT **RECEIVER 4** 1V/DIV DRIVER 1 INPUT 2V/DI\ INPUT **RECEIVER 5** 5V/DIV OUTPUT **RECEIVER 5** 5V/DIV OUTPUT 2µs/DIV 2µs/DIV 1686/87 F158 1686/87 F16

Figure 15b. 1.6Mbps Pulse and Square Wave Signals Over 8000 Feet Category 5 UTP Using Three Repeaters

propagation of a 600ns pulse through the network of Figure 15A. The bottom two traces show a 1.6Mbps square wave. Notice that the duty cycle does not noticeably degrade. For the case of the single pulse, however, there is a slight degradation of the pulse width.

By slowing down the data rate slightly to 1Mbps, one can obtain minimal pulse width degradation as the signal traverses through the repeater network. Figure 16 shows that the output pulse (bottom trace) is nearly the same width to the input pulse (top trace). The middle three traces of Figure 16 show the signal at the end of each of the first three 2000 feet sections of category 5 UTP. Notice how the LTC1687 repeaters are able to regenerate the signal with little loss. This implies that we can cascade more repeater networks and potentially achieve **1Mbps operation at total distances of over 10,000 feet!** A higher data rate can be achieved if the repeaters are spaced closer together.

#### HIGH SPEED BACKPLANE TRANSMISSION

The LTC1686/LTC1687 can also be used in backplane point-to-point transceiver applications, where the user wants to assure operation even when the common mode

Figure 16. Intermediate Signals of a 1 $\mu s$  Pulse

goes above or below the rails. It is advisable to terminate the PC traces when approaching maximum speeds. Since the LTC1686/LTC1687 are not intended to drive parallel terminated cables with characteristic impedances much less than that of twisted pair, both ends of the PC trace must be series terminated with the characteristic impedance of the trace. For best results, the signal should be routed differentially. The true and complement outputs of the LTC1686/LTC1687 should be routed on adjacent lavers of the PC board. The two traces should be routed very symmetrically, minimizing and equalizing parasitics to nearby signal and power/ground layers. For single-ended transmission, route the series terminated single-ended trace over an adjacent ground plane. Then set the (bypassed) negative input of the receiver to roughly 2.5V. Note that single-ended operation might not reach maximum speeds.

#### LAYOUT CONSIDERATIONS

A ground plane is recommended when using high frequency devices like the LTC1686/LTC1687. A  $0.1\mu$ F ceramic bypass capacitor less than 0.25 inch away from the V<sub>DD</sub> pin is also recommended.

Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

# APPLICATIONS INFORMATION

Long traces bounded by a  $V_{DD}$  and/or GND planes can add substantial parasitic capacitance. Parasitic capacitances on the receiver/driver outputs can also unduly slow down both the propagation delay and the rise/fall times.

The receiver inputs are high bandwidth and high impedance. If they are left floating, any capacitive coupling from any other signal can cause a glitch at the receiver output. Thus, if the receiver is not being used, it is advisable to always ground at least one of the two receiver input pins.

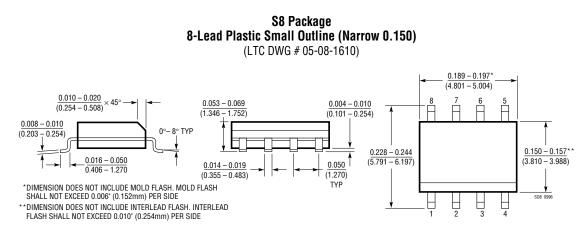

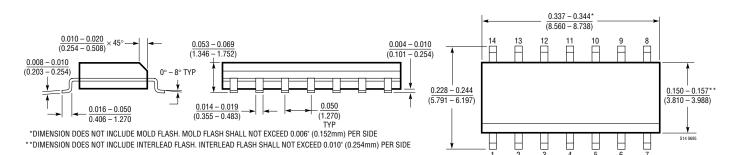

### PACKAGE DESCRIPTION Dimensions in inches (millimeters) unless otherwise noted.

S Package 14-Lead Plastic Small Outline (Narrow 0.150) (LTC DWG # 05-08-1610)

# **RELATED PARTS**

| PART NUMBER | DESCRIPTION                             | COMMENTS                                           |

|-------------|-----------------------------------------|----------------------------------------------------|

| LTC490      | Low Power RS485 Full-Duplex Transceiver | I <sub>CC</sub> = 300µA (Typ), SO-8 Package        |

| LTC491      | Low Power RS485 Full-Duplex Transceiver | I <sub>CC</sub> = 300µA (Typ), 14-Lead SO Package  |

| LTC1518     | High Speed Quad RS485 Receiver          | 52Mbps, Pin Compatible with LTC488                 |

| LTC1519     | High Speed Quad RS485 Receiver          | 52Mbps, Pin Compatible with LTC489                 |

| LTC1520     | High Speed Quad Differential Receiver   | 52Mbps, ±100mV Threshold, Rail-to-Rail Common Mode |

| LTC1685     | High Speed RS485 Transceiver            | 52Mbps, Pin Compatible with LTC485                 |