# OGY 10-Bit Rail-to-Rail Micropower DAC with I<sup>2</sup>C Interface

#### **FEATURES**

- Micropower 10-Bit DAC in SOT-23

- Low Operating Current: 60µA

- Ultralow Power Shutdown Mode: 12µA

- 2-Wire Serial Interface Compatible with I<sup>2</sup>C™

- Selectable Internal Reference or Ratiometric to V<sub>CC</sub>

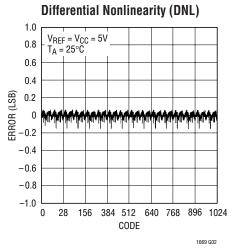

- Maximum DNL Error: 0.75LSB

- 8 User Selectable Addresses (MSOP Package)

- Single 2.7V to 5.5V Operation

- Buffered True Rail-to-Rail Voltage Output

- Power-On Reset

- 1.5V V<sub>II</sub> and 2.1V V<sub>IH</sub> for SDA and SCL

- Small 5-Lead SOT-23 and 8-Lead MSOP Packages

#### **APPLICATIONS**

- Digital Calibration

- Offset/Gain Adjustment

- Industrial Process Control

- Automatic Test Equipment

- Arbitrary Function Generators

- Battery-Powered Data Conversion Products

#### DESCRIPTION

The LTC®1669 is a 10-bit voltage output DAC with true buffered rail-to-rail output voltage capability. It operates from a single supply with a range of 2.7V to 5.5V. The reference for the DAC is selectable between the supply voltage or an internal bandgap reference. Selecting the internal bandgap reference will set the full-scale output voltage range to 2.5V. Selecting the supply as the reference sets the output voltage range to the supply voltage.

The part features a simple 2-wire serial interface compatible with I<sup>2</sup>C that allows communication between many devices. The internal data registers are double buffered to allow for simultaneous update of several devices at once. The DAC can be put in low current power-down mode for use in power conscious systems.

Power-on reset ensures the DAC output is at 0V when power is initially applied, and all internal registers are cleared. The LTC1669 is pin-for-pin compatible with the LTC1663.

(T), LTC and LT are registered trademarks of Linear Technology Corporation. I<sup>2</sup>C is a trademark of Philips Electronics N.V.

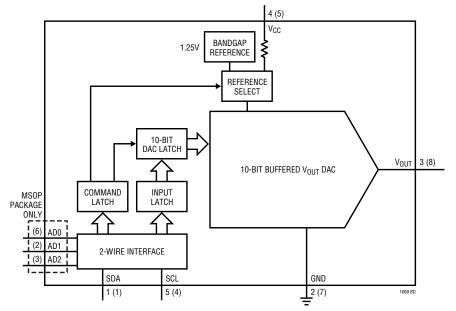

# **BLOCK DIAGRAM**

# Differential Nonlinearity (DNL) 1.0 0.8 VREF = VCC = 5V TA = 25°C 0.4 -0.4 -0.6 -0.8 -1.0 0 28 156 384 512 640 768 896 1024 CODE

NOTE: PIN NUMBERS IN PARENTHESES REFER TO THE MSOP PACKAGE

# **ABSOLUTE MAXIMUM RATINGS** (Note 1)

| V <sub>CC</sub> to GND    | 0.3V to 7.5V                | Operating Temperature Range         |               |

|---------------------------|-----------------------------|-------------------------------------|---------------|

| SDA, SCL                  | 0.3V to 7.5V                | LTC1669C                            | 0°C to 70°C   |

| ADO, AD1, AD2 (MSOP Only) | $0.3V$ to $(V_{CC} + 0.3V)$ | LTC1669I                            | 40°C to 85°C  |

| V <sub>OUT</sub>          | $0.3V$ to $(V_{CC} + 0.3V)$ | Storage Temperature Range           | 65°C to 150°C |

|                           |                             | Lead Temperature (Soldering, 10 sec | 300°C         |

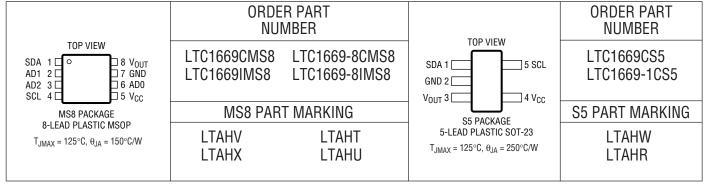

#### PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges.

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{CC} = 2.7V$  to 5.5V,  $V_{CC}$  set as reference,  $V_{OUT}$  unloaded, unless otherwise noted.

| SYMBOL            | PARAMETER                                  | CONDITIONS                                                            |   | MIN | TYP                              | MAX        | UNITS          |

|-------------------|--------------------------------------------|-----------------------------------------------------------------------|---|-----|----------------------------------|------------|----------------|

| DAC               |                                            |                                                                       |   |     |                                  |            |                |

|                   | Resolution                                 |                                                                       | • | 10  |                                  |            | Bits           |

|                   | Monotonicity                               | (Note 2)                                                              | • | 10  |                                  |            | Bits           |

| DNL               | Differential Nonlinearity                  | Guaranteed Monotonic (Note 2)                                         | • |     | ±0.2                             | ±0.75      | LSB            |

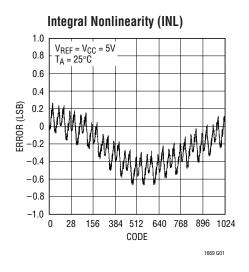

| INL               | Integral Nonlinearity                      | (Note 2)                                                              | • |     | ±0.5                             | ±2.5       | LSB            |

| V <sub>OS</sub>   | Offset Error                               | Measured at Code 20                                                   | • |     | ±10                              | ±30        | mV             |

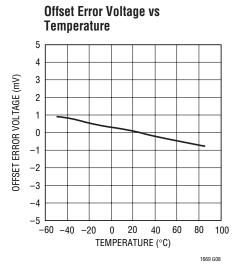

| V <sub>OSTC</sub> | Offset Error Temperature Coefficient       |                                                                       |   |     | ±15                              |            | μV/°C          |

| FSE               | Full-Scale Error                           | Reference Set to V <sub>CC</sub><br>Reference Set to Internal Bandgap | • |     | ±3<br>±3                         | ±15<br>±15 | LSB<br>LSB     |

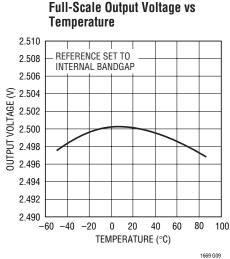

| V <sub>OUT</sub>  | DAC Output Span                            | Reference Set to V <sub>CC</sub><br>Reference Set to Internal Bandgap |   |     | 0 to V <sub>CC</sub><br>0 to 2.5 |            | V              |

| V <sub>FSTC</sub> | Full-Scale Voltage Temperature Coefficient | Reference Set to V <sub>CC</sub><br>Reference Set to Internal Bandgap |   |     | ±30<br>±50                       |            | μV/°C<br>μV/°C |

| PSRR              | Power Supply Rejection Ratio               | Reference Set to Internal Bandgap,<br>Code = 1023                     |   |     | ±0.4                             |            | LSB/V          |

| Power Su          | pply                                       |                                                                       |   |     |                                  |            |                |

| $V_{CC}$          | Positive Supply Voltage                    |                                                                       | • | 2.7 |                                  | 5.5        | V              |

| I <sub>CC</sub>   | Supply Current                             | V <sub>CC</sub> = 3V (Note 3)<br>V <sub>CC</sub> = 5V (Note 3)        | • |     | 60<br>75                         | 100<br>125 | μA<br>μA       |

| I <sub>SD</sub>   | Supply Current in Shutdown Mode            | (Note 3)                                                              | • |     | 12                               | 24         | μА             |

| Op Amp D          | C Performance                              |                                                                       |   |     |                                  |            |                |

|                   | Short-Circuit Current (Sourcing)           | V <sub>OUT</sub> Shorted to GND, Input Code = 1023                    | • |     | 25                               | 100        | mA             |

|                   | Short-Circuit Current (Sinking)            | $V_{OUT}$ Shorted to $V_{CC}$ , Input Code = 0                        | • |     | 30                               | 120        | mA             |

|                   |                                            |                                                                       |   |     |                                  |            | 1669f          |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{CC} = 2.7V$  to 5.5V,  $V_{CC}$  set as reference,  $V_{OUT}$  unloaded, unless otherwise noted.

| SYMBOL            | PARAMETER                           | CONDITIONS                                                                 |   | MIN            | TYP          | MAX | UNITS               |

|-------------------|-------------------------------------|----------------------------------------------------------------------------|---|----------------|--------------|-----|---------------------|

|                   | Output Impedance to GND             | Input Code = 0, V <sub>CC</sub> = 5V                                       |   |                | 65           |     | Ω                   |

|                   |                                     | Input Code = 0, V <sub>CC</sub> = 3V<br>In Shutdown Mode                   |   |                | 150<br>500   |     | $\Omega$ k $\Omega$ |

|                   | Output Impedance to V               |                                                                            |   |                | 80           |     |                     |

|                   | Output Impedance to V <sub>CC</sub> | Input Code = $1023$ , $V_{CC} = 5V$<br>Input Code = $1023$ , $V_{CC} = 3V$ |   |                | 120          |     | $\Omega$            |

| AC Perfor         | mance                               |                                                                            |   |                |              |     |                     |

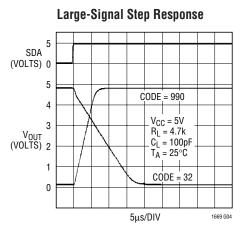

|                   | Voltage Output Slew Rate            | Rising (Notes 4, 5)<br>Falling (Notes 4, 5)                                |   |                | 0.75<br>0.25 |     | V/μs<br>V/μs        |

|                   | Voltage Output Settling Time        | To $\pm 0.5$ LSB (Notes 4, 5)                                              |   |                | 30           |     | μS                  |

|                   | Digital Feedthrough                 |                                                                            |   |                | 0.75         |     | nV • s              |

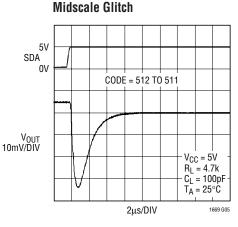

|                   | Digital-to-Analog Glitch Impulse    | 1LSB Change Around Major Carry                                             |   |                | 70           |     | nV • s              |

| Digital Inp       | puts SCL, SDA                       | ·                                                                          | ' |                |              |     |                     |

| $V_{IH}$          | High Level Input Voltage            |                                                                            | • | 2.1            |              |     | V                   |

| V <sub>IL</sub>   | Low Level Input Voltage             |                                                                            | • |                |              | 1.5 | V                   |

| $V_{LTH}$         | Logic Threshold Voltage             |                                                                            |   |                | 1.8          |     | V                   |

| I <sub>LEAK</sub> | Digital Input Leakage               | $V_{CC}$ = 5.5V and 0V, $V_{IN}$ = GND to $V_{CC}$                         | • |                |              | ±1  | μΑ                  |

| C <sub>IN</sub>   | Digital Input Capacitance           | (Note 7)                                                                   | • |                |              | 10  | pF                  |

| Digital Ou        | itput SDA                           |                                                                            |   |                |              |     |                     |

| V <sub>OL</sub>   | Digital Output Low Voltage          | I <sub>PULLUP</sub> = 3mA                                                  | • |                |              | 0.4 | V                   |

| Address I         | nputs ADO, AD1, AD2 (MSOP Only)     |                                                                            |   |                |              |     |                     |

| I <sub>UP</sub>   | Address Pin Pull-Up Current         | $V_{IN} = 0V$                                                              | • |                | 0.5          | 1.5 | μА                  |

| V <sub>IH</sub>   | High Level Input Voltage            |                                                                            | • | $V_{CC} - 0.3$ |              |     | V                   |

| V <sub>IL</sub>   | Low Level Input Voltage             |                                                                            | • |                | ·            | 8.0 | V                   |

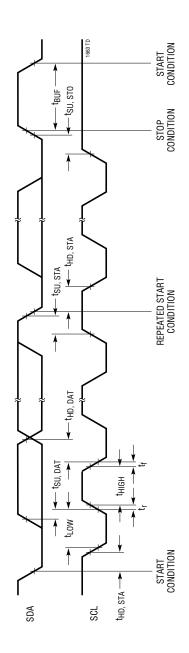

**TIMING CHARACTERISTICS** The  $\bullet$  denotes specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{CC} = 2.7V$  to 5.5V,  $V_{CC}$  set as reference,  $V_{OUT}$  unloaded, unless otherwise noted.

| SYMBOL                              | PARAMETER                                      | MIN | TYP | MAX | UNITS |     |  |  |  |

|-------------------------------------|------------------------------------------------|-----|-----|-----|-------|-----|--|--|--|

| Timing Characteristics (Notes 6, 7) |                                                |     |     |     |       |     |  |  |  |

| $f_{SCL}$                           | Clock Operating Frequency                      | •   |     |     | 100   | kHz |  |  |  |

| t <sub>BUF</sub>                    | Bus Free Time Between Stop and Start Condition | •   | 4.7 |     |       | μs  |  |  |  |

| t <sub>HD, STA</sub>                | Hold Time After (Repeated) Start Condition     | •   | 4   |     |       | μs  |  |  |  |

| t <sub>SU, STA</sub>                | Repeated Start Condition Setup Time            | •   | 4.7 |     |       | μs  |  |  |  |

| t <sub>SU, STO</sub>                | Stop Condition Setup Time                      | •   | 4   |     |       | μs  |  |  |  |

| t <sub>HD, DAT (IN)</sub>           | Data Hold Time (Input)                         | •   | 0   |     |       | ns  |  |  |  |

| t <sub>HD, DAT</sub> (OUT)          | Data Hold Time (Output)                        | •   | 225 | 500 | 3450  | ns  |  |  |  |

| t <sub>SU, DAT</sub>                | Data Setup Time                                | •   | 250 |     |       | ns  |  |  |  |

| t <sub>LOW</sub>                    | Clock Low Period                               | •   | 4.7 |     |       | μs  |  |  |  |

| t <sub>HIGH</sub>                   | Clock High Period                              | •   | 4   |     |       | μs  |  |  |  |

| t <sub>f</sub>                      | Clock, Data Fall Time                          | •   | 20  |     | 300   | ns  |  |  |  |

| t <sub>r</sub>                      | Clock, Data Rise Time                          | •   | 20  |     | 1000  | ns  |  |  |  |

**Note 1:** Absolute maximum ratings are those values beyond which the life of a device may be impaired.

**Note 2:** Nonlinearity and monotonicity are defined from code 20 to code 1003 (full scale). See Applications Information.

Note 3: Digital inputs at OV or V<sub>CC</sub>.

**Note 4:** Load is  $10k\Omega$  in parallel with 100pF.

Note 5:  $V_{CC} = V_{REF} = 5V$ . DAC switched between  $0.1V_{FS}$  and  $0.9V_{FS}$ , i.e., codes k = 102 and k = 922.

Note 6: All values are referenced to  $V_{IH}$  and  $V_{IL}$  levels.

Note 7: Guaranteed by design and not subject to test.

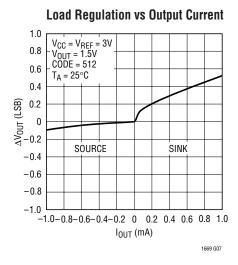

# TYPICAL PERFORMANCE CHARACTERISTICS

#### PIN FUNCTIONS

**SDA (Pin 1, Pin 1 on SOT-23):** Serial Data Bidirectional Pin. Data is shifted into the SDA pin and acknowledged by the SDA pin. High impedance pin while data is shifted in. Open-drain N-channel output during acknowledgment. Requires a pull-up resistor or current source to  $V_{CC}$ .

**AD1 (Pin 2):** Slave Address Select Bit 1. Tie this pin to either  $V_{CC}$  or GND to modify the corresponding bit of the LTC1669's slave address.

**AD2** (Pin 3): Slave Address Select Bit 2. Tie this pin to either  $V_{CC}$  or GND to modify the corresponding bit of the LTC1669's slave address.

**SCL** (**Pin 4**, **Pin 5 on SOT-23**): Serial Clock Input Pin. Data is shifted into the SDA pin at the rising edges of the clock. This high impedance pin requires a pull-up resistor or current source to  $V_{CG}$ .

**V<sub>CC</sub>** (Pin 5, Pin 4 on SOT-23): Power Supply.  $2.7V \le V_{CC} \le 5.5V$ . Also used as the reference voltage input when the part is programmed to use  $V_{CC}$  as the reference.

**ADO (Pin 6):** Slave Address Select Bit 0. Tie this pin to either  $V_{CC}$  or GND to modify the corresponding bit of the LTC1669's slave address.

GND (Pin 7, Pin 2 on SOT-23): System Ground.

**V<sub>OUT</sub>** (Pin 8, Pin 3 on SOT-23): Voltage Output. Buffered rail-to-rail DAC output.

# **DEFINITIONS**

**Differential Nonlinearity (DNL):** The difference between the measured change and the ideal 1LSB change for any two adjacent codes. The DNL error between any two codes is calculated as follows:

$$DNL = (\Delta V_{OUT} - LSB)/LSB$$

Where  $\Delta V_{OUT}$  is the measured voltage difference between two adjacent codes.

**Digital Feedthrough:** The glitch that appears at the analog output caused by AC coupling from the digital inputs when they change state. The area of the glitch is specified in (nV)(sec).

**Full-Scale Error (FSE):** The deviation of the actual full-scale voltage from ideal. FSE includes the effects of offset and gain errors (see Applications Information).

Integral Nonlinearity (INL): The deviation from a straight line passing through the endpoints of the DAC transfer curve (Endpoint INL). Because the output cannot go below zero, the linearity is measured between full scale and the lowest code that guarantees the output will be greater than

zero. The INL error at a given input code is calculated as follows:

$$INL = [V_{OUT} - V_{OS} - (V_{FS} - V_{OS})(code/1023)]/LSB$$

Where  $V_{OUT}$  is the output voltage of the DAC measured at the given input code.

**Least Significant Bit (LSB):** The ideal voltage difference between two successive codes.

$$LSB = V_{REF}/1024$$

**Resolution (n):** Defines the number of DAC output states (2<sup>n</sup>) that divide the full-scale range. Resolution does not imply linearity.

**Voltage Offset Error (V<sub>0S</sub>):** Nominally, the voltage at the output when the DAC is loaded with all zeros. A single supply DAC can have a true negative offset, but the output cannot go below zero (see Applications Information).

For this reason, single supply DAC offset is measured at the lowest code that guarantees the output will be greater than zero.

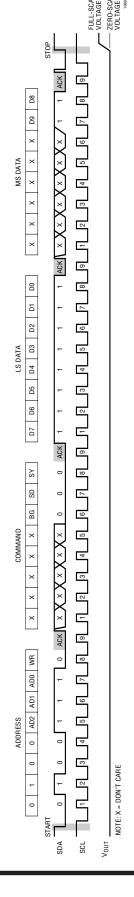

# TIMING DIAGRAM

Typical LTC1669 Input Waveform—Programming DAC Output for Full Scale (AD2 to AD0 Set High)

1669

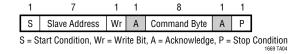

#### Write Word Protocol Used by the LTC1669

S = Start Condition, Wr = Write Bit = 0, A = Acknowledge, P = Stop Condition

#### Serial Digital Interface

The LTC1669 communicates with a host (master) using the standard 2-wire interface. The Timing Diagram shows the timing relationship of the signals on the bus. The two bus lines, SDA and SCL, must be high when the bus is not in use. External pull-up resistors or current sources, such as the LTC1694 SMBus/I<sup>2</sup>C Accelerator, are required on these lines.

The LTC1669 is a receive-only (slave) device. The master can communicate with the LTC1669 using the Quick Command, Send Byte or Write Word protocols as explained later.

#### The START and STOP Conditions

When the bus is not in use, both SCL and SDA must be high. A bus master signals the beginning of a communication to a slave device by transmitting a START condition. A START condition is generated by transitioning SDA from high to low while SCL is high.

When the master has finished communicating with the slave, it issues a STOP condition. A STOP condition is generated by transitioning SDA from low to high while SCL is high. The bus is then free for communication with another SMBus device.

#### **Acknowledge**

The Acknowledge signal is used for handshaking between the master and the slave. An Acknowledge (active LOW) generated by the slave lets the master know that the latest byte of information was received. The Acknowledge related clock pulse is generated by the master. The master releases the SDA line (HIGH) during the Acknowledge clock pulse. The slave-receiver must pull down the SDA line during the Acknowledge clock pulse so that it remains a stable LOW during the HIGH period of this clock pulse.

#### Write Word Protocol

The master initiates communication with the LTC1669 with a START condition and a 7-bit address followed by the Write Bit (Wr) = 0. The LTC1669 acknowledges and the master delivers the command byte. The LTC1669 acknowledges and latches the command byte into the command byte input register. The master then delivers the least significant data byte. Again the LTC1669 acknowledges and the data is latched into the least significant data byte input register. The master then delivers the most significant data byte. The LTC1669 acknowledges once more and latches the data into the most significant data byte input register. Lastly, the master terminates the communication with a STOP condition. On the reception of the STOP condition, the LTC1669 transfers the input register information to output registers and the DAC output is updated.

#### Slave Address (MSOP Package Only)

The LTC1669 can respond to one of eight 7-bit addresses. The first 4 bits (MSBs) have been factory programmed to 0100. The first 4 bits of the LTC1669-8 have been factory programmed to 0011. The three address bits, AD2, AD1 and AD0 are programmed by the user and determine the LSBs of the slave address, as shown in the table below:

|     |     |     | LTC1669  | LTC-1669-8 |

|-----|-----|-----|----------|------------|

| AD2 | AD1 | AD0 | 0100 xxx | 0011 xxx   |

| L   | L   | L   | 0100 000 | 0011 000   |

| L   | L   | Н   | 0100 001 | 0011 001   |

| L   | Н   | L   | 0100 010 | 0011 010   |

| L   | Н   | Н   | 0100 011 | 0011 011   |

| Н   | L   | L   | 0100 100 | 0011 100   |

| Н   | L   | Н   | 0100 101 | 0011 101   |

| Н   | Н   | L   | 0100 110 | 0011 110   |

| Н   | Н   | Н   | 0100 111 | 0011 111   |

#### Slave Address (SOT-23 Package)

The slave address for the SOT-23 package has been factory programmed to be "0100 000" (LTC1669) and "0100 001" (LTC1669-1). If another address is required, please consult the factory.

#### **Command Byte**

| 7 | 6 | 5 | 4 | 3 | 2  | 1  | 0  |

|---|---|---|---|---|----|----|----|

| Χ | Χ | Χ | Χ | Χ | BG | SD | SY |

| SY | 1<br>0 | Allows update on Acknowledge of SYNC Address only Update on Stop condition only (Power-On Default) |

|----|--------|----------------------------------------------------------------------------------------------------|

| SD | 1<br>0 | Puts the device in power-down mode Puts the device in standard operating mode (Power-On Default)   |

| BG | 1<br>0 | Selects the internal bandgap reference<br>Selects the supply as the reference (Power-On Default)   |

| Χ  | Χ      | Don't Care                                                                                         |

The stop condition normally initiates the update of the DAC's output latches. Simultaneous update of more than one DAC or other devices on the bus can be achieved by reissuing new start bit, address, command and data bytes before issuing a final stop condition (which will update all the devices). An alternate way to achieve simultaneous LTC1669 updates is to override the stop condition update by setting the "SY" bit of the command byte. Setting this bit sets the device to update the DAC output latches only at the reception of a SYNC address quick command. The actual update occurs on the rising edge of SCL during the Acknowledge. In this way, all devices can update on the reception of the SYNC address quick command instead of the STOP condition.

A Shutdown (SD) bit = HIGH will put the device in a low power state but retain all data latch information. Shutdown will occur at the reception of a STOP condition. This way shutdown could be synchronized to other devices. The output impedance of the DAC will go to a high impedance state ( $\approx 500 k\Omega$  to GND).

The Bandgap (BG) bit when set to "0" selects the DAC supply voltage as its voltage reference. The full-scale output of the DAC with this setting is equal to the supply voltage. When the BG bit is set to "1," the internal bandgap reference ( $\approx 1.25$ V) is selected as the DAC's reference. The full-scale output voltage for this setting is 2.5V.

#### **Data Bytes**

#### **Least Significant Data Byte**

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |  |  |

|----|----|----|----|----|----|----|----|--|--|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |  |

#### Most Significant Data Byte

| moot organicant bata byto |   |   |   |   |   |    |    |  |

|---------------------------|---|---|---|---|---|----|----|--|

| 7                         | 6 | 5 | 4 | 3 | 2 | 1  | 0  |  |

| Χ                         | Х | Χ | Χ | Χ | Х | D9 | D8 |  |

X = Don't care

#### **Send Byte Protocol**

The Send Byte protocol used on the LTC1669 is actually a subset of the Write Word protocol described previously. The Send Byte protocol can only be used to send the command byte information to the LTC1669.

The Send Byte protocol is also used whenever the Write Word protocol is interrupted for any reason. Reception of a START or STOP condition after the Acknowledge of the command byte, but before the Acknowledge of the last data byte, will cause both data bytes to be ignored and the command byte to be accepted.

Reception of a START or STOP condition before the Acknowledge of the command byte will cause the interrupted command byte to be ignored.

LINEAR

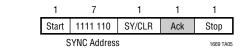

#### SYNC Address/Quick Command

In addition to the slave address, the LTC1669 has an address that can be shared by other devices so that they may be updated synchronously. The address is called to the SYNC address and uses the quick command protocol.

The SYNC Address is 1111 110

| SY/CLR | 1 | Update output latches on rising edge of SCL during      |

|--------|---|---------------------------------------------------------|

|        |   | Acknowledge of SYNC Address                             |

|        | 0 | Clear all internal latches on rising edge of SCL during |

|        |   | Acknowledge of SYNC Address                             |

The SY/CLR bit set high only has meaning when the "SY" bit of the command byte was previously set HIGH. On the otherhand, the SY/CLR bit set LOW will always clear the part, independent of the state of the "SY" bit in the command byte.

#### **Voltage Output**

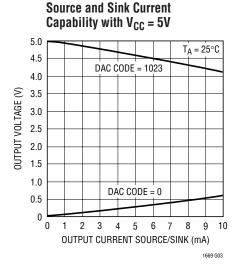

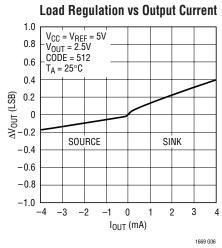

The output amplifier contained in the LTC1669 can source or sink up to 5mA. The output stage swings to within a few millivolts of either supply rail when unloaded and has an equivalent output resistance of  $85\Omega$  when driving a load to the rails. The output amplifier is stable driving capacitive loads up to 1000pF.

A small resistor placed in series with the output can be used to achieve stability for any load capacitance greater than 1000pF. For example, a  $0.1\mu\text{F}$  load can be driven by the LTC1669 if a  $110\Omega$  series resistance is used. The phase margin of the resulting circuit is  $45^{\circ}$  and increases monotonically from this point if larger values of resistance, capacitance or both are substituted for the values given.

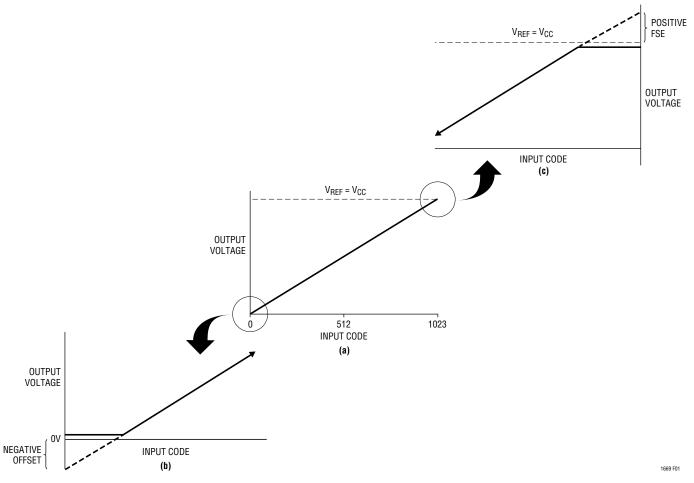

#### **Rail-to-Rail Output Considerations**

As in any rail-to-rail device, the output is limited to voltages within the supply range.

If the DAC offset is negative, the output for the lowest codes limits at 0V as shown in Figure 1b.

Similarly, limiting can occur near full scale when  $V_{CC}$  is used as the reference. If  $V_{REF} = V_{CC}$  and the DAC full-scale error (FSE) is positive, the output for the highest codes limits at  $V_{CC}$  as shown in Figure 1c. No full-scale limiting can occur if the internal reference is used.

Offset and linearity are defined and tested over the region of the DAC transfer function where no output limiting can occur.

#### **Internal Reference**

In applications where a predictable output is required that is independent of supply voltage, the LTC1669 has a user-selectable internal reference. Selecting the internal reference will set the full-scale output voltage to 2.5V. This can be useful in applications where the supply voltage is poorly regulated.

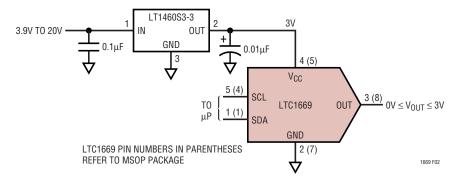

# Using the LT®1460 Micropower Series Reference as a Power Supply for the LTC1669

In applications where the advantages of using the internal reference are required but the full-scale range needs to be greater than 2.5V, an external series reference can be used. The LT1460 is ideal for use as a power supply for the LTC1669 and can provide 3V, 3.3V and 5V full-scale output voltage ranges. The LT1460 provides accuracy, noise immunity and extended supply range to the LTC1669 when the LTC1669 is operated ratiometric to  $V_{CC}$ . Since both parts are available in SOT-23 packages, the PC board space for this application is extremely small. See Figure 2.

Figure 1. Effects of Rail-to-Rail Operation On a DAC Transfer Curve. (a) Overall Transfer Function (b) Effect of Negative Offset for Codes Near Zero Scale (c) Effect of Positive Full-Scale Error for Input Codes Near Full Scale When  $V_{REF} = V_{CC}$

Figure 2. LT1460 As Power Supply for the LTC1669

/ LINEAR

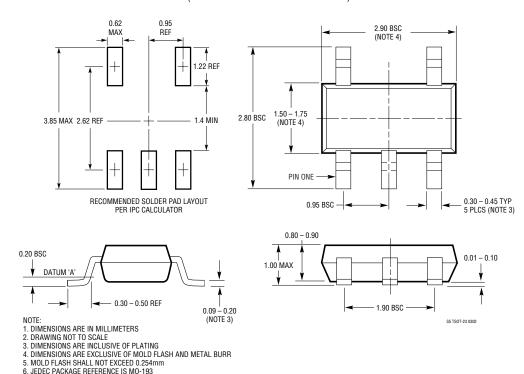

## PACKAGE DESCRIPTION

#### S5 Package 5-Lead Plastic TSOT-23

(Reference LTC DWG # 05-08-1635)

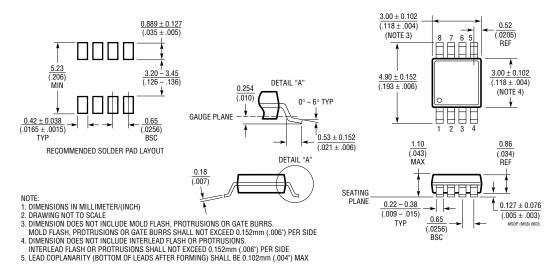

#### MS8 Package 8-Lead Plastic MSOP

(Reference LTC DWG # 05-08-1660)

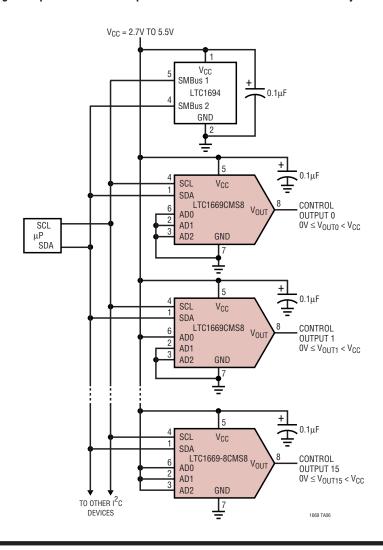

# TYPICAL APPLICATION

Program Up to 16 Control Outputs Per BUS and Place Them Where They Are Needed

# **RELATED PARTS**

| PART NUMBER     | DESCRIPTION                                                                              | COMMENTS                                                                                                                                |  |  |

|-----------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| LTC1694         | SMBus/I <sup>2</sup> C Accelerator                                                       | Dual SMBus Accelerator with Active AC and DC Pull-Up Current Sources                                                                    |  |  |

| LTC1694-1       | SMBus/I <sup>2</sup> C Accelerator                                                       | Dual SMBus Accelerator with Active AC Pull-Up Current Only                                                                              |  |  |

| DACs            |                                                                                          |                                                                                                                                         |  |  |

| LTC1659         | Single Rail-to-Rail 12-Bit $V_{OUT}$ DAC in 8-Lead MSOP Package. $V_{CC}$ = 2.7V to 5.5V | Low Power Multiplying V <sub>OUT</sub> DAC. Output Swings from GND to REF. REF Input Can Be Tied to V <sub>CC</sub> . 3-Wire Interface. |  |  |

| LTC1660/LTC1664 | Octal/Quad 10-Bit V <sub>OUT</sub> DACs in 16-Pin Narrow SSOP                            | V <sub>CC</sub> = 2.7V to 5.5V Micropower Rail-to-Rail Output. 3-Wire Interface.                                                        |  |  |

| LTC1661         | Dual 10-Bit V <sub>OUT</sub> in 8-Lead MSOP Package                                      | V <sub>CC</sub> = 2.7V to 5.5V Micropower Rail-to-Rail Output. 3-Wire Interface.                                                        |  |  |

| LTC1663         | 10-Bit V <sub>OUT</sub> in SOT-23, SMBUS Interface                                       | Pin-for-Pin Compatible with LTC1669                                                                                                     |  |  |

| ADCs            |                                                                                          |                                                                                                                                         |  |  |

| LTC1285/LTC1288 | 8-Pin SO, 3V Micropower ADCs                                                             | 1- or 2-Channel, Autoshutdown                                                                                                           |  |  |

| LTC1286/LTC1298 | 8-Pin SO, 5V Micropower ADCs                                                             | 1- or 2-Channel, Autoshutdown                                                                                                           |  |  |