# Quad Parametric Measurement Unit With Integrated 16-Bit Level Setting DACs

**Preliminary Technical Data**

# AD5522

### FEATURES

**Ouad Parametric Measurement Unit** FV, FI, FN, MV, MI Functions 4 Programmable Current Ranges (Internal R<sub>SENSE</sub>) 5uA, 20uA, 200uA and 2mA 1 Programmable Current Range up to 64mA (external R<sub>SENSE</sub>) 22.5 V FV Range with Asymmetrical Operation **Integrated 16-Bit DACs Provide Programmable Levels Offset and Gain Correction on Chip** Low Capacitance Outputs Suited to Relay Less Systems **On-chip Comparators Per Channel** FI Voltage Clamps & FV Current Clamps **Guard Drive Amplifier** System PMU connections **Programmable Temperature Shutdown Feature** SPI/Microwire/DSP & LVDS Compatible Interfaces Compact 80 lead TQFP Package with Exposed Pad (Top Or Bottom)

### **APPLICATIONS**

Automatic Test Equipment (ATE) per pin Parametric Measurement Unit Continuity & Leakage Testing Device Power Supply Instrumentation SMU (Source Measure Unit)

### **Precision Measurement**

### **PRODUCT OVERVIEW**

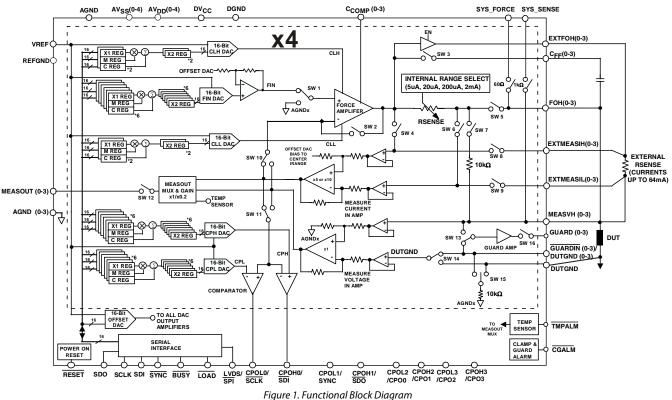

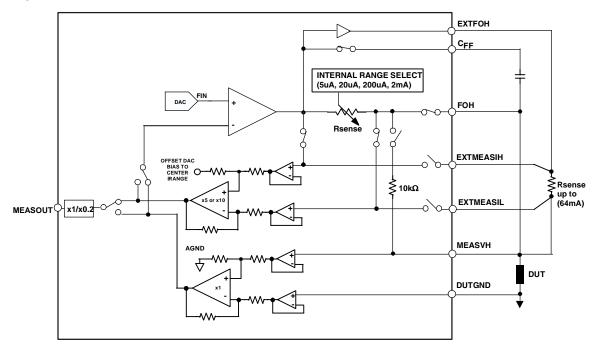

The AD5522 is a high performance, highly integrated parametric measurement unit consisting of four independent channels. Each PPMU channel includes five, 16-bit, voltage out DACs setting the programmable inputs levels for the force voltage input, clamp and comparator inputs (high and low). Five programmable force and measure current ranges are available ranging from  $5\mu$ A to 64mA. Four of these ranges use on chip sense resistors, while a high current range up to 64mA is available per channel using off chip sense resistors. Currents in excess of 64mA require an external amplifier. Low capacitance DUT connections (FOH, EXT FOH) ensure the device is suited to relay less test systems. The PMU functions are controlled via a simple three wire serial interface compatible with SPI/QSPI/Microwire and DSP interface standards. Interface clocks of 50MHz allow fast updating of modes. LVDS (Low Voltage Differential Signaling) interface protocol at

100MHz is also supported. Comparator outputs are provided per channel for device go no-go testing and characterization. Control registers provide easy way of changing force or measure conditions, DAC levels and selected current ranges. SDO (serial data out) allows the user to readback information for diagnostic purposes.

#### Rev.PrM

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2007 Analog Devices, Inc. All rights reserved.

# TABLE OF CONTENTS

| Features1                                     |

|-----------------------------------------------|

| Revision History                              |

| Specifications                                |

| Table 2. TIMING Characteristics   9           |

| Absolute Maximum Ratings12                    |

| Thermal Resistance12                          |

| ESD Caution                                   |

| Pin Configuration and Function Descriptions13 |

| TERMINOLOGY16                                 |

| Functional Description17                      |

| Force Amplifier19                             |

| Comparators19                                 |

| Clamps19                                      |

| Current Range selection20                     |

| High Current ranges                           |

| Device under test ground (DUTGND)20           |

| Guard amplifer21                              |

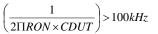

| Compensation Capacitors21                     |

| System Force Sense Switches                   |

| Temperature Sensor                            |

| Measure Output (MEASOUT)22                    |

| DAC Levels                                    |

| Offset DAC                                    |

| Offset and Gain registers                     |

| Cached x2 registers23                         |

| V <sub>REF</sub>                              |

| Reference Selection                           |

| Calibration25                                 |

| System Level Calibration25                    |

|                                               |

| Force Voltage, FV                                                                                                                                                                                                                                        | 26                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Force Current, FI                                                                                                                                                                                                                                        | 27                                                                                                                     |

| SPI INTERFACE                                                                                                                                                                                                                                            | 28                                                                                                                     |

| LVDS INTERFACE                                                                                                                                                                                                                                           | 28                                                                                                                     |

| Serial Interface Write Mode                                                                                                                                                                                                                              | 28                                                                                                                     |

| RESET Function                                                                                                                                                                                                                                           | 28                                                                                                                     |

| BUSY and LOAD Function                                                                                                                                                                                                                                   | 28                                                                                                                     |

| Register Update Rates                                                                                                                                                                                                                                    | 29                                                                                                                     |

| Register Selection                                                                                                                                                                                                                                       | 30                                                                                                                     |

| Write System Control Register                                                                                                                                                                                                                            | 31                                                                                                                     |

| Write PMU Register                                                                                                                                                                                                                                       | 33                                                                                                                     |

| Write DAC Register                                                                                                                                                                                                                                       | 35                                                                                                                     |

| Read Registers                                                                                                                                                                                                                                           | 37                                                                                                                     |

| Readback of System Control Register                                                                                                                                                                                                                      | 38                                                                                                                     |

|                                                                                                                                                                                                                                                          |                                                                                                                        |

| Readback of PMU Register                                                                                                                                                                                                                                 | 39                                                                                                                     |

| Readback of PMU Register                                                                                                                                                                                                                                 |                                                                                                                        |

| ũ là chí                                                                                                                                                                                                             | 39                                                                                                                     |

| Readback of Comparator Status Register                                                                                                                                                                                                                   | 39<br>40                                                                                                               |

| Readback of Comparator Status Register<br>Readback of Alarm Status Register                                                                                                                                                                              | 39<br>40<br>40                                                                                                         |

| Readback of Comparator Status Register<br>Readback of Alarm Status Register<br>Readback of DAC Register                                                                                                                                                  | 39<br>40<br>40<br>41                                                                                                   |

| Readback of Comparator Status Register<br>Readback of Alarm Status Register<br>Readback of DAC Register<br>Power On Default                                                                                                                              | <ol> <li>39</li> <li>40</li> <li>40</li> <li>41</li> <li>42</li> </ol>                                                 |

| Readback of Comparator Status Register<br>Readback of Alarm Status Register<br>Readback of DAC Register<br>Power On Default<br>Setting up the device on power on                                                                                         | <ol> <li>39</li> <li>40</li> <li>40</li> <li>41</li> <li>42</li> <li>42</li> </ol>                                     |

| Readback of Comparator Status Register<br>Readback of Alarm Status Register<br>Readback of DAC Register<br>Power On Default<br>Setting up the device on power on<br>Changing Modes                                                                       | <ol> <li>39</li> <li>40</li> <li>40</li> <li>41</li> <li>42</li> <li>42</li> <li>43</li> </ol>                         |

| Readback of Comparator Status Register<br>Readback of Alarm Status Register<br>Readback of DAC Register<br>Power On Default<br>Setting up the device on power on<br>Changing Modes<br>Required external components                                       | <ol> <li>39</li> <li>40</li> <li>40</li> <li>41</li> <li>42</li> <li>42</li> <li>43</li> <li>45</li> </ol>             |

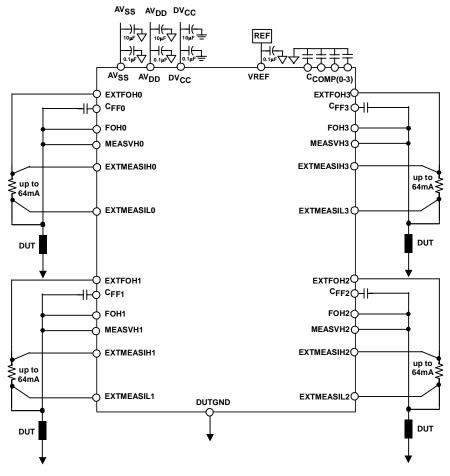

| Readback of Comparator Status Register<br>Readback of Alarm Status Register<br>Readback of DAC Register<br>Power On Default<br>Setting up the device on power on<br>Changing Modes<br>Required external components<br>Typical Application for the AD5522 | <ol> <li>39</li> <li>40</li> <li>40</li> <li>41</li> <li>42</li> <li>42</li> <li>43</li> <li>45</li> <li>46</li> </ol> |

### **REVISION HISTORY**

Rev PrM, 12th March - Update to specification pages, addition of typical plots, general update of all sections of datasheet. Update of AD5522 models. .

# **Preliminary Technical Data**

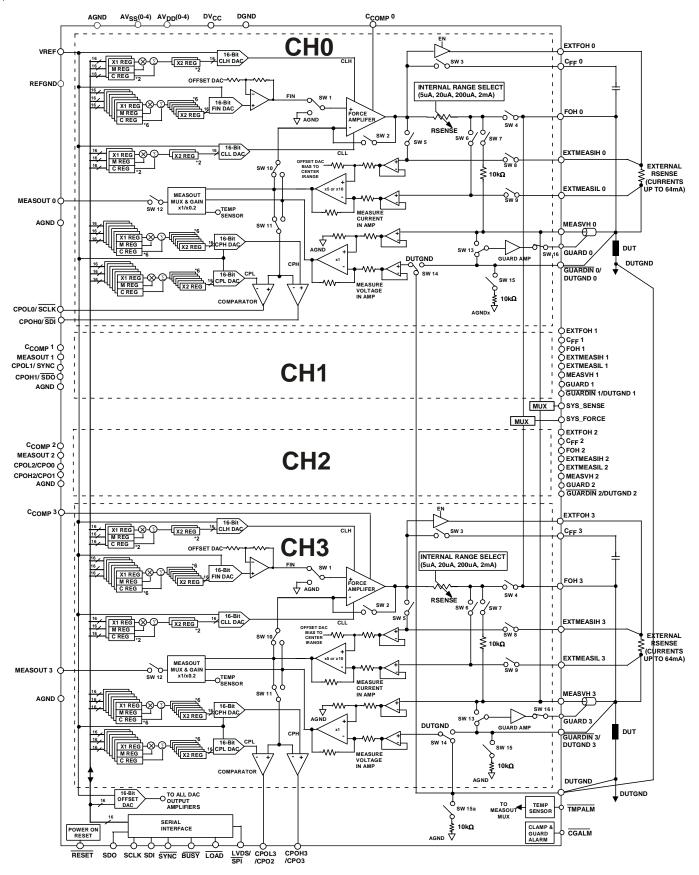

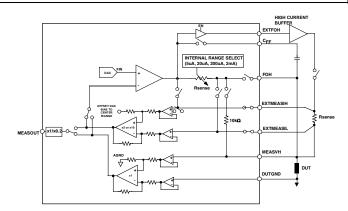

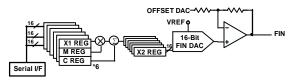

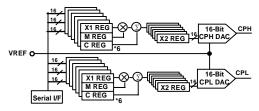

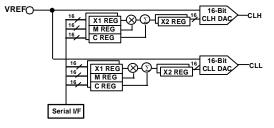

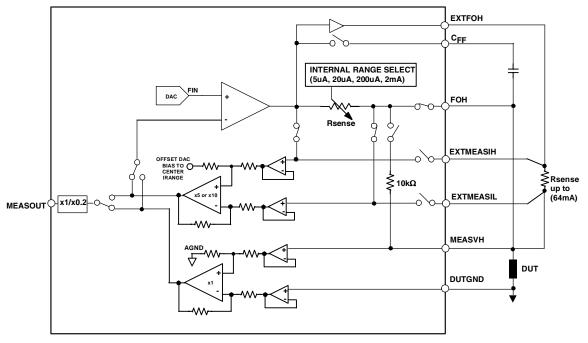

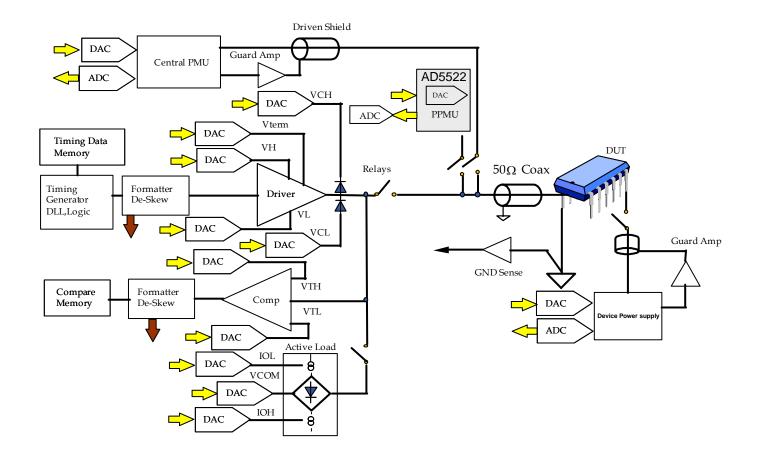

Figure 2. Detailed Block Diagram

Rev. PrM | Page 3 of 48

# SPECIFICATIONS

Table 1.  $AV_{DD} \ge 10V$ ,  $AV_{SS} \le -5V$ ,  $|AV_{DD} - AV_{SS}| \ge 20V$  and  $\le 33V$ ,  $DV_{CC} = 2.3V$  to 5.25V,  $V_{REF}=5V$ , Gain (m), Offset (c) and DAC Offset registers at default values ( $T_J = +25$  to  $+90^{\circ}C$ , max specs unless otherwise noted.)

| Parameter                                         | Min                 | Typ <sup>1</sup> | Max                 | Units            | Test Conditions/Comments                                                                                   |  |

|---------------------------------------------------|---------------------|------------------|---------------------|------------------|------------------------------------------------------------------------------------------------------------|--|

| FORCE VOLTAGE                                     |                     |                  |                     |                  |                                                                                                            |  |

| FOH Output Voltage Range                          | AV <sub>ss</sub> +4 |                  | AV <sub>DD</sub> -4 | V                | All current ranges from FOH at full scale current. Includes ±1V dropped across sense resistor              |  |

| EXTFOH Output Voltage Range                       | AV <sub>ss</sub> +3 |                  | AV <sub>DD</sub> -3 | V                | External high current range at full scale current. Does not include $\pm 1V$ dropped across sense resistor |  |

| Output Voltage Span                               |                     |                  | 22.5                | V                |                                                                                                            |  |

| Offset Error                                      | -100                |                  | 100                 | mV               | Measured at Midscale Code, 0V. Prior to calibration.                                                       |  |

| Offset Error Tempco <sup>2</sup>                  |                     | ±100             |                     | μV/°C            |                                                                                                            |  |

| Gain Error                                        | -0.5                |                  | 0.5                 | %                | Prior to calibration.                                                                                      |  |

| Gain Error Tempco <sup>2</sup>                    |                     | ±10              |                     | ppm/°C           |                                                                                                            |  |

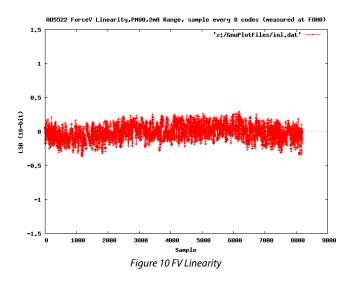

| Linearity Error                                   | -0.02               |                  | 0.02                | % FSR            | $FSR = Fullscale Range. \pm 10 V range, Gain and offset errors calibrated out.$                            |  |

| Short Circuit Current Limit <sup>2</sup>          | -120                |                  | 120                 | mA               | On 64mA range.                                                                                             |  |

|                                                   | -10                 |                  | 10                  | mA               | In all other ranges.                                                                                       |  |

| MEASURE CURRENT                                   |                     |                  |                     |                  | MEASURE = (IDUT X RSENSE x GAIN)                                                                           |  |

| Offset Error                                      | -1                  |                  | 1                   | %                | V(Rsense)= $\pm 1V$ , Measured with zero current flowing.                                                  |  |

| Offset Error Tempco <sup>2</sup>                  |                     | ±10              |                     | μV/°C            |                                                                                                            |  |

| Gain Error                                        | -1                  | 25               | 1                   | %                | Instrumentation Amp Gain = 5 or 10                                                                         |  |

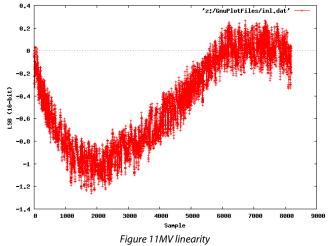

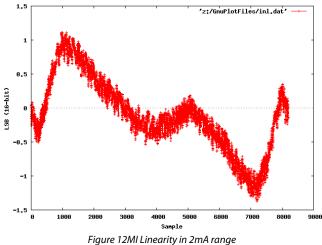

| Gain Error Tempco <sup>2</sup><br>Linearity Error | -0.01               | 25               | 0.01                | ppm/°C<br>% FSCR | Offset and Gain errors calibrated out                                                                      |  |

| Output Voltage Span <sup>2</sup>                  | -0.01               |                  | 22.5                | V V              | Onset and Gaineriors calibrated out                                                                        |  |

| CM Error                                          | -0.005              |                  | 0.005               | v<br>%FSVR/V     | % of FS Change at measure output per V change in DUT voltage                                               |  |

| Measure Current Ranges                            |                     | ±5               |                     | μA               | Set using internal sense resistor                                                                          |  |

| j                                                 |                     | ±20              |                     | μA               | Set using internal sense resistor                                                                          |  |

|                                                   |                     | ±200             |                     | μA               | Set using internal sense resistor                                                                          |  |

|                                                   |                     | ±2               |                     | mA               | Set using internal sense resistor                                                                          |  |

|                                                   |                     |                  | Up to ±64           | mA               | Set using external sense resistor, internal amplifier can drive to 64mA                                    |  |

| FORCE CURRENT                                     |                     |                  |                     |                  |                                                                                                            |  |

| Voltage Compliance, FOH                           | AV <sub>ss</sub> +4 |                  | AV <sub>DD</sub> -4 | V                |                                                                                                            |  |

| Voltage Compliance, EXTFOH                        | AV <sub>SS</sub> +3 |                  | AV <sub>DD</sub> -3 | V                |                                                                                                            |  |

| Offset Error                                      | -2                  |                  | 2                   | %FSCR            | Measured at Midscale Code, 0V. Prior to calibration.                                                       |  |

| Offset Error Tempco <sup>2</sup>                  |                     | ±10              |                     | ppm FS/<br>℃     |                                                                                                            |  |

| Gain Error                                        | -0.5                |                  | 0.5                 | %                | Prior to calibration.                                                                                      |  |

| Gain Error Tempco <sup>2</sup>                    |                     | ±25              |                     | ppm/°C           |                                                                                                            |  |

| Linearity Error                                   | -0.02               |                  | 0.02                | % FSCR           |                                                                                                            |  |

| CM Error                                          | -0.005              |                  | 0.005               | %FSCR/V          | % of FS Change at measure output per V change in DUT voltage                                               |  |

| Force Current Ranges                              |                     | ±5               |                     | μΑ               | Set using internal sense resistor, 200k $\Omega$                                                           |  |

|                                                   |                     | ±20              |                     | μΑ               | Set using internal sense resistor, 50k $\Omega$                                                            |  |

|                                                   |                     | ±200             |                     | μΑ               | Set using internal sense resistor, $5k\Omega$                                                              |  |

|                                                   |                     | ±2               |                     | mA               | Set using internal sense resistor, $500\Omega$                                                             |  |

|                                                   |                     |                  | Up to ±64           | mA               | Set using external sense resistor, internal amplifier can drive to 64mA                                    |  |

| MEASURE VOLTAGE                                   |                     |      |                     |                 |                                                          |

|---------------------------------------------------|---------------------|------|---------------------|-----------------|----------------------------------------------------------|

| Measure Voltage Range                             |                     |      | AV <sub>DD</sub> -4 | v               |                                                          |

| measure voltage hange                             | AV <sub>ss</sub> +4 |      |                     | v               |                                                          |

| Offset Error                                      | -10                 |      | 10                  | mV              | GAIN = 1, measured at 0V                                 |

| Offset Error                                      | -40                 |      | 40                  | mV              | GAIN = 1, measured at 0V<br>GAIN = 0.2, measured at 0V   |

| Offset Error Tempco <sup>2</sup>                  | -40                 | ±10  | 40                  | μV/°C           | GAIN – 0.2, measured at 0V                               |

| Gain Error                                        | -0.5                | ±10  | 0.5                 | μν/ C<br>% FSR  | Gain = 1                                                 |

| Gain Error                                        | -0.5                |      | 0.5                 | % FSR           | Gain = 0.2                                               |

|                                                   | -0.5                | ±10  | 0.5                 | ppm/°C          | Gain = 0.2                                               |

| Gain Error Tempco <sup>2</sup><br>Linearity Error | -0.01               | ±10  | 0.01                | % FSR           |                                                          |

| COMPARATOR                                        | 0.01                |      | 0.01                | 701 511         |                                                          |

| Comparator Span                                   |                     |      | 22.5                | v               |                                                          |

| Offset Error                                      | -10                 | 1    | 10                  | mV              |                                                          |

| Propagation delay <sup>2</sup>                    | -10                 | 0.25 | 10                  | μs              |                                                          |

| VOLTAGE CLAMPS                                    |                     | 0.25 |                     | μ               |                                                          |

| Clamp Span                                        |                     |      | 22.5                | v               |                                                          |

| Positive Clamp Accuracy                           |                     |      | 150                 | mV              |                                                          |

| Negative Clamp Accuracy                           | -150                |      | 001                 | mV              |                                                          |

| Recovery Time <sup>2</sup>                        | -150                | 0.5  | 1.5                 | μs              |                                                          |

| Activation Time <sup>2</sup>                      |                     | 1.5  | 3                   | •               |                                                          |

|                                                   |                     | L.1  | 5                   | μs              |                                                          |

| CORRENT CLAMPS                                    | Drog/d              |      | Programmed          |                 |                                                          |

| Clamp Accuracy                                    | Prog'd<br>Clamp     |      | Clamp value         | % of FSC        | Clamp current scales with selected range                 |

| clump //ccurucy                                   | value               |      | +15                 | range           | clump current scales with selected range                 |

| Recovery Time <sup>2</sup>                        |                     | 0.5  | 1.5                 | μs              |                                                          |

| Activation Time <sup>2</sup>                      |                     | 1.5  | 3                   | μs              |                                                          |

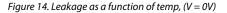

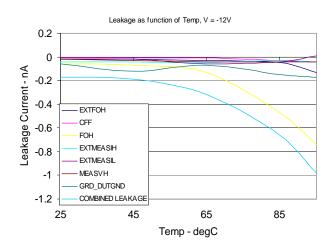

| FOH, EXTFOH, EXTMEASIL,                           |                     |      |                     |                 |                                                          |

| EXTMEASIH, CFF                                    |                     |      |                     |                 |                                                          |

| Pin Capacitance <sup>2</sup>                      |                     | 10   |                     | pF              |                                                          |

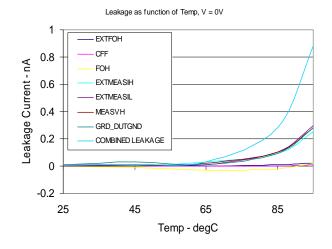

| Leakage Current                                   | -3                  |      | 3                   | nA              | On or off switch leakage                                 |

| Leakage Current Tempco <sup>2</sup>               |                     | ±0.1 |                     | nA/°C           |                                                          |

| MEASVH                                            |                     |      |                     |                 |                                                          |

| Pin Capacitance <sup>2</sup>                      |                     | 3    |                     | pF              |                                                          |

| Leakage/Bias Current                              | -3                  |      | 3                   | nA              |                                                          |

| Leakage Current Tempco <sup>2</sup>               |                     | ±0.1 |                     | nA/°C           |                                                          |

| SYS_SENSE                                         |                     |      |                     |                 | SYS_Sense Connected, Force Amplifier Inhibited           |

| Pin Capacitance <sup>2</sup>                      |                     | 3    |                     | pF              |                                                          |

| SYS_SENSE Impedance                               |                     | 1    | 1.3                 | kΩ              |                                                          |

| Leakage Current                                   | -3                  |      | 3                   | nA              |                                                          |

| Leakage Current Tempco <sup>2</sup>               |                     | ±0.1 |                     | nA/°C           |                                                          |

| SYS_FORCE                                         |                     |      |                     |                 | SYS_Force Connected, Force Amplifier Inhibited           |

| Pin Capacitance <sup>2</sup>                      |                     | 6    |                     | pF              |                                                          |

| SYS_FORCE Impedance                               |                     | 60   | 80                  | Ω               |                                                          |

| Leakage Current                                   | -3                  |      | 3                   | nA              |                                                          |

| Leakage Current Tempco <sup>2</sup>               |                     | ±0.1 |                     | nA/°C           |                                                          |

| COMBINED LEAKAGE at DUT                           |                     |      |                     |                 | Includes FOH, MEASVH, SYS_SENSE, SYS_FORCE,<br>EXTMEASIL |

| Leakage Current                                   | -15                 |      | 15                  | nA              |                                                          |

| Leakage Current                                   |                     | 1    | -                   |                 |                                                          |

| ÷                                                 |                     | ±0.5 |                     | nA/°C tvp       |                                                          |

| Leakage Current Tempco <sup>2</sup>               |                     | ±0.5 |                     | nA/°C typ       |                                                          |

| -                                                 | -500                | ±0.5 | 500                 | nA/°C typ<br>mV |                                                          |

| MEASURE OUTPUT (MEASOUT)                     |     |      |        |      | With respect to AGND                                                       |

|----------------------------------------------|-----|------|--------|------|----------------------------------------------------------------------------|

| Measure Output Voltage Span                  |     |      | 22.5   | v    | Software Programmable output range                                         |

| Measure Pin output Impedance                 |     |      | 100    | Ω    |                                                                            |

| Output leakage current                       | -3  |      | 3      | nA   | With SW12 off                                                              |

| Output Capacitance <sup>2</sup>              | 5   |      | 15     | pF   |                                                                            |

| Max Load Capacitance <sup>2</sup>            |     |      | 1      | μF   |                                                                            |

| Output Current drive <sup>2</sup>            |     | 2    | •      | mA   |                                                                            |

| Short Circuit Current <sup>2</sup>           | -10 | -    | 10     | mA   |                                                                            |

| MEASOUT Slew Rate <sup>2</sup>               | 10  | 2    | 10     | V/µs |                                                                            |

| MEASOUT enable time <sup>2</sup>             |     | 150  | 320    | ns   | Closing SW12, Measured from BUSY rising edge.                              |

| MEASOUT disable time <sup>2</sup>            |     | 400  | 1100   |      | Opening SW12, Measured from BUSY rising edge.                              |

|                                              |     |      | 1100   | ns   |                                                                            |

| MEASOUT MI to MV switching time <sup>2</sup> |     | 200  |        | ns   | Measured from BUSY rising edge.                                            |

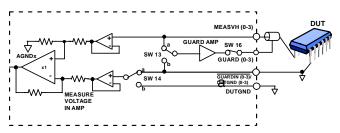

| GUARD OUTPUT                                 |     |      | 22.5   | N/   |                                                                            |

| Guard Output Voltage Span                    | 10  |      | 22.5   | V    |                                                                            |

| Guard Output Offset                          | -10 |      | 10     | mV   |                                                                            |

| Short Circuit Current <sup>2</sup>           | -10 |      | 10     | mA   |                                                                            |

| Max Load Capacitance <sup>2</sup>            |     |      | 1000   | nF   |                                                                            |

| Guard Output Impedance                       |     | 100  |        | Ω    |                                                                            |

| Slew Rate <sup>2</sup>                       |     | 5    |        | V/µs | $C_{LOAD} = 10 \text{ pf}$                                                 |

| Alarm Activation Time <sup>2</sup>           |     | 200  |        | μs   | Alarm delayed to eliminate false alarms.                                   |

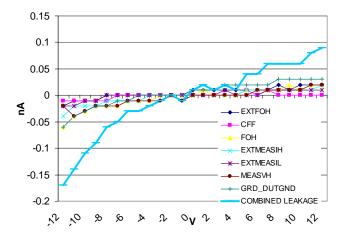

| FORCE AMPLIFIER                              |     |      |        |      |                                                                            |

| Slew Rate <sup>2</sup>                       |     | 0.4  |        | V/us | Ccomp=100pF, Cff=220pF, Cload=200pF                                        |

| Gain Bandwidth <sup>2</sup>                  |     | 1.3  |        | MHz  | Ccomp=100pF, Cff=220pF, Cload=200pF                                        |

| Max stable load Capacitance <sup>2</sup>     |     |      | 10,000 | pF   | $C_{COMP} = 100 pF.$ Larger Load cap requires larger $C_{COMP}$            |

|                                              |     |      | 100    | nF   | $C_{COMP} = 1$ nF. Larger Load cap requires larger $C_{COMP}$              |

| FV SETTLING TIME TO 0.05% OF FS              |     |      |        |      | Mid scale to full scale change, Measured from /SYNC rising edge, Clamps ON |

| 64mA Range <sup>2</sup>                      |     | 17   | 40     | μs   | Ccomp=100pF, Cff=220pF, Cload=200pF                                        |

| 2mA range <sup>2</sup>                       |     | 17   | 40     | μs   | Ccomp=100pF, Cff=220pF, Cload=200pF                                        |

| 200µA range <sup>2</sup>                     |     | 32   | 80     | μs   | Ccomp=100pF, Cff=220pF, Cload=200pF                                        |

| 20µA range <sup>2</sup>                      |     | TBD  | 80     | μs   | Ccomp=100pF, Cff=220pF, Cload=200pF                                        |

| 5µA range <sup>2</sup>                       |     | TBD  | 300    | μs   | Ccomp=100pF, Cff=220pF, Cload=200pF                                        |

| MI SETTLING TIME TO 0.05% OF FS              |     |      |        |      | Mid scale to full scale change, Measured from /SYNC rising edge, Clamps ON |

| 64mA Range <sup>2</sup>                      |     | 17   | 40     | μs   | Ccomp=100pF, Cff=220pF, Cload=200pF                                        |

| 2mA range <sup>2</sup>                       |     | 18   | 40     | μs   | Ccomp=100pF, Cff=220pF, Cload=200pF                                        |

| $200\mu$ A range <sup>2</sup>                |     | 40   | 80     | μs   | Ccomp=100pF, Cff=220pF, Cload=200pF                                        |

| 20μA range <sup>2</sup>                      |     | TBD  | TBD    | μs   | Ccomp=100pF, Cff=220pF, Cload=200pF                                        |

| 5µA range <sup>2</sup>                       |     | TBD  | TBD    | μs   | Ccomp=100pF, Cff=220pF, Cload=200pF                                        |

| FI SETTLING TIME TO 0.05% OF FS              |     |      |        | 1    | Mid scale to full scale change, Measured from /SYNC                        |

| FI JET I LING TIME I U U.UJ% UF FS           |     |      |        |      | rising edge, Clamps ON                                                     |

| 64mA Range <sup>2</sup>                      |     | 18   | 55     | μs   | Ccomp=100pF, Cload=200pF                                                   |

| 2mA range <sup>2</sup>                       |     | 22   | 85     | μs   | Ccomp=100pF, Cload=200pF                                                   |

| 200µA range <sup>2</sup>                     |     | 45   | 120    | μs   | Ccomp=100pF, Cload=200pF                                                   |

| 20µA range <sup>2</sup>                      |     | 1000 | TBD    | μs   | Ccomp=100pF, Cload=200pF                                                   |

| 5µA range <sup>2</sup>                       |     | 2300 | 4000   | μs   | Ccomp=100pF, Cload=200pF                                                   |

| MV SETTLING TIME TO .05% OF FS               |     |      |        |      | Mid scale to full scale change, Measured from /SYNC rising edge, Clamps ON |

| 64mA Range <sup>2</sup>                      |     | 20   | 65     | μs   | Ccomp=100pF, Cload=200pF                                                   |

| 2mA range <sup>2</sup>                       |     | 21   | 85     | μs   | Ccomp=100pF, Cload=200pF                                                   |

| 200µA range <sup>2</sup>                     |     | 50   | 120    | μs   | Ccomp=100pF, Cload=200pF                                                   |

| 20µA range <sup>2</sup>                      |     | 1000 | TBD    | μs   | Ccomp=100pF, Cload=200pF                                                   |

| 5µA range <sup>2</sup>                       |     | 2300 | 4000   | μs   | Ccomp=100pF, Cload=200pF                                                   |

# **Preliminary Technical Data**

| AD5522 |

|--------|

|--------|

| DAC SPECIFICATIONS                                  |                        |      |         |       |                                                                                                                                                                                              |

|-----------------------------------------------------|------------------------|------|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Resolution                                          |                        |      | 16      | Bits  |                                                                                                                                                                                              |

| Voltage Output Span <sup>2</sup>                    |                        |      | 22.5    | V     | $V_{REF}$ =5V, within a range of -16.25 to 22.5V                                                                                                                                             |

| Differential Nonlinearity <sup>2</sup>              | -1                     |      | 1       | LSB   | Guaranteed monotonic by design over temperature.                                                                                                                                             |

| COMPARATOR DAC DYNAMIC<br>SPECIFICATIONS            |                        |      |         |       |                                                                                                                                                                                              |

| Output Voltage Settling Time <sup>2</sup>           |                        |      | 1.5     | μs    | 500mV change to $\pm \frac{1}{2}$ LSB.                                                                                                                                                       |

| Slew Rate <sup>2</sup>                              |                        | 5.5  |         | V/µs  |                                                                                                                                                                                              |

| Digital-to-Analog Glitch Energy <sup>2</sup>        |                        | 20   |         | nV-s  |                                                                                                                                                                                              |

| Glitch Impulse Peak Amplitude <sup>2</sup>          |                        | 10   |         | mV    |                                                                                                                                                                                              |

| REFERENCE INPUT                                     |                        |      |         |       |                                                                                                                                                                                              |

| V <sub>REF</sub> DC Input Impedance                 | 1                      |      |         | MΩ    | Typically 100 MΩ.                                                                                                                                                                            |

| V <sub>REF</sub> Input Current                      | -10                    |      | 10      | μΑ    | Per input. Typically ±30 nA.                                                                                                                                                                 |

| V <sub>REF</sub> Range                              | 2                      |      | 5       | V     |                                                                                                                                                                                              |

| DIE TEMPERATURE SENSOR                              |                        |      |         |       |                                                                                                                                                                                              |

| Accuracy                                            |                        | ±7   |         | °C    |                                                                                                                                                                                              |

| Output Voltage at 25°C                              |                        | 1.5  |         | V     |                                                                                                                                                                                              |

| Output Scale Factor                                 |                        | 5    |         | mV/°C |                                                                                                                                                                                              |

| Output Voltage Range                                | 0                      |      | 3       | V     |                                                                                                                                                                                              |

| INTERACTION & CROSSTALK                             |                        |      |         |       |                                                                                                                                                                                              |

| Crosstalk (VM) <sup>2</sup>                         | -0.01                  |      | 0.01    | % FSR | All channels in FIMV mode, measure the voltage for one<br>channel in the highest current force range, once when all<br>three other channels are at FI = 0mA and once when<br>they are at 2mA |

| Crosstalk (MI) <sup>2</sup>                         | -0.01                  |      | 0.01    | % FSR | All channels in FVMI mode, measure the current for one channel in the lowest current measure range, once when all three other channels are at FV = -10V and once when they are at +10V       |

| Crosstalk within a channel <sup>2</sup>             |                        |      | 0.5     | mV    | All channels in FVMI mode, one channel at midscale,<br>measure the current for one channel in the lowest<br>current range, for a change in comparator or clamp DAC<br>levels for that PMU.   |

| Shorted DUT Crosstalk <sup>2</sup>                  |                        | TBD  | TBD     |       | S/C applied to one PMU channel, measure effect on other channels.                                                                                                                            |

| SPI INTERFACE LOGIC                                 |                        |      |         |       |                                                                                                                                                                                              |

| LOGIC INPUTS                                        |                        |      |         |       |                                                                                                                                                                                              |

| V⊮, Input High Voltage                              | 1.7/2.0                |      |         | V     | (2.3 to 2.7)/(2.7 to 5.25V) Jedec Compliant Input Levels                                                                                                                                     |

| V <sub>IL</sub> , Input Low Voltage                 |                        |      | 0.7/0.8 | V     | (2.3 to 2.7)/(2.7 to 5.25V) Jedec Compliant Input Levels                                                                                                                                     |

| I <sub>INH</sub> , I <sub>INL</sub> , Input Current | -1                     |      | 1       | μΑ    |                                                                                                                                                                                              |

| C <sub>IN</sub> , Input Capacitance <sup>2</sup>    |                        |      | 10      | pF    |                                                                                                                                                                                              |

| CMOS LOGIC OUTPUTS                                  |                        |      |         |       | SDO, CPOX                                                                                                                                                                                    |

| V <sub>OH</sub> , Output High Voltage               | DV <sub>CC</sub> – 0.4 |      |         | V     |                                                                                                                                                                                              |

| V <sub>OL</sub> , Output Low Voltage                |                        |      | 0.4     | V     | $I_{OL} = 500 \mu\text{A}$                                                                                                                                                                   |

| Tristate leakage current                            | -1                     |      | 1       | μΑ    |                                                                                                                                                                                              |

| Output Capacitance <sup>2</sup>                     |                        |      | 10      | pF    |                                                                                                                                                                                              |

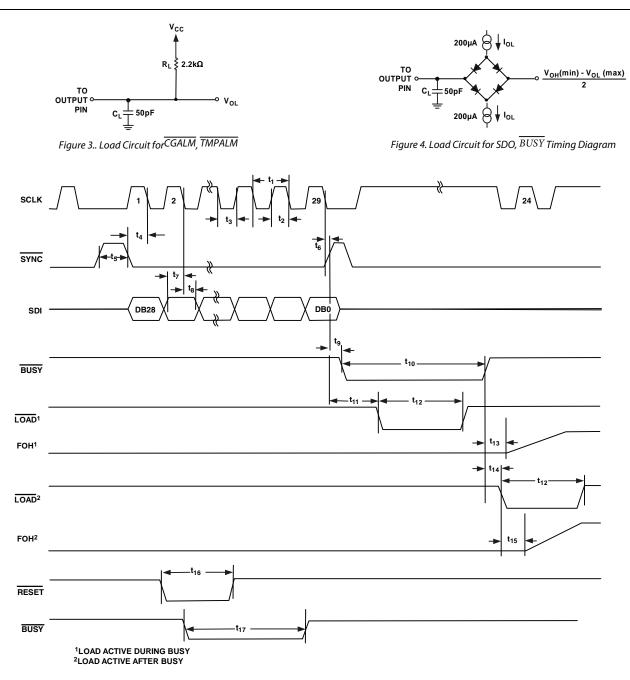

| OPEN DRAIN LOGIC OUTPUTS                            |                        |      |         |       | BUSY, TMPALM, CGALM                                                                                                                                                                          |

| Vol, Output Low Voltage                             |                        |      | 0.4     | V     | $I_{OL} = 500 \ \mu\text{A}, \ C_L = 50 pF, \ R_{PULLUP} = 1 k\Omega$                                                                                                                        |

| Output Capacitance <sup>2</sup>                     |                        |      | 10      | pF    |                                                                                                                                                                                              |

| LVDS INTERFACE LOGIC                                |                        |      |         |       |                                                                                                                                                                                              |

| LOGIC INPUTS – Reduced Range Link                   |                        |      |         |       |                                                                                                                                                                                              |

| Input Voltage Range                                 | 875                    |      | 1575    | mV    |                                                                                                                                                                                              |

| Input Differential Threshold                        | -100                   |      | 100     | mV    |                                                                                                                                                                                              |

| External Termination Resistance                     | 80                     | 100  | 120     | Ω     |                                                                                                                                                                                              |

| Differential Input Voltage                          | 100                    |      |         | mV    |                                                                                                                                                                                              |

| LOGIC OUTPUTS – Reduced Range Link                  |                        |      |         |       |                                                                                                                                                                                              |

| Output Offset Voltage                               |                        | 1200 |         | mV    |                                                                                                                                                                                              |

| Output Differential Voltage                         |                        | 400  |         | mV    |                                                                                                                                                                                              |

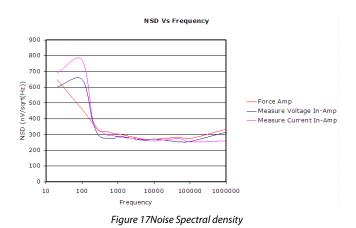

| NOISE PERFORMANCE                                    |     |     |      |        |                                                         |

|------------------------------------------------------|-----|-----|------|--------|---------------------------------------------------------|

| NSD of Measure Voltage In-Amp                        |     | 290 |      | nV/√Hz | @ 1kHz, measured at MEASOUT                             |

| NSD of Measure Current In-Amp                        |     | 290 |      | nV/√Hz | @ 1kHz, measured at MEASOUT                             |

| NSD of Force Amplifier                               |     | 300 |      | nV/√Hz | @ 1kHz, measured at FOH                                 |

| POWER SUPPLIES                                       |     |     |      |        |                                                         |

| AV <sub>DD</sub>                                     | 10  |     | 28   | V      | $ AV_{DD} - AV_{SS}  \le 33V$                           |

| AV <sub>ss</sub>                                     | -5  |     | -23  | V      |                                                         |

| DVcc                                                 | 2.3 |     | 5.25 | V      |                                                         |

| Al <sub>DD</sub>                                     |     |     | 25   | mA     | Internal ranges (5µA to 2mA), Excluding Load Conditions |

| Alss                                                 |     |     | -25  | mA     | Internal ranges (5µA to 2mA), Excluding Load Conditions |

| Al <sub>DD</sub>                                     |     |     | 35   | mA     | External range, Excluding Load Conditions               |

| Alss                                                 |     |     | -35  | mA     | External range, Excluding Load Conditions               |

| Dlcc                                                 |     |     | 3    | mA     |                                                         |

| Max Power Dissipation <sup>2</sup>                   |     |     | 7    | W      |                                                         |

| Power Supply Sensitivity <sup>2</sup>                |     |     |      |        | From DC to 1kHz                                         |

| ΔForced Voltage/ΔAV <sub>DD</sub>                    |     | -75 |      | dB     |                                                         |

| ΔForced Voltage/ΔAV <sub>ss</sub>                    |     | -75 |      | dB     |                                                         |

| $\Delta$ Measured Current/ $\Delta$ AV <sub>DD</sub> |     | -75 |      | dB     |                                                         |

| $\Delta$ Measured Current/ $\Delta$ AV <sub>ss</sub> |     | -75 |      | dB     |                                                         |

| $\Delta$ Forced Current/ $\Delta$ AV <sub>DD</sub>   |     | -75 |      | dB     |                                                         |

| ΔForced Current/ΔAV <sub>ss</sub>                    |     | -75 |      | dB     |                                                         |

| $\Delta$ Measured Voltage/ $\Delta$ AV <sub>DD</sub> |     | -75 |      | dB     |                                                         |

| $\Delta$ Measured Voltage/ $\Delta$ AV <sub>ss</sub> |     | -75 |      | dB     |                                                         |

| $\Delta$ Forced Voltage/ $\Delta$ DV <sub>cc</sub>   |     | -90 |      | dB     |                                                         |

| $\Delta$ Measured Current/ $\Delta$ DV <sub>cc</sub> |     | -90 |      | dB     |                                                         |

| $\Delta$ Forced Voltage/ $\Delta$ DV <sub>cc</sub>   |     | -90 |      | dB     |                                                         |

| $\Delta$ Measured Current/ $\Delta$ DV <sub>cc</sub> |     | -90 |      | dB     |                                                         |

$^1$  Typical specifications are at 25°C and nominal supply, ±15.25V, unless otherwise noted.  $^2$  Guaranteed by design and characterization, not production tested.

FV = Force Voltage, FI = Force Current, MV = Measure Voltage, MI = Measure Current FSR = Full Scale Range, FSCR = Full Scale Current Range, FS = Full Scale. Specifications subject to change without notice.

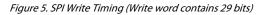

### **TABLE 2. TIMING CHARACTERISTICS**

$AV_{DD} \ge 10V$ ,  $AV_{SS} \le -5V$ ,  $|AV_{DD} - AV_{SS}| \ge 20V$  and  $\le 33V$ ,  $DV_{CC} = 2.3V$  to 5.25V,  $V_{REF} = 5V$

$(T_J = +25 \text{ to } +90^{\circ}\text{C}, \text{ max specs unless otherwise noted.})$

| SPI INTERFACE (Figure 5 and Figure 6) |                                           |        |                                                                             |  |  |  |  |

|---------------------------------------|-------------------------------------------|--------|-----------------------------------------------------------------------------|--|--|--|--|

| Parameter <sup>1, 2, 3</sup>          | Limit at TMIN, TMAX                       | Unit   | Description                                                                 |  |  |  |  |

|                                       | 595                                       | ns min | Single channel write time                                                   |  |  |  |  |

| t1                                    | 20                                        | ns min | SCLK Cycle Time.                                                            |  |  |  |  |

| t <sub>2</sub>                        | 8                                         | ns min | SCLK High Time.                                                             |  |  |  |  |

| t <sub>3</sub>                        | 8                                         | ns min | SCLK Low Time.                                                              |  |  |  |  |

| t4                                    | 10                                        | ns min | SYNC Falling Edge to SCLK Falling Edge Setup Time.                          |  |  |  |  |

| t <sub>5</sub>                        | 15                                        | ns min | Minimum SYNC High Time.                                                     |  |  |  |  |

| t <sub>6</sub>                        | 5                                         | ns min | 29th SCLK Falling Edge to SYNC Rising Edge.                                 |  |  |  |  |

| t <sub>7</sub>                        | 5                                         | ns min | Data Setup Time.                                                            |  |  |  |  |

| t <sub>8</sub>                        | 4.5                                       | ns min | Data Hold Time.                                                             |  |  |  |  |

| t9 <sup>3</sup>                       | 30                                        | ns max | SYNC Rising Edge to BUSY Falling Edge.                                      |  |  |  |  |

| t <sub>10</sub>                       |                                           |        | BUSY Pulse Width Low                                                        |  |  |  |  |

| 1 DAC X1                              | 1.25                                      | µs max | BUSY Pulse Width Low                                                        |  |  |  |  |

| 2 DAC X1                              | 1.75                                      | µs max | BUSY Pulse Width Low                                                        |  |  |  |  |

| 3 DAC X1                              | 2.25                                      | µs max | BUSY Pulse Width Low                                                        |  |  |  |  |

| 4 DAC X1                              | 2.75                                      | µs max | BUSY Pulse Width Low                                                        |  |  |  |  |

| Other Regs                            | 270                                       | ns max | BUSY Pulse Width Low, System Control Register/PMU Register/M or C Registers |  |  |  |  |

| t <sub>11</sub>                       | 20                                        | ns min | 29 <sup>th</sup> SLCK Falling EDGE to LOAD Falling Edge                     |  |  |  |  |

| t <sub>12</sub>                       | 20                                        | ns min | LOAD pulse width low                                                        |  |  |  |  |

| t <sub>13</sub>                       | 150                                       | ns min | BUSY rising edge to FOH Output Response time                                |  |  |  |  |

| t <sub>14</sub>                       | 0                                         | ns min | BUSY rising edge to LOAD falling edge                                       |  |  |  |  |

| t15                                   | 100                                       | ns max | LOAD rising edge to FOH Output Response time                                |  |  |  |  |

| t <sub>16</sub>                       | 10                                        | ns min | RESET Pulse Width Low.                                                      |  |  |  |  |

| t <sub>17</sub>                       | 300                                       | µs max | RESET Time Indicated by BUSY Low.                                           |  |  |  |  |

| t <sub>18</sub>                       | 100                                       | ns min | Minimum SYNC High Time in Readback Mode.                                    |  |  |  |  |

| t <sub>19</sub> <sup>4, 5</sup>       | 25                                        | ns max | $DV_{CC} = 5V$ to 5.25V, SCLK Rising Edge to SDO Valid.                     |  |  |  |  |

|                                       | 45                                        | ns max | DV <sub>cc</sub> = 3V to 3.7V, SCLK Rising Edge to SDO Valid                |  |  |  |  |

|                                       | 60                                        | ns max | DV <sub>cc</sub> = 2.3V to 3V, SCLK Rising Edge to SDO Valid                |  |  |  |  |

| LVDS INTERFAC                         | E (Figure 7)                              |        |                                                                             |  |  |  |  |

| Parameter <sup>1, 2, 3</sup>          | Limit at TMIN, TMAX                       | Unit   | Description                                                                 |  |  |  |  |

| t1                                    | 10                                        | ns min | SCLK Cycle Time.                                                            |  |  |  |  |

| t <sub>2</sub>                        | 4                                         | ns min | SCLK Pulse Width High and Low Time.                                         |  |  |  |  |

| t <sub>3</sub>                        | 2                                         | ns min | SYNC to SCLK Setup Time.                                                    |  |  |  |  |

| <b>t</b> 4                            | 2                                         | ns min | Data Setup Time.                                                            |  |  |  |  |

| t5                                    | 2                                         | ns min | Data Hold Time.                                                             |  |  |  |  |

| t <sub>6</sub>                        | 2                                         | ns min | SCLK to SYNC Hold Time.                                                     |  |  |  |  |

| t <sub>7</sub>                        | TBD                                       | ns min | SCLK Rising Edge to SDO Valid.                                              |  |  |  |  |

| t <sub>8</sub>                        | TBD<br>sign and characterization, not pro | ns min | SYNC high time                                                              |  |  |  |  |

<sup>1</sup> Guaranteed by design and characterization, not production tested.

<sup>2</sup> All input signals are specified with  $t_r = t_f = 2$  ns (10% to 90% of V<sub>cc</sub>) and timed from a voltage level of 1.2 V. <sup>3</sup>See Figure 5 and Figure 6

<sup>4</sup>This is measured with load circuit of Figure 4

${}^{\rm 5}$ SDO output gets slower with lower DV<sub>CC</sub> supply and may require use of slower SCLK.

# **Preliminary Technical Data**

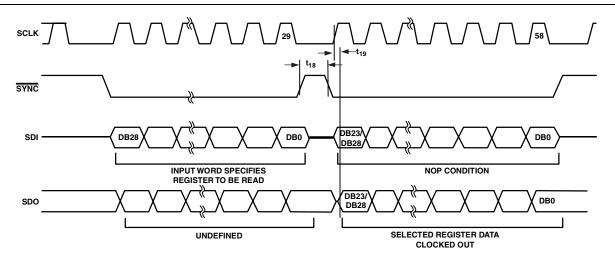

Figure 6. SPI Read Timing (Readback word contains 24 bits and can be clocked out with a minimum of 24 clock edges)

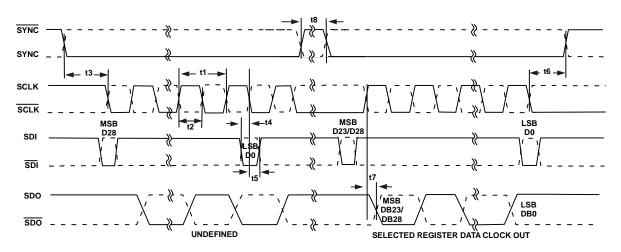

Figure 7. LVDS Read and Write Timing, (Readback word contains 24 bits and can be clocked out with a minimum of 24 clock edges)

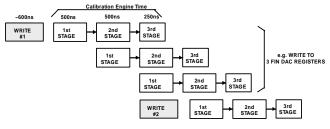

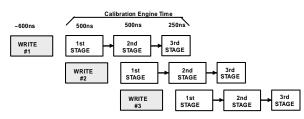

### AD5522

# **ABSOLUTE MAXIMUM RATINGS**

Table 3. AD5522 Absolute Maximum Ratings

| Parameter                                           | Rating                                           |

|-----------------------------------------------------|--------------------------------------------------|

| Supply Voltage AV <sub>DD</sub> to AV <sub>SS</sub> | 34V                                              |

| AV <sub>DD</sub> to AGND                            | -0.3V to 34V                                     |

| AV <sub>ss</sub> to AGND                            | 0.3V to -34V                                     |

| V <sub>REF</sub> to AGND                            | -0.3 V, +7V                                      |

| DUTGND to AGND                                      | AV <sub>DD</sub> +0.3V to AV <sub>SS</sub> -0.3V |

| REFGND to AGND                                      | $AV_{DD}$ +0.3V to $AV_{SS}$ -0.3V               |

| DV <sub>cc</sub> to DGND                            | - 0.3V to 7V                                     |

| AGND to DGND                                        | - 0.3V to +0.3V                                  |

| Digital Inputs to DGND                              | - 0.3V to DV <sub>cc</sub> +0.3V                 |

| Analog Inputs to AGND                               | $AV_{SS}$ - 0.3V to $AV_{DD}$ +0.3V              |

| Storage Temperature                                 | –65°C to +125°C                                  |

| Operating Junction Temperature                      | +25 to +90°C                                     |

| Reflow Soldering                                    |                                                  |

| Peak Temperature                                    | 230°C                                            |

| Time at Peak Temperature                            | 10s to 40s                                       |

| Junction Temperature                                | 150°C max                                        |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition s above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **THERMAL RESISTANCE<sup>3</sup>**

Thermal resistance values are specified for the worst-case conditions, i.e., specified for device soldered in circuit board for surface mount packages.

### Table 4. Thermal Resistance (JEDEC 4 layer (1S2P) board)

| Air Flow (LFPM)       |     | 0    | 200  | 500  | Unit |

|-----------------------|-----|------|------|------|------|

| TQFP Exposed Pad Down | θја | 22.3 | 17.2 | 15.1 | °C/W |

|                       | οιθ | 4.8  |      |      | °C/W |

| TQFP Exposed Pad Up   | Αιθ | TBD  | TBD  | TBD  | °C/W |

|                       | эιθ | 2    |      |      | °C/W |

Table 5. Thermal Resistance (JEDEC 4 layer (1S2P) board with cooling plate<sup>4</sup> at 45°C, natural convection at 55°C ambient)

| Package Thermals      | θιΑ | οισ | Unit |

|-----------------------|-----|-----|------|

| TQFP Exposed Pad Down | 5.4 | 4.8 | °C/W |

| TQFP Exposed Pad Up   | 3.0 | 2   | °C/W |

<sup>3</sup> Simulated Thermal information.

<sup>4</sup> Assumes perfect thermal contact between cooling plate and exposed paddle

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

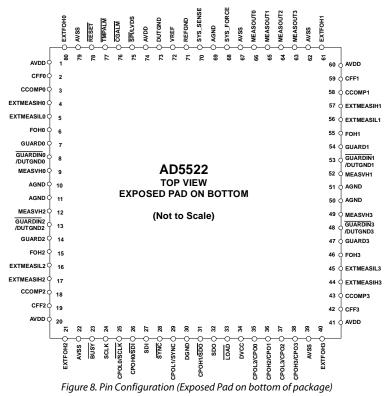

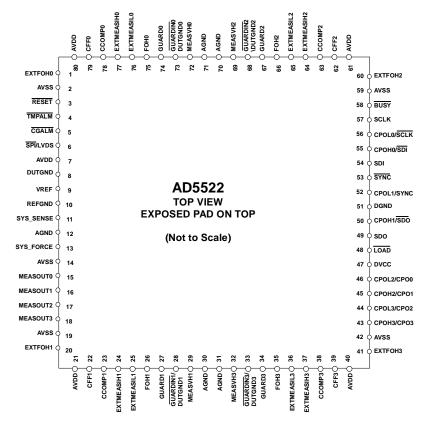

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

| Pin No.                | Pin No.               | Mnemonic               | Description                                                                                                                                                                                                                                                                                                                |

|------------------------|-----------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bottom                 | Тор                   | Exposed Pad            | The exposed pad is electrically connected to AVss.                                                                                                                                                                                                                                                                         |

|                        |                       |                        | TQFP with exposed pad on BOTTOM: For enhanced thermal, electrical and board level performance, the exposed paddle on the bottom of the package should be soldered to a corresponding thermal land paddle on the PCB.                                                                                                       |

| 22, 39, 62,<br>67, 79, | 2, 14, 19,<br>42,59,  | AV <sub>SS</sub> (0-4) | Negative analog supply voltage                                                                                                                                                                                                                                                                                             |

| 1, 20, 41, 60,<br>74   | 7, 21, 40,<br>61, 80  | AV <sub>DD</sub> (0-4) | Positive analog supply voltage                                                                                                                                                                                                                                                                                             |

| 33                     | 48                    | LOAD                   | Active low logic input used for synchronizing updates within one device or across a group of devices. If synchronization is not required, LOAD may be tied low and updates to DAC channels or PMU modes will happen as they are presented to the device. See the BUSY and LOAD FUNCTIONS section for detailed information. |

| 34                     | 47                    | DVcc                   | Digital supply voltage                                                                                                                                                                                                                                                                                                     |

| 10, 11, 50,<br>51, 69  | 12, 30, 31,<br>70, 71 | AGND                   | Analog ground, reference points for force and measure circuitry                                                                                                                                                                                                                                                            |

| 30                     | 51                    | DGND                   | Digital ground reference point.                                                                                                                                                                                                                                                                                            |

| 23                     | 58                    | BUSY                   | Open Drain active low input/output indicating the status of interface.                                                                                                                                                                                                                                                     |