# Quad +15V 256-Step DigiPOTs with Pin Selectable SPI / I<sup>2</sup>C Digital Interface

# **Preliminary Technical Data**

AD5263

#### **FEATURES**

256 Position

4-Channel (Independently Programmable)

20k, 50k, 200k Ohms

Low Temperature Coefficient 50ppm/°C

Selectable Digital Interface (3-Wire SPI Compatible or 2-Wire I<sup>2</sup>C Compatible Serial Data Input)

Operating temperature range -40 to 125°C

+5 to +15V Single-Supply; ±5V Dual-Supply Operation

#### APPLICATIONS

Mechanical Potentiometer Replacement

Optical Network Laser LED Adjust

Instrumentation: Gain, Offset Adjustment

Stereo Channel Audio Level Control

Automotive Electronics Adjustment

Programmable Voltage to Current Conversion

Programmable Filters, Delays, Time Constants

Line Impedance Matching

Low Resolution DAC Replacement

#### GENERAL DESCRIPTION

The AD5263 is the industry first quad channel, 256 position, digital potentiometer<sup>1</sup> selectable digital interface. These devices perform the same electronic adjustment function as mechanical potentiometers or variable resistor with enhanced resolution, solidstate reliability, and superior low temperature coefficient performance. Each Channel of the AD5263 contains a fixed resistor with a wiper contact that taps the fixed resistor value at a point determined by a digital code loaded into the 3 wire SPI or 2-wire I<sup>2</sup>C compatible serial-input register. The resistance between the wiper and either end point of the fixed resistor varies linearly with respect to the digital code transferred into the RDAC latch<sup>1</sup>. The variable resistor offers a completely programmable value of resistance, between the A terminal and the wiper or the B terminal and the wiper. The fixed A to B terminal resistance of 20k, 50k or  $200k\Omega$  has a nominal temperature coefficient of 50 ppm/°C. Unlike majority of the digital potentiometers in the market, these devices can operate up to 15V or ±5V provided proper supply voltages are furnished.

The AD5263 are available in thin narrow body TSSOP-24. All parts are guaranteed to operate over the extended automotive temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

#### **Functional Block Diagram** RDAC 4 RDAC 1 RDAC 2 RDAC 3 REGISTER REGISTER REGISTER REGISTER AD5263 ADDRESS DECODER CLK /SCL SDI / SDA SERIAL INPUT CS / ADO SPL/I2C REGISTER SDO / 01

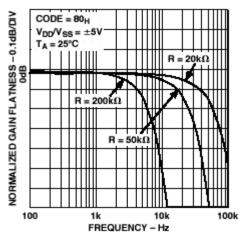

Figure 1 Normalized Gain Flatness Versus Frequency.

08 AUG '02, REV PrD

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

# Quad +15V Digital Potentiometers

AD5263

### ELECTRICAL CHARACTERISTICS 20K, 50K, 200K OHM VERSION (VDD = +5V, VSS = -5V, VL = +5V,

$V_A = +V_{DD}$ ,  $V_B = 0V$ ,  $-40^{\circ}C < T_A < +125^{\circ}C$  unless otherwise noted.) **Parameter** Symbol **Conditions** Min Typ<sup>1</sup> Units Max DC CHARACTERISTICS RHEOSTAT MODE Specifications apply to all VRs Resistor Differential NL<sup>2</sup> R-DNL R<sub>WB</sub>, V<sub>A</sub>=NC -1 ±1/4 +1 LSB Resistor Nonlinearity<sup>2</sup> R-INL -2 +2 R<sub>WB</sub>, V<sub>A</sub>=NC  $\pm 1/2$ LSB  $T_A = 25^{\circ}C$ Nominal resistor tolerance3  $\Delta R_{AB}$ -30 30 % Resistance Temperature Coefficient Wiper = No Connect 30 ppm/°C  $\Delta R_{AB}/\Delta T$  $I_W = 1 \text{ V/R}_{AB}, V_{DD} = +5 \text{ V}$ 50 100 Ω Wiper Resistance  $R_{W}$ DC CHARACTERISTICS POTENTIOMETER DIVIDER MODE Specifications apply to all VRs Resolution 8 Bits Differential Nonlinearity4 DNL -1 ±1/4 +1 LSB Integral Nonlinearity4 INL -2 ±1/2 +2 LSB Voltage Divider Temperature Coefficient  $\Delta V_{M}/\Delta T$ Code = 40H5 ppm/°C Full-Scale Error  $V_{\text{WFSE}}$ Code = FFH -2 -1 +0 LSB Zero-Scale Error  $V_{WZSE}$ Code = 00H0 +1 +2 LSB **RESISTOR TERMINALS** Voltage Range<sup>5</sup>  $V_{A.B.W}$  $V_{SS}$  $V_{DD}$ ٧  $\mathsf{C}_{\mathsf{A},\mathsf{B}}$ Capacitance<sup>6</sup> Ax, Bx f = 1 MHz, measured to GND, Code = 40<sub>H</sub> **TBD** pF pF Capacitance<sup>6</sup> Wx f = 1 MHz, measured to GND, Code =  $40_H$ TBD  $\mathsf{C}_\mathsf{W}$  $V_A = V_B = V_{DD} / 2$ Common-Mode Leakage Ісм 1 nΑ **DIGITAL INPUTS** Input Logic High  $V_{IH}$ 2.4 ٧  $V_{\mathsf{IL}}$ V Input Logic Low 8.0 Input Logic High  $V_{IH}$  $V_L = +3V, V_{SS} = 0V$ ٧ 2.1 Input Logic Low  $V_{\mathsf{IL}}$  $V_L = +3V, V_{SS} = 0V$ 0.6 V  $V_{IN} = 0V \text{ or } +5V$ Input Current  $I_{\rm IL}$ ±1 μΑ Input Capacitance<sup>6</sup>  $C_{IL}$ 5 pF **DIGITAL Output** 2.4 5.5 01,02  $V_{OH}$ IOH=0.4mA ٧ 01,02  $V_{OL}$  $I_{OI} = -1.6 \text{mA}$ 0 0.4 V SDA  $V_{OL}$  $I_{OL} = -6mA$ 0.6 V **SDA**  $V_{OL}$  $I_{OL} = -3mA$ 0.4 V Three-State Leakage Current  $V_{IN} = 0V \text{ or } +5V$  $I_{OZ}$ ±1 μΑ Output Capacitance<sup>6</sup> 3 8  $C_{OZ}$ pF POWER SUPPLIES Logic Supply  $V_{I}$ 2.7 5.5 ٧ Power Single-Supply Range ٧  $V_{SS} = 0V$ 5 16.5  $V_{DD RANGE}$ Power Dual-Supply Range  $V_{\rm DD/SS\ RANGE}$ ±4.5 ±5.5 ٧ μΑ Logic Supply Current  $I_{\parallel}$  $V_1 = +5V$ 60 Positive Supply Current  $V_{III} = +5V \text{ or } V_{II} = 0V$ 1  $I_{DD}$ μΑ μΑ **Negative Supply Current**  $V_{SS} = -5V$ 1  $I_{SS}$ Power Dissipation9  $V_{IH}$  = +5V or  $V_{II}$  = 0V,  $V_{DD}$  = +5V,  $V_{SS}$  = -5V  $P_{\text{DISS}}$ 0.6 mWPower Supply Sensitivity **PSS**  $\Delta V_{DD} = +5V \pm 10\%$ 0.0002 0.005 %/% DYNAMIC CHARACTERISTICS<sup>6, 10</sup> Bandwidth -3dB BW 20K 400 KHz  $V_{\Delta}$  =1Vrms,  $V_{R}$  = 0V, f=1KHz,  $R_{AB}$  = 20K $\Omega$ **Total Harmonic Distortion**  $THD_{W}$ 0.008 %  $V_A = 10V$ ,  $V_B = 0V$ ,  $\pm 1$  LSB error band 2 V<sub>w</sub> Settling Time  $t_S$ μs  $R_{WB} = 10K\Omega$ , f = 1KHz, RS = 0Resistor Noise Voltage 9 nV√Hz  $e_{\text{N WB}}$

# Quad +15V Digital Potentiometers

AD5263

μs

### ELECTRICAL CHARACTERISTICS 20K, 50K, 200K OHM VERSION (VDD = +5V, VSS = -5V, VL = +5V,

$V_A = +V_{DD}$ ,  $V_B = 0V$ ,  $-40^{\circ}C < T_A < +125^{\circ}C$  unless otherwise noted.) **Parameter Symbol Conditions** Min Typ<sup>1</sup> Max Units SPI (DIS='0') INTERFACE TIMING CHARACTERISTICS applies to all parts (Notes 6,12) Input Clock Pulse Width Clock level high or low 50  $t_{CH}, t_{CL}$ ns Data Setup Time 20 ns  $t_{DS}$ Data Hold Time 20 ns  $t_{DH}$ CLK to SDO Propagation Delay<sup>13</sup>  $R_L = 1K\Omega$ ,  $C_L < 20pF$ 1 150  $t_{PD}$ ns CS Setup Time 20  $t_{\text{CSS}} \\$ ns CS High Pulse Width 40 ns  $t_{CSW}$ Reset Pulse Width 90  $t_{RS}$ ns CLK Fall to CS Rise Hold Time 0  $t_{CSH}$ ns CS Rise to Clock Rise Setup 10 t<sub>CS1</sub> ns I<sup>2</sup>C (DIS='1') INTERFACE TIMING CHARACTERISTICS applies to all parts(Notes 6,12) SCL Clock Frequency 0 400 KHz  $t_{\mathsf{BUF}}$  Bus free time between STOP & START  $t_1$ 1.3 μs t<sub>HD:STA</sub> Hold Time (repeated START)  $t_2$ After this period the first clock pulse is generated 0.6 μs  $t_{\text{LOW}}$  Low Period of SCL Clock 1.3  $t_3$ us tHIGH High Period of SCL Clock  $t_4$ 0.6 US t<sub>SU:STA</sub> Setup Time For START Condition  $t_5$ 0.6 us t<sub>HD:DAT</sub> Data Hold Time 0 0.9  $t_6$ μs t<sub>SU:DAT</sub> Data Setup Time 100 t<sub>7</sub> ns t<sub>F</sub> Fall Time of both SDA & SCL signals t<sub>8</sub> 300 ns t<sub>R</sub> Rise Time of both SDA & SCL signals 300 t9 ns

#### NOTES:

- 1. Typicals represent average readings at +25 °C and  $V_{DD} = +5V$ ,  $V_{SS} = -5V$ .

- Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the

relative step change from ideal between successive tap positions. Parts are guaranteed monotonic. I<sub>W</sub> = V<sub>DD</sub>/R for both V<sub>DD</sub>=+5V, V<sub>SS</sub>=-5V.

0.6

3.  $V_{AB} = V_{DD}$ , Wiper  $(V_W) = No$  connect

t<sub>SU:STO</sub> Setup time for STOP Condition

- INL and DNL are measured at V<sub>W</sub> with the RDAC configured as a potentiometer divider similar to a voltage output D/A converter. VA = V<sub>DD</sub> and V<sub>B</sub> = 0V. DNL specification limits of ±1LSB maximum are Guaranteed Monotonic operating conditions.

- 5. Resistor terminals A, B, W have no limitations on polarity with respect to each other

- Guaranteed by design and not subject to production test.

- 7. Measured at the Ax terminals. All Ax terminals are open circuited in shutdown mode.

- 8. Worst case supply current consumed when input all logic-input levels set at 2.4V, standard characteristic of CMOS logic.

t<sub>10</sub>

- P<sub>DISS</sub> is calculated from (I<sub>DD</sub> x V<sub>DD</sub>). CMOS logic level inputs result in minimum power dissipation.

- 10. All dynamic characteristics use  $V_{DD}$  = +5V,  $V_{SS}$  = -5V,  $V_L$  = +5V

- 11. Measured at a V<sub>W</sub> pin where an adjacent V<sub>W</sub> pin is making a full-scale voltage change.

- 12. See timing diagram for location of measured values. All input control voltages are specified with t<sub>R</sub>=t<sub>F</sub>=2ns(10% to 90% of +3V) and timed from a voltage level of 1.5V. Switching characteristics are measured using V<sub>L</sub> = +5V.

- 13. Propagation delay depends on value of V<sub>DD</sub>, R<sub>L</sub>, and C<sub>L</sub> see applications text.

- 14. The AD5260/AD5262 contains 1,968 transistors. Die Size: 89mil x 105mil, 9,345sq. mil.

# Quad +15V Digital Potentiometers

AD5263

| ABSOLUTE MAXIMUM RATINGS ( $T_A$                        | = $+25$ °C, unless                |

|---------------------------------------------------------|-----------------------------------|

| otherwise noted)                                        |                                   |

| V <sub>DD</sub> to GND                                  | 0.3, +15V                         |

| V <sub>SS</sub> to GND                                  | 0V, -7V                           |

| V <sub>DD</sub> to V <sub>SS</sub>                      | +15V                              |

| V <sub>A</sub> , V <sub>B</sub> , V <sub>W</sub> to GND | V <sub>SS</sub> , V <sub>DD</sub> |

| $A_X - B_X, A_X - W_X, B_X - W_X$                       |                                   |

| Intermittent <sup>2</sup>                               | ±20mA                             |

| Continuous                                              | ±2mA                              |

| Digital Inputs & Output Voltage to GND                  | 0V, +7V                           |

| Operating Temperature Range                             | 40°C to +85°C                     |

| Maximum Junction Temperature (T <sub>J</sub> MAX)       | +150°C                            |

| Storage Temperature                                     | 65°C to +150°C                    |

| Lead Temperature (Soldering, 10 sec)                    | +300°C                            |

| Vapor Phase (60 sec)                                    | +215 °C                           |

|                                                         |                                   |

| Infrared (15 sec)                                | +220 °C                                |

|--------------------------------------------------|----------------------------------------|

| Thermal Resistance $^*$ $\theta_{JA}$ ,          |                                        |

| TSSOP-24                                         | 143°C/W                                |

| *Package Power Dissipation = (T <sub>J</sub> MA) | X - T <sub>A</sub> ) / θ <sub>JA</sub> |

#### **NOTES**

- 1. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Maximum terminal current is bounded by the maximum current handling of the switches, maximum power dissipation of the package, and maximum applied voltage across any two of the A, B, and W terminals at a given resistance.

#### **ORDERING GUIDE**

| Model              | $R_{AB}$    | Temp       | Package     | Package | # Parts per | Top Mark*  |

|--------------------|-------------|------------|-------------|---------|-------------|------------|

|                    | $(k\Omega)$ |            | Description | Option  | Container   |            |

| AD5263BRU20        | 20          | -40/+125°C | TSSOP-24    | RU-24   | 62          | AD5263B20  |

| AD5263BRU20-REEL7  | 20          | -40/+125°C | TSSOP-24    | RU-24   | 1,000       | AD5263B20  |

| AD5263BRU50        | 50          | -40/+125°C | TSSOP-24    | RU-24   | 62          | AD5263B50  |

| AD5263BRU50-REEL7  | 50          | -40/+125°C | TSSOP-24    | RU-24   | 1,000       | AD5263B50  |

| AD5263BRU200       | 200         | -40/+125°C | TSSOP-24    | RU-24   | 62          | AD5263B200 |

| AD5263BRU200-REEL7 | 200         | -40/+125°C | TSSOP-24    | RU-24   | 1,000       | AD5263B200 |

<sup>\*</sup>Line 1 contains part number, line 2 branding containing differentiating detail by part type and ADI logo symbol, line 3 contains date code YWW.

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD5263 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

SDO (Data Out)

CLK

cs

Vout 0٧

$V_{DD}$

# Quad +15V Digital Potentiometers

AD5263

tPD MAX

tcsH1

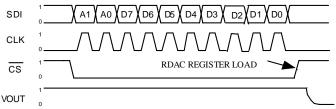

## SPI Compatible Digital Interface (DIS='0')

TABLE IA: SPI 10-Bit Serial-Data Word

| Forma | ιt |

|-------|----|

|       | •• |

| ADDR    |           | DATA |           |           |           |           |           |           |           |  |  |  |  |

|---------|-----------|------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|--|--|--|--|

| B9      | <b>B8</b> | B7   | <b>B6</b> | <b>B5</b> | <b>B4</b> | <b>B3</b> | <b>B2</b> | <b>B1</b> | <b>B0</b> |  |  |  |  |

| A1      | A0        | D7   | D6        | D5        | D4        | D3        | D2        | D1        | D0        |  |  |  |  |

|         |           | MSB  |           |           |           |           |           |           | LSB       |  |  |  |  |

| $2^{9}$ |           | 27   |           |           |           |           |           |           | $2^{0}$   |  |  |  |  |

Figure 1B. Detail SPI Timing Diagram

A'x or D'x

A'x or D'x

Figure 1A. SPI Timing Diagram

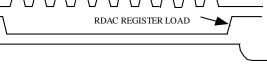

## I<sup>2</sup>C Compatible Digital Interface (DIS='1')

## TABLE IIA: I<sup>2</sup>C Write Mode Data Word Format

| S | 0 | 1 | 0    | 1     | 1     | A<br>D<br>1 | A<br>D<br>0 | W | Α | Х                | A<br>1 | A<br>0 | R<br>S | S<br>D | 0 | 0 2 | Х | Α    | D<br>7 | D<br>6 | D<br>5 | D<br>4 | D<br>3 | D<br>2 | D<br>1 | D<br>0 | Α | Р |

|---|---|---|------|-------|-------|-------------|-------------|---|---|------------------|--------|--------|--------|--------|---|-----|---|------|--------|--------|--------|--------|--------|--------|--------|--------|---|---|

|   |   |   | Slav | e Ado | dress | Byte        |             |   |   | Instruction Byte |        |        |        |        |   |     |   | Data | Byte   | ;      |        |        |        |        |        |        |   |   |

## TABLE IIB: I<sup>2</sup>C Read Mode Data Word Format:

| S | 0                  | 1 | 0 | 1 | 1 | 0 | A<br>D<br>0 | R | Α | D<br>7 | D<br>8 | D<br>5 | D<br>4 | D<br>3 | D<br>2 | D<br>1 | D<br>0 | Α | Р |

|---|--------------------|---|---|---|---|---|-------------|---|---|--------|--------|--------|--------|--------|--------|--------|--------|---|---|

|   | Slave Address Byte |   |   |   |   |   |             |   |   |        | Data   | Byte   |        |        |        |        |        |   |   |

S = Start Condition

P = Stop Condition

$\mathbf{A} = Acknowledge$

AD1, AD0 = Package pin programmable address bits, Must match with the logic states at pins AD1, AD0

A1, A0 = RDAC sub address select

**RS** = Software Reset wiper (A1, A0) to mid scale position

**SD** = Shutdown active high, ties wiper (A1, A0) to terminal A, opens terminal B, RDAC register contents are not disturbed. To exit shutdown a command SD = '0' must be executed for each RDAC (A1, A0).

$\overline{\mathbf{W}} = \text{Write} = \mathbf{0}$

$\mathbf{R} = \text{Read} = '1'$

**D7,D6,D5,D4,D3,D2,D1,D0** = Data Bits

X = Don't Care

Figure 2. I<sup>2</sup>C Compatible Detail Timing Diagram

08 AUG '02. REV PrD

# Quad +15V Digital Potentiometers

AD5263

|     | AD520               | 63 PIN CONFI   | <b>GURATION</b>           | 9  | DIS         | Digital Interface Select (SPI/I <sup>2</sup> C Select); SPI when DIS='0', I <sup>2</sup> C when DIS='1' |

|-----|---------------------|----------------|---------------------------|----|-------------|---------------------------------------------------------------------------------------------------------|

|     | B1                  | 1              | 24 B2                     | 10 | $V_{LOGIC}$ | Logic Supply Voltage, needs to be                                                                       |

|     | A1                  | 2              | 23 A2                     |    | Logic       | same voltage as the digital logic                                                                       |

|     | W1                  | 3              | 22 W2                     |    |             | controlling the AD5263.                                                                                 |

|     | В3                  | 4              | 21 B4                     | 11 | SDI/SDA     | SDI = 3-wire Serial Data Input/ SDA =                                                                   |

|     | DJ                  | AD5263         | 21 64                     |    |             | 2-wire Serial Data Input/Output                                                                         |

|     | A3                  | 5 TSSOP-24     | 20 A4                     | 12 | CLK/SCL     | Serial Clock Input                                                                                      |

|     | W3                  | 6              | 19 W4                     | 13 | CS/AD0      | Chip Select / I <sup>2</sup> C Compatabile Device                                                       |

|     | $V_{DD}$            | 7              | 18 V <sub>SS</sub>        |    |             | Address Bit 0                                                                                           |

|     |                     |                |                           | 14 | RESB/AD1    | RESETB/I <sup>2</sup> C Compatabile Device                                                              |

|     | GND                 | 8              | 17 NC/O2                  |    |             | Address Bit 1                                                                                           |

|     | DIS                 | 9              | 16 SDO/O1                 | 15 | SHDN        | Shutdown Ties wiper to terminal A,                                                                      |

|     | $V_{LOGIC}$         | 10             | 15 SHDN                   |    |             | opens terminal B                                                                                        |

|     |                     |                |                           | 16 | SDO/O1      | Serial Data Output, Open Drain                                                                          |

|     | SDI/SDA             | 11             | 14 RESB/AD1               |    |             | transistor requires pull-up                                                                             |

|     | CLK/SCL             | 12             | 13 CS/AD0                 |    |             | resistor/Digital Output O1, can be used                                                                 |

|     |                     |                |                           |    |             | to drive external logic                                                                                 |

|     |                     |                |                           | 17 | NC/O2       | No Connection/Digital Output O2, can                                                                    |

|     |                     |                |                           |    |             | be used to drive external logic                                                                         |

| TAB | L <b>E III:</b> AD5 | 263 PIN Descri | ptions                    | 18 | $V_{SS}$    | Negative power supply, specified for                                                                    |

| Pin | Name                | Description    | n                         |    |             | operation from 0 to -5V.                                                                                |

| 1   | B1                  | Resistor terr  | ninal B1                  | 19 | W4          | Wiper terminal W4 (ADDR=11)                                                                             |

| 2   | A1                  | Resistor terr  | ninal A1 (ADDR=00)        | 20 | A4          | Resistor terminal A4                                                                                    |

| 3   | W1                  | Wiper termi    | nal W1                    | 21 | B4          | Resistor terminal B4                                                                                    |

| 4   | В3                  | Resistor terr  | ninal B3                  | 22 | W2          | Wiper terminal W2 (ADDR=01)                                                                             |

| 5   | A3                  | Resistor terr  | ninal A3                  | 23 | A2          | Resistor terminal A2                                                                                    |

| 6   | W3                  |                | nal W3 (ADDR=10)          | 24 | B2          | Resistor terminal B2                                                                                    |

| 7   | $V_{\mathrm{DD}}$   | Positive pov   | ver supply, specified for |    |             |                                                                                                         |

|     |                     | +5V to +15V    | V operation               |    |             |                                                                                                         |

| 8   | GND                 | Ground         |                           |    |             |                                                                                                         |

|     |                     |                |                           |    |             |                                                                                                         |

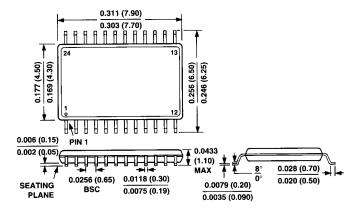

## **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm)

24-Lead Thin Surface Mount TSSOP Package (RU-24)

08 AUG '02, REV PrD