NanoAmp Solutions, Inc. 670 North McCarthy Blvd. Suite 220, Milpitas, CA 95035 ph: 408-935-7777, FAX: 408-935-7770 www.nanoamp.com

# N02M0818L1A

### 2Mb Ultra-Low Power Asynchronous Medical CMOS SRAM 256Kx8 bit

### Overview

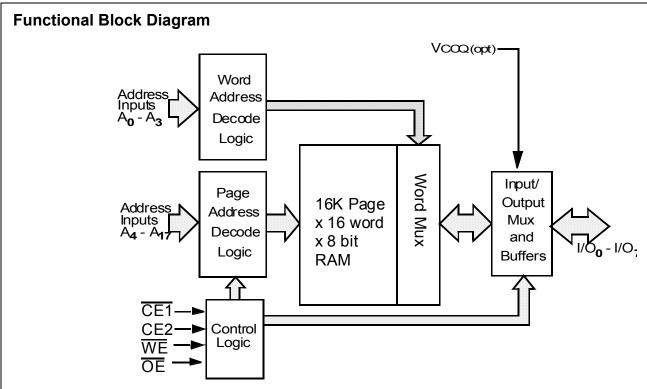

The N02M0818L1A is an integrated memory device intended for non life-support (Class 1 or 2) medical applications. This device comprises a 2 Mbit Static Random Access Memory organized as 262,144 words by 8 bits. The device is designed and fabricated using NanoAmp's advanced CMOS technology with reliability inhancements for medical users. The base design is the same as NanoAmp's N02M0818L2A, which has further reliability processing for life-support (Class 3) medical applications. The device operates with two chip enable (CE1 and CE2) controls and output enable (OE) to allow for easy memory expansion. The N02M0818L1A is optimal for various applications where low-power is critical such as battery backup and hand-held devices. The device can operate over a very wide temperature range of -40°C to +85°C and is available in JEDEC standard packages compatible with other standard 256Kb x 8 SRAMs

#### Features

- Single Wide Power Supply Range 1.4 to 2.3 Volts - STSOP package

- Dual Power Supply Die Only 1.4 to 2.3 Volts - VCC 1.4 to 3.6 Volts - VCCQ

- Very low standby current 200nA maximum at 2.0V and 37 deg C

- Very low operating current 1 mA at 2.0V and 1µs (Typical)

- Very low Page Mode operating current 0.5mA at 1.0V and 1µs (Typical)

- Simple memory control Dual Chip Enables (CE1 and CE2) Output Enable (OE) for memory expansion

- Low voltage data retention Vcc = 1.2V

- Automatic power down to standby mode

- Special Processing to reduce Soft Error Rate (SER)

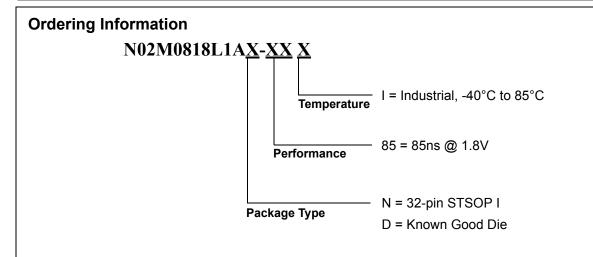

## Product Family

| Part Number  | Package Type   | Operating<br>Temperature | Power<br>Supply (Vcc) | Speed        | Standby<br>Current<br>(I <sub>SB</sub> ), Max | Operating<br>Current (Icc),<br>Max |

|--------------|----------------|--------------------------|-----------------------|--------------|-----------------------------------------------|------------------------------------|

| N02M0818L1AN | 32 - STSOP I   |                          | 1.4V - 2.3V           | 85ns @ 1.7V  | 20 uA                                         | 2.5 mA @ 1MHz                      |

| N02M0818L1AD | Known Good Die | -40°C to +85°C           | 1.40 - 2.30           | 150ns @ 1.4V | 20 μΑ                                         |                                    |

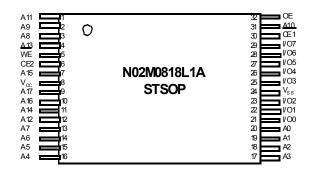

#### Pin Configuration

#### **Pin Descriptions**

| Pin Name                           | Pin Function            |

|------------------------------------|-------------------------|

| A <sub>0</sub> -A <sub>17</sub>    | Address Inputs          |

| WE                                 | Write Enable Input      |

| CE1, CE2                           | Chip Enable Input       |

| OE                                 | Output Enable Input     |

| 1/0 <sub>0</sub> -1/0 <sub>7</sub> | Data Inputs/Outputs     |

| V <sub>CCQ</sub>                   | Output Power (die only) |

| V <sub>CC</sub>                    | Power                   |

| V <sub>SS</sub>                    | Ground                  |

Stock No. 23208-01 11/01/02

#### **Functional Description**

| CE1 | CE2 | WE | OE             | I/O <sub>0</sub> - I/O <sub>7</sub> | MODE                 | POWER   |

|-----|-----|----|----------------|-------------------------------------|----------------------|---------|

| Н   | Х   | Х  | Х              | High Z                              | Standby <sup>1</sup> | Standby |

| Х   | L   | Х  | Х              | High Z                              | Standby <sup>1</sup> | Standby |

| L   | Н   | L  | X <sup>2</sup> | Data In                             | Write <sup>2</sup>   | Active  |

| L   | Н   | Н  | L              | Data Out                            | Read                 | Active  |

| L   | Н   | Н  | Н              | High Z                              | Active               | Active  |

1. When the device is in standby mode, control inputs ( $\overline{WE}$  and  $\overline{OE}$ ), address inputs and data input/outputs are internally isolated from any external influence and disabled from exerting any influence externally.

2. When  $\overline{\text{WE}}$  is invoked, the  $\overline{\text{OE}}$  input is internally disabled and has no effect on the circuit.

#### Capacitance<sup>1</sup>

| Item              | Symbol           | Test Condition                                                      | Min | Max | Unit |

|-------------------|------------------|---------------------------------------------------------------------|-----|-----|------|

| Input Capacitance | C <sub>IN</sub>  | V <sub>IN</sub> = 0V, f = 1 MHz, T <sub>A</sub> = 25 <sup>o</sup> C |     | 8   | pF   |

| I/O Capacitance   | C <sub>I/O</sub> | V <sub>IN</sub> = 0V, f = 1 MHz, T <sub>A</sub> = 25 <sup>o</sup> C |     | 8   | pF   |

1. These parameters are verified in device characterization and are not 100% tested

Stock No. 23208-01 11/01/02

#### Absolute Maximum Ratings<sup>1</sup>

| Item                                            | Symbol              | Rating                       | Unit |

|-------------------------------------------------|---------------------|------------------------------|------|

| Voltage on any pin relative to $V_{SS}$         | V <sub>IN,OUT</sub> | –0.3 to V <sub>CC</sub> +0.3 | V    |

| Voltage on $V_{CC}$ Supply Relative to $V_{SS}$ | V <sub>CC</sub>     | –0.3 to 4.5                  | V    |

| Power Dissipation                               | PD                  | 500                          | mW   |

| Storage Temperature                             | T <sub>STG</sub>    | -40 to 125                   | °C   |

| Operating Temperature                           | T <sub>A</sub>      | -40 to +85                   | °C   |

| Soldering Temperature and Time                  | T <sub>SOLDER</sub> | 240°C, 10sec(Lead only)      | °C   |

1. Stresses greater than those listed above may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operating section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Operating Characteristics (Over Specified Temperature Range)**

| Item                                                                                                                                  | Symbol           | Test Conditions                                                                                                   | Min.                  | Typ <sup>1</sup> | Мах                   | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------|------------------|-----------------------|------|

| Core Supply Voltage                                                                                                                   | V <sub>CC</sub>  |                                                                                                                   | 1.4                   | 1.8              | 2.3                   | V    |

| I/O Supply Voltage                                                                                                                    | V <sub>CCQ</sub> | $V_{CCQ}$ > or = $V_{CC}$                                                                                         | 1.4                   | 1.8              | 3.6                   | V    |

| Data Retention Voltage                                                                                                                | V <sub>DR</sub>  | Chip Disabled <sup>3</sup>                                                                                        | 1.2                   |                  |                       | V    |

| Input High Voltage                                                                                                                    | V <sub>IH</sub>  |                                                                                                                   | V <sub>CCQ</sub> -0.6 |                  | V <sub>CCQ</sub> +0.3 | V    |

| Input Low Voltage                                                                                                                     | V <sub>IL</sub>  |                                                                                                                   | -0.3                  |                  | 0.6                   | V    |

| Output High Voltage                                                                                                                   | V <sub>OH</sub>  | I <sub>OH</sub> = 0.2mA                                                                                           | V <sub>CCQ</sub> -0.2 |                  |                       | V    |

| Output Low Voltage                                                                                                                    | V <sub>OL</sub>  | I <sub>OL</sub> = -0.2mA                                                                                          |                       |                  | 0.2                   | V    |

| Input Leakage Current                                                                                                                 | Ι <sub>LI</sub>  | $V_{IN}$ = 0 to $V_{CC}$                                                                                          |                       |                  | 0.1                   | μA   |

| Output Leakage Current                                                                                                                | I <sub>LO</sub>  | $\overline{OE} = V_{IH}$ or Chip Disabled                                                                         |                       |                  | 0.1                   | μA   |

| Read/Write Operating Supply Current<br>@ 1 μs Cycle Time <sup>2</sup>                                                                 | I <sub>CC1</sub> | $V_{CC}$ =2.3 V, $V_{IN}$ = $V_{IH}$ or $V_{IL}$<br>Chip Enabled, $I_{OUT}$ = 0                                   |                       | 1.5              | 2.5                   | mA   |

| Read/Write Operating Supply Current<br>@ 85 ns Cycle Time <sup>2</sup>                                                                | I <sub>CC2</sub> | $V_{CC}$ =2.3 V, $V_{IN}$ = $V_{IH}$ or $V_{IL}$<br>Chip Enabled, $I_{OUT}$ = 0                                   |                       | 10.0             | 13.0                  | mA   |

| Page Mode Operating Supply Current<br>@ 85 ns Cycle Time <sup>2</sup> (Refer to Power<br>Savings with Page Mode Operation<br>diagram) | I <sub>CC3</sub> | V <sub>CC</sub> =2.3 V, V <sub>IN</sub> =V <sub>IH</sub> or V <sub>IL</sub><br>Chip Enabled, I <sub>OUT</sub> = 0 |                       | 3.5              |                       | mA   |

| Read/Write Quiescent Operating Sup-<br>ply Current <sup>3</sup>                                                                       | I <sub>CC4</sub> | $V_{CC}$ =2.3 V, $V_{IN}$ = $V_{IH}$ or $V_{IL}$<br>Chip Enabled, $I_{OUT}$ = 0,<br>f = 0                         |                       | 0.2              |                       | μA   |

| Standby Current <sup>3</sup>                                                                                                          | I <sub>SB1</sub> | $V_{IN} = V_{CC} \text{ or } 0V$<br>Chip Disabled<br>$t_A = 85^{\circ}C, V_{CC} = 2.3 V$                          |                       | 0.2              | 20.0                  | μA   |

| Data Retention Current <sup>3</sup>                                                                                                   | I <sub>DR</sub>  | $V_{CC}$ = 1.8V, $V_{IN}$ = $V_{CC}$ or 0<br>Chip Disabled, $t_A$ = 85°C                                          |                       | 0.1              | 1.0                   | μA   |

1. Typical values are measured at Vcc=Vcc Typ.,  $T_A$ =25°C and not 100% tested.

2. This parameter is specified with the outputs disabled to avoid external loading effects. The user must add current required to drive output capacitance expected in the actual system.

3. This device assumes a standby mode if the chip is disabled ( $\overline{CE1}$  high or CE2 low). In order to achieve low standby current all inputs must be within 0.2 volts of either VCC or VSS.

#### Stock No. 23208-01 11/01/02

| ower Sa | vings with Page N               | lode Operation (WE = V <sub>IH</sub> ) |         |

|---------|---------------------------------|----------------------------------------|---------|

| Page Ad | ddre <mark>ss (A4 - A17)</mark> | Open page                              | X       |

| Word Ad | ddress (A0 - A3)                | Word 1 Word 2                          | Word 16 |

| CE1     |                                 |                                        |         |

| CE2     |                                 |                                        |         |

| ŌĒ      |                                 |                                        |         |

|         |                                 |                                        |         |

Note: Page mode operation is a method of addressing the SRAM to save operating current. The internal organization of the SRAM is optimized to allow this unique operating mode to be used as a valuable power saving feature.

The only thing that needs to be done is to address the SRAM in a manner that the internal page is left open and 8-bit words of data are read from the open page. By treating addresses A0-A3 as the least significant bits and addressing the 16 words within the open page, power is reduced to the page mode value which is considerably lower than standard operating currents for low power SRAMs.

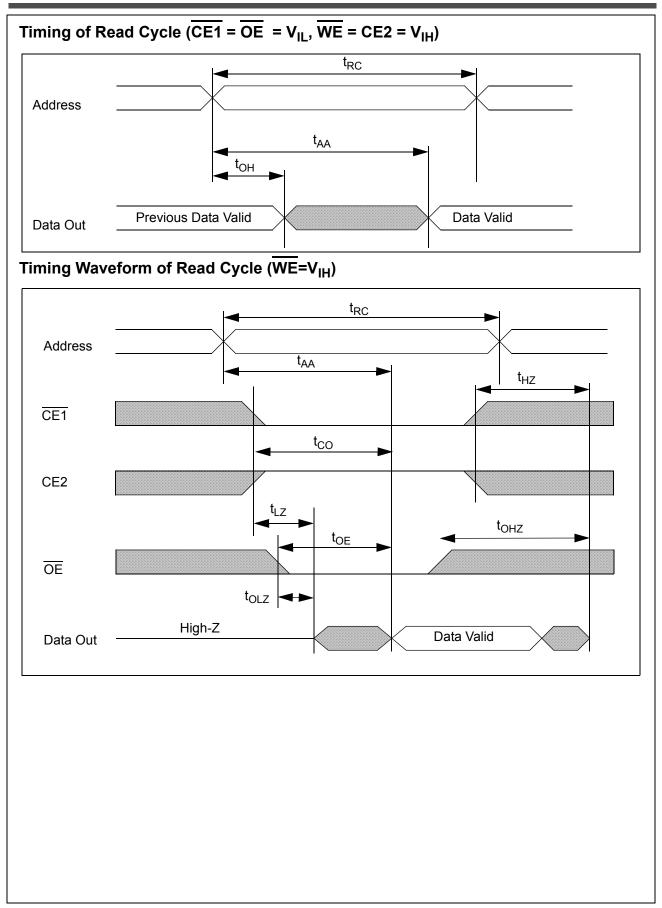

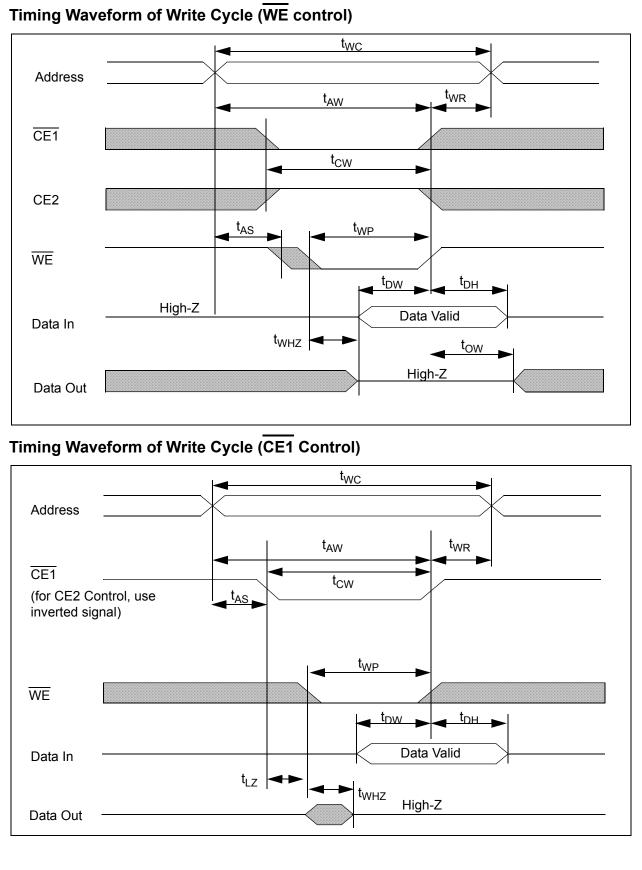

# Timing Test Conditions

| Item                                     |                                           |

|------------------------------------------|-------------------------------------------|

| Input Pulse Level                        | 0.1V <sub>CC</sub> to 0.9 V <sub>CC</sub> |

| Input Rise and Fall Time                 | 5ns                                       |

| Input and Output Timing Reference Levels | 0.5 V <sub>CC</sub>                       |

| Output Load                              | CL = 30pF                                 |

| Operating Temperature                    | -40 to +85 <sup>o</sup> C                 |

#### Timing $V_{CCQ} > or = V_{CC}$

| Item                            | Symbol           | V <sub>CC</sub> = 1 | .4 - 2.3 V | V <sub>CC</sub> = 1 | .7 - 2.3 V | Units |

|---------------------------------|------------------|---------------------|------------|---------------------|------------|-------|

| item                            | Symbol           | Min.                | Max.       | Min.                | Max.       | Units |

| Read Cycle Time                 | t <sub>RC</sub>  | 150                 |            | 85                  |            | ns    |

| Address Access Time             | t <sub>AA</sub>  |                     | 150        |                     | 85         | ns    |

| Chip Enable to Valid Output     | t <sub>CO</sub>  |                     | 150        |                     | 85         | ns    |

| Output Enable to Valid Output   | t <sub>OE</sub>  |                     | 50         |                     | 40         | ns    |

| Chip Enable to Low-Z output     | t <sub>LZ</sub>  | 20                  |            | 10                  |            | ns    |

| Output Enable to Low-Z Output   | t <sub>OLZ</sub> | 20                  |            | 5                   |            | ns    |

| Chip Disable to High-Z Output   | t <sub>HZ</sub>  | 0                   | 30         | 0                   | 15         | ns    |

| Output Disable to High-Z Output | t <sub>OHZ</sub> | 0                   | 30         | 0                   | 15         | ns    |

| Output Hold from Address Change | t <sub>OH</sub>  | 20                  |            | 10                  |            | ns    |

| Write Cycle Time                | t <sub>WC</sub>  | 150                 |            | 85                  |            | ns    |

| Chip Enable to End of Write     | t <sub>CW</sub>  | 75                  |            | 50                  |            | ns    |

| Address Valid to End of Write   | t <sub>AW</sub>  | 75                  |            | 50                  |            | ns    |

| Write Pulse Width               | t <sub>WP</sub>  | 50                  |            | 40                  |            | ns    |

| Address Setup Time              | t <sub>AS</sub>  | 0                   |            | 0                   |            | ns    |

| Write Recovery Time             | t <sub>WR</sub>  | 0                   |            | 0                   |            | ns    |

| Write to High-Z Output          | t <sub>wHZ</sub> |                     | 30         |                     | 15         | ns    |

| Data to Write Time Overlap      | t <sub>DW</sub>  | 50                  |            | 40                  |            | ns    |

| Data Hold from Write Time       | t <sub>DH</sub>  | 0                   |            | 0                   |            | ns    |

| End Write to Low-Z Output       | t <sub>OW</sub>  | 10                  |            | 5                   |            | ns    |

Stock No. 23208-01 11/01/02

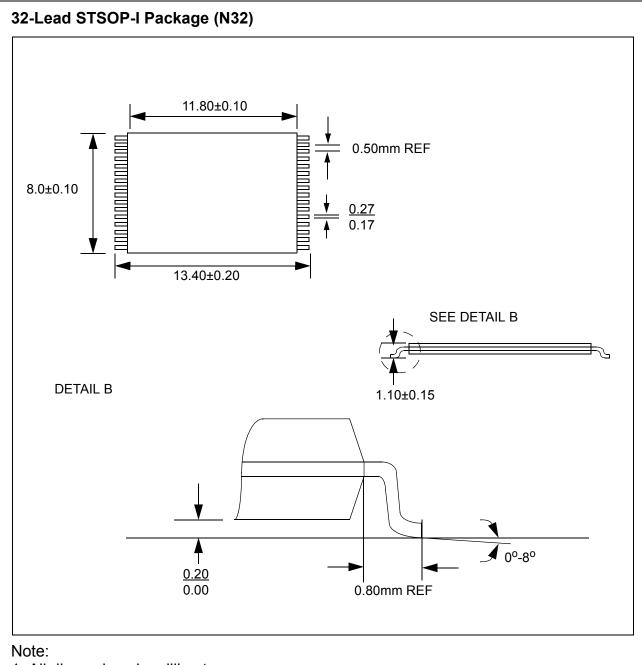

- 1. All dimensions in millimeters

- 2. Package dimensions exclude molding flash

#### **Revision History**

| Revision # | Date     | Change Description |

|------------|----------|--------------------|

| 01         | 11/01/02 | Initial Release    |

|            |          |                    |

|            |          |                    |

© 2001 - 2002 Nanoamp Solutions, Inc. All rights reserved.

NanoAmp Solutions, Inc. ("NanoAmp") reserves the right to change or modify the information contained in this data sheet and the products described therein, without prior notice. NanoAmp does not convey any license under its patent rights nor the rights of others. Charts, drawings and schedules contained in this data sheet are provided for illustration purposes only and they vary depending upon specific applications.

NanoAmp makes no warranty or guarantee regarding suitability of these products for any particular purpose, nor does NanoAmp assume any liability arising out of the application or use of any product or circuit described herein. NanoAmp does not authorize use of its products as critical components in any application in which the failure of the NanoAmp product may be expected to result in significant injury or death, including life support systems and critical medical instruments.