# Programmable Multi-Phase Synchronous Buck Converter with PMBus

### **Preliminary Technical Data**

#### **ERY FEATURES**

- Selectable 1-, 2-, 3-, 4-, 5-, 6, 7 or 8- phase operation at up to 1 MHz per phase

- PMBus Interface enables digital programmability of set points and readback of monitored values

- Logic-level PWM outputs for interface to external high power drivers

- Fast-Enhanced PWM flex mode for excellent load transient performance

Active current balancing between all output phases

- Built-in power-good/crowbar blanking supports on-the-fly VID code changes

- Digitally programmable 0.375 V to 1.6 V output supports both VR11 and VR11.1 specifications

Programmable Offset up to ±200mV Programmable short-circuit protection with programmable

latch-off delay Supports PSI# – Power saving mode during light loads

Over – Clocking Control

#### APPLICATIONS

- CPU Power controllers for Servers, Workstations and high end Desktops.

- Next generation Intel® VRM modules POL Applications such as Memory

#### **GENERAL DESCRIPTION**

The ASP0800<sup>1</sup> is an integrated power control IC with a PMBus interface. The ASP0800 is a highly efficient, multiphase, synchronous buck switching regulator controller, which aids design of High Efficiency and High Density solutions. The PMBus interface enables digital programming of key system parameters to optimize system performance and provide feedback to the system. The ASP0800 is compatible for use with coupled inductors,

The ASP0800 is optimized for converting a 12 V main supply into the core supply voltage required by high performance Intel processors. It uses an internal 8-bit DAC to read the voltage identification (VID) code directly from the processor, which is used to set the output voltage between 0.375 V and 1.6 V.

This device uses a multimode PWM architecture to drive the logic-level outputs at a programmable switching frequency that can be optimized for VR size and efficiency. The ASP0800 can be programmed for 1-, 2-, 3-, 4-, 5-, 6, 7 or 8- phase operation, allowing for the construction of up to 8 complementary buck

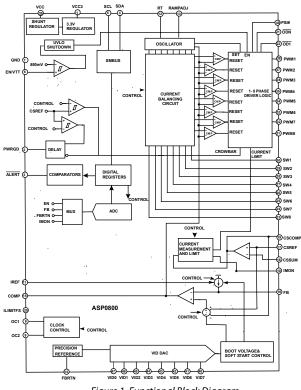

#### FUNCTIONAL BLOCK DIAGRAM

**ASP0800**

Figure 1. Functional Block Diagram

#### phases at light loads.

The ASP0800 includes a PMBus interface, which can be used to program system set points such as voltage offset, load line, phase balance and output voltage. Key system performance data such as CPU current, CPU voltage, and power and fault conditions can also be read back over the PMBus from the ASP0800.

The ASP0800 OC Feature allows programming different offset voltages depending on the load current being supplied. 3 OC Thresholds and 4 OC Offsets value registers are supported.

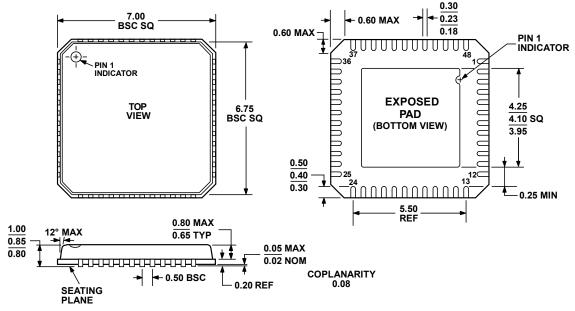

The ASP0800 has a built in shunt regulator that allows the part to be powered from the +12V system supply through a series resistor. The ASP0800 is specified over the extended commercial temperature range of 0°C to +85°C and is available in a 48 Lead LFCSP package.

<sup>1</sup> Protected by U.S. Patent Number 6,683,441; other patents pending.

©2008 SCILLC. All rights reserved. March 2008 - Rev. P1

### TABLE OF CONTENTS

|   | Output Current Sensing                                 | . 12 |

|---|--------------------------------------------------------|------|

|   | Output current monitor                                 | . 12 |

|   | Dynamic VID                                            | . 13 |

|   | INTERNAL Delay Timer                                   | . 14 |

|   | Soft Start                                             | . 14 |

|   | Current-Limit, Short-Circuit, and Latch-Off Protection | . 16 |

|   | Power-Good Monitoring                                  | . 17 |

|   | POWER STATE INDICATOR                                  | . 17 |

|   | Output Crowbar                                         | . 18 |

|   | Output Enable and UVLO                                 | . 18 |

|   | OVERCLOCKING (OC) LIMITS AND OFFSETS                   | . 18 |

|   | PMBUS Interface                                        | . 18 |

|   | Write Operations                                       | . 21 |

|   | Read Operations                                        | . 22 |

|   | PMBus Timeout                                          | . 23 |

| 0 | outline Dimensions                                     | . 38 |

|   |                                                        |      |

#### **REVISION HISTORY**

03/08—Rev P1: Conversion to ON Semiconductor

### **SPECIFICATIONS**

VCC = 5 V, FBRTN = GND,  $T_A = 0^{\circ}$ C to 85°C, unless otherwise noted.<sup>1</sup>

#### Table 1

| Parameter                                            | Symbol                   | Conditions                                                         | Min  | Тур  | Max  | Unit |

|------------------------------------------------------|--------------------------|--------------------------------------------------------------------|------|------|------|------|

| REFERENCE CURRENT                                    |                          |                                                                    |      |      |      |      |

| Reference Bias Voltage                               | VIREF                    |                                                                    | 1.75 | 1.8  | 1.85 | V    |

| Reference Bias Current                               | IIREF                    | $R_{IREF} = 121 \ k\Omega$                                         |      | 15   |      | uA   |

| ERROR AMPLIFIER                                      |                          |                                                                    |      |      |      |      |

| Output Voltage Range <sup>2</sup>                    | V <sub>COMP</sub>        |                                                                    | 0    |      | 4.4  | V    |

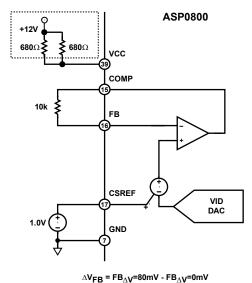

| Accuracy                                             | Vfb                      | Relative to nominal DAC output, referenced to FBRTN (see Figure 3) | -10  |      | +10  | mV   |

|                                                      | V <sub>FB(BOOT)</sub>    | In startup                                                         | 1.09 | 1.1  | 1.11 | V    |

| Load Line Positioning Accuracy                       |                          |                                                                    | -77  | -80  | -83  | mV   |

| Load Line Range                                      |                          |                                                                    | -350 |      | 0    | mV   |

| Load Line Attenuation                                |                          |                                                                    | 0    |      | 100  | %    |

| Differential Nonlinearity                            |                          |                                                                    | -1   |      | +1   | LSB  |

| Input Bias Current                                   | I <sub>FB</sub>          | IFB = IIREF                                                        | 13.5 | 15   | 16.5 | μΑ   |

| Offset Accuracy                                      |                          | VR Offset Register = TBD, VID = 1.0V                               |      | -200 |      | mV   |

|                                                      |                          | VR Offset Register = TBD , VID = 1.0V                              |      | 200  |      | mV   |

| FBRTN Current                                        | IFBRTN                   |                                                                    |      | 70   | 200  | μΑ   |

| Output Current                                       | Ісомр                    | FB forced to Vout – 3%                                             |      | 500  |      | μΑ   |

| Gain Bandwidth Product                               | GBW(ERR)                 | COMP = FB                                                          |      | 20   |      | MHz  |

| Slew Rate                                            |                          | COMP = FB                                                          |      | 25   |      | V/µs |

| BOOT Voltage Hold Time                               | <b>t</b> BOOT            | Internal Timer                                                     |      | 2    |      | ms   |

| VID INPUTS                                           |                          |                                                                    |      |      |      |      |

| Input Low Voltage                                    | V <sub>IL(VID)</sub>     | VID(X)                                                             |      |      | 0.3  | V    |

| Input High Voltage                                   | V <sub>IH(VID)</sub>     | VID(X)                                                             | 0.8  |      |      | V    |

| Input Current                                        | I <sub>IN(VID)</sub>     |                                                                    |      | -5   |      | μΑ   |

| VID Transition Delay Time <sup>2</sup>               |                          | VID code change to FB change                                       | 400  |      |      | ns   |

| No CPU Detection Turn-Off<br>Delay Time <sup>2</sup> |                          | VID code change to PWM going low                                   | 5    |      |      | μs   |

| OSCILLATOR                                           |                          |                                                                    |      |      |      |      |

| Frequency Range <sup>2</sup>                         | fosc                     |                                                                    | 0.25 |      | 9    | MHz  |

| Frequency Variation                                  | <b>f</b> PHASE           | $T_A = 25^{\circ}C, R_T = 500 \text{ k}\Omega, 4\text{-phase}$     | 170  | 195  | 225  | kHz  |

|                                                      |                          | $T_A = 25^{\circ}C, R_T = 250 k\Omega, 4$ -phase                   |      | 375  |      | kHz  |

|                                                      |                          | $T_A = 25^{\circ}C, R_T = 121 \text{ k}\Omega, 4\text{-phase}$     |      | 750  |      | kHz  |

| Output Voltage                                       | V <sub>RT</sub>          | $R_T = 500 \text{ k}\Omega \text{ to GND}$                         | 1.9  | 2.0  | 2.1  | v    |

| RAMPADJ Output Voltage                               | VRAMPADJ                 | $RAMPADJ - FB, V_{FB} = 1V,$                                       | -50  |      | +50  | mV   |

| RAMPADJ Input Current Range                          | IRAMPADJ                 |                                                                    | 5    |      | 125  | μΑ   |

| CURRENT SENSE AMPLIFIER                              |                          |                                                                    |      |      |      |      |

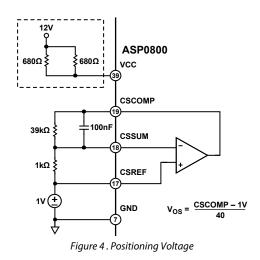

| Offset Voltage                                       | V <sub>OS(CSA)</sub>     | CSSUM – CSREF (see Figure 3)                                       | -1.0 |      | +1.0 | mV   |

| Input Bias Current, CSREF                            | I <sub>BIAS(CSREF)</sub> | CSREF = 1V                                                         | -20  |      | +20  | μA   |

| Input Bias Current, CSSUM                            | BIAS(CSSUM)              | CSREF = 1V                                                         | -10  |      | +10  | nA   |

| Gain Bandwidth Product                               | GBW <sub>(CSA)</sub>     | CSSUM = CSCOMP                                                     |      | 10   |      | MHz  |

| Slew Rate                                            |                          | C <sub>CSCOMP</sub> = 10 pF                                        |      | 10   |      | V/µs |

| Input Common-Mode Range                              |                          | CSSUM and CSREF                                                    | 0    |      | 3.0  | V    |

| Output Voltage Range                                 |                          |                                                                    | 0.05 |      | 3.0  | v    |

| Output Current                                       | I <sub>CSCOMP</sub>      |                                                                    |      | 500  |      | μA   |

| Current Limit Latch off Delay Time                   |                          | Internal Timer                                                     |      | 8    |      | ms   |

<sup>1</sup> All limits at temperature extremes are guaranteed via correlation using standard statistical quality control (SQC). <sup>2</sup> Guaranteed by design or bench characterization, not tested in production.

Preliminary Technical Data

| Parameter                          | Symbol                               | Conditions                            | Min  | Тур  | Max  | Unit |

|------------------------------------|--------------------------------------|---------------------------------------|------|------|------|------|

| PSI#                               |                                      |                                       |      |      |      |      |

| Input Low Voltage                  |                                      |                                       |      |      | 0.3  | v    |

| Input High Voltage                 |                                      |                                       | 0.8  |      |      | v    |

| Input Current                      |                                      |                                       |      | -5   |      | μA   |

| Assertion Timing                   |                                      | Fsw = 300kHz                          |      | 3.3  |      | μs   |

| Deassertion Timing                 |                                      | Fsw = 300kHz                          |      | 825  |      | ns   |

| IMON OUTPUT                        |                                      |                                       |      |      |      |      |

| Clamp Voltage                      |                                      |                                       | 1.0  |      | 1.15 | v    |

| Accuracy                           |                                      | 10 × (CSREF – CSCOMP)/RILIM           | -3   |      | 3    | %    |

| Output Current                     |                                      |                                       |      |      | 800  | μA   |

| Offset                             |                                      |                                       | -3   |      | 3    | mV   |

| CURRENT LIMIT COMPARITOR           |                                      |                                       |      |      |      |      |

| ILIM Bias Current                  | ILIM                                 | CSREF – CSCOMP)/RILIM , (CSREF –      |      | 20   |      | μA   |

|                                    | LIM                                  | CSCOMP)=150 mV, RILIMC=7.5 kΩ         |      | 20   |      | μ    |

| Current Limit Threshold Current    | I <sub>CL</sub>                      | $4/3 	imes I_{\text{iref}}$           |      | 20   |      | μΑ   |

| CURRENT BALANCE AMPLIFIER          |                                      |                                       |      |      |      |      |

| Common-Mode Range                  | V <sub>SW(X)CM</sub>                 |                                       | -600 |      | +200 | mV   |

| Input Resistance                   | R <sub>SW(X)</sub>                   | SW(X) = 0 V                           | 14   | 19   | 25   | kΩ   |

| Input Current                      | I <sub>SW(X)</sub>                   | SW(X) = 0 V                           | 7    | 12   | 20   | μΑ   |

| Input Current Matching             | $\Delta I_{SW(X)}$                   | SW(X) = 0 V                           | -6   |      | +6   | %    |

| Phase Balance Adjustment Range Low |                                      | Phase Bal Registers = 00000           |      | -25  |      | %    |

| Phase Balance Adjustment Range     |                                      | Phase Bal Registers = 11111           |      | +25  |      | %    |

| High                               |                                      |                                       |      |      |      |      |

| DELAY TIMER                        |                                      |                                       |      |      |      |      |

| Internal Timer                     |                                      | Delay Time Register = 011             |      | 2    |      | ms   |

| Timer Range Low                    |                                      | Delay Time Register = 000             |      | 0.5  |      | ms   |

| Timer Range High                   |                                      | Delay Time Register = 111             |      | 4    |      | ms   |

| SOFT START                         |                                      |                                       |      |      |      |      |

| Internal Timer                     |                                      | Soft Start Slope Register = 010       |      | 0.5  |      | V/ms |

| Timer Range Low                    |                                      | Soft Start Slope Register = 000       |      | 0.1  |      | V/ms |

| Timer Range High                   |                                      | Soft Start Slope Register = 111       |      | 1.5  |      | V/ms |

| ENABLE INPUT                       |                                      |                                       |      |      |      | .,   |

| Input Low Voltage                  | VIL(EN)                              |                                       |      |      | 0.3  | v    |

| Input High Voltage                 | V <sub>IH(EN)</sub>                  |                                       | 0.8  |      | 0.0  | v    |

| Input Current                      |                                      |                                       | 010  | -1   |      | μA   |

| Delay Time                         | t <sub>DELAY(EN)</sub>               | EN > 0.8V , Internal Delay            |      | 2    |      | ms   |

| ODN / OD1 OUTPUTS                  | CDELAT(EIN)                          |                                       |      | -    |      | 1115 |

| Output Low Voltage                 |                                      | 1 - 400 4                             |      | 160  | 500  | mV   |

| · -                                | Vol(ODN/1,)                          | $I_{OD(SINK)} = -400 \ \mu A$         | _    |      | 500  |      |

| Output High Voltage                | V <sub>OH</sub> ( <sub>ODN/1</sub> ) | $I_{OD(SOURCE)} = 400 \ \mu A$        | 4    | 5    |      | V    |

| ODN / OD1 Pull-Down Resistor       |                                      |                                       |      | 60   |      | kΩ   |

| OVER-CLOCKING OUTPUTS (OC1, OC2)   |                                      |                                       |      |      |      |      |

| Output Low Voltage                 | V <sub>OL</sub>                      | $I_{OC(SINK)} = -1 \text{ mA}$        |      | 160  | 500  | mV   |

| POWER GOOD COMPARATOR              |                                      |                                       |      |      |      |      |

| Undervoltage Threshold             | V <sub>PWRGD(UV)</sub>               | Relative to nominal DAC output        | -600 | -500 | -400 | mV   |

| Undervoltage Adjustment Range Low  |                                      | PWRGD_LO Register = 000               |      | -500 |      | mV   |

| Undervoltage Adjustment Range      |                                      | PWRGD_LO Register = 111               |      | -150 |      | mV   |

| High                               |                                      |                                       |      |      |      |      |

| Overvoltage Threshold              | V <sub>PWRGD(OV)</sub>               | Relative to DAC output, PWRGD_Hi = 00 | 200  | 300  | 400  | mV   |

| Overvoltage Adjustment Range Low   |                                      | PWRGD_Hi Register = 11                |      | 150  |      | mV   |

| Overvoltage Adjustment Range High  |                                      | PWRGD_Hi Register = 00                |      | 300  |      | mV   |

| Output Low Voltage                 | VOL(PWRGD)                           | $I_{PWRGD(SINK)} = -4 \text{ mA}$     |      | 150  | 300  | mV   |

| Power Good Delay Time              |                                      |                                       | 1    |      |      | 1    |

Rev. P1 | Page 4 of 36 | www.onsemi.com

ASP0800

| Parameter                          | Symbol               | Conditions                                                                | Min  | Тур | Max  | Unit |

|------------------------------------|----------------------|---------------------------------------------------------------------------|------|-----|------|------|

| During Soft Start <sup>2</sup>     |                      | Internal Timer                                                            |      | 2   |      | ms   |

| VID Code Changing                  |                      |                                                                           | 100  | 250 |      | μs   |

| VID Code Static                    |                      |                                                                           |      | 200 |      | ns   |

| Crowbar Trip Point                 | VCROWBAR             | Relative to DAC output, PWRGD_Hi = 00                                     | 200  | 300 | 400  | mV   |

| Overvoltage Adjustment Range Low   |                      | PWRGD_Hi Register = 11                                                    |      | 150 |      | mV   |

| Overvoltage Adjustment Range High  |                      | PWRGD_Hi Register = 00                                                    |      | 300 |      | mV   |

| Crowbar Reset Point                |                      | Relative to FBRTN                                                         | 250  | 300 | 350  | mV   |

| Crowbar Delay Time                 | <b>t</b> crowbar     | Overvoltage to PWM going low                                              |      |     |      |      |

| VID Code Changing                  |                      |                                                                           | 100  | 250 |      | μs   |

| VID Code Static                    |                      |                                                                           |      | 400 |      | ns   |

| PWM OUTPUTS                        |                      |                                                                           |      |     |      |      |

| Output Low Voltage                 | VOL(PWM)             | $I_{PWM(SINK)} = -400 \ \mu A$                                            |      | 160 | 500  | mV   |

| Output High Voltage                | V <sub>OH(PWM)</sub> | $I_{PWM(SOURCE)} = 400 \ \mu A$                                           | 4    | 5   |      | v    |

| PMBus Interface                    |                      |                                                                           |      |     |      |      |

| Logic High Input Voltage           | VIH(SDA, SCL)        |                                                                           | 2.1  |     |      | v    |

| Logic Input Low Voltage            | VIL(SDA, SCL)        |                                                                           |      |     | 0.8  | V    |

| Hysteresis                         |                      |                                                                           |      | 500 |      | mV   |

| SDA Output Low Voltage             | V <sub>OL</sub>      | $I_{SDA} = -6mA$                                                          |      |     | 0.4  | V    |

| Input Current                      | lıн ; lı∟            |                                                                           | -1   |     | 1    | μΑ   |

| Input Capacitance C <sub>sct</sub> |                      |                                                                           |      | 5   |      | рF   |

| Clock Frequency                    | f <sub>scl</sub>     |                                                                           |      |     | 400  | kHz  |

| SCL Falling Edge to SDA Valid Time |                      |                                                                           |      |     | 1    | μs   |

| ALERT FAULT OUTPUTS                |                      |                                                                           |      |     |      |      |

| Output Low Voltage                 | V <sub>OL</sub>      | I <sub>OUT</sub> = -6mA                                                   |      |     | 0.4  | v    |

| Output High Leakage Current        | Іон                  | $V_{OH} = 5V$                                                             |      |     | 1    | uA   |

| ANALOG/DIGITAL CONVERTER           |                      |                                                                           |      |     |      |      |

| Total Unadjusted Error (TUE)       |                      |                                                                           |      | ±2  |      | %    |

| Differential Non linearity (DNL)   |                      | TBD Bits                                                                  |      | 1   |      | LSB  |

| Conversion Time                    |                      | Averaging Enabled (32 averages)                                           |      | 80  |      | ms   |

| SUPPLY                             |                      | $V_{\text{SYSTEM}} = 12 \text{ V}, \text{ R}_{\text{SHUNT}} = 340 \Omega$ |      |     |      |      |

| VCC <sup>2</sup> VCC               |                      |                                                                           | 4.70 | 5   | 5.45 | V    |

| DC Supply Current Ivcc             |                      | $V_{SYSTEM} = 13.2 \text{ V}, \text{ R}_{SHUNT} = 340 \Omega$             |      | 21  | 26   | mA   |

| UVLO Turn-On Current               |                      |                                                                           |      | 6.5 | 11   | mA   |

| UVLO Threshold Voltage             | VUVLO                | VCC rising                                                                | 9    |     |      | V    |

| UVLO Turn-Off Voltage              |                      | VCC falling                                                               |      | 4.1 |      | V    |

| VCC3 Output Voltage                | VCC3                 | $I_{VCC3} = 1 m A$                                                        | 3.0  | 3.3 | 3.6  | v    |

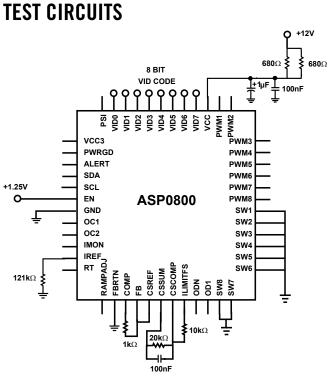

Figure 2. Closed-Loop Output Voltage Accuracy

Figure 3 . Current Sense Amplifier Vos

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 2.

| Parameter                           | Rating                |

|-------------------------------------|-----------------------|

| VCC                                 | -0.3 V to +6 V        |

| FBRTN                               | –0.3 V to +0.3 V      |

| PWM2 to PWM8, RAMPADJ               | –0.3 V to VCC + 0.3 V |

| SW1 to SW8                          | –5 V to +25 V         |

| <200 ns                             | –10 V to +25 V        |

| All Other Inputs and Outputs        | –0.3 V to VCC + 0.3 V |

| Storage Temperature Range           | –65°C to +150°C       |

| Operating Ambient Temperature Range | 0°C to 85°C           |

| Operating Junction Temperature      | 125°C                 |

| Lead Temperature                    |                       |

| Soldering (10 sec)                  | 300°C                 |

| Infrared (15 sec)                   | 260°C                 |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

#### Table 3. Thermal Resistance

| Package Type                        | θ <sub>JA</sub> | οισ | Unit |

|-------------------------------------|-----------------|-----|------|

| Thermal Impedance ( $\theta_{JA}$ ) | 27°C/W          |     |      |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

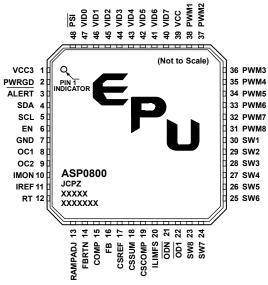

### **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 5. Pin Configuration

#### **Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                                 |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VCC3     | 3.3V Power Supply Output. A capacitor from this pin to ground provided decoupling for the interval 3.3V LDO.                                                                                                                                |

| 2       | PWRGD    | Power-Good Output: Open-drain output that signals when the output voltage is outside of the proper operating range.                                                                                                                         |

| 3       | ALERT    | ALERT Output : Open drain output that asserts low when the VR exceeds a programmable limit. Can be configured for Comparator Mode or Interrupt Mode.                                                                                        |

| 4       | SDA      | Digital Input / Output. PMBus serial data bidirectional pin. Requires PMBus pull up.                                                                                                                                                        |

| 5       | SCL      | Digital Input. PMBus serial bus clock open drain input. Requires PMBus pull up.                                                                                                                                                             |

| 6       | EN       | Power Supply Enable Input. Pulling this pin to GND disables the PWM outputs and pulls the PWRGD output low.                                                                                                                                 |

| 7       | GND      | Ground. All internal biasing and the logic output signals of the device are referenced to this ground                                                                                                                                       |

| 8       | OC1      | Over Clocking Bit 1 Output. The pin is connected to the clock control chip to set the over-clocking state.                                                                                                                                  |

| 9       | OC2      | Over Clocking Bit 2 Output. The pin is connected to the clock control chip to set the over-clocking state.                                                                                                                                  |

| 10      | IMON     | Total Current Output Pin.                                                                                                                                                                                                                   |

| 11      | IREF     | Current Reference Input. An external resistor from this pin to ground sets the reference current for IFB, and IILIMFS.                                                                                                                      |

| 12      | RT       | Frequency Setting Resistor Input. An external resistor connected between this pin and GND sets the oscillator frequency of the device.                                                                                                      |

| 13      | RAMPADJ  | PWM Ramp Current Input. An external resistor from the converter input voltage to this pin sets the internal PWM ramp.                                                                                                                       |

| 14      | FBRTN    | Feedback Return. VID DAC and error amplifier reference for remote sensing of the output voltage.                                                                                                                                            |

| 15      | COMP     | Error Amplifier Output and Compensation Point.                                                                                                                                                                                              |

| 16      | FB       | Feedback Input. Error amplifier input for remote sensing of the output voltage. An external resistor between this pin and the output voltage sets the no load offset point.                                                                 |

| 17      | CSREF    | Current Sense Reference Voltage Input. The voltage on this pin is used as the reference for the current sense amplifier and the power-good and crowbar functions. This pin should be connected to the common point of the output inductors. |

| 18      | CSSUM    | Current Sense Summing Node. External resistors from each switch node to this pin sum the average inductor currents together to measure the total output current.                                                                            |

| 19      | CSCOMP   | Current Sense Compensation Point. A resistor and capacitor from this pin to CSSUM determines the gain of the current sense amplifier and the positioning loop response time.                                                                |

| 20      | ILIMFS   | Current Sense and Limit Scaling Pin. An external resistor from this pin to CSCOMP sets the internal current sensing signal for current-limit and IMON. This value can be over-written using the PMBus interface.                            |

| 21      | ODN      | Output Disable Logic Output for PSI# operation. This pin is actively pulled low when PSI# is low, otherwise it functions in the same way as OD1.                                                                                            |

| 22      | OD1      | Output Disable Logic Output. This pin is actively pulled low when the EN input is low or when VCC is below its UVLO threshold to signal to the Driver IC that the driver high-side and low-side outputs should go low.                      |

Rev. P1 | Page 8 of 36 | www.onsemi.com

| Pin No.     | Mnemonic        | Description                                                                                                                                                                                                                                                                                                   |

|-------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23 to<br>30 | SW8 to SW1      | Current Balance Inputs. Inputs for measuring the current level in each phase. The SW pins of unused phases should be left open.                                                                                                                                                                               |

| 31 to<br>38 | PWM8 to<br>PWM1 | Logic-Level PWM Outputs. Each output is connected to the input of an external MOSFET driver such as the ADP3121. Connecting the PWM8, PWM7, PWM6, PWM5, PWM4, PWM3 and PWM2 outputs to VCC causes that phase to turn off, allowing the ASP0800 to operate as a 1, 2-, 3-, 4-, 5-, 6, 7 or 8-phase controller. |

| 39          | VCC             | Supply Voltage for the Device. A 340 $\Omega$ resistor should be placed between the 12 V system supply and the VCC pin. The internal shunt regulator maintains VCC = 5 V.                                                                                                                                     |

| 40 to<br>47 | VID7 to VID0    | Voltage Identification DAC Inputs. These eight pins are pulled down to GND, providing a logic zero if left open. When in normal operation mode, the DAC output programs the FB regulation voltage from 0.375 V to 1.6                                                                                         |

| 48          | PSI             | Power State Indicator. Pulling this pin low places the controller in lower power state operation.                                                                                                                                                                                                             |

### **TYPICAL PERFORMANCE CHARACTERISTICS**

# TBD

### **THEORY OF OPERATION**

The ASP0800 combines a multi-mode, fixed frequency PWM control with multi-phase logic outputs for use in multi-phase synchronous buck CPU core supply power converters. The internal VID DAC is designed to interface with the Intel 8-bit VR 11 and VR 11.1 compatible CPUs .

In addition, the ASP0800 incorporates a serial interface to allow the programming of key system performance specifications and read back CPU data such as voltage, current and power.

Multiphase operation is important for producing the high currents and low voltages demanded by today's microprocessors. Handling the high currents in a single-phase converter would place high thermal demands on the components in the system such as the inductors and MOSFETs.

The multimode control of the ASP0800 ensures a stable, high performance topology for:

- Balancing currents and thermals between phases for both static and dynamic operation.

- High speed response at the lowest possible switching frequency and output decoupling

- FEPWM improves load step response.

- Minimizing thermal switching losses by utilizing lower frequency operation

- High current output due to 8 phase operation

- Tight load line regulation and accuracy

- Reduced output ripple due to multiphase cancellation

- PC board layout noise immunity

- Ease of use and design due to independent component selection

- Flexibility in operation for tailoring design to low cost or high performance

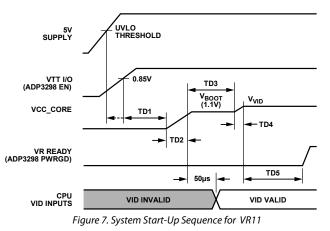

#### **START-UP SEQUENCE**

The ASP0800 follows the VR11 start-up sequence shown in Figure 7. After both the EN and UVLO conditions are met, a programmable internal timer goes through one cycle TD1. This delay cycle is programmed using Delay Command, default delay = 2ms). The first eight clock cycles of TD2 are blanked from the PWM outputs and used for phase detection as explained in the following section. Then the programmable internal soft-start ramp is enabled (TD2) and the output comes up to the boot voltage of 1.1V. The boot hold time is also set by the Delay Command. This second delay cycle is called TD3. During TD3 the processor VID pins settle to the required VID code. When TD3 is over, the ASP0800 reads the VID inputs and soft starts either up or down to the final VID voltage (TD4). After TD4 has been completed and the PWRGD masking time (equal to VID on the fly masking) is finished, a third cycle of the internal timer sets the PWRGD blanking (TD5).

The internal delay and soft start times are programmable using the serial interface and the Delay Command and Soft Start Command.

#### PHASE DETECTION SEQUENCE

During startup, the number of operational phases and their phase relationship is determined by the internal circuitry that monitors the PWM outputs. Normally, the ASP0800 operates as a 8-phase PWM controller.

To operate as a 7-phase controller connect PWM8 to VCC.

To operate as a 6-phase controller connect PWM7 and PWM8 to VCC.

To operate as a 5-phase controller connect PWM6, PWM7 and PWM8 to VCC.

To operate as a 4-phaase controller connect PWM5, PWM6, PWM7 and PWM8 to VCC.

To operate as a 3-phase controller connect PWM4, PWM5, PWM6, PWM7 and PWM8 to VCC.

To operate as a 2-phase controller connect PWM3, PWM4, PWM5, PWM6, PWM7 and PWM8 to VCC.

To operate as a 1-phase controller connect PWM2, PWM3, PWM4, PWM5, PWM6, PWM7 and PWM8 to VCC.

Prior to soft start, while EN is low, the PWM8, PWM7, PWM6, PWM5, PWM4, PWM3 and PWM2 pins sink approximately 100  $\mu$ A each. An internal comparator checks each pin's voltage vs. a threshold of 3 V. If the pin is tied to VCC, it is above the threshold. Otherwise, an internal current sink pulls the pin to GND, which is below the threshold. PWM1 is low during the phase detection interval that occurs during the first eight clock cycles of TD2. After this time, if the remaining PWM outputs are not pulled to VCC, the 100  $\mu$ A current sink is removed, and they function as normal PWM outputs. If they are pulled to

Rev. P1 | Page 11 of 36 | www.onsemi.com

VCC, the 100  $\mu A$  current source is removed, and the outputs are put into a high impedance state.

The PWM outputs are logic-level devices intended for driving fast response external gate drivers such as the ADP3121 and ADP3122. Because each phase is monitored independently, operation approaching 100% duty cycle is possible. In addition, more than one output can be on at the same time to allow overlapping phases.

#### MASTER CLOCK FREQUENCY

The clock frequency of the ASP0800 is set with an external resistor connected from the RT pin to ground. The frequency follows the graph in Figure 6. To determine the frequency per phase, the clock is divided by the number of phases in use. If all phases are in use, divide by 6. If 4 phases are in use divide by 4.

#### **OUTPUT VOLTAGE DIFFERENTIAL SENSING**

The ASP0800 combines differential sensing with a high accuracy VID DAC and reference, and a low offset error amplifier. This maintains a worst-case specification of  $\pm 10 \text{ mV}$  differential sensing error over its full operating output voltage and temperature range. The output voltage is sensed between the FB pin and FBRTN pin. FB is connected through a resistor, R<sub>B</sub> to the regulation point, usually the remote sense pin of the microprocessor. FBRTN is connected directly to the remote sense ground point. The internal VID DAC and precision reference are referenced to FBRTN, which has a minimal current of 70  $\mu$ A to allow accurate remote sensing. The internal error amplifier compares the output of the DAC to the FB pin to regulate the output voltage.

#### **OUTPUT CURRENT SENSING**

The ASP0800 provides a dedicated current-sense amplifier (CSA) to monitor the total output current for proper voltage positioning vs. load current, for the IMON output and for current-limit detection. Sensing the load current at the output gives the total real time current being delivered to the load, which is an inherently more accurate method than peak current detection or sampling the current across a sense element such as the low-side MOSFET. This amplifier can be configured several ways, depending on the objectives of the system, as follows:

- Output inductor DCR sensing without a thermistor for lowest cost.

- Output inductor DCR sensing with a thermistor for improved accuracy with tracking of inductor temperature.

- Sense resistors for highest accuracy measurements.

The positive input of the CSA is connected to the CSREF pin, which is connected to the average output voltage. The inputs to the amplifier are summed together through resistors from the sensing element, such as the switch node side of the output inductors, to the inverting input CSSUM. The feedback resistor between CSCOMP and CSSUM sets the gain of the amplifier and a filter capacitor is placed in parallel with this resistor. The gain of the amplifier is programmable by adjusting the feedback resistor. This difference signal is used internally to offset the VID DAC for voltage positioning. This different signal can be adjusted between 50%-150% of the external value using the PMBus Loadline Calibration (0xDE) and Loadline Set (0xDF) commands.

The difference between CSREF and CSCOMP is then used as a differential input for the current-limit comparator.

To provide the best accuracy for sensing current, the CSA is designed to have a low offset input voltage. Also, the sensing gain is determined by external resistors to make it extremely accurate.

The CPU current can also be monitored over the PMBus. The current limit and the load line can be programmed over PMBus.

#### **OUTPUT CURRENT MONITOR**

IMON is an analog output from the ASP0800 representing the total current being delivered to the load. It outputs an accurate current that is directly proportional to the current set by the ILIMFS resistor. The current is then run through a parallel RC connected from the IMON pin to the FBRTN pin to generate an accurately scaled and filtered voltage as per the VR11.1 specification. The size of the resistor is used to set the IMON scaling.

If the IMON and the OCP need to be changed based on the TDC of the CPU, then the ILIMFS resistor is the only component that needs to be changed. If the IMON scaling is the only change needed then changing the IMON resistor accomplishes this.

The IMON pin also includes an active clamp to limit the IMON voltage to 1.15V MAX while maintaining 900mV MIN full scale accurate reporting.

#### ACTIVE IMPEDANCE CONTROL MODE

For controlling the dynamic output voltage droop as a function of output current, the CSA gain and load line programming can be scaled to be equal to the droop impedance of the regulator times the output current. This droop voltage is then used to set the input control voltage to the system. The droop voltage is subtracted from the DAC reference input voltage directly to tell the error amplifier where the output voltage should be. This allows enhanced feed-forward response.

# CURRENT CONTROL MODE AND THERMAL BALANCE

The ASP0800 has individual inputs (SW1 to SW8) for each phase that are used for monitoring the current of each phase. This information is combined with an internal ramp to create a current balancing feedback system that has been optimized for initial current balance accuracy and dynamic thermal balancing during operation. This current balance information is independent of the average output current information used for positioning as described in the Output Current Sensing section.

The magnitude of the internal ramp can be set to optimize the transient response of the system. It also monitors the supply voltage for feed-forward control for changes in the supply. A resistor connected from the power input voltage to the RAMPADJ pin determines the slope of the internal PWM ramp.

The balance between the phases can be programmed using the PMBus Phase Bal SW(x) commands (TBD to TBD). This allows each phase to be adjusted if there is a difference in temperature due to layout and airflow considerations. The phase balance can be adjusted from a default gain of 5 (Bits 4:0 = 10000). The minimum gain programmable is 3.75 (Bits 4:0 = 00000) and the max gain is 6.25 (Bits 4:0 = 11111).

#### **VOLTAGE CONTROL MODE**

A high gain, high bandwidth, voltage mode error amplifier is used for the voltage mode control loop. The control input voltage to the positive input is set via the VID logic according to the voltages listed in Table 5. The VID code is set using the VID Input pins or it can be programmed over the PMBus using the VOUT\_Command. By default, the ASP0800 outputs a voltage corresponding to the VID Inputs. To output a voltage following the VOUT\_Command the user first needs to program the required VID Code. Then the VID\_EN Bits need to be enabled. The following is the sequence

Program the required VID Code to the VOUT\_Command code (0x21)

Set the VID\_EN bit (Bit 3) in the VR Config 1A (0xD2) and on the VR Config 1B (0xD3).

This voltage is also offset by the droop voltage for active positioning of the output voltage as a function of current, commonly known as active voltage positioning. The output of the amplifier is the COMP pin, which sets the termination voltage for the internal PWM ramps.

The negative input (FB) is tied to the output sense location with Resistor  $R_B$  and is used for sensing and controlling the output voltage at this point. A current source (equal to IREF) from the FB pin flowing through  $R_B$  is used for setting the no load offset voltage from the VID voltage. The no load voltage is negative with respect to the VID DAC for Intel CPU's. The main loop compensation is incorporated into the feedback network between FB and COMP.

An offset voltage can be added to the control voltage over the serial interface. This is done using Bits <5:0> of the VOUT\_TRIM (0xDB) and VOUT\_CAL (0xDC) Commands. The max offset that can be applied is +/-200mV (even if the sum of the offsets > 200mV). The LSB size id 6.25mV. A positive offset is applied when Bit 4 = 0. A negative offset is applied when Bit 4 = 1.

#### Table 5. Offset Codes

| VOUT_TRI<br>M CODE | TRIM<br>OFFSET<br>VOLTAG<br>E | VOUT_CA<br>L CODE | CAL<br>OFFSET<br>VOLTAG<br>E | TOTAL<br>OFFSET<br>VOLTAG<br>E |

|--------------------|-------------------------------|-------------------|------------------------------|--------------------------------|

| TBD                | TBD                           | TBD               | TBD                          | TBD                            |

| TBD                | TBD                           | TBD               | TBD                          | TBD                            |

| TBD                | TBD                           | TBD               | TBD                          | TBD                            |

#### DYNAMIC VID

The ASP0800 has the ability to dynamically change the VID inputs while the controller is running. This allows the output voltage to change while the supply is running and supplying current to the load. This is commonly referred to as Dynamic VID (DVID). A DVID can occur under either light or heavy load conditions. The processor signals the controller by changing the VID inputs (or by programming a new VOUT\_Command) in a single or multiple steps from the start code to the finish code. This change can be positive or negative.

When a VID bit changes state, the ASP0800 detects the change and ignores the DAC inputs for a minimum of 200 ns. This time prevents a false code due to logic skew while the VID inputs are changing. Additionally, the first VID change initiates the PWRGD and CROWBAR blanking functions for a minimum of 100 µs to prevent a false PWRGD or CROWBAR event. Each VID change resets the internal timer.

If a VID off code is detected the ASP0800 will wait for 5usec to ensure that the code is correct before initiating a shutdown of the controller.

The ASP0800 also uses the TON\_Transition (0xD6) to limit the DVID slew rates. These can be encountered when the system does a large single VID step for power state changes, thus the DVID slew rate needs to be limited to prevent large inrush currents.

The transition slew rate is programmed using Bits <2:0> of the Ton\_Transition (0xD6) command code. Table 6 provides the transition rate values.

| Table 6. | Transition | Rate | Codes |

|----------|------------|------|-------|

|----------|------------|------|-------|

| Code | Transition Rate (V/msec) |

|------|--------------------------|

| 000  | 1                        |

| 001  | 3                        |

| 010  | 5 = default              |

| 011  | 7                        |

| 100  | 9                        |

| 101  | 11                       |

| 110  | 13                       |

| 111  | 15                       |

#### ENHANCED TRANSIENTS MODE

The ASP0800 incorporates enhanced transient response for both load step up and load release. For load step up it senses the output of the error amp to determine if a load step up has occurred and then sequences on the appropriate number of phases to ramp up the output current.

#### **CURRENT REFERENCE**

The IREF pin is used to set an internal current reference. This reference current sets  $I_{FB}$ . A resistor to ground programs the current based on the 1.8 V output.

$$IREF = \frac{1.8 \,\mathrm{V}}{R_{IREF}}$$

Typically,  $R_{IREF}$  is set to 121 k $\Omega$  to program  $IREF = 15 \mu A$ . The following currents are then equal to

$$I_{FB} = IREF = 15 \ \mu A$$

#### **INTERNAL DELAY TIMER**

The delay times for the start up timing sequence are set by an internal timer. The default time is 2msec which can be changed through the PMBus interface. This timer is used for multiple

delay timings (TD1, TD3, and TD5) during the start-up sequence. Also, it is used for timing the current limit latch off as explained in the CURRENT LIMIT section. The current limit timer is set to 4 times the delay timer.

The delay timer is programmed using Bits <2:0> of the Ton Delay command (0xD4). The delay can be programmed between 0.5msec and 4msec. Table 7 provides the programmable delay values

| 1 4010 / 1 2 014 / 00400 |              |  |  |  |  |

|--------------------------|--------------|--|--|--|--|

| Code                     | Delay (msec) |  |  |  |  |

| 000                      | 0.5          |  |  |  |  |

| 001                      | 1            |  |  |  |  |

| 010                      | 1.5          |  |  |  |  |

| 011                      | 2 = default  |  |  |  |  |

| 100                      | 2.5          |  |  |  |  |

| 101                      | 3            |  |  |  |  |

| 110                      | 3.5          |  |  |  |  |

| 111                      | 4            |  |  |  |  |

|                          |              |  |  |  |  |

#### SOFT START

The Soft Start slope for the output voltage is set by an internal timer. The default value is 0.5V/msec., which can be programmed through the PMBus interface. After TD1 and the phase detection cycle have been completed, the SS time (TD2 in Figure 7) starts. The SS circuit uses the internal VID DAC to increase the output voltage in 6.25mV steps up to the 1.1 V boot voltage.

Once the SS circuit has reached the boot voltage, the boot voltage delay time (TD3) is started. The end of the boot voltage delay time signals the beginning of the second soft start time (TD4). The SS voltage changes from the boot voltage to the programmed VID DAC voltage (either higher or lower) using 6.25mV steps.

The soft start slew rate is programmed using Bits <2:0> of the Ton\_Rise (0xD5) command code.

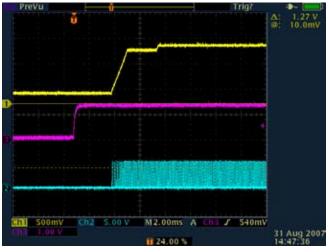

Table 8. Soft Start Codes provides the soft start values. Figure 8 shows typical start-up waveforms for the ASP0800.

#### Table 8. Soft Start Codes

| Code | Soft Start (V/msec) |

|------|---------------------|

| 000  | 0.3                 |

| 001  | 0.3                 |

| 010  | 0.5 = default       |

| 011  | 0.7                 |

| 100  | 0.9                 |

| 101  | 1.1                 |

| 110  | 1.3                 |

| 111  | 1.5                 |

Figure 8 shows typical start up waveforms for the ASP0800.

Figure 8. Typical Start up waveforms Channel 1: CSREF Channel 2: EN Channel 3: PWM1

#### CURRENT-LIMIT, SHORT-CIRCUIT, AND LATCH-OFF PROTECTION

The ASP0800 compares a programmable current limit set point to the voltage from the output of the current sense amplifier. The level of current limit is set with the resistor from the ILIMFS pin to CSCOMP, and can be adjusted using the PMBus interface.

The current limit threshold can be modified from the resistor programmed value by using the PMBus interface using Bits <4:0> of the Current Limit Threshold command (0xE2). The limit is programmable between 50% of the external limit and 146.7% of the external limit. The resolution is 3.3%.

Table 9 gives some examples codes

| Table 9. Current Lim | it |

|----------------------|----|

|----------------------|----|

| Code   | Current Limit (% of external limit) |

|--------|-------------------------------------|

| 0 0000 | 50%                                 |

| 0 0001 | 53.3%                               |

| 1 0000 | 100% = default                      |

| 1 0001 | 103.3%                              |

| 1 1110 | 143.3%                              |

| 1 1111 | 146.7%                              |

The current limit threshold can be modified from the resistor programmed value by using the serial interface.

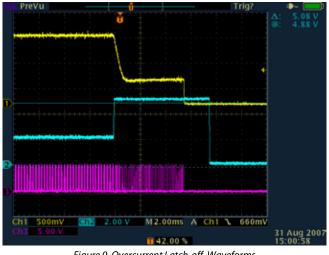

If the limit is reached and TD5 has completed, an internal latchoff delay time will start, and the controller will shut down if the fault is not removed. This delay is four times longer than the delay time during the start-up sequence. The current limit delay time only starts after the TD5 has completed. If there is a current limit during start-up, the ASP0800 will go through TD1 to TD5, and then start the latch-off time. Because the controller continues to cycle the phases during the latch-off delay time, if the short is removed before the timer is complete, the controller can return to normal operation.

The latch-off function can be reset by either removing and reapplying the supply voltage to the ASP0800, or by toggling the EN pin low for a short time.

The OCP latch-off function can be disabled by using the PMBus interface. Setting the CLIM\_EN bit (bit 1) of the VR Config 1A (0xD2) and VR Config 1B (0xD3) registers to 0 disables the current limit latch off function. The ASP0800 can continue to operate in current limit indefinitely.

During start-up when the output voltage is below 200 mV, a secondary current limit is active. This is necessary because the voltage swing of CSCOMP cannot go below ground. This secondary current limit limits controls the internal COMP voltage to the PWM comparators to 1.5 V. This limits the voltage drop across the low-side MOSFETs through the current balance circuitry. Typical over-current latch-off waveforms are shown in Figure 9.

Figure 9. Overcurrent Latch-off Waveforms Channel 1: CSREF, Channel 2: COMP, Channel 3: PWM1

An inherent per phase current limit protects individual phases if one or more phases stops functioning because of a faulty component. This limit is based on the maximum normal mode COMP voltage.

### **POWER-GOOD MONITORING**

The power good comparator monitors the output voltage via the CSREF pin. The PWRGD pin is an open-drain output whose high level (when connected to a pull-up resistor) indicates that the output voltage is within the nominal limits specified in the specifications above based on the VID voltage setting. PWRGD goes low if the output voltage is outside of this specified range, if the VID DAC inputs are in no CPU mode, or whenever the EN pin is pulled low. PWRGD is blanked during a DVID event for a period of 100  $\mu$ s to prevent false signals during the time the output is changing.

The PWRGD circuitry also incorporates an initial turn-on delay time (TD5). Prior to the SS voltage reaching the programmed VID DAC voltage and the PWRGD masking time finishing, the PWRGD pin is held low. Once the SS circuit reaches the programmed DAC voltage, the internal timer operates.

The value for the PWRGD high limit and low limit can be programmed using the serial interface.

#### POWER STATE INDICATOR

The PSI# pin is an input used to determine the operating state of the load. If this input is pulled low, the load is in a low power state and the controller asserts the  $\overrightarrow{ODN}$  pin low, which can be used to disable phases and maintain better efficiency at lighter loads.

The sequencing into and out of low power operation is maintained to minimize output deviations as well as providing full power load transients immediately after exiting a low power

#### **OUTPUT CROWBAR**

As part of the protection for the load and output components of the supply, the PWM outputs are driven low (turning on the low-side MOSFETs) when the output voltage exceeds the upper crowbar threshold. This crowbar action stops once the output voltage falls below the release threshold of approximately 300 mV.

The value for the crowbar limit follows the programmable PWRGD high limit.

Turning on the low-side MOSFETs pulls down the output as the reverse current builds up in the inductors. If the output overvoltage is due to a short in the high-side MOSFET, this action current-limits the input supply or blows its fuse, protecting the microprocessor from being destroyed.

#### **OUTPUT ENABLE AND UVLO**

For the ASP0800 to begin switching, the input supply current to the controller must be higher than the UVLO threshold and the EN pin must be higher than its 0.8 V threshold. This initiates a system start-up sequence. If either UVLO or EN is less than their respective thresholds, the ASP0800 is disabled. This holds the PWM outputs at ground and forces PWRGD,  $\overline{ODN}$  and  $\overline{OD1}$  signals low.

In the application circuit (see Figure TBD), the  $\overline{OD1}$  pin should be connected to the  $\overline{OD}$  inputs of the external drivers for the phases that are always on. The  $\overline{ODN}$  pin should be connected to the  $\overline{OD}$  inputs of the external drivers on the phases that are shut down during low power operation. Grounding the driver  $\overline{OD}$ inputs disables the drivers such that both DRVH and DRVL are grounded. This feature is important in preventing the discharge of the output capacitors when the controller is shut off. If the driver outputs are not disabled, a negative voltage can be generated during output due to the high current discharge of the output capacitors through the inductors.

### **OVERCLOCKING (OC) LIMITS AND OFFSETS**

The ASP0800 includes an overclocking function. The total output current is monitored by the ASP0800 using the  $I_{\rm MON}$  output.

Read\_IOUT Command gives the total current in Amps The IOUT value is compared with the Over Clocking or OC Thresholds. There are three OC thresholds Command TBD = OC Threshold 1; Default = TBD Command TBD = OC Threshold 2; Default = TBD Command TBD = OC Threshold 3; Default = TBD IouT is first compared with OC3, If IouT is greater than OC3 then the system is in OC State TBD and Offset TBD is applied. If IouT is less than OC3 but greater than OC2 then the system is in OC State TBD. If IouT is less than OC2 but greater than OC1 then the system is in OC State TBD. If IouT is less than OC1 then the system is in OC State TBD. If IouT is less than OC1 corresponding Offset voltage. The offset voltage for each state is programmable in TBD mV steps up to a max value of  $\pm 200$  mV.

Register TBD VR Offset 1 = Offset voltage for State 1, default value = 0x00

Register TBD VR Offset 2 = Offset voltage for State 2, default value = 0x00

Register TBD VR Offset 3 = Offset voltage for State 3, default value = 0x00

Register TBD VR Offset 4 = Offset voltage for State 4, default value = 0x00

#### **PMBUS INTERFACE**

Control of the ASP0800 is carried out using the PMBus Interface. The physical protocol for PMBus closely matches that of SMBus.

The ASP0800 is connected to this bus as a slave device, under the control of a master controller.

To setup the PMBus Address the ASP0800 sources a 10uA current from the ADD pin through an external resistor. The voltage is then measured by the ADC and user to set the PMBus address. The table below gives the thresholds for each possible PMBus address and also a suitable resistor value.

| Address<br>(8 Bits) | High<br>Threshold | Low<br>Threshold | Suggested Resistor<br>Value |

|---------------------|-------------------|------------------|-----------------------------|

| 0xC0                | 0.1               |                  |                             |

| 0xC2                | 0.25              | 0.15             |                             |

| 0xC4                | 0.5               | 0.3              |                             |

| 0xC6                | 0.75              | 0.55             |                             |

| 0xC8                | 1.0               | 0.8              |                             |

| 0xCA                | 1.4               | 1.1              |                             |

| 0xCC                | 1.9               | 1.5              |                             |

| 0xCE                |                   | 2.0              |                             |

#### Table 10: Setting up the PMBus Address

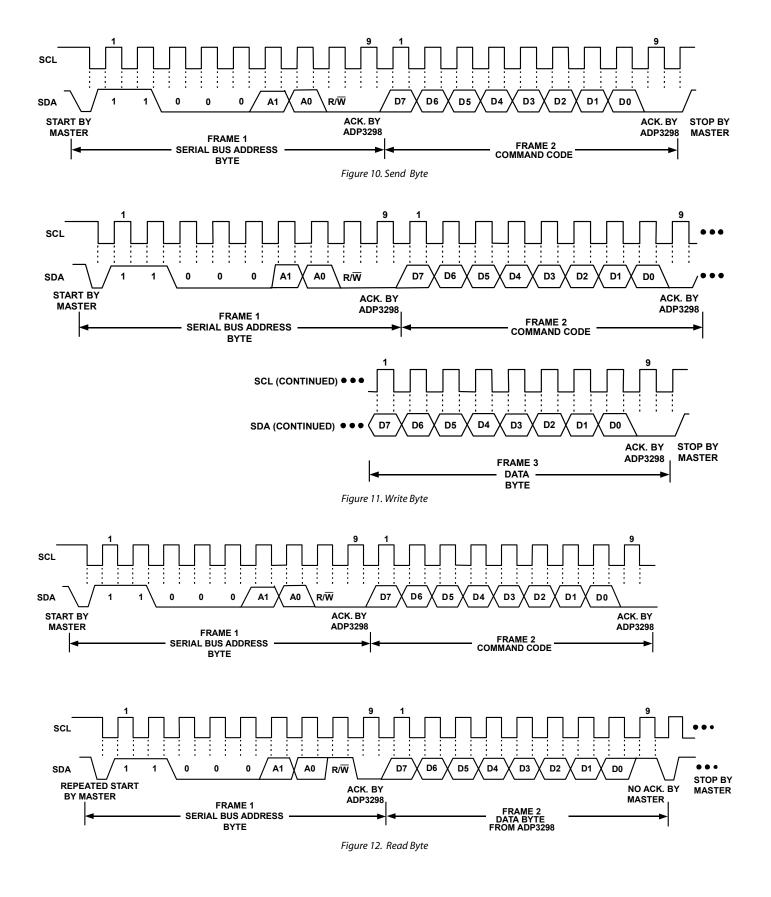

Data is sent over the serial bus in sequences of nine clock pulses: eight bits of data followed by an acknowledge bit from the slave device. Transitions on the data line must occur during the low period of the clock signal and remain stable during the high period, because a low-to-high transition when the clock is high might be interpreted as a stop signal. The number of data bytes that can be transmitted over the serial bus in a single read or write operation is limited only by what the master and slave devices can handle.

1. When all data bytes have been read or written, stop conditions are established. In write mode, the master pulls the data line high during the tenth clock pulse to assert a stop condition. In read mode, the master device overrides the acknowledge bit by pulling the data line high during the low period before the ninth clock pulse; this is known as No Acknowledge. The master takes the data line low during the low period before the tenth clock pulse, and then high during the tenth clock pulse to assert a stop condition.

Any number of bytes of data can be transferred over the serial bus in one operation, but it is not possible to mix read and write in one operation because the type of operation is determined at the beginning and cannot subsequently be changed without starting a new operation.

In the ASP0800, write operations contain one, two or three bytes, and read operations contain one or two bytes. The command code or register address determines the number of bytes to be read or written, See the register map for more information.

To write data to one of the device data registers or read data from it, the address pointer register must be set so that the correct data register is addressed (i.e. command code), and then data can be written to that register or read from it. The first byte of a read or write operation always contains an address that is stored in the address pointer register. If data is to be written to the device, the write operation contains a second data byte that is written to the register selected by the address pointer register.

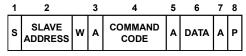

This write byte operation is shown in Figure 11. The device address is sent over the bus, and then  $R/\overline{W}$  is set to 0. This is followed by two data bytes. The first data byte is the address of the internal data register to be written to, which is stored in the address pointer register. The second data byte is the data to be written to the internal data register.

2. The read byte operation is shown in Figure 12. First the command code needs to be written to the ASP0800 so that the required data is sent back. This is done by performing a write to the ASP0800 as before, but only the data byte containing the register address is sent, because no data is written to the register. A repeated start is then issued and a read operation is then performed consisting of the serial bus address; R/W bit set to 1, followed by the data byte read from the data register.

### ASP0800

Rev. P1 | Page 18 of 36 | www.onsemi.com

3. It is not possible to read or write a data byte from a data register without first writing to the address pointer register, even if the address pointer register is already at the correct value.

4. In addition to supporting the send byte, the ASP0800 also supports the read byte, write byte, read word and write word protocols. (See *System Management Bus Specifications Rev. 2.0* and the *PMBus Specification Rev 1.1 Part I and Part II* for more information.)

#### WRITE OPERATIONS

The PMBus specification defines several protocols for different types of read and write operations. The ones used in the ASP0800 are discussed in this section. The following abbreviations are used in the diagrams:

S—START P—STOP R—READ W—WRITE <u>A</u>—ACKNOWLEDGE <u>A</u>—NO ACKNOWLEDGE

The ASP0800 uses the following PMBus write protocols.

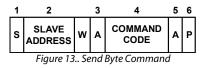

#### Send Byte

In this operation, the master device sends a single command byte to a slave device as follows:

- 1. The master device asserts a start condition on SDA.

- 2. The master sends the 7-bit slave address followed by the write bit (low).

- 3. The addressed slave device asserts ACK on SDA.

- 4. The master sends a command code.

- 5. The slave asserts ACK on SDA.

- 6. The master asserts a stop condition on SDA and the transaction ends.

For the ASP0800, the send byte protocol is used to clear Faults. This operation is shown in Figure 13.

If the master is required to read data from the register immediately after setting up the address, it can assert a repeat start condition immediately after the final ACK and carry out a single byte read without asserting an intermediate stop condition.

#### Write Byte

In this operation, the master device sends a command byte and one data byte to the slave device as follows:

- 5. The master device asserts a start condition on SDA.

- 6. The master sends the 7-bit slave address followed by the write bit (low).

- 7. The addressed slave device asserts ACK on SDA.

- 8. The master sends a command code.

- 9. The slave asserts ACK on SDA.

- 10. The master sends a data byte.

- 11. The slave asserts ACK on SDA.

- 12. The master asserts a stop condition on SDA and the transaction ends.

The byte write operation is shown in Figure 14.

Figure 14. Single Byte Write to a Register

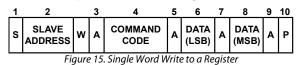

#### Write Word

In this operation, the master device sends a command byte and two data bytes to the slave device as follows:

- 1. The master device asserts a start condition on SDA.

- 2. The master sends the 7-bit slave address followed by the write bit (low).

- 3. The addressed slave device asserts ACK on SDA.

- 4. The master sends a command code.

- 5. The slave asserts ACK on SDA.

- 6. The master sends the first data byte.

- 7. The slave asserts ACK on SDA.

- 8. The master sends the second data byte.

- 9. The slave asserts ACK on SDA.

- 10. The master asserts a stop condition on SDA and the transaction ends.

The word write operation is shown in Figure 15.

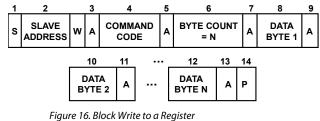

#### **Block Write**

In this operation, the master device sends a command byte and a byte count followed by the stated number of data bytes to the slave device as follows:

- 1. The master device asserts a START condition on SDA.

- The master sends the 7-bit slave address followed by 2. the write bit (low).

- The addressed slave device asserts ACK on SDA. 3.

- 4. The master sends a command code

- The slave asserts ACK on SDA 5.

- The master sends the byte count N 6.

- 7. The slave asserts ACK on SDA

- 8. The master sends the first data byte

- 9. The slave asserts ACK on SDA

- 10. The master sends the second data byte.

- 11. The slave asserts ACK on SDA

- 12. The master sends the remainder of the data byes

- 13. The slave asserts an ACK on SDA after each data byte.

- 14. After the last data byte the master asserts a STOP condition on SDA

#### **READ OPERATIONS**

The ASP0800 uses the following PMBus read protocols.

#### **Read Byte**

13.

In this operation, the master device receives a single byte from a slave device as follows:

- The master device asserts a start condition on SDA. 1.

- The master sends the 7-bit slave address followed by the 2. write bit (low).

- The addressed slave device asserts ACK on SDA. 3.

- 4. The master sends a command code.

- 5. The slave asserted ACK on SDA.

- The master sends a repeated start condition on SDA 6.

- The master sends the 7 bit slave address followed by the 7. read bit (high)

- The slave asserts ACK on SDA 8.

- The slave sends the Data Byte 9

- 10. The master asserts NO ACK on SDA.

- 11. The master asserts a stop condition on SDA and the transaction ends.

| 1 | 2                                           |   | 3 | 4               | 5 | 6 | 7                |   | 8 | 9    | 10 | 11 |

|---|---------------------------------------------|---|---|-----------------|---|---|------------------|---|---|------|----|----|

| s | SLAVE<br>ADDRESS                            | w | A | COMMAND<br>CODE | A | s | SLAVE<br>ADDRESS | R | A | DATA | Ā  | Ρ  |

|   | Figure 17. Single Byte Read from a Register |   |   |                 |   |   |                  |   |   |      |    |    |

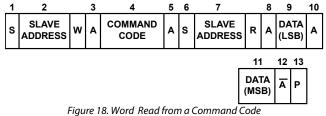

#### **Read Word**

In this operation, the master device receives two data bytes from a slave device as follows:

- The master device asserts a start condition on SDA. 1

- 2. The master sends the 7-bit slave address followed by the write bit (low).

- 3. The addressed slave device asserts ACK on SDA.

- 4. The master sends a command code.

- 5. The slave asserted ACK on SDA.

- The master sends a repeated start condition on SDA 6.

- The master sends the 7 bit slave address followed by 7. the read bit (high)

- 8. The slave asserts ACK on SDA

- 9. The slave sends the first Data Byte (low Data Byte)

- 10. The master asserts ACK on SDA.

- 11. The slave sends the second Data Byte (high Data Byte)

- 12. The masters asserts a No ACK on SDA

- 13. The master asserts a stop condition on SDA and the transaction ends.

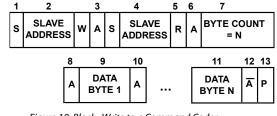

#### **Block Read**

In this operation, the master device sends a command byte, the slave sends a byte count followed by the stated number of data bytes to the master device as follows:

- 1. The master device asserts a START condition on SDA.

- The master sends the 7-bit slave address followed by 2 the write bit (low).

- 3. The addressed slave device asserts ACK on SDA.

- 4. The master sends a REPEATED START condition on SDA

- 5. The master sends the 7-bit slave address followed by the read bit (high).

- The slave asserts ACK on SDA 6.

- 7. The slave sends the byte count N

- 8. The master asserts ACK on SDA

- The slave sends the first data byte 9.

- 10. The master asserts ACK on SDA

- 11. The slave sends the remainder of the data byes, the master asserts an ACK on SDA after each data byte.

- 12. After the last data byte the master asserts a No ACK on SDA.

- 13. The master asserts a STOP condition on SDA

14.

Figure 19. Block Write to a Command Coder

#### PMBus TIMEOUT

The ASP0800 includes an PMBus timeout feature. If there is no PMBus activity for 35 ms, the ASP0800 assumes that the bus is locked and releases the bus. This prevents the device from locking or holding the PMBus expecting data. Some PMBus controllers cannot handle the PMBus timeout feature, so it can be disabled.

#### Configuration Register 1 (0xTBD)

Bit 3 SMB\_TO\_EN = 1; PMBus timeout enabled.

Bit 3 TODIS = 0; PMBus timeout disabled (default).

| VR11 DAC CODES: VIDSEL = HIGH |      |      |      |      |      |      |      |      |  |  |

|-------------------------------|------|------|------|------|------|------|------|------|--|--|

| OUTPUT                        | VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 |  |  |

| OFF                           | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |  |  |

| OFF                           | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    |  |  |

| 1.60000                       | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0    |  |  |

| 1.59375                       | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 1    |  |  |