# 8-Bit Parallel-to-Serial Shift Register

The SN74LS165 is an 8-bit parallel load or serial-in register with complementary outputs available from the last stage. Parallel inputing occurs asynchronously when the Parallel Load  $(\overline{PL})$  input is LOW. With  $\overline{PL}$  HIGH, serial shifting occurs on the rising edge of the clock; new data enters via the Serial Data (DS) input. The 2-input OR clock can be used to combine two independent clock sources, or one input can act as an active LOW clock enable.

# **GUARANTEED OPERATING RANGES**

| Symbol          | Parameter                              | Min  | Тур | Max  | Unit |

|-----------------|----------------------------------------|------|-----|------|------|

| V <sub>CC</sub> | Supply Voltage                         | 4.75 | 5.0 | 5.25 | V    |

| T <sub>A</sub>  | Operating Ambient<br>Temperature Range | 0    | 25  | 70   | °C   |

| I <sub>OH</sub> | Output Current – High                  |      |     | -0.4 | mA   |

| I <sub>OL</sub> | Output Current – Low                   |      |     | 8.0  | mA   |

# ON Semiconductor

Formerly a Division of Motorola http://onsemi.com

> LOW POWER SCHOTTKY

PLASTIC N SUFFIX CASE 648

SOIC D SUFFIX CASE 751B

#### **ORDERING INFORMATION**

| Device     | Package    | Shipping         |

|------------|------------|------------------|

| SN74LS165N | 16 Pin DIP | 2000 Units/Box   |

| SN74LS165D | 16 Pin     | 2500/Tape & Reel |

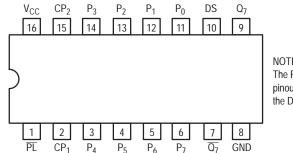

# **CONNECTION DIAGRAM DIP (TOP VIEW)**

NOTE: The Flatpak version has the same pinouts (Connection Diagram) as the Dual In-Line Package.

|                                                           |                                                                                                             | LOADING                          | (Note a)                            |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------------|

| PIN NAMES                                                 |                                                                                                             | HIGH                             | LOW                                 |

| CP <sub>1</sub> , CP <sub>2</sub><br>DS<br><del>P</del> L | Clock (LOW-to-HIGH Going Edge) Inputs<br>Serial Data Input<br>Asynchronous Parallel Load (Active LOW) Input | 0.5 U.L.<br>0.5 U.L.<br>1.5 U.L. | 0.25 U.L.<br>0.25 U.L.<br>0.75 U.L. |

| P <sub>0</sub> – P <sub>7</sub><br>Q <sub>7</sub>         | Parallel Data Inputs Serial Output from Last State                                                          | 0.5 U.L.<br>10 U.L.              | 0.75 U.L.<br>0.25 U.L.<br>5 U.L.    |

| $\overline{\mathbb{Q}}_7$                                 | Complementary Output                                                                                        | 10 U.L.                          | 5 U.L.                              |

# NOTES:

a) 1 TTL Unit Load (U.L.) = 40  $\mu$ A HIGH/1.6 mA LOW.

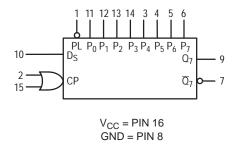

# **LOGIC SYMBOL**

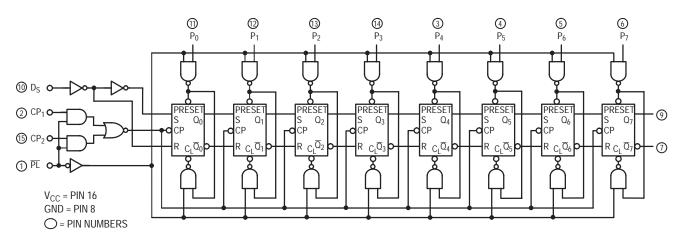

#### **LOGIC DIAGRAM**

# **FUNCTIONAL DESCRIPTION**

The SN74LS165 contains eight clocked master/slave RS flip-flops connected as a shift register, with auxiliary gating to provide overriding asynchronous parallel entry. Parallel data enters when the  $\overline{PL}$  signal is LOW. The parallel data can change while  $\overline{PL}$  is LOW, provided that the recommended setup and hold times are observed.

For clock operation,  $\overline{PL}$  must be HIGH. The two clock inputs perform identically; one can be used as a clock inhibit

by applying a HIGH signal. To avoid double clocking, however, the inhibit signal should only go HIGH while the clock is HIGH. Otherwise, the rising inhibit signal will cause the same response as a rising clock edge. The flip-flops are edge-triggered for serial operations. The serial input data can change at any time, provided only that the recommended setup and hold times are observed, with respect to the rising edge of the clock.

**TRUTH TABLE**

| PL | С | P |                | CONTENTS       |                |                |       |                |                |                | RESPONSE       |  |

|----|---|---|----------------|----------------|----------------|----------------|-------|----------------|----------------|----------------|----------------|--|

|    | 1 | 2 | $Q_0$          | Q <sub>1</sub> | Q <sub>2</sub> | $Q_3$          | $Q_4$ | Q <sub>5</sub> | $Q_6$          | Q <sub>7</sub> | RESPONSE       |  |

| L  | Х | Х | P <sub>0</sub> | P <sub>1</sub> | P <sub>2</sub> | P <sub>3</sub> | $P_4$ | P <sub>5</sub> | P <sub>6</sub> | P <sub>7</sub> | Parallel Entry |  |

| Н  | L |   | Ds             | $Q_0$          | $Q_1$          | $Q_2$          | $Q_3$ | $Q_4$          | $Q_5$          | $Q_6$          | Right Shift    |  |

| Н  | Н |   | $Q_0$          | $Q_1$          | $Q_2$          | $Q_3$          | $Q_4$ | $Q_5$          | $Q_6$          | Q <sub>7</sub> | No Change      |  |

| Н  |   | L | Ds             | $Q_0$          | $Q_1$          | $Q_2$          | $Q_3$ | $Q_4$          | $Q_5$          | Q <sub>6</sub> | Right Shift    |  |

| Н  |   | Н | $Q_0$          | Q <sub>1</sub> | $Q_2$          | $Q_3$          | $Q_4$ | $Q_5$          | $Q_6$          | Q <sub>7</sub> | No Change      |  |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

# DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

|                 |                                          |     | Limits |              |      |                                                                                 |                                                                         |

|-----------------|------------------------------------------|-----|--------|--------------|------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Symbol          | Parameter                                | Min | Тур    | Max          | Unit | Tes                                                                             | t Conditions                                                            |

| V <sub>IH</sub> | Input HIGH Voltage                       | 2.0 |        |              | V    | Guaranteed Input HIGH Voltage for All Inputs                                    |                                                                         |

| V <sub>IL</sub> | Input LOW Voltage                        |     |        | 0.8          | V    | Guaranteed Inpu                                                                 | t LOW Voltage for                                                       |

| $V_{IK}$        | Input Clamp Diode Voltage                |     | -0.65  | -1.5         | V    | $V_{CC} = MIN, I_{IN} =$                                                        | –18 mA                                                                  |

| V <sub>OH</sub> | Output HIGH Voltage                      | 2.7 | 3.5    |              | V    | $V_{CC}$ = MIN, $I_{OH}$ = MAX, $V_{IN}$ = $V_{IH}$ or $V_{IL}$ per Truth Table |                                                                         |

|                 | Outroot I OW/Vallana                     |     | 0.25   | 0.4          | ٧    | I <sub>OL</sub> = 4.0 mA                                                        | $V_{CC} = V_{CC} MIN,$                                                  |

| $V_{OL}$        | Output LOW Voltage                       |     | 0.35   | 0.5          | ٧    | I <sub>OL</sub> = 8.0 mA                                                        | V <sub>IN</sub> = V <sub>IL</sub> or V <sub>IH</sub><br>per Truth Table |

| l <sub>IH</sub> | Input HIGH Current Other Inputs PL Input |     |        | 20<br>60     | μΑ   | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 2.7 V                                  |                                                                         |

| ""              | Other Inputs PL Input                    |     |        | 0.1<br>0.3   | mA   | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 7.0 V                                  |                                                                         |

| I <sub>IL</sub> | Input LOW Current Other Inputs PL Input  |     |        | -0.4<br>-1.2 | mA   | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 0.4 V                                  |                                                                         |

| I <sub>OS</sub> | Short Circuit Current (Note 1)           | -20 |        | -100         | mA   | V <sub>CC</sub> = MAX                                                           |                                                                         |

| I <sub>CC</sub> | Power Supply Current                     |     |        | 36           | mA   | V <sub>CC</sub> = MAX                                                           |                                                                         |

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.

#

|                                      |                                                    |     | Limits   |          |      |                                                  |

|--------------------------------------|----------------------------------------------------|-----|----------|----------|------|--------------------------------------------------|

| Symbol                               | Parameter                                          | Min | Тур      | Max      | Unit | Test Conditions                                  |

| f <sub>MAX</sub>                     | Maximum Input Clock Frequency                      | 25  | 35       |          | MHz  |                                                  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay PE to Output                     |     | 22<br>22 | 35<br>35 | ns   |                                                  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>Clock to Output               |     | 27<br>28 | 40<br>40 | ns   | $V_{CC} = 5.0 \text{ V}$ $C_{L} = 15 \text{ pF}$ |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay P <sub>7</sub> to Q <sub>7</sub> |     | 14<br>21 | 25<br>30 | ns   | - '                                              |

| t <sub>PLH</sub>                     | Propagation Delay $P_7$ to $\overline{Q}_7$        |     | 21<br>16 | 30<br>25 | ns   |                                                  |

# AC SETUP REQUIREMENTS $(T_A = 25^{\circ}C)$

|                  |                                                            |     | Limits |     | Limits |                         |  |  |

|------------------|------------------------------------------------------------|-----|--------|-----|--------|-------------------------|--|--|

| Symbol           | Parameter                                                  | Min | Тур    | Max | Unit   | Test Conditions         |  |  |

| t <sub>W</sub>   | CP Clock Pulse Width                                       | 25  |        |     | ns     |                         |  |  |

| t <sub>W</sub>   | PL Pulse Width                                             | 15  |        |     | ns     |                         |  |  |

| t <sub>s</sub>   | Parallel Data Setup Time                                   | 10  |        |     | ns     |                         |  |  |

| t <sub>s</sub>   | Serial Data Setup Time                                     | 20  |        |     | ns     | V <sub>CC</sub> = 5.0 V |  |  |

| t <sub>s</sub>   | CP <sub>1</sub> to CP <sub>2</sub> Setup Time <sup>1</sup> | 30  |        |     | ns     |                         |  |  |

| t <sub>h</sub>   | Hold Time                                                  | 0   |        |     | ns     |                         |  |  |

| t <sub>rec</sub> | Recovery Time, PL to CP                                    | 45  |        |     | ns     |                         |  |  |

<sup>&</sup>lt;sup>1</sup>The role of CP<sub>1</sub> and CP<sub>2</sub> in an application may be interchanged.

#### **DEFINITION OF TERMS:**

SETUP TIME  $(t_s)$  — is defined as the minimum time required for the correct logic level to be present at the logic input prior to the clock transition from LOW-to-HIGH in order to be recognized and transferred to the outputs.

HOLD TIME (t<sub>h</sub>) — is defined as the minimum time following the clock transition from LOW-to-HIGH that the logic level must be maintained at the input in order to ensure

continued recognition. A negative hold time indicates that the correct logic level may be released prior to the clock transition from LOW-to-HIGH and still be recognized.

RECOVERY TIME ( $t_{rec}$ )—is defined as the minimum time required between the end of the  $\overline{PL}$  pulse and the clock transition from LOW-to-HIGH in order to recognize and transfer loaded Data to the Q outputs.

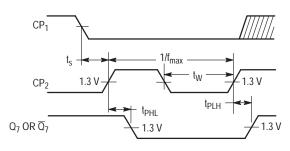

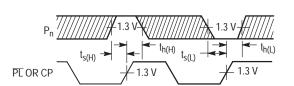

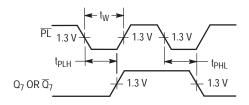

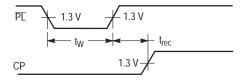

# **AC WAVEFORMS**

Figure 1.

Figure 3.

Figure 2.

Figure 4.

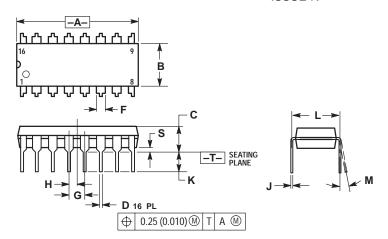

# **PACKAGE DIMENSIONS**

# **N SUFFIX** PLASTIC PACKAGE CASE 648-08 ISSUE R

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.

4. DIMENSION B DOES NOT INCLUDE MOLD FLASH.

5. ROUNDED CORNERS OPTIONAL.

|     | INC   | HES         | MILLIN   | IETERS |  |

|-----|-------|-------------|----------|--------|--|

| DIM | MIN   | MAX         | MIN      | MAX    |  |

| Α   | 0.740 | 0.770       | 18.80    | 19.55  |  |

| В   | 0.250 | 0.270       | 6.35     | 6.85   |  |

| С   | 0.145 | 0.175       | 3.69     | 4.44   |  |

| D   | 0.015 | 0.021       | 0.39     | 0.53   |  |

| F   | 0.040 | 0.70        | 1.02     | 1.77   |  |

| G   | 0.100 | BSC         | 2.54 BSC |        |  |

| Н   | 0.050 | BSC         | 1.27 BSC |        |  |

| J   | 0.008 | 0.015       | 0.21     | 0.38   |  |

| K   | 0.110 | 0.130       | 2.80     | 3.30   |  |

| L   | 0.295 | 0.295 0.305 |          | 7.74   |  |

| М   | 0°    | 10 °        | 0°       | 10 °   |  |

| S   | 0.020 | 0.040       | 0.51     | 1.01   |  |

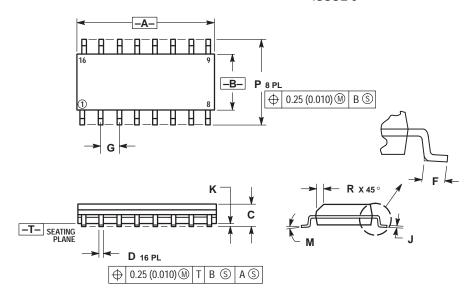

# **PACKAGE DIMENSIONS**

# **D SUFFIX** PLASTIC SOIC PACKAGE CASE 751B-05 **ISSUE J**

#### NOTES:

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIN | IETERS | INC       | HES   |  |

|-----|--------|--------|-----------|-------|--|

| DIM | MIN    | MAX    | MIN       | MAX   |  |

| Α   | 9.80   | 10.00  | 0.386     | 0.393 |  |

| В   | 3.80   | 4.00   | 0.150     | 0.157 |  |

| С   | 1.35   | 1.75   | 0.054     | 0.068 |  |

| D   | 0.35   | 0.49   | 0.014     | 0.019 |  |

| F   | 0.40   | 1.25   | 0.016     | 0.049 |  |

| G   | 1.27   | BSC    | 0.050 BSC |       |  |

| J   | 0.19   | 0.25   | 0.008     | 0.009 |  |

| K   | 0.10   | 0.25   | 0.004     | 0.009 |  |

| M   | 0 °    | 7°     | 0 °       | 7°    |  |

| Р   | 5.80   | 6.20   | 0.229     | 0.244 |  |

| R   | 0.25   | 0.50   | 0.010     | 0.019 |  |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### PUBLICATION ORDERING INFORMATION

North America Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: ONlit@hibbertco.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

EUROPE: LDC for ON Semiconductor – European Support

German Phone: (+1) 303–308–7140 (M–F 2:30pm to 5:00pm Munich Time)

Email: ONlit–german@hibbertco.com

French Phone: (+1) 303–308–7141 (M–F 2:30pm to 5:00pm Toulouse Time)

Email: ONlit-french@hibbertco.com

English Phone: (+1) 303–308–7142 (M–F 1:30pm to 5:00pm UK Time)

Email: ONlit@hibbertco.com

ASIA/PACIFIC: LDC for ON Semiconductor – Asia Support

Phone: 303–675–2121 (Tue–Fri 9:00am to 1:00pm, Hong Kong Time) Toll Free from Hong Kong 800–4422–3781

Email: ONlit-asia@hibbertco.com

JAPAN: ON Semiconductor, Japan Customer Focus Center 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–8549

**Phone**: 81–3–5487–8345 **Email**: r14153@onsemi.com

**Fax Response Line**: 303–675–2167

800-344-3810 Toll Free USA/Canada

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local

Sales Representative.

SN74LS165/D