# CS43122

# 122 dB, 24-Bit, 192 kHz DAC for Digital Audio

## **Features**

- 24 Bit Conversion

- Up to 192 kHz Sample Rates

- 122 dB Dynamic Range

- •-102 dB THD+N

- Second-Order Dynamic-Element Matching

- Low Clock Jitter Sensitivity

- 102 dB Stop-band attenuation

- Single +5 V supply

- Soft Mute Control

- Digital De-Emphasis for 32, 44.1, and 48 kHz

- External Reference Input

- Pin-compatible with the CS4396

## Description

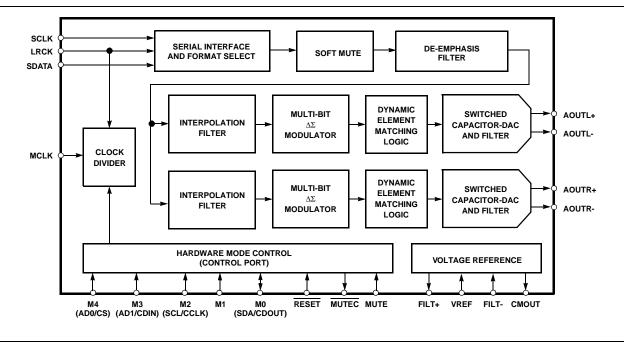

The CS43122 is a complete high performance 24 bit-192 kHz stereo digital-to-analog conversion system. The device includes a digital interpolation filter followed by an oversampled 5 bit delta-sigma modulator which drives second generation dynamic-element-matching (DEM) selection logic. The output from the DEM block controls the input to a multi-element switched capacitor DAC/lowpass filter, with fully-differential outputs. This multi-bit architecture features significantly lower out-of-band noise and jitter sensitivity than traditional 1-bit designs, and the advanced second generation DEM guarantees low noise and distortion at all signal levels.

The CS43122 is the optimal D/A converter solution for any application that requires the highest performance and best possible sound quality including high-end consumer and professional audio products such as Universal DVD players, A/V receivers, Outboard D/A Converters, CD Players, and Mixing Consoles.

#### **ORDERING INFORMATION**

CS43122-KS -10° to 70° C 28-pin SOIC CDB43122

**Evaluation Board**

Advance Product Information

This document contains information for a new product. Cirrus Logic reserves the right to modify this product without notice.

CIRRUS LOGIC P.O. Box 17847, Austin, Texas 78760 (512) 445 7222 FAX: (512) 445 7581 http://www.cirrus.com

Copyright © Cirrus Logic, Inc. 2000 (All Rights Reserved)

#### **TABLE OF CONTENTS**

| 1. | CHARACTERISTICS/SPECIFICATIONS           | 4    |

|----|------------------------------------------|------|

|    | ANALOG CHARACTERISTICS                   | 4    |

|    | DIGITAL CHARACTERISTICS                  | 8    |

|    | ABSOLUTE MAXIMUM RATINGS                 | 8    |

|    | RECOMMENDED OPERATING CONDITIONS         | 8    |

|    | SWITCHING CHARACTERISTICS                | 9    |

|    | SWITCHING CHARACTERISTICS - CONTROL PORT | . 10 |

| 2. | TYPICAL CONNECTION DIAGRAM               | .12  |

| 3. | REGISTER DESCRIPTION                     | .13  |

|    | 3.1 Mode Control Register (Address 01H)  | . 13 |

| 4. | PIN DESCRIPTION                          | .15  |

| 5. | APPLICATIONS                             | . 19 |

|    | 5.1 Recommended Power-up Sequence        | . 19 |

| 6. | CONTROL PORT INTERFACE                   |      |

|    | 6.1 SPI Mode                             | . 19 |

|    | 6.2 2 Wire Mode                          |      |

|    | 6.3 Memory Address Pointer (MAP)         | . 20 |

| 7. | PARAMETER DEFINITIONS                    |      |

| 8. | REFERENCES                               | . 25 |

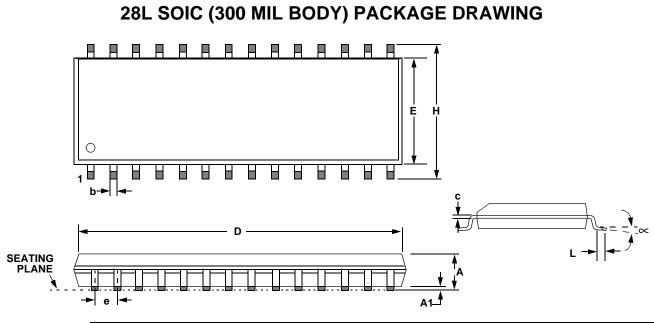

| 9. | PACKAGE DIMENSIONS                       | . 26 |

Contacting Cirrus Logic Support For a complete listing of Direct Sales, Distributor, and Sales Representative contacts, visit the Cirrus Logic web site at: http://www.cirrus.com/corporate/contacts/sales.cfm

Preliminary product information describes products which are in production, but for which full characterization data is not yet available. Advance product information describes products which are in development and subject to development changes. Cirrus Logic, Inc. has made best efforts to ensure that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (express or implied). Customers are advised to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability. No responsibility is assumed by Cirrus Logic, Inc. for the use of this information, including use of this information as the basis for manufacture or sale of any items, nor for infringements of patents or other rights of third parties. This document is the property of Cirrus Logic, Inc. and by furnishing this information, Cirrus Logic, Inc. Gruns Logic, Inc., copyright owner of the information contained herein, gives consent for copies to be made of the information only for use within your organization with respect to Cirrus Logic integrated circuits or other parts of Cirrus Logic, Inc. The same consent is given for similar information contained on any Cirrus Logic website or disk. This consent does not extend to other copyright such as copyring for general distribution, advertising or promotional purposes, or for creating any work for resale. The names of products of Cirrus Logic, Inc. or other vendors and suppliers appearing in this document may be trademarks or service marks of their respective owners which may be registered in some jurisdictions. A list of Cirrus Logic, Inc. trademarks and service marks can be found at http://www.cirrus.com.

## LIST OF FIGURES

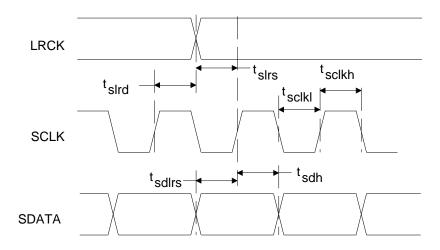

| Figure 1. Serial Audio Input Timing               | 9  |

|---------------------------------------------------|----|

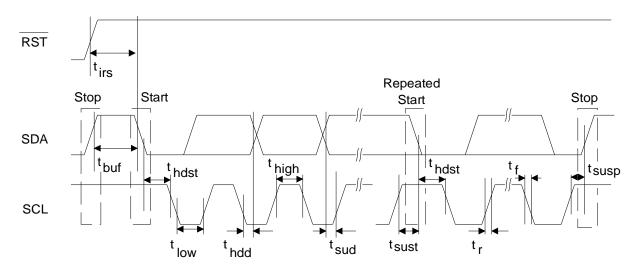

| Figure 2. 2 Wire Mode Control Port Timing         | 10 |

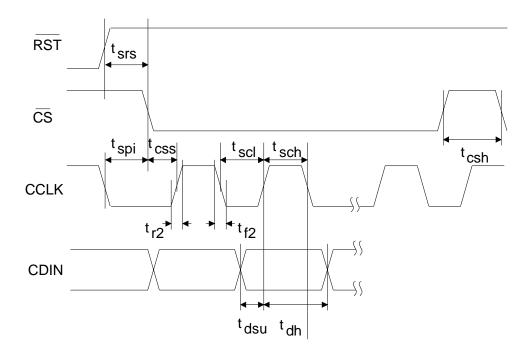

| Figure 3. SPI Control Port Timing                 | 11 |

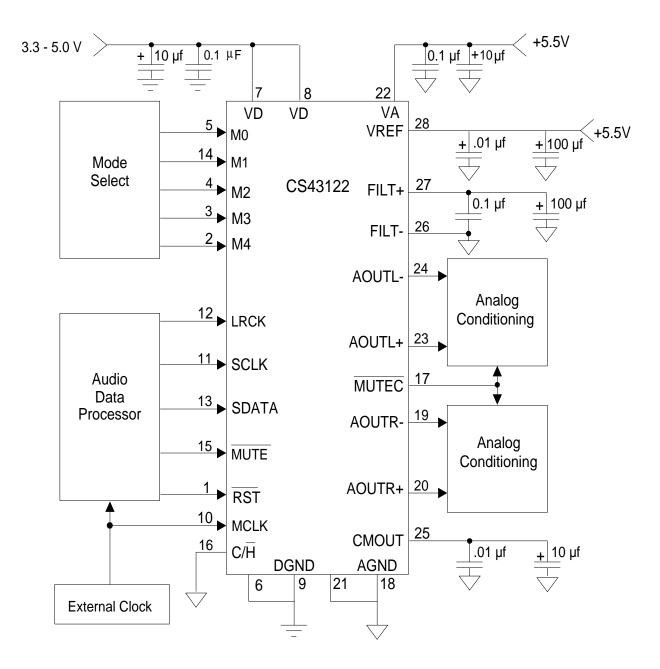

| Figure 4. Typical Connection Diagram              | 12 |

| Figure 5. Control Port Timing, SPI mode           | 20 |

| Figure 6. Control Port Timing, 2 wire Mode        | 20 |

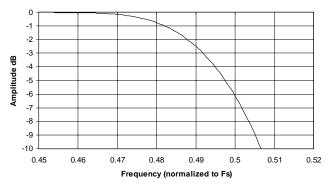

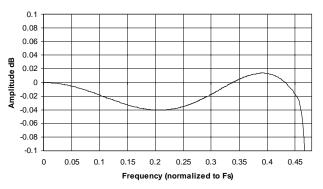

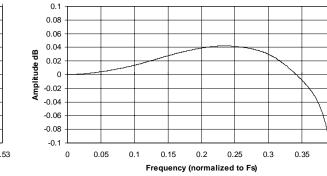

| Figure 7. Operational Mode 0 Transition Band      |    |

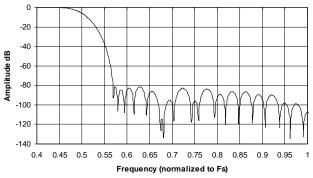

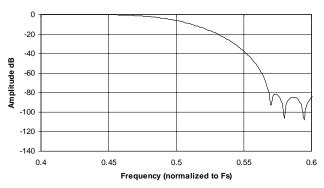

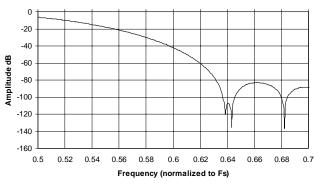

| Figure 8. Operational Mode 0 Stopband Rejection   |    |

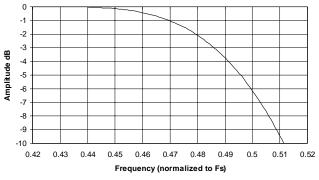

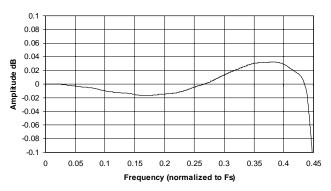

| Figure 9. Operational Mode 0 Transition Band      | 22 |

| Figure 10. Operational Mode 0 Frequency Response  | 22 |

| Figure 11. Operational Mode 0 Stopband            |    |

| Figure 12. Operational Mode 0 Transition Band     |    |

| Figure 13. Operational Mode 0 Transition Band     | 22 |

| Figure 14. Operational Mode 0 Frequency Response  | 22 |

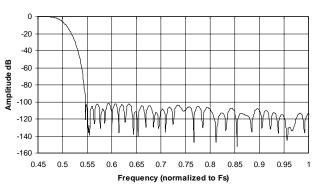

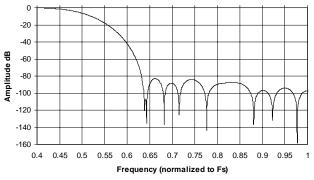

| Figure 15. Operational Mode 2 Stopband Rejection  |    |

| Figure 16. Operational Mode 2 Transition Band     |    |

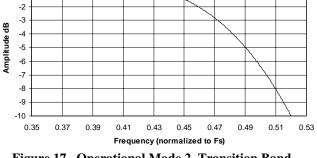

| Figure 17. Operational Mode 2 Transition Band     | 23 |

| Figure 18. Operational Mode 2 Frequency Response  |    |

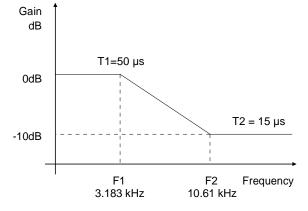

| Figure 19. De-Emphasis Curve                      |    |

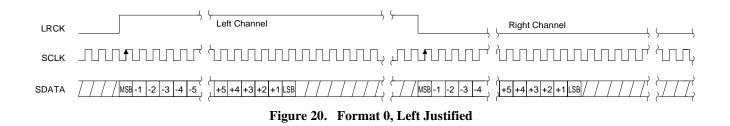

| Figure 20. Format 0, Left Justified               |    |

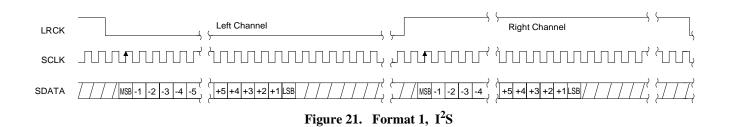

| Figure 21. Format 1, I <sup>2</sup> S             | 24 |

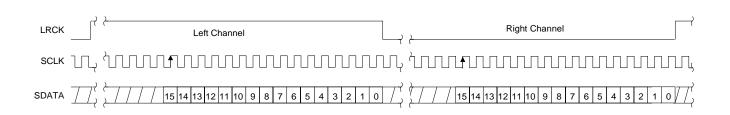

| Figure 22. Format 2, Right Justified, 16-Bit Data | 24 |

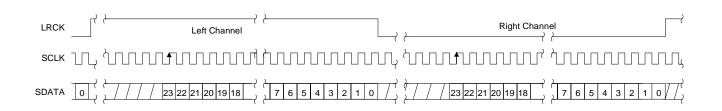

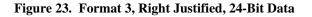

| Figure 23. Format 3, Right Justified, 24-Bit Data | 24 |

|                                                   |    |

## LIST OF TABLES

| Table 1. Operational Mode 0 (16 to 55 kHz sample rates) Common Clock Frequencies  | 16 |

|-----------------------------------------------------------------------------------|----|

| Table 2. Operational Mode 1 (45 to 105 kHz sample rates) Common Clock Frequencies | 16 |

| Table 3. Operational Mode 2 (95 to 200 kHz sample rates) Common Clock Frequencies | 16 |

| Table 4. Operational Mode 0 (16 to 55 kHz) Digital Interface Format Options       | 21 |

| Table 5. Operational Mode 0 (16 to 55 kHz) De-Emphasis Options                    | 21 |

| Table 6. Operational Mode 1 (45 to 105 kHz) Sample Rate Mode Options              | 21 |

| Table 7. Operational Mode 2 (95 to 200 kHz) Sample Rate Mode Options              | 21 |

## 1. CHARACTERISTICS/SPECIFICATIONS

**ANALOG CHARACTERISTICS** ( $T_A = 25^{\circ}$  C; Logic "1" = VD = 3 V; VA = 5.5 V;VREF=5.5 V Logic "0" = DGND;Full-Scale Output Sine Wave, 997 Hz; MCLK = 12.288 MHz; SCLK = 3.072 MHz; Measurement Bandwidth 10 Hz to 20 kHz, unless otherwise specified. Test load =  $R_L = 1k\Omega$ ,  $C_L = 10$  pF)

| Parame                      | eter         |            | Symbol | Min | Тур  | Мах | Unit |

|-----------------------------|--------------|------------|--------|-----|------|-----|------|

| Dynamic Performance - O     | Mode 1 (Fs = | - 48 kHz)  |        |     |      | I   |      |

| Dynamic Range               |              | (Note 1)   |        |     |      |     |      |

|                             | 24-Bit       | unweighted |        | TBD | 119  | -   | dB   |

|                             |              | A-Weighted |        | TBD | 122  | -   | dB   |

|                             | 16-Bit       | unweighted |        | -   | 95   | -   | dB   |

|                             | (Note 2)     | A-Weighted |        | -   | 98   | -   | dB   |

| Total Harmonic Distortion + | Noise        | (Note 1)   | THD+N  |     |      |     |      |

|                             | 24-Bit       | 0 dB       |        | -   | -102 | TBD | dB   |

|                             |              | -20 dB     |        | -   | -99  | TBD | dB   |

|                             |              | -60 dB     |        | -   | -59  | TBD | dB   |

|                             | 16-Bit       | 0 dB       |        | -   | -95  | -   | dB   |

|                             | (Note 2)     | -20 dB     |        | -   | -75  | -   | dB   |

|                             |              | -60 dB     |        | -   | -35  | -   | dB   |

## ANALOG CHARACTERISTICS (CONTINUED)

| Param                       | neter       |                  | Symbol     | Min | Тур        | Max | Unit |

|-----------------------------|-------------|------------------|------------|-----|------------|-----|------|

| Dynamic Performance - 0     | Operational | Mode 0 (Fs =     | 48 kHz)    |     |            |     |      |

| Dynamic Range               |             | (Note 1)         |            |     |            |     |      |

|                             | 24-Bit      | unweighted       |            | TBD | 117        | -   | dB   |

|                             |             | A-Weighted       |            | TBD | 120        | -   | dB   |

|                             | 16-Bit      | unweighted       |            | -   | 95         | -   | dB   |

|                             | (Note 2)    | A-Weighted       |            | -   | 98         | -   | dB   |

| Total Harmonic Distortion + | Noise       | (Note 1)         | THD+N      |     |            |     |      |

|                             | 24-Bit      | 0 dB             |            | -   | -100       | TBD | dB   |

|                             |             | -20 dB           |            | -   | -97        | TBD | dB   |

|                             |             | -60 dB           |            | -   | -55        | TBD | dB   |

|                             | 16-Bit      | 0 dB             |            | -   | -95        | -   | dB   |

|                             | (Note 2)    | -20 dB           |            | -   | -75        | -   | dB   |

|                             | · · ·       | -60 dB           |            | -   | -35        | -   | dB   |

| Dynamic Performance - C     | Operational | Mode 1 (Fs =     | - 96 kHz)  |     |            |     |      |

| Dynamic Range               | -           | (Note 1)         | -          |     |            |     |      |

| , ,                         | 24-Bit      | unweighted       |            | TBD | 117        | -   | dB   |

|                             |             | A-Weighted       |            | TBD | 120        | -   | dB   |

|                             | 40 kHz ba   | -                |            | TBD | 114        | -   | dB   |

|                             |             | unweighted       |            | -   | 92         | -   | dB   |

|                             | 16-Bit      | unweighted       |            | -   | 98         | -   | dB   |

|                             | (Note 2)    | A-Weighted       |            |     |            |     |      |

| Total Harmonic Distortion + | Noise       | (Note 1)         | THD+N      |     |            |     |      |

|                             | 24-Bit      | 0 dB             |            | -   | -100       | TBD | dB   |

|                             |             | -20 dB           |            | -   | -97        | TBD | dB   |

|                             |             | -60 dB           |            | -   | -55        | TBD | dB   |

|                             | 16-Bit      | 0 dB             |            | -   | -95        | -   | dB   |

|                             | (Note 2)    | -20 dB           |            | -   | -75        | -   | dB   |

|                             | (           | -60 dB           |            | -   | -35        | -   | dB   |

| Dynamic Performance - C     | Operationa  |                  | = 192 kHz) |     |            |     | -    |

| Dynamic Range               |             | (Note 1)         |            |     |            |     |      |

|                             | 24-Bit      | unweighted       |            | TBD | 117        | -   | dB   |

|                             | ZIBR        | A-Weighted       |            | TBD | 120        | _   | dB   |

|                             | 40 kHz ba   |                  |            | TBD | 114        | _   | dB   |

|                             |             | unweighted       |            | -   | 95         | _   | dB   |

|                             | 16-Bit      | unweighted       |            | -   | 98         | -   | dB   |

|                             | (Note 2)    | A-Weighted       |            |     | 50         |     | 20   |

| Total Harmonic Distortion + | · /         | (Note 1)         | THD+N      |     |            |     |      |

|                             | 24-Bit      | (Note T)<br>0 dB |            | _   | -100       | TBD | dB   |

|                             |             | -20 dB           |            | -   | -97        | TBD | dB   |

|                             |             | -20 dB<br>-60 dB |            | -   | -55        | TBD | dB   |

|                             | 16-Bit      | -00 dB<br>0 dB   |            | -   | -55<br>-95 |     | dB   |

|                             | (Note 2)    | -20 dB           |            | -   | -95<br>-75 | -   | dB   |

|                             |             | -20 dB<br>-60 dB |            | -   | -75        | -   | dB   |

|                             |             | -00 0D           |            | _   |            | -   | uD   |

## ANALOG CHARACTERISTICS (CONTINUED)

| Para                   | ameter            | Symbo                 | 1 1 | /D = 3 | V   | \<br>\ | /D = 5 | V   | Unit |

|------------------------|-------------------|-----------------------|-----|--------|-----|--------|--------|-----|------|

| Power Supplies         |                   |                       | Min | Тур    | Max | Min    | Тур    | Max |      |

| Supply Current         | normal oper       | ration I <sub>A</sub> | -   | 17     | TBD | -      | 17     | TBD | mA   |

| VA = 5 .0V             | normal oper       | ration I <sub>D</sub> | -   | 27     |     | -      | 24     |     | mA   |

|                        | power-down        | state $I_D + I_A$     | -   | 60     |     | -      | 30     | -   | μΑ   |

| Power Dissipation      | normal oper       | ation                 | -   | 166    | TBD | -      | 205    | TBD | mW   |

| VA = 5 .0V             | power-            | down                  | -   | 0.3    | -   | -      | 0.3    | -   | mW   |

| Power Supply Rejection | Ratio (1 kHz) (No | ote 3) PSRR           | -   | 60     | -   | -      | 60     | -   | dB   |

|                        | (12               | 0 Hz)                 | -   | 40     | -   | -      | 40     | -   | dB   |

| Parameter                              | Symbol | Min | Тур      | Max | Unit   |

|----------------------------------------|--------|-----|----------|-----|--------|

| Analog Output                          |        |     |          |     |        |

| Full Scale Differential Output Voltage |        | TBD | 1.33VREF | TBD | Vpp    |

| Common Mode Voltage                    |        | -   | 0.5VREF  | -   | VDC    |

| Interchannel Gain Mismatch             |        | -   | 0.1      | -   | dB     |

| Gain Drift                             |        | -   | 100      | -   | ppm/°C |

| Differential DC Offset                 |        | -   | 2.0      | TBD | mV     |

| AC-Load Resistance                     | RL     | 1.0 | -        | -   | kΩ     |

| Load Capacitance                       | CL     | -   | -        | 100 | pF     |

| Interchannel Isolation (1 kHz          | z)     | -   | 90       | -   | dB     |

Notes: 1. Triangular PDF dithered data.

- 2. Performance limited by 16-bit quantization noise.

- 3. Valid with the recommended capacitor values on FILT+ and CMOUT as shown in Figure 1. Increasing the capacitance will also increase the PSRR.

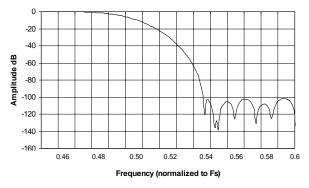

## ANALOG CHARACTERISTICS (Continued)

| Parame                    | ter                                  | Symbol     | Min          | Тур   | Max            | Unit     |

|---------------------------|--------------------------------------|------------|--------------|-------|----------------|----------|

| Combined Digital and On-c | hip Analog Filter Resp               | oonse - Op | erational Mo | ode 0 |                |          |

| Passband                  | (Note 4)                             |            |              |       |                |          |

|                           | to -0.1 dB corner                    |            | -            | -     | 0.470          | Fs       |

|                           | to -3 dB corner                      |            | -            | -     | 0.492          | Fs       |

| Frequency Response 10 Hz  | to 20 kHz                            |            | 020          | -     | +0.015         | dB       |

| Passband Ripple           |                                      |            | -            | -     | ±0.0001        | dB       |

| StopBand                  |                                      |            | .5465        | -     | -              | Fs       |

| StopBand Attenuation      | (Note 5)                             |            | 102          | -     | -              | dB       |

| Group Delay               | (Note 6)                             | tgd        | -            | 37/Fs | -              | S        |

| De-emphasis Error         | (Note 7)                             |            |              |       |                |          |

|                           | Fs = 32 kHz                          |            | -            | -     | ±0.10          | dB       |

| (Relative to 1 kHz)       | Fs = 44.1 kHz                        |            | -            | -     | ±0.10          | dB       |

|                           | Fs = 48 kHz                          |            | -            | -     | ±0.13          | dB       |

| Combined Digital and On-c |                                      | -          | erational Mo | ode 1 |                |          |

| Passband                  | (Note 4)                             |            |              |       | 0.440          | _        |

|                           | to -0.1 dB corner<br>to -3 dB corner |            | 0            | -     | 0.448<br>0.486 | Fs<br>Fs |

|                           |                                      |            | •            | -     |                | -        |

| Frequency Response 10 Hz  | 10 20 KHZ                            |            | -0.017       | -     | 0.035          | dB       |

| Passband Ripple           |                                      |            | -            | -     | ±0.0008        | dB       |

| StopBand                  |                                      |            | .570         | -     | -              | Fs       |

| StopBand Attenuation      | (Note 5)                             |            | 82           | -     | -              | dB       |

| Group Delay               |                                      | tgd        | -            | 20/Fs | -              | S        |

| Combined Digital and On-c | hip Analog Filter Resp               | oonse - Op | erational Mo | ode 2 |                |          |

| Passband                  | (Note 4)                             |            |              |       |                |          |

|                           | to -0.1 dB corner                    |            | -            | -     | 0.385          | Fs       |

|                           | to -3 dB corner                      |            | -            | -     | 0.472          | Fs       |

| Frequency Response 10 Hz  | to 20 kHz                            |            | 0            | -     | +0.015         | dB       |

| Passband Ripple           |                                      |            | -            | -     | ±0.00065       | dB       |

| StopBand                  |                                      |            | 0.635        | -     | -              | Fs       |

| StopBand Attenuation      | (Note 5)                             |            | 83           | -     | -              | dB       |

| Group Delay               |                                      | tgd        | -            | 11/Fs | -              | S        |

Notes: 4. Response is clock dependent and will scale with Fs. Note that the response plots (Figures 7-18) have been normalized to Fs and can be de-normalized by multiplying the X-axis scale by Fs.

- 5. For Operational Mode 0, the Measurement Bandwidth is 0.5465 Fs to 1.4 Fs. For Operational Mode 1, the Measurement Bandwidth is 0.570 Fs to 1.4 Fs. For Operational Mode 2, the Measurement Bandwidth is 0.635 Fs to 1.3 Fs.

- 6. Group Delay for Fs=48 kHz 37/48 kHz=770 μs

- 7. De-emphasis is available only in Operational Mode 0.

## **DIGITAL CHARACTERISTICS** ( $T_A = 25^{\circ}$ C; VD = 3.0 V - 5.25 V)

| Parameters                  |          | Symbol          | Min | Тур | Max | Units |

|-----------------------------|----------|-----------------|-----|-----|-----|-------|

| High-Level Input Voltage    | VD = 5 V | VIH             | 2.0 | -   | -   | V     |

|                             | VD = 3 V |                 | 2.0 | -   | -   | V     |

| Low-Level Input Voltage     | VD = 5 V | V <sub>IL</sub> | -   | -   | 0.8 | V     |

|                             | VD = 3 V |                 | -   | -   | 0.8 | V     |

| Input Leakage Current       |          | l <sub>in</sub> | -   | -   | ±10 | μA    |

| Input Capacitance           |          |                 | -   | 8   | -   | pF    |

| Maximum MUTEC Drive Current |          |                 | -   | 3   | -   | mA    |

## **ABSOLUTE MAXIMUM RATINGS** (AGND = 0 V, all voltages with respect to ground.)

|                        | Parameter                                     | Symbol           | Min  | Max      | Unit |

|------------------------|-----------------------------------------------|------------------|------|----------|------|

| DC Power Supply:       | Positive Analog                               | VA               | -0.3 | 6.0      | V    |

|                        | Positive Digital                              | VD               | -0.3 | 6.0      | V    |

|                        | Reference Voltage                             | VREF             | -0.3 | VA       | V    |

| Input Current, Any Pin | Except Supplies                               | l <sub>in</sub>  | -    | ±10      | mA   |

| Digital Input Voltage  |                                               | V <sub>IND</sub> | -0.3 | (VD)+0.4 | V    |

| Ambient Operating Ten  | Ambient Operating Temperature (power applied) |                  | -55  | 125      | °C   |

| Storage Temperature    |                                               | T <sub>stg</sub> | -65  | 150      | °C   |

WARNING: WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

## **RECOMMENDED OPERATING CONDITIONS** (DGND = 0V; all voltages with respect to ground)

|                       | Parameter         | Symbol         | Min  | Тур | Max  | Unit |

|-----------------------|-------------------|----------------|------|-----|------|------|

| DC Power Supply:      | Positive Digital  | VD             | 3.0  | 3.3 | 5.25 | V    |

|                       | Positive Analog   | VA             | 5.25 | 5.5 | 5.75 | V    |

|                       | Reference Voltage | VREF           | 5.25 | 5.5 | VA   | V    |

| Specified Temperature | Range             | T <sub>A</sub> | -10  | -   | 70   | °C   |

## **SWITCHING CHARACTERISTICS** ( $T_A$ = -10 to 70° C; Logic 0 = AGND = DGND; Logic

1 = VD = 5.25 to 3.0 Volts;  $C_L = 20$  pF)

|                        | Parameter                                                                                     | Symbol             | Min    | Тур | Max    | Unit |

|------------------------|-----------------------------------------------------------------------------------------------|--------------------|--------|-----|--------|------|

| Input Sample Rate      | (Operational Mode 0)                                                                          | Fs                 | 16     | -   | 55     | kHz  |

|                        | (Operational Mode 1)                                                                          |                    | 45     | -   | 105    | kHz  |

|                        | (Operational Mode 2)                                                                          | Fs                 | 95     | -   | 200    | kHz  |

| LRCK Duty Cycle        |                                                                                               |                    | 45     | 50  | 55     | %    |

| MCLK Frequency         | (Operational Mode 0, 256 Fs)<br>(Operational Mode 1, 128 Fs)<br>(Operational Mode 2, 64 Fs)   |                    | 4.096  | -   | 14.08  | MHz  |

| MCLK Frequency         | (Operational Mode 0, 384 Fs)<br>(Operational Mode 1, 192 Fs)<br>(Operational Mode 2, 96 Fs)   |                    | 6.144  | -   | 21.12  | MHz  |

| MCLK Frequency         | (Operational Mode 0, 512 Fs)<br>(Operational Mode 1, 256 Fs)<br>(Operational Mode 2 , 128 Fs) |                    | 8.192  | -   | 28.16  | MHz  |

| MCLK Frequency         | (Operational Mode 0, 768 Fs)<br>(Operational Mode 1, 384 Fs)<br>(Operational Mode 2 , 192 Fs) |                    | 12.288 | -   | 42.24  | MHz  |

| MCLK Duty Cycle        |                                                                                               |                    | 40     | 50  | 60     | %    |

| SCLK Frequency         | (Operational                                                                                  |                    | -      | -   | 256×Fs | Hz   |

| Mode 0)                | (Operational Mode 1)                                                                          |                    | -      | -   | 128×Fs | Hz   |

|                        | (Operational Mode 2)                                                                          |                    | -      | -   | 64×Fs  | Hz   |

| SCLK rising to LRCK ed | dge delay                                                                                     | t <sub>slrd</sub>  | 20     | -   | -      | ns   |

| SCLK rising to LRCK ed | dge setup time                                                                                | t <sub>slrs</sub>  | 20     | -   | -      | ns   |

| SDATA valid to SCLK ri | sing setup time                                                                               | t <sub>sdlrs</sub> | 20     | -   | -      | ns   |

| SCLK rising to SDATA I | nold time                                                                                     | t <sub>sdh</sub>   | 20     | -   | -      | ns   |

Figure 1. Serial Audio Input Timing

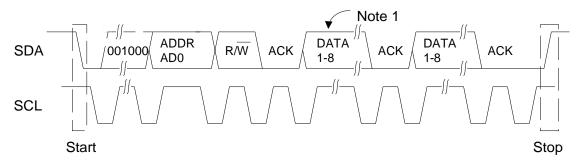

## **SWITCHING CHARACTERISTICS - CONTROL PORT**

$(T_A = 25^{\circ} \text{ C}; \text{ VD} = 5.25 \text{ V} \text{ to } 3.0 \text{ Volts}; \text{ Inputs: logic } 0 = \text{AGND}, \text{ logic } 1 = \text{VD}, \text{ C}_L = 30 \text{ pF})$

| Parameter                                              | Symbol            | Min | Max | Unit |

|--------------------------------------------------------|-------------------|-----|-----|------|

| 2 Wire Mode                                            |                   |     |     |      |

| SCL Clock Frequency                                    | f <sub>scl</sub>  | -   | 100 | KHz  |

| RST Rising Edge to Start                               | t <sub>irs</sub>  | 500 | -   | ns   |

| Bus Free Time Between Transmissions                    | t <sub>buf</sub>  | 4.7 | -   | μs   |

| Start Condition Hold Time (prior to first clock pulse) | t <sub>hdst</sub> | 4.0 | -   | μs   |

| Clock Low time                                         | t <sub>low</sub>  | 4.7 | -   | μs   |

| Clock High Time                                        | t <sub>high</sub> | 4.0 | -   | μs   |

| Setup Time for Repeated Start Condition                | t <sub>sust</sub> | 4.7 | -   | μs   |

| SDA Hold Time from SCL Falling (Note 8)                | t <sub>hdd</sub>  | 0   | -   | μs   |

| SDA Setup time to SCL Rising                           | t <sub>sud</sub>  | 250 | -   | ns   |

| Rise Time of Both SDA and SCL Lines                    | t <sub>r</sub>    | -   | 1   | μs   |

| Fall Time of Both SDA and SCL Lines                    | t <sub>f</sub>    | -   | 300 | ns   |

| Setup Time for Stop Condition                          | t <sub>susp</sub> | 4.7 | -   | μs   |

Notes: 8. Data must be held for sufficient time to bridge the 300 ns transition time of SCL.

Figure 2. 2 Wire Mode Control Port Timing

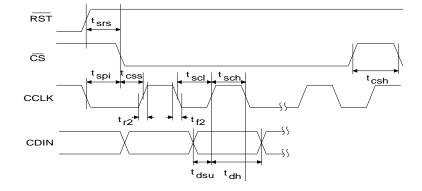

## **SWITCHING CHARACTERISTICS - CONTROL PORT**

(T<sub>A</sub> = 25° C; VD = 5.25 V to 3.0 Volts; Inputs: logic 0 = AGND, logic 1 = VD, C<sub>L</sub> = 30 pF)

| Parameter                          |           | Symbol            | Min | Max | Unit |

|------------------------------------|-----------|-------------------|-----|-----|------|

| SPI Mode                           |           |                   |     |     |      |

| CCLK Clock Frequency               |           | f <sub>sclk</sub> | -   | 6   | MHz  |

| RST Rising Edge to CS Falling      |           | t <sub>srs</sub>  | 500 | -   | ns   |

| CCLK Edge to CS Falling            | (Note 9)  | t <sub>spi</sub>  | 500 | -   | ns   |

| CS High Time Between Transmissions |           | t <sub>csh</sub>  | 1.0 | -   | μs   |

| CS Falling to CCLK Edge            |           | t <sub>css</sub>  | 20  | -   | ns   |

| CCLK Low Time                      |           | t <sub>scl</sub>  | 66  | -   | ns   |

| CCLK High Time                     |           | t <sub>sch</sub>  | 66  | -   | ns   |

| CDIN to CCLK Rising Setup Time     |           | t <sub>dsu</sub>  | 40  | -   | ns   |

| CCLK Rising to DATA Hold Time      | (Note 10) | t <sub>dh</sub>   | 15  | -   | ns   |

| Rise Time of CCLK and CDIN         | (Note 11) | t <sub>r2</sub>   | -   | 100 | ns   |

| Fall Time of CCLK and CDIN         | (Note 11) | t <sub>f2</sub>   | -   | 100 | ns   |

| CCLK Falling to CDOUT valid        |           | t <sub>ov</sub>   | 45  |     | ns   |

Notes: 9.  $t_{spi}$  only needed before first falling edge of  $\overline{CS}$  after  $\overline{RST}$  rising edge.  $t_{spi} = 0$  at all other times.

- 10. Data must be held for sufficient time to bridge the transition time of CCLK.

- 11. For  $F_{SCK} < 1 \text{ MHz}$

Figure 3. SPI Control Port Timing

## 2. TYPICAL CONNECTION DIAGRAM

Figure 4. Typical Connection Diagram

#### 3. REGISTER DESCRIPTION

#### 3.1 MODE CONTROL REGISTER (ADDRESS 01H)

| 7   | 6    | 5  | 4  | 3  | 2  | 1  | 0   |

|-----|------|----|----|----|----|----|-----|

| CAL | MUTE | M4 | M3 | M2 | M1 | MO | PDN |

| 0   | 0    | 0  | 0  | 0  | 0  | 0  | 0   |

4.11 Differential DC offset calibration (CAL)

Default = 0

0 - Disabled

1 - Enabled

#### Function:

Enabling this function will initiate a calibration to minimize the differential DC offset. This function will be automatically reset following completion of the calibration sequence.

#### 4.12 Soft Mute (MUTE)

Default = 0 0 - Disabled 1 - Enabled

#### Function:

The analog outputs will ramp to a muted state when enabled. The ramp requires 1152 left/right clock cycles in Operational Mode 0, 2304 cycles in Operational Mode 1 and 4608 cycles in Operational Mode 2. The bias voltage on the outputs will be retained and MUTEC will go low at the completion of the ramp period.

The analog outputs will ramp to a normal state when this function transitions from the enabled to disabled state. The ramp requires 1152 left/right clock cycles in Operational Mode 0, 2304 cycles in Operational Mode 1 and 4608 cycles in Operational Mode 2. The MUTEC will go high immediately on disabling of MUTE.

#### 4.13 Mode Select (M4-M0)

#### Default = 00000

#### Function:

The Mode Select pins determine the operational mode of the device as detailed in Tables 4-7. The options include:

Selection of the Digital Interface Format which determines the required relationship between the Left/Right clock, serial clock and serial data as detailed in Figures 20-23

Selection of the standard 15  $\mu$ s/50  $\mu$ s digital de-emphasis filter response, Figure 28, which requires reconfiguration of the digital filter to maintain the proper filter response for 32, 44.1 or 48 kHz sample rates.

Selection of the appropriate operational clocking mode to match the input sample rates.

#### 4.14 Power Down (PDN)

Default = 1

- 0 Disabled

- 1 Enabled

#### Function:

The analog and digital sections will be placed into a power-down mode when this function is enabled. This bit must be cleared to resume normal operation.

## 4. PIN DESCRIPTION

|                  |               | Γ | •     | ]         |              |                              |

|------------------|---------------|---|-------|-----------|--------------|------------------------------|

| Reset            | <u>RST</u>    |   | 1 28  |           | VREF         | Voltage Reference            |

| See Description  | M4(AD0/CS)    |   | 2 27  |           | FILT+        | Reference Filter             |

| See Description  | M3(AD1/CDIN)  |   | 3 26  |           | FILT-        | Reference Ground             |

| See Description  | M2(SCL/CCLK)  |   | 4 25  | $\square$ | CMOUT        | Common ModeS Voltage         |

| See Description  | M0(SDA/CDOUT) |   | 5 24  |           | AOUTL-       | Differential Output          |

| Digital Ground   | DGND          |   | 6 23  |           | AOUTL+       | Differential Output          |

| Digital Power    | VD            |   | 7 22  |           | VA           | Analog Power                 |

| Digital Power    | VD            |   | 8 21  |           | AGND         | Analog Ground                |

| Digital Ground   | DGND          |   | 9 20  |           | AOUTR+       | Differential Output          |

| Master Clock     | MCLK          |   | 10 19 |           | AOUTR-       | Differential Output          |

| Serial Clock     | SCLK          |   | 11 18 |           | AGND         | Analog Ground                |

| Left/Right Clock | LRCK          |   | 12 17 |           | <b>MUTEC</b> | Mute Control                 |

| Serial Data      | SDATA         |   | 13 16 | $\square$ | C/H          | Control port/Hardware select |

| See Description  | M1            |   | 14 15 |           | MUTE         | Soft Mute                    |

|                  |               |   |       | ]         |              |                              |

| RST  | 1    | <b>Reset</b> ( <i>Input</i> ) - The device enters a low power mode and all internal state machines registers are reset when low. When high, the device will be in a normal operation mode. |

|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DGND | 6, 9 | Digital Ground (Input) - Digital ground reference.                                                                                                                                         |

| VD   | 7, 8 | Digital Power (Input) - Digital power supply. Typically 3.0 to 5.0 VDC.                                                                                                                    |

MCLK

**Master Clock** (*Input*) - The master clock frequency must be either 256x, 384x, 512x or 768x the input sample rate in Operational Mode 0; either 128x, 192x 256x or 384x the input sample rate in Operational Mode 1; or 64x, 96x 128x or 192x the input sample rate in Operational Mode 2. Tables 4-6 illustrate the standard audio sample rates and the required master clock frequencies.

| Sample Rate | MCLK (MHz) |         |         |         |  |  |  |

|-------------|------------|---------|---------|---------|--|--|--|

| (kHz)       | 256x       | 384x    | 512x    | 768x    |  |  |  |

| 32          | 8.1920     | 12.2880 | 16.3840 | 24.5760 |  |  |  |

| 44.1        | 11.2896    | 16.9344 | 22.5792 | 33.8688 |  |  |  |

| 48          | 12.2880    | 18.4320 | 24.5760 | 36.8640 |  |  |  |

Table 1. Operational Mode 0 (16 to 55 kHz sample rates) Common Clock Frequencies

| Sample Rate | MCLK (MHz) |         |         |         |  |  |

|-------------|------------|---------|---------|---------|--|--|

| (kHz)       | 128x       | 192x    | 256x    | 384x    |  |  |

| 48          | 6.1440     | 8.1920  | 12.2880 | 16.3840 |  |  |

| 64          | 8.1920     | 12.2880 | 16.3840 | 24.5760 |  |  |

| 88.2        | 11.2896    | 16.9344 | 22.5792 | 33.8688 |  |  |

| 96          | 12.2880    | 18.4320 | 24.5760 | 36.8640 |  |  |

Table 2. Operational Mode 1 (45 to 105 kHz sample rates) Common Clock Frequencies

| Sample Rate | MCLK (MHz) |         |         |         |  |  |

|-------------|------------|---------|---------|---------|--|--|

| (kHz)       | 64x        | 96x     | 128x    | 192x    |  |  |

| 176.4       | 11.2896    | 16.9344 | 22.5792 | 33.8688 |  |  |

| 192         | 12.2880    | 18.4320 | 24.5760 | 36.8640 |  |  |

Table 3. Operational Mode 2 (95 to 200 kHz sample rates) Common Clock Frequencies

| SCLK  | 11 | <b>Serial Clock</b> ( <i>Input</i> ) - Clocks individual bits of serial data into the SDATA pin. The required relationship between the Left/Right clock, serial clock and serial data is defined by either the Mode Control Byte in Control Port Mode or the M0 - M4 pins in Hardware Mode. The options are detailed in Figures 20-23.                                                                                                                                                                                                                                                   |

|-------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LRCK  | 12 | <b>Left/Right Clock</b> <i>(Input)</i> - The Left/Right clock determines which channel is currently being input on the serial audio data input, SDATA. The frequency of the Left/Right clock must be at the input sample rate. Audio samples in Left/Right sample pairs will be simultaneously output from the digital-to-analog converter whereas Right/Left pairs will exhibit a one sample period difference. The required relationship between the Left/Right clock, serial clock and serial data is defined by the Mode Control Byte and the options are detailed in Figures 20-23. |

| SDATA | 13 | <b>Serial Audio Data</b> <i>(Input)</i> - Two's complement MSB-first serial data is input on this pin. The data is clocked into SDATA via the serial clock and the channel is determined by the Left/Right clock. The required relationship between the Left/Right clock, serial clock and serial data is defined by the Mode Control Byte and the options are detailed inin Figures 20-23.                                                                                                                                                                                              |

| MUTE<br>C/H                                  | 15                | <ul> <li>Soft Mute (<i>Input</i>) - The analog outputs will ramp to a muted state when enabled. The ramp requires 1152 left/right clock cycles in Operational Mode 0, 2304 cycles in Operational Mode 1 and 4608 cycles in Operational Mode 2. The bias voltage on the outputs will be retained and MUTEC will go active at the completion of the ramp period.</li> <li>The analog outputs will ramp to a normal state when this function transitions from the enabled to disabled state. The ramp requires 1152 left/right clock cycles in Operational Mode 2. The MUTEC will release immediately on setting MUTE = 1. The converter analog outputs will mute when enabled. The bias voltage on the outputs will be retained and MUTEC will go active during the mute period</li> <li>Control Port / Hardware Mode Select (<i>Input</i>) - Determines if the device will operate in either the Hardware Mode or Control Port Mode.</li> </ul> |

|----------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MUTEC                                        | 17                | <b>Mute Control</b> ( <i>Output</i> ) - The Mute Control pin goes low during power-up initializa-<br>tion, reset, muting, master clock to left/right clock frequency ratio is incorrect or<br>power-down. This pin is intended to be used as a control for an external mute circuit<br>to prevent the clicks and pops that can occur in any single supply system. Use of<br>Mute Control is not mandatory but recommended for designs requiring the absolute<br>minimum in extraneous clicks and pops.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AGND                                         | 18, 21            | Analog Ground (Inputs) - Analog ground reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AOUTR- , AOUTR+<br>AOUTL- , AOUTL+           | 19, 20,<br>23, 24 | <b>Differential Analog Outputs</b> ( <i>Outputs</i> ) - The full scale differential analog output level is specified in the Analog Characteristics specifications table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VA                                           | 22                | <b>Analog Power</b> ( <i>Input</i> ) - Power for the analog and reference circuits. Typically 5.5 VDC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CMOUT                                        | 25                | <b>Common Mode Voltage</b> ( <i>Output</i> ) - Filter connection for internal bias voltage, typ-<br>ically 50% of VREF. Capacitors must be connected from CMOUT to analog<br>ground, as shown in the Typical Connection Diagram. CMOUT has a typical<br>source impedence of 25 k $\Omega$ and any current drawn from this pin will alter device<br>performance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| FILT-                                        | 26                | Reference Ground ( <i>Input</i> ) - Ground reference for the internal sampling circuits.<br>Must be connected to analog ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| FILT+                                        | 27                | <b>Reference Filter</b> ( <i>Output</i> ) - Positive reference for internal sampling circuits. Exter-<br>nal capacitors are required from FILT+ to analog ground, as shown in the Typical<br>Connection Diagram. The recommended values will typically provide 60 dB of<br>PSRR at 1 kHz and 40 dB of PSRR at 120 Hz. FILT+ is not intended to supply<br>external current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VREF                                         | 28                | Voltage Reference Input (Input) - Analog voltage reference. Typically 5.5 VDC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>M0, M1, M2, M3, M4</b><br>(Hardware Mode) | 2, 3, 4,<br>5,14  | <b>Mode Select</b> <i>(Inputs)</i> - The Mode Select pins determine the operational mode of the device as detailed in Tables 4-7. The options include;<br>Selection of the Digital Interface Format which determines the required relationship between the Left/Right clock, serial clock and serial data as detailed in Figures 20-23Selection of the standard 15 $\mu$ s/50 $\mu$ s digital de-emphasis filter response, Figure 28, which requires reconfiguration of the digital filter to maintain the proper filter response for 32, 44.1 or 48 kHz sample rates.<br>Selection of the appropriate clocking mode to match the input sample rates.                                                                                                                                                                                                                                                                                          |

| AD0 / CS<br>(Control Port Mode)              | 2                 | Address Bit 0 / Chip Select ( <i>Input</i> ) - In 2 wire mode, AD0 is a chip address bit.<br>CS is used to enable the control port interface in SPI mode. The device will enter<br>the SPI mode at anytime a high to low transition is detected on this pin. Once the<br>device has entered the SPI mode, it will remain until either the part is reset or<br>undergoes a power-down cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AD1/CDIN<br>(Control Port Mode)  | 3  | Address Bit 1 / Control Data Input ( <i>Input</i> ) - In 2 Wire Mode, AD1 is a chip address bit. CDIN is the control data input line for the control port interface in SPI mode.                             |

|----------------------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCL/CCLK<br>(Control Port Mode)  | 4  | Serial Control Interface Clock ( <i>Input</i> ) - In 2 Wire Mode, SCL clocks the serial control data into or from SDA/CDOUT.<br>In SPI mode, CCLK clocks the serial data into AD1/CDIN and out of SDA/CDOUT. |

| SDA/CDOUT<br>(Control Port Mode) | 5  | <b>Serial Control Data I/O</b> ( <i>Input/Output</i> ) - In 2 Wire Mode, SDA is a data input/output. CDOUT is the control data output for the control port interface in SPI mode.                            |

| M1<br>(Control Port Mode)        | 14 | <b>Mode Select</b> ( <i>Input</i> ) - This pin is not used in Control Port Mode and must be termi-<br>nated to ground.                                                                                       |

## 5. APPLICATIONS

#### 5.1 Recommended Power-up Sequence

- 1) Hold RST high until the power supplies, master clock, and left/right clock are stable.

- 2) Bring  $\overline{\text{RST}}$  high.

## 6. CONTROL PORT INTERFACE

The control port is used to load all the internal settings of the CS43122. The operation of the control port may be completely asynchronous to the audio sample rate. However, to avoid potential interference problems, the control port pins should remain static if no operation is required.

The control port has 2 modes: SPI and "2 wire", with the CS43122 operating as a slave device in both modes. If 2 wire operation is desired,  $AD0/\overline{CS}$  should be tied to VD or DGND. If the CS43122 ever detects a high to low transition on  $AD0/\overline{CS}$  after power-up, SPI mode will be selected.

### 6.1 SPI Mode

In SPI mode,  $\overline{CS}$  is the CS43122 chip select signal, CCLK is the control port bit clock, CDIN is the input data line from the microcontroller, CDOUT is the data output and the chip address is 0010000. The data is clocked on the rising edge of CCLK.

Figure 5 shows the operation of the control port in SPI mode. To write to a register, bring  $\overline{CS}$  low. The first 7 bits on CDIN form the chip address, and must be 0010000. The eighth bit is a read/write indicator (R/W). The next 8 bits form the Memory Address Pointer (MAP), which is set to 01h. The

next 8 bits are the data which will be placed into the register designated by the MAP.

## 6.2 2 Wire Mode

In 2 Wire Mode, SDA is a bi-directional data line. Data is clocked into and out of the part by the clock, SCL, with the clock to data relationship as shown in Figure 2. There is no  $\overline{CS}$  pin. Pins AD0 and AD1 form the partial chip address and should be tied to VD or DGND as required. The 7-bit address field, which is the first byte sent to the CS43122, must be 00100(AD1)(AD0) where (AD1) and (AD0) match the setting of the AD0 and AD1 pins. The eighth bit of the address byte is the  $R/\overline{W}$  bit (high for a read, low for a write). If the operation is a write, the next byte is the Memory Address Pointer, MAP, which selects the register to be read or written. The MAP is then followed by the data to be written. If the operation is a read, then the contents of the register pointed to by the MAP will be output after the chip address.

## 6.3 Memory Address Pointer (MAP)

|   | 7    | 6        | 5        | 4        | 3        | 2    | 1    | 0    |

|---|------|----------|----------|----------|----------|------|------|------|

| Ī | INCR | Reserved | Reserved | Reserved | Reserved | MAP2 | MAP1 | MAP0 |

| Ī | 0    | 0        | 0        | 0        | 0        | 0    | 0    | 1    |

INCR (Auto MAP Increment Enable) Default = '0'

0 - Disabled

1 - Enabled

MAP0-2 (Memory Address Pointer) Default = '001'

Figure 5. Control Port Timing, SPI mode

Note: If operation is a write, this byte contains the Memory Address Pointer, MAP.

#### Figure 6. Control Port Timing, 2 wire Mode

| M4 | M1<br>(DIF1) | M0<br>(DIF0) | DESCRIPTION                         | FORMAT | FIGURE |

|----|--------------|--------------|-------------------------------------|--------|--------|

| 0  | 0            | 0            | Left Justified, up to 24-bit data   | 0      | 20     |

| 0  | 0            | 1            | I <sup>2</sup> S, up to 24-bit data | 1      | 21     |

| 0  | 1            | 0            | Right Justified, 16-bit Data        | 2      | 22     |

| 0  | 1            | 1            | Right Justified, 24-bit Data        | 3      | 23     |

Table 4. Operational Mode 0 (16 to 55 kHz) Digital Interface Format Options

| M4 | M3     | M2     | DESCRIPTION          | FIGURE |

|----|--------|--------|----------------------|--------|

|    | (DEM1) | (DEM0) |                      |        |

| 0  | 0      | 0      | 32 kHz De-Emphasis   | 19     |

| 0  | 0      | 1      | 44.1 kHz De-Emphasis | 19     |

| 0  | 1      | 0      | 48 kHz De-Emphasis   | 19     |

| 0  | 1      | 1      | De-Emphasis Disabled | -      |

Table 5. Operational Mode 0 (16 to 55 kHz) De-Emphasis Options

| M4 | M3 | M2 | M1 | MO | DESCRIPTION                                  |

|----|----|----|----|----|----------------------------------------------|

| 1  | 1  | 1  | 0  | 0  | Left Justified up to 24-bit data, Format 0   |

| 1  | 1  | 1  | 0  | 1  | I <sup>2</sup> S up to 24-bit data, Format 1 |

| 1  | 1  | 1  | 1  | 0  | Right Justified 16-bit data, Format 2        |

| 1  | 1  | 1  | 1  | 1  | Right Justified 24-bit data, Format 3        |

Table 6. Operational Mode 1 (45 to 105 kHz) Sample Rate Mode Options

| M4 | M3 | M2 | M1 | MO | DESCRIPTION                                  |

|----|----|----|----|----|----------------------------------------------|

| 1  | 1  | 0  | 0  | 0  | Left Justified up to 24-bit data, Format 0   |

| 1  | 1  | 0  | 0  | 1  | I <sup>2</sup> S up to 24-bit data, Format 1 |

| 1  | 1  | 0  | 1  | 0  | Right Justified 16-bit data, Format 2        |

| 1  | 1  | 0  | 1  | 1  | Right Justified 24-bit data, Format 3        |

Table 7. Operational Mode 2 (95 to 200 kHz) Sample Rate Mode Options

Figure 7. Operational Mode 0 Transition Band

Figure 9. Operational Mode 0 Transition Band

Figure 11. Operational Mode 0 Stopband

Figure 13. Operational Mode 0 Transition Band

Figure 8. Operational Mode 0 Stopband Rejection

Figure 10. Operational Mode 0 Frequency Response

Figure 12. Operational Mode 0 Transition Band

Figure 14. Operational Mode 0 Frequency Response

-1

0.4

Figure 15. Operational Mode 2 Stopband Rejection

Figure 16. Operational Mode 2 Transition Band

Figure 18. Operational Mode 2 Frequency Response

Figure 17. Operational Mode 2 Transition Band

Figure 19. De-Emphasis Curve

Figure 22. Format 2, Right Justified, 16-Bit Data

### 7. PARAMETER DEFINITIONS

#### Total Harmonic Distortion + Noise (THD+N)

The ratio of the rms value of the signal to the rms sum of all other spectral components over the specified bandwidth (typically 10 Hz to 20 kHz), including distortion components. Expressed in decibels.

#### **Dynamic Range**

The ratio of the full scale rms value of the signal to the rms sum of all other spectral components over the specified bandwidth. Dynamic range is a signal-to-noise measurement over the specified bandwidth made with a -60 dBFS signal. 60 dB is then added to the resulting measurement to refer the measurement to full scale. This technique ensures that the distortion components are below the noise level and do not effect the measurement. This measurement technique has been accepted by the Audio Engineering Society, AES17-1991, and the Electronic Industries Association of Japan, EIAJ CP-307.

#### Interchannel Isolation

A measure of crosstalk between the left and right channels. Measured for each channel at the converter's output with all zeros to the input under test and a full-scale signal applied to the other channel. Units in decibels.

#### **Interchannel Gain Mismatch**

The gain difference between left and right channels. Units in decibels.

#### **Gain Error**

The deviation from the nominal full scale analog output for a full scale digital input.

#### **Gain Drift**

The change in gain value with temperature. Units in ppm/°C.

#### 8. REFERENCES

- 1) "How to Achieve Optimum Performance from Delta-Sigma A/D & D/A Converters" by Steven Harris. Paper presented at the 93rd Convention of the Audio Engineering Society, October 1992.

- 2) CDB43122 Evaluation Board Datasheet

## 9. PACKAGE DIMENSIONS

| -   | ► e <del>&lt;</del> |        | A1_1  |             |       |       |  |  |

|-----|---------------------|--------|-------|-------------|-------|-------|--|--|

|     |                     | INCHES |       | MILLIMETERS |       |       |  |  |

| DIM | MIN                 | NOM    | MAX   | MIN         | NOM   | MAX   |  |  |

| А   | 0.093               | 0.098  | 0.104 | 2.35        | 2.50  | 2.65  |  |  |

| A1  | 0.004               | 0.008  | 0.012 | 0.10        | 0.20  | 0.30  |  |  |

| b   | 0.013               | 0.017  | 0.020 | 0.33        | 0.42  | 0.51  |  |  |

| С   | 0.009               | 0.011  | 0.013 | 0.23        | 0.28  | 0.32  |  |  |

| D   | 0.697               | 0.705  | 0.713 | 17.70       | 17.90 | 18.10 |  |  |

| E   | 0.291               | 0.295  | 0.299 | 7.40        | 7.50  | 7.60  |  |  |

| е   | 0.040               | 0.050  | 0.060 | 1.02        | 1.27  | 1.52  |  |  |

| Н   | 0.394               | 0.407  | 0.419 | 10.00       | 10.34 | 10.65 |  |  |

| L   | 0.016               | 0.026  | 0.050 | 0.40        | 0.65  | 1.27  |  |  |

| ×   | 0°                  | 4°     | 8°    | 0°          | 4°    | 8°    |  |  |

JEDEC #: MS-013

Controling Dimension is Millimeters

# • Notes •