# Honeywell

#### Preliminary

## 31.0 dB, DC-4GHz, 5 Bit **Serial Digital Attenuator**

#### **Features**

- Very Low DC Power Consumption •

- Attenuation In Steps From 1 dB To 31 dB •

- Single Or Dual Power Supply Voltages

- Serial Data Interface

- 50 Ohm Compatible Impedance •

- Space Saving LPCC<sup>™</sup> Surface Mount Packaging

### **Product Description**

The Honeywell HRF-AT4521 is a 5-bit digital attenuator that is ideal for use in broadband communication system applications that require accuracy, speed and low power consumption. The HRF-AT4521 is manufactured with Honeywell's patented Silicon On Insulator (SOI) CMOS manufacturing technology, which provides the performance of GaAs with the economy and integration capabilities of conventional CMOS.

#### HRF-AT4521 in LPCC<sup>™</sup> Package

| Parameter                           | Test Condition                                                              | Frequency    | Minimum                        | Typical             | Maximum | Units |

|-------------------------------------|-----------------------------------------------------------------------------|--------------|--------------------------------|---------------------|---------|-------|

| Insertion Loss                      |                                                                             | DC – 0.5 GHz |                                | 1.8                 |         | dB    |

|                                     |                                                                             | 2.0 GHz      |                                | 2.8                 |         | dB    |

|                                     |                                                                             | 3.0 GHz      |                                |                     |         | dB    |

|                                     |                                                                             | 4.0 GHz      |                                |                     |         | dB    |

| 1dB Compression                     | VSS = 0V, Input Power                                                       | DC – 2.0 GHz |                                | 24                  |         | dBm   |

| 1dB Compression                     | VSS = - VDD, Input Power                                                    | DC – 2.0 GHz |                                | 29                  |         | dBm   |

| Input IP3                           | VSS = 0V Two-tone inputs<br>Up To +5 dBm @ 0 dBm<br>Attenuation             | DC – 2.0 GHz |                                | 38                  |         | dBm   |

| nput IP3                            | $V_{ss} = - V_{DD}$<br>Two-tone inputs Up To + 5<br>dBm @ 0 dBm Attenuation | DC – 2.0 GHz |                                | >38                 |         | dBm   |

| Return Loss*                        | Any Combination of Bits                                                     | DC - 4.0 GHz |                                | 11                  |         | dB    |

| Attenuation Accuracy                | All attenuation states                                                      | DC – 1.0 GHz | +/-(0.3 + 3% of programmed IL) |                     | dB      |       |

| 2                                   | All attenuation states                                                      | 2.0 GHz      |                                | 0.3 + 3% of program |         | dB    |

|                                     | All attenuation states                                                      | 3.0 GHz      |                                | 0.4 + 4% of program |         | dB    |

|                                     | All attenuation states                                                      | 4.0 GHz      | +/-(0.5 + 6% of programmed IL) |                     | dB      |       |

| Trise, Tfall*                       | 10% To 90%                                                                  |              |                                | TBD                 |         | nS    |

| Ton, Toff (Tpd)                     | 50% Cntl To 90%/10%RF                                                       |              |                                |                     |         | nS    |

| Transients                          | In-Band                                                                     |              |                                |                     |         | mV    |

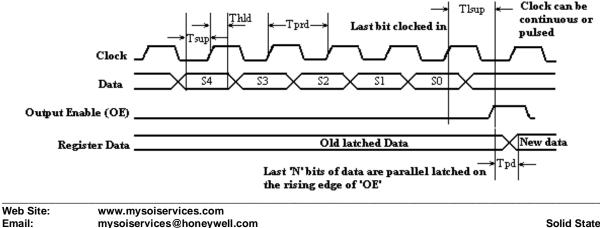

| T clock Period (Tprd)*              | T high / T low = $\frac{1}{2}$ minimum clock period                         |              | 50                             |                     |         | nS    |

| T data set up (Tsup)*               | Set up to rising edge of clock                                              |              | 5                              |                     |         | nS    |

| T data hold (Thld)*                 | Data hold after rising edge of clock                                        |              | 2                              |                     |         | nS    |

| T latch set up (Tlsup)*             | TIsup)* Data set up to falling edge of OE                                   |              | 5                              |                     |         | nS    |

| 01uF Decoupling Capaci<br>3v design | itors Required On Power Supply                                              | Rails.       |                                |                     |         |       |

## Electrical Cracifications @ . 25°C

2002 4521W Published June 2002 Page 1

mysoiservices@honeywell.com

Solid State Electronics Center 12001 State Highway 55 Plymouth, Minnesota 55441-4799 1-800-323-8295

Email:

Preliminary

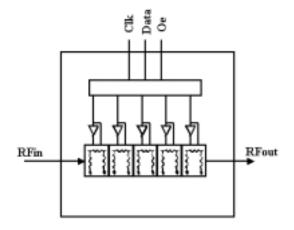

### **Functional Schematic**

### DC Electrical Specifications @ + 25°C

| Parameter                            | Minimum          | Typical | Maximum         | Units |

|--------------------------------------|------------------|---------|-----------------|-------|

| V <sub>DD</sub>                      | 3.3 <sup>1</sup> | 5.0     |                 | V     |

| V <sub>SS</sub>                      |                  |         | -5.0            | V     |

| I <sub>DD</sub> Power Supply Current |                  |         | 2               | mA    |

| CMOS Logic level (0)                 | 0                |         | 0.8             | V     |

| CMOS Logic level (1)                 | $V_{DD} - 0.8$   |         | V <sub>DD</sub> | V     |

| Input Leakage Current                |                  |         | 10              | uA    |

Note 1, the performance curves are for Vdd = +5.0 + -10%

## Absolute Maximum Ratings<sup>2</sup>

| Parameter             | Absolute Maximum                                     | Units     |  |

|-----------------------|------------------------------------------------------|-----------|--|

| Input Power           | + 35                                                 | dBm       |  |

| V <sub>DD</sub>       | +6.0                                                 | V         |  |

| V <sub>SS</sub>       | -5.5                                                 | V         |  |

| ESD Voltage           | 400                                                  | V         |  |

| Operating Temperature | -40 To +85                                           | Degrees C |  |

| Storage Temperature   | -65 To +125                                          | Degrees C |  |

| Digital Inputs        | V <sub>DD</sub> +0.6 max to V <sub>SS</sub> -0.6 min | V         |  |

Note 2) Operation of this Device beyond any of these parameters may cause permanent damage.

Latch-Up: Unlike conventional CMOS digital attenuators, Honeywells' HRF-AT4521 is immune to latch-up.

**ESD Protection:** Although the HRF-AT4521 contains ESD protection circuitry on all digital inputs, conventional precautions should be taken to ensure that the Absolute Maximum Ratings are not exceeded.

| Web Site:  | www.mysoiservices.com       |  |  |  |

|------------|-----------------------------|--|--|--|

| Email:     | mysoiservices@honeywell.com |  |  |  |

| 2002 4521W | Published June 2002 Page 2  |  |  |  |

Preliminary

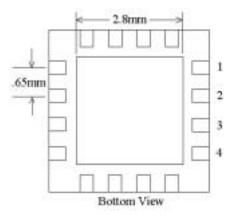

### **Package Outline Drawing**

This package conforms to the LPCC<sup>1M</sup> 4 x 4 mm 16 lead body dimensions. See ASAT LPCC Marketing Outline Dwg. # DGMJ00004 Latest Rev. at <u>http://www.asat.com</u> for additional dimensional information.

### **Pin Configuration**

| Pin | Function | Pin | Function       |

|-----|----------|-----|----------------|

| 1   | VDD      | 9   | GROUND         |

| 2   | GROUND   | 10  | RF OUTPUT      |

| 3   | RF INPUT | 11  | GROUND         |

| 4   | GROUND   | 12  | VSS            |

| 5   | GROUND   | 13  | DIGITAL GROUND |

| 6   | GROUND   | 14  | OE             |

| 7   | GROUND   | 15  | CLK            |

| 8   | GROUND   | 16  | DATA           |

#### **Serial Data Load**

Serial data is shifted into the register on the rising edge of clock, MSB first. The OE falling edge must occur prior to any additional rising clock edges. See the Electrical Spec Table for AC parameters.

Honeywell Solid State Electronics Center 12001 State Highway 55 Plymouth, Minnesota 55441-4799 1-800-323-8295

Published June 2002 Page 3

2002 4521W

Preliminary

### Truth Table

| S4 | S3 | S2 | S1 | S0 | Output          |

|----|----|----|----|----|-----------------|

| 0  | 0  | 0  | 0  | 0  | Reference Input |

| 0  | 0  | 0  | 0  | 1  | 1 dB            |

| 0  | 0  | 0  | 1  | 0  | 2 dB            |

| 0  | 0  | 1  | 0  | 0  | 4 dB            |

| 0  | 1  | 0  | 0  | 0  | 8 dB            |

| 1  | 0  | 0  | 0  | 0  | 16 dB           |

| 1  | 1  | 1  | 1  | 1  | 31 dB           |

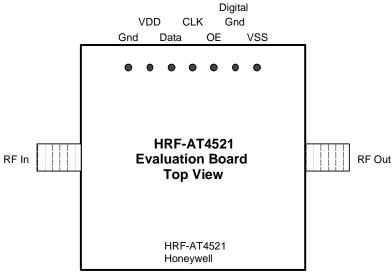

### **Evaluation Circuit Board**

Honeywell's evaluation board provides an easy to use method of evaluating the RF performance of our attenuator. Simply connect power, DC and RF signals to be measuring switch performance in less than 10 minutes.

**HRF-AT4521 Evaluation Board**

#### **Evaluation Circuit Board Layout Design Details**

| Item           | Description                                                    |  |  |

|----------------|----------------------------------------------------------------|--|--|

| PCB            | Impedance Matched Multi-Layer FR4                              |  |  |

| Attenuator     | HRF-AT4521 Digital Attenuator                                  |  |  |

| Chip Capacitor | Panasonic Model ECU-E1C103KBQ Capacitor, .01uf 0402 10% 16V    |  |  |

| RF Connector   | Johnson Connectors Model 142-0701-801 SMA RF Coaxial Connector |  |  |

| DC Pin         | Mil-Max Model 800-10-064-10-001 Header Pins                    |  |  |

Web Site:

www.mysoiservices.com

Email:

mysoiservices@honeywell.com

2002 4521W

Published June 2002

Page 4

#### Preliminary

### **Evaluation Circuit Board Connections**

"0" = CMOS Low, "1" = CMOS High

## **Performance Curves**

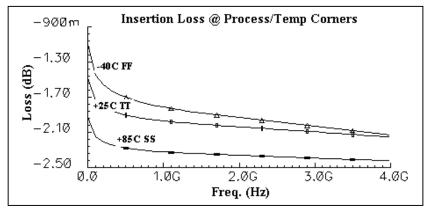

#### Insertion Loss

This Insertion Loss curve represents the Min/Max conditions for the "0" pass state versus all processing and temperature conditions. The Min case is at -40C with the "Fast" processing conditions. The Max case is at +85C with the "Slow" processing conditions. All other combinations fall within that band. The typical 25C case is labeled +25C TT.

Web Site:

www.mysoiservices.com

Email:

mysoiservices@honeywell.com

2002 4521W

Published June 2002

Page 5

#### Preliminary

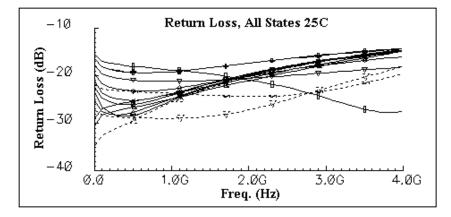

#### **Return Loss**

This Return Loss set of curves represents the combination of all Return Loss cases for all attenuation settings. All cases are better than -14dB Return Loss at 4GHz.

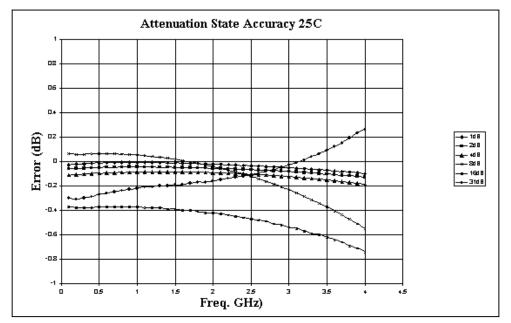

#### Attenuation State Accuracy

The Attenuation Accuracy curve with vertical axis of +/- 1dB shows all states better than +/- 0.5dB to 2GHz and better than +/- 0.8dB to 4GHz.

Web Site:

www.mysoiservices.com

Email:

mysoiservices@honeywell.com

2002 4521W

Published June 2002

Page 6

Honeywell

#### Preliminary

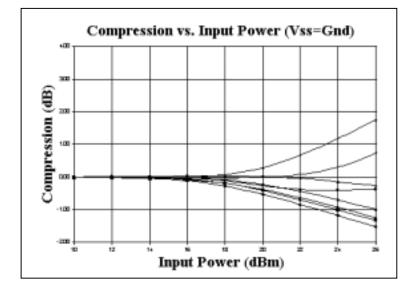

#### Compression

The P1dB curve shows all states with a P1dB compression at approximately 23dB input power. The conditions for this curve are Vdd = +5.0v and Vss = 0v. For higher P1dB compression values, supply Vss with a negative voltage as shown in the next curve.

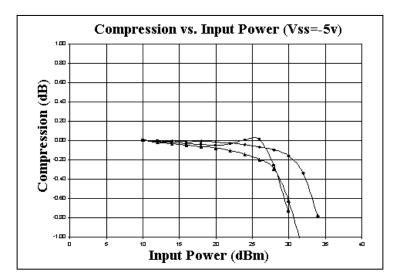

The P1dB curve shows all states with a P1dB compression at approximately 31dB input power. The conditions for this curve are Vdd = +5.0v and Vss = -5.0v.

Web Site:

www.mysoiservices.com

Email:

mysoiservices@honeywell.com

2002 4521W

Published June 2002

Page 7

Honeywell

Preliminary

## **Ordering Information**

| Ordering Number | Delivery Method                            | Units Per Shipment                 |

|-----------------|--------------------------------------------|------------------------------------|

| HRF-AT4521-B    | In Chip Tubes                              | Customer Specific, Usually Minimum |

|                 |                                            | Of 50 Per Chip Tube                |

| HRF-AT4521-TR   | On Tape And Reel <sup>3</sup>              | Customer Specific                  |

| HRF-AT4521-E    | On Individual Engineering Evaluation Board | One Board Per Box                  |

(Note 3) Call Honeywell for details

LPCC<sup>™</sup> is a registered Trademark of ASAT Ltd.

Honeywell reserves the right to make changes to improve reliability, function or design. Honeywell does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.