### MIC5316

Low Voltage Dual 300mA LDO with Power on Reset and Voltage Select

### **General Description**

The MIC5316 is a high performance, dual low input voltage, low dropout regulator with Power On Reset (POR) and voltage select. Major features include two 300mA LDOs, input voltage down to 1.7V, ultra low drop out of 85mV at full load, Power on Reset, and voltage select. Each LDO has its own low voltage input for system flexibility. The low input voltages and low drop out operation provides high efficiency by reducing the input to output voltage step which minimizes the regulator power loss. Voltage select is incorporated into the second output, which reduces the output voltage to further save power while in stand-by mode. An adjustable delay time POR output is provided for the second regulator for design flexibility.

Ideal for battery operated applications; the MIC5316 offers 1% accuracy and low ground current to increase light load efficiency. The MIC5316 can also be put into a zero-offmode current state, drawing virtually no current when disabled.

The MIC5316 is available in fixed output voltages in the 12-pin 2.5mm x 2.5mm Thin MLF<sup>®</sup> leadless package.

Data sheets and support documentation can be found on Micrel's web site at: www.micrel.com.

#### **Features**

- 300mA output current for each LDO

- Dual low voltage regulator inputs: 1.7V to 5.5V

- Low output voltage range: 0.8V to 2.0V

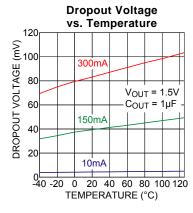

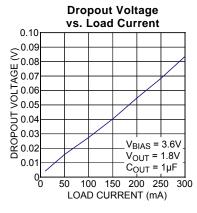

- Ultra-low dropout voltage of 85mV @ 300mA

- · Voltage select function

- Power On Reset output with adjustable delay

- Stable with 1µF ceramic output capacitors

- Very fast transient response

- Thermal shutdown and current limit protection

- Tiny 12-pin 2.5mm x 2.5mm Thin MLF<sup>®</sup> package

### **Applications**

- Mobile Phones

- · GPS and Navigation Devices

- Portable Media Players

- Digital still and video cameras

- PDAs

- Portable electronics

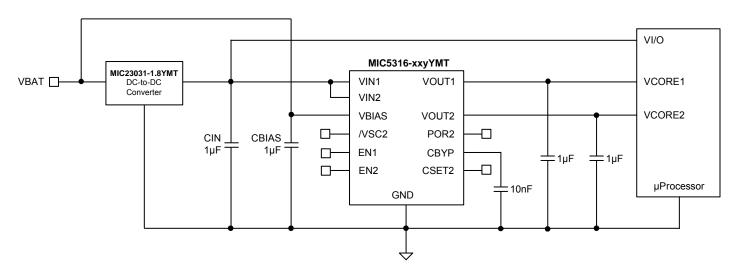

## **Typical Application**

MLF and MicroLeadFrame are registered trademarks of Amkor Technology, Inc.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

July 2008 M9999-070208-A

## **Ordering Information**

| Part Number            | Manufacturing<br>Part Number | Marking <sup>(1)</sup> | VOUT1 <sup>(2)</sup> | VOUT2 <sup>(2)</sup> | Junction<br>Temp. Range | Package <sup>(3)</sup>                        |

|------------------------|------------------------------|------------------------|----------------------|----------------------|-------------------------|-----------------------------------------------|

| MIC5316-1.5/1.2/1.0YMT | MIC5316-F4CYMT               | QSF4C                  | 1.5V                 | 1.2V/1.0V            | –40°C to +125°C         | 12-Pin 2.5mm x 2.5mm<br>Thin MLF <sup>®</sup> |

| MIC5316-1.5/1.3/1.0YMT | MIC5316-F5CYMT               | QSF5C                  | 1.5V                 | 1.3V/1.0V            | –40°C to +125°C         | 12-Pin 2.5mm x 2.5mm<br>Thin MLF <sup>®</sup> |

| MIC5316-1.8/1.6/1.1YMT | MIC5316-GW3YMT               | QSGW3                  | 1.8V                 | 1.6V/1.1V            | –40°C to +125°C         | 12-Pin 2.5mm x 2.5mm<br>Thin MLF <sup>®</sup> |

| MIC5316-1.8/1.8/1.0YMT | MIC5316-GGCYMT               | QSGGC                  | 1.8V                 | 1.8V/1.0V            | -40°C to +125°C         | 12-Pin 2.5mm x 2.5mm<br>Thin MLF <sup>®</sup> |

#### Notes:

- Pin 1 identifier = ▲.

- 2. For other voltage option, contact Micrel Marketing for details

- 3. MLF® is a GREEN RoHS compliant package. Lead finish is NiPdAu. Mold compound is Halogen Free.

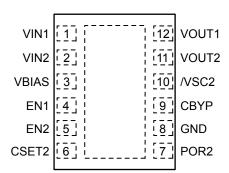

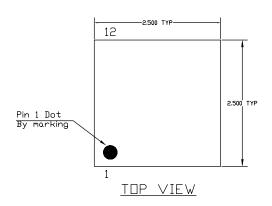

# **Pin Configuration**

12-Pin 2.5mm × 2.5mm Thin MLF® (MT)

# **Pin Description**

| Pin Number | Pin Name | Pin Function                                                                                                                                         |

|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VIN1     | Voltage Input for LDO1.                                                                                                                              |

| 2          | VIN2     | Voltage Input for LDO2.                                                                                                                              |

| 3          | VBIAS    | Bias Input Voltage.                                                                                                                                  |

| 4          | EN1      | Enable Input for LDO1. Active High Input. Logic High = On; Logic Low = Off; Do not leave floating.                                                   |

| 5          | EN2      | Enable Input for LDO2. Active High Input. Logic High = On; Logic Low = Off; Do not leave floating.                                                   |

| 6          | CSET2    | Delay Set Input for POR2. Connect an external capacitor to GND to set the delay for POR2. When left open, there is no delay. Do not ground this pin. |

| 7          | POR2     | Power-on Reset for LDO2.                                                                                                                             |

| 8          | GND      | Ground.                                                                                                                                              |

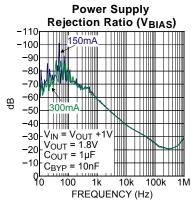

| 9          | CBYP     | Bypass: Connect a capacitor to ground to improve output noise and PSRR.                                                                              |

| 10         | /VSC2    | Voltage Select Input for LDO2. Active Low Input. Logic High = Full Output Voltage; Logic Low = Low Output Voltage. Do not leave floating.            |

| 11         | VOUT2    | Output of regulator 2.                                                                                                                               |

| 12         | VOUT1    | Output of regulator 1.                                                                                                                               |

# Absolute Maximum Ratings<sup>(1)</sup>

| Main Input Voltage (V <sub>IN1</sub> , V <sub>IN2</sub> )          | 0V to V <sub>BIAS</sub>            |

|--------------------------------------------------------------------|------------------------------------|

| Bias Supply Voltage (V <sub>BIAS</sub> )                           |                                    |

| Enable Input Voltage (V <sub>EN1</sub> , V <sub>EN2</sub> )        | 0V to V <sub>BIAS</sub>            |

| Voltage Select Input Voltage (V <sub>NSC2</sub> ).                 | 0V to V <sub>BIAS</sub>            |

| POR Voltage (V <sub>POR2</sub> )                                   | 0V to V <sub>BIAS</sub>            |

| Power Dissipation                                                  | .Internally Limited <sup>(3)</sup> |

| Lead Temperature (soldering, 3sec.).                               | 260°C                              |

| Storage Temperature (T <sub>s</sub> )                              | –65°C to +150°C                    |

| Storage Temperature (T <sub>s</sub> )<br>ESD Rating <sup>(4)</sup> | 2kV                                |

# Operating Ratings<sup>(2)</sup>

| Supply voltage (V <sub>IN1</sub> , V <sub>IN2</sub> )       | +1.7V to V <sub>BIAS</sub> |

|-------------------------------------------------------------|----------------------------|

| Bias Supply Voltage (V <sub>BIAS</sub> )                    | 2.5V to +5.5V              |

| Enable Input Voltage (V <sub>EN1</sub> , V <sub>EN2</sub> ) | 0V to V <sub>BIAS</sub>    |

| Voltage Select Input Voltage (V <sub>/VSC2</sub> )          | 0V to V <sub>BIAS</sub>    |

| POR Voltage (V <sub>POR2</sub> )                            | $0V$ to $V_{BIAS}$         |

| Junction Temperature (T <sub>J</sub> )                      | –40°C to +125°C            |

| Junction Thermal Resistance                                 |                            |

| 2.5mm x 2.5mm Thin MLF-12 ( $\theta_{JA}$ )                 | 70°C/W                     |

|                                                             |                            |

# **Electrical Characteristics**(4)

$V_{\text{BIAS}} = 3.6 \text{V}; \ V_{\text{IN1}} = V_{\text{IN2}} = V_{\text{OUT}} \ (\text{Highest of two regulators}) + 1 \text{V}; \ C_{\text{BIAS}} = C_{\text{OUT}} = 1.0 \mu\text{F}, \ C_{\text{BYP}} = 0.01 \mu\text{F}, \ I_{\text{OUT}} = 100 \mu\text{A}; \ T_{\text{J}} = 25^{\circ}\text{C}, \ \text{bold} \ \text{values indicate} -40^{\circ}\text{C} \ \text{to} + 125^{\circ}\text{C}; \ \text{unless noted}.$

| Parameter                                             | Condition                                                                | Min  | Тур  | Max                                                                                      | Units         |

|-------------------------------------------------------|--------------------------------------------------------------------------|------|------|------------------------------------------------------------------------------------------|---------------|

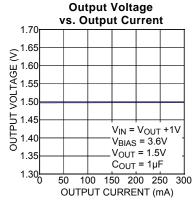

| Output Voltage Accuracy                               | Variation from nominal V <sub>OUT1</sub> & V <sub>OUT2</sub>             | -1.0 |      | +1.0                                                                                     | %             |

|                                                       | Variation from nominal V <sub>OUT1</sub> & V <sub>OUT2</sub>             | -2.0 |      | +1.0<br>+2.0<br>+3.0<br>+4.0<br>0.3<br>0.3<br>1.0<br>100<br>200<br>12<br>12<br>46<br>1.0 | %             |

| Select Mode Output Voltage                            | V <sub>OUT2</sub> ; V <sub>/VSC2</sub> = Logic Low                       | -3.0 |      | +3.0                                                                                     | %             |

| Accuracy                                              | V <sub>OUT2</sub> ; V <sub>/VSC2</sub> = Logic Low                       | -4.0 |      | +4.0                                                                                     | %             |

| V <sub>IN</sub> Line Regulation                       | $V_{IN} = V_{OUT} + 1V$ to 5.5V, $V_{BIAS} = 5.5V$                       |      | 0.02 | 0.3                                                                                      | %/V           |

| V <sub>BIAS</sub> Line Regulation                     | V <sub>BIAS</sub> = 3.6V to 5.5V, V <sub>IN</sub> = V <sub>OUT</sub> +1V |      | 0.02 | 0.3                                                                                      | %/V           |

| Load Regulation                                       | I <sub>OUT</sub> = 100μA to 300mA                                        |      | 0.4  | 1.0                                                                                      | %             |

| Dropout Voltage                                       | I <sub>OUT</sub> = 150mA                                                 |      | 40   | 100                                                                                      | mV            |

|                                                       | I <sub>OUT</sub> = 300mA                                                 |      | 85   | 200                                                                                      | mV            |

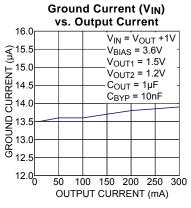

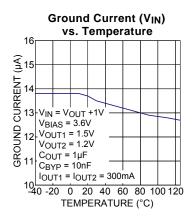

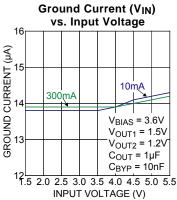

| Ground Pin Current V <sub>IN1</sub> ,V <sub>IN2</sub> | $V_{EN1}$ = High; $V_{EN2}$ = Low; $I_{OUT1}$ = 100 $\mu$ A to 300mA     |      | 7    | 12                                                                                       | μA            |

|                                                       | $V_{EN1}$ = Low; $V_{EN2}$ = High; $I_{OUT2}$ = 100 $\mu$ A to 300mA     |      | 7    | 12                                                                                       | μA            |

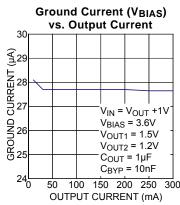

| Ground Pin Current V <sub>BIAS</sub>                  | $I_{OUT1} = I_{OUT2} = 100 \mu A \text{ to } 300 \text{mA}$              |      | 30   | 46                                                                                       | μA            |

| Ground Pin Current in Shutdown                        | V <sub>EN</sub> ≤ 0.2V                                                   |      | 0.01 | 1.0                                                                                      | μA            |

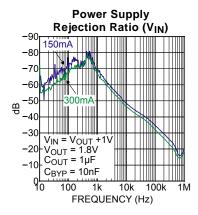

| V <sub>IN</sub> Ripple Rejection                      | $f = 1kHz; C_{OUT} = 1.0\mu F; C_{BYP} = 0.01\mu F$                      |      | 65   |                                                                                          | dB            |

|                                                       | $f = 20kHz; C_{OUT} = 1.0\mu F; C_{BYP} = 0.01\mu F$                     |      | 40   |                                                                                          | dB            |

| Current Limit                                         | V <sub>OUT</sub> = 0V                                                    | 350  | 550  |                                                                                          | mA            |

| Output Voltage Noise                                  | $C_{OUT}$ = 1 $\mu$ F, $C_{BYP}$ = 0.01 $\mu$ F, 10Hz to 100kHz          |      | 30   |                                                                                          | $\mu V_{RMS}$ |

| Enable                                                |                                                                          |      | •    |                                                                                          |               |

| Enable Input Voltage                                  | Logic Low                                                                |      |      | 0.2                                                                                      | V             |

|                                                       | Logic High                                                               | 1.2  |      |                                                                                          | V             |

| Enable Input Current                                  | V <sub>IL</sub> ≤ 0.2V                                                   |      | 0.02 | 1                                                                                        | μA            |

|                                                       | V <sub>IH</sub> ≥ 1.2V                                                   |      | 0.2  | 1                                                                                        | μA            |

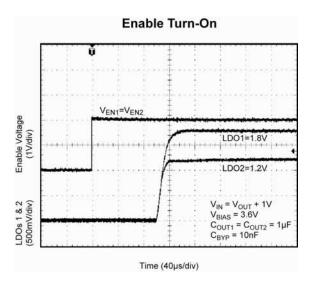

| Turn-on Time                                          | $C_{OUT} = 1\mu F; C_{BYP} = 0.01\mu F$                                  |      | 150  | 300                                                                                      | μs            |

| Parameter                      | Condition                                             | Min   | Тур  | Max   | Units |

|--------------------------------|-------------------------------------------------------|-------|------|-------|-------|

| POR2 Output                    |                                                       |       |      |       |       |

| $V_{TH}$                       | Low Threshold, % of V <sub>OUT2</sub> (Flag ON)       | 88    |      |       | %     |

|                                | High Threshold, % of V <sub>OUT2</sub> (Flag OFF)     |       |      | 98    | %     |

| V <sub>OL</sub>                | POR2 Output Logic Low Voltage; I <sub>L</sub> = 250μA |       | 0.02 | 0.1   | V     |

| I <sub>POR2</sub>              | Flag Leakage Current, Flag OFF                        | -1    | 0.01 | +1    | μΑ    |

| CSET2 INPUT                    |                                                       |       |      |       |       |

| CSET2 Pin Current Source       | V <sub>CSET2</sub> = 0V                               | 8.0   | 1.4  | 2     | μA    |

| CSET2 Pin Threshold<br>Voltage | POR2 = High                                           | 1.212 | 1.25 | 1.288 | V     |

#### Notes:

- 1. Exceeding the absolute maximum rating may damage the device.

- 2. The device is not guaranteed to function outside its operating rating.

- 3. The maximum allowable power dissipation of any  $T_A$  (ambient temperature) is  $P_{D(max)} = T_{J(max)} T_A$ ) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will result in excessive die temperature, and the regulator will go into thermal shutdown.

- 4. Devices are ESD sensitive. Handling precautions recommended. Human body model,  $1.5k\Omega$  in series with 100pF.

- 5. Specification for packaged product only.

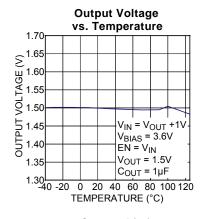

### **Typical Characteristics**

# **Typical Characteristics (continued)**

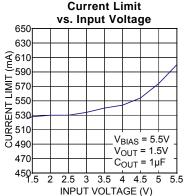

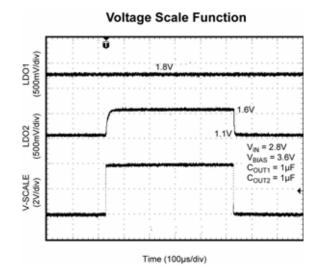

## **Functional Characteristics**

## **Functional Characteristics (continued)**

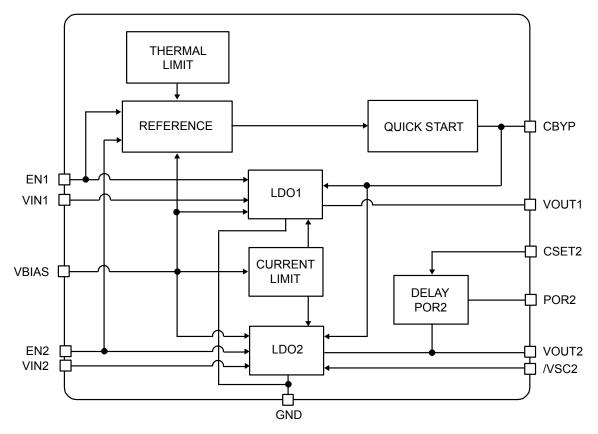

## **Functional Diagram**

MIC5316 Block Diagram

### **Application Information**

The MIC5316 is a high performance, dual low input voltage, ultra-low dropout regulator designed for applications requiring very fast transient response. The MIC5316 utilizes two input supplies ( $V_{\text{IN}}$  and  $V_{\text{BIAS}}$ ), significantly reducing the dropout voltage.

The MIC5316 regulator is fully protected from damage due to fault conditions, offering linear current limiting and thermal shutdown.

#### **Bias Supply Voltage**

$V_{\text{BIAS}},$  requiring relatively light current, provides power to the control portion of the MIC5316. Bypassing on the bias pin is recommended to improve performance of the regulator during line and load transients. A  $1\mu\text{F}$  ceramic capacitor from  $V_{\text{BIAS}}\text{-to-ground}$  is recommended to help reduce the high frequency noise from being injected into the control circuitry.

#### **Input Supply Voltage**

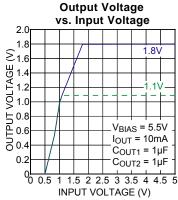

$V_{\text{IN1}}$  and  $V_{\text{IN2}}$ , provide the supply to power the LDOs independently. The minimum input voltage is 1.7V allowing conversion from low voltage supplies. The low input voltage provides high efficiency by reducing the input to output voltage step which minimizes the regulator power loss.

#### **Input Capacitor**

The MIC5316 is a high-performance, high bandwidth device. Therefore, it requires a well-bypassed input supply for optimal performance. A 1µF capacitor is required from the input-to-ground to provide stability. Low-ESR ceramic capacitors provide optimal performance at a minimum of space. Additional high-frequency capacitors, such as small-valued NPO dielectric-type capacitors, help filter out high-frequency noise and are good practice in any RF-based circuit. X5R or X7R dielectrics are recommended for the input capacitor. Y5V dielectrics lose most of their capacitance over temperature and are therefore, not recommended.

#### **Output Capacitor**

The MIC5316 requires an output capacitor of  $1\mu F$  or greater to maintain stability. The design is optimized for use with low-ESR ceramic chip capacitors. High ESR capacitors may cause high frequency oscillation. The output capacitor can be increased, but performance has been optimized for a  $1\mu F$  ceramic output capacitor and does not improve significantly with larger capacitance.

X7R/X5R dielectric-type ceramic capacitors are recommended because of their temperature performance. X7R-type capacitors change capacitance by 15% over their operating temperature range and are the most stable type of ceramic capacitors. Z5U and Y5V dielectric capacitors change value by as much as

50% and 60%, respectively, over their operating temperature ranges. To use a ceramic chip capacitor with Y5V dielectric, the value must be much higher than an X7R ceramic capacitor to ensure the same minimum capacitance over the equivalent operating temperature range.

#### **Bypass Capacitor**

A capacitor can be placed from the bypass pin-to-ground to reduce the output voltage noise. The capacitor bypasses the internal reference. A 0.01µF capacitor is recommended for applications that require low-noise outputs. The bypass capacitor can be increased, further reducing noise and improving PSRR. Turn-on time increases slightly with respect to the bypass capacitance. A unique, quick-start circuit allows the MIC5316 to drive a large capacitor on the bypass pin without significantly slowing turn-on time.

#### **No-Load Stability**

Unlike many other voltage regulators, the MIC5316 will remain stable and in regulation with no load. This is especially important in CMOS RAM keep-alive applications.

#### Enable/Shutdown

The MIC5316 is provided with dual active-high enable pins that allow each regulator to be disabled independently. Forcing the enable pin low disables the regulator and sends it into a "zero" off-mode-current state. In this state, current consumed by the regulator goes nearly to zero. Forcing the enable pin high enables the output voltage. The active-high enable pin uses CMOS technology and the enable pin cannot be left floating; a floating enable pin may cause an indeterminate state on the output.

#### **Power On Reset**

The second regulator (LDO2) provides a Power On Reset (POR2) status pin. This pin is an open drain output. When LDO2 is enabled an active low POR2 indicates an under voltage condition on  $V_{\text{OUT2}}$ .

The POR2 status signal can be programmed for a delay (1sec/ $\mu$ F) by adding a capacitor from the  $C_{SET2}$  pin to ground. Zero delay is added by leaving the  $C_{SET2}$  pin open circuit.

#### **Voltage Select**

The MIC5316 incorporates voltage select technology to set LDO2's voltage output to a preset lower level. The /VSC2 pin is an active low input. A logic high signal sets  $V_{\text{OUT2}}$  to the full output voltage; while a logic low signal sets  $V_{\text{OUT2}}$  to the lower output voltage.

#### **Thermal Considerations**

The MIC5316 is designed to provide 300mA of continuous current for both outputs in a very small package. Maximum ambient operating temperature can be calculated based upon the output current and the voltage drop across the part. Given that the input voltage is 1.8V, the output voltage is 1.5V for  $V_{\text{OUT1}}$ , 1.0V for  $V_{\text{OUT2}}$  and the output current = 300mA for each output. The actual power dissipation of the regulator circuit can be determined using the equation:

$P_D$  =  $(V_{\text{IN}}-V_{\text{OUT1}})~I_{\text{OUT1}}+(V_{\text{IN}}-V_{\text{OUT2}})~I_{\text{OUT2}}+V_{\text{BIAS}}~I_{\text{GND}}$  Because this device is CMOS and the ground current is typically <100µA over the load range, the power dissipation contributed by the ground current is <1% and can be ignored for this calculation.

$$P_D = (1.8V - 1.5V) \times 300\text{mA} + (1.8V - 1.0V) \times 300\text{mA}$$

$P_D = 0.33W$

To determine the maximum ambient operating temperature of the package, use the junction-to-ambient thermal resistance of the device and the following basic equation:

$$P_{D(MAX)} = \left(\frac{T_{J(MAX)} - T_{A}}{\theta_{JA}}\right)$$

$T_{J(max)}$  = 125°C, the maximum junction temperature of the die. The junction-to-ambient thermal resistance for the minimum footprint, is  $\theta_{JA}$  = 70°C/W.

Substituting  $P_D$  for  $P_{D(max)}$  and solving for the ambient operating temperature will give the maximum operating conditions for the regulator circuit.

The maximum power dissipation must not be exceeded for proper operation.

For example, when operating the MIC5316-F5CYMT at an input voltage of 1.8V and 300mA, loads at each output with a minimum footprint layout, the maximum ambient operating temperature  $T_A$  can be determined as follows:

$$0.33W = (125^{\circ}C - T_{A})/(70^{\circ}C/W)$$

$T_{A} = 101.9^{\circ}C$

For a full discussion of heat sinking and thermal effects on voltage regulators, refer to the "Regulator Thermals" section of *Micrel's Designing with Low-Dropout Voltage Regulators* handbook. This information can be found on Micrel's website at:

http://www.micrel.com/\_PDF/other/LDOBk\_ds.pdf

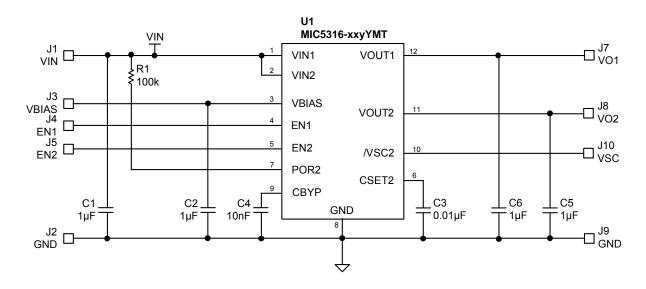

# **MIC5316 Typical Application Circuit**

### **Bill of Materials**

| Item           | Part Number        | Manufacturer          | Description                                      | Qty |

|----------------|--------------------|-----------------------|--------------------------------------------------|-----|

| C1, C2, C5, C6 | C1608X5R1A105K     | TDK <sup>(1)</sup>    | Capacitor, 1µF Ceramic, 10V, X5R, Size 0603      | 4   |

| C3             | VJ0603Y104KXACW1BC | Vishay <sup>(2)</sup> | Capacitor, 0.1µF, 50V, X7R, Size 0603            | 1   |

| C4             | VJ0603Y103KXACW1BC | Vishay <sup>(2)</sup> | Capacitor, 0.01µF, 50V, X7R, Size 0603           | 1   |

| R1             | CRCW0603100KFKEA   | Vishay <sup>(2)</sup> | Resistor, 100kΩ, 1%, 1/16W, Size 0603            | 1   |

| U1             | MIC5316-xxyYMT     | Micrel <sup>(3)</sup> | Low Voltage Dual 300mA LDO with POR and V Select | 1   |

#### Notes:

- 1. TDK: www.tdk.com

- 2. Vishay: www.vishay.com

- 3. Micrel, Inc.: www.micrel.com

## **PCB Layout Recommendations**

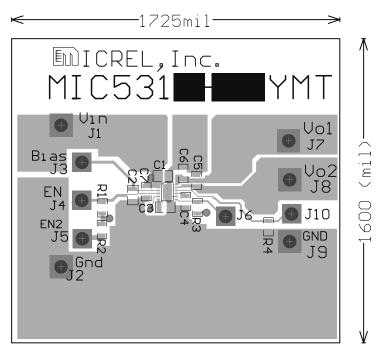

**Top Layer**

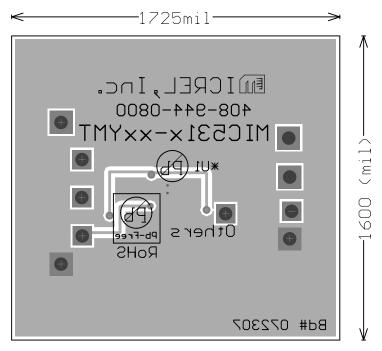

**Bottom Layer**

MIC5316 Micrel, Inc.

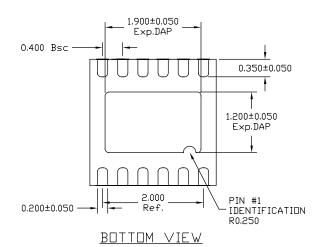

### **Package Information**

0.55±0.05 0.000-0.050 0.152 Ref.

#### NDTES :

- ALL DIMENSIONS ARE IN MILLIMETERS.

MAX. PACKAGE WARPAGE IS 0.05 mm.

MAXIMUM ALLOWABE BURRS IS 0.076 mm IN ALL DIRECTIONS.

- PIN #1 ID ON TOP WILL BE LASER MARKED.

SIDE VIEW

12-Pin 2.5mm × 2.5mm Thin MLF® (MT)

#### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

The information furnished by Micrel in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2008 Micrel, Incorporated.

July 2008 14 M9999-070208-A