# RETOKO

## **FEATURES**

- Optimized for Off-Line and Battery Powered Operation

- Internal Zero-Voltage Detector

- Soft-Start

- Pulse-by-Pulse Current Limit

- Overdissipation Protection with Soft-Start

- Overvoltage Protection with Soft-Start

- Low-Current Standby mode

- Programmable On/Off Timing

- Enable Control

# DESCRIPTION

The TK75020 is a low-cost, high-performance Zero-Voltage Switching (ZVS) controller IC. The primary applications are in inverters for Cold Cathode Fluorescent Lamps (CCFL) and in ZVS quasi-resonant or multi-resonant converters. The combination of a unique (patent-pending) control concept and a ZVS resonant inverter generates low-distortion sine wave for the fluorescent lamp, leading to extended lamp life and high luminous efficiency. The IC features all necessary circuits of a controller for such applications, including externally adjustable timing parameters (frequency,  $T_{on(min)}$ ,  $T_{off(max)}$ ), current limit, Soft-Start, enable, error amplifier, and a trimmed reference. The same reference is used for undervoltage protection and other critical internal biases. Supply current in the "off" mode is kept at a minimum level (2 µA typical). Special care has been taken to avoid undesirable turn-on of the external power MOSFET when sufficient supply voltage is not available, or when the device is held in the off mode. Even with no  $V_{cc}$  applied, the drive pin of the IC will sink in

January 1999 TOKO, Inc.

# ZVS RESONANT CONTROLLER

## **APPLICATIONS**

- Cold Cathode Fluorescent Lamps

- Resonant Power Supplies

- Power Supplies for Notebook Computers

- Power Supplies for Personal Electronics

excess of 20 mA while maintaining the voltage below 1 V to prevent that leakage currents turn on the power MOSFET. An internal zero-voltage detector monitors the voltage across the MOSFET and ensures that the turn-on will only take place under zero-voltage conditions. A unique overdissipation protection prevents the overheating of the power MOSFET in case the zero-voltage switching is lost.

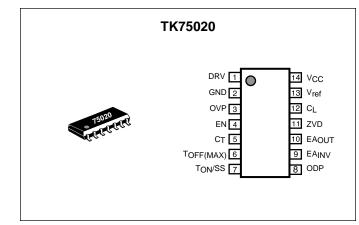

The TK75020 is available in a 14-lead surface mount package.

# **ABSOLUTE MAXIMUM RATINGS**

| All Pins Except $T_{ON}$ / SS, $T_{OFF(MAX)}$ , $V_{REF}$ , $C_{T}$ , ODP and EN (Low Impedance Source) |        |

|---------------------------------------------------------------------------------------------------------|--------|

| ODP and EN (Low Impedance Source)                                                                       | 16 V   |

| $T_{ON}$ / SS, $T_{OFF(MAX)}$ , ref, $C_{T}$ , ODP Pins                                                 | 6 V    |

| EŇ Pin                                                                                                  | 16 V   |

| Power Dissipation (Note 1)                                                                              | 500 mW |

| Maximum Current (V <sub>cc</sub> and ZVD Pins) | 20 mA          |

|------------------------------------------------|----------------|

| Storage Temperature Range                      | -55 to +150 °C |

| Operating Temperature Range                    | 20 to +85 °C   |

| Junction Temperature                           | 150 °C         |

| Lead Soldering Temperature (10 s)              | 235 °C         |

# **TK75020 ELECTRICAL CHARACTERISTICS**

Test conditions:  $V_{CC} = 12 \text{ V}$ ,  $V_{EN} = 2.4 \text{ V}$ ,  $C_T = 360 \text{ pF}$ ,  $I_{TON/SS} = I_{TOFF(MAX)} = 50 \mu\text{A}$ , DRV is Open,  $T_A = Full \text{ Operating Temperature Range}$ , Typical numbers apply at  $T_A = 25 \text{ °C}$ , unless otherwise specified.

| SYMBOL                       | PARAMETER                         | TEST C                                        | ONDITIONS                   | MIN  | TYP | MAX  | UNITS |

|------------------------------|-----------------------------------|-----------------------------------------------|-----------------------------|------|-----|------|-------|

| I <sub>CC(OFF)</sub>         | Supply Current OFF                | $V_{EN} = 0 V$                                |                             |      | 2   | 100  | μA    |

| I <sub>CC(OFF,H)</sub>       | Supply Current OFF, HIGH          | V <sub>EN</sub> = 0 V, V <sub>CC</sub> = 16 V |                             |      |     | 2    | mA    |

| I <sub>CC(UVLO)</sub>        | Supply Current, UVLO Mode         | $V_{cc} = 5 V$                                |                             |      | 700 | 1000 | μA    |

| 1                            | Supply Current ON                 | $V_{\rm CC} = 6 V$                            |                             |      | 4.7 | 6    | mA    |

| CC(ON)                       |                                   | 6 V < V <sub>cc</sub> < 16                    | 6 V                         |      |     | 8    | mA    |

| 1                            |                                   | $V_{\rm CC} = 6 \text{ V}, \text{ C}_{\rm C}$ | <sub>DRV</sub> = 1 nF       |      | 5.6 | 8    | mA    |

| CC(ON,DRV)                   | Supply Current ON, DRV            | 6 V < V <sub>cc</sub> < 16                    | 6 V                         |      |     | 10   | mA    |

| V <sub>CC(ON)</sub>          | UVLO High Threshold               |                                               |                             | 5.2  | 5.6 | 6.0  | V     |

| $V_{CC(OFF)}$                | UVLO Low Threshold                |                                               |                             | 5.0  | 5.3 | 5.6  | V     |

| V <sub>CC(HYST)</sub>        | UVLO Hysteresis                   |                                               |                             | 80   |     | 500  | mV    |

|                              | ECTION (EN PIN)                   |                                               |                             |      |     |      |       |

| V <sub>EN</sub>              | Threshold Voltage                 | 6 V < V <sub>cc</sub> < 16                    | 6 V                         | 0.4  |     | 2.4  | V     |

| 1                            | Innut Current                     | V <sub>EN</sub> = 2.4 V                       |                             |      | 4   |      | μA    |

| I <sub>EN</sub>              | Input Current                     | V <sub>EN</sub> = 0 V, (Note 2)               |                             | -100 |     |      | nA    |

| REFEREN                      | CE SECTION (V <sub>REF</sub> PIN) | •                                             |                             |      | •   | •    | •     |

|                              | Reference Output Voltage          | I <sub>ref</sub> = 0 mA                       | T <sub>A</sub> = 25 ° C     | 3.8  | 4.0 | 4.2  | V     |

| V <sub>ref</sub>             |                                   |                                               | T <sub>A</sub> = Full Range | 3.7  | 4.0 | 4.3  | V     |

| $ \Delta V_{\rm ref(LOAD)} $ | Load Regulation                   | -1 mA < I <sub>ref</sub> < 0 mA               |                             |      | 4.0 |      | mV    |

| $ \Delta V_{\rm ref(LINE)} $ | Line Regulation                   | 6 V < V <sub>cc</sub> < 16 V                  |                             |      | 15  |      | mV    |

| I<br>ref(SC)                 | Short Circuit Current             | $V_{ref} = 0 V$                               |                             |      | -12 |      | mA    |

Note 1: Power Dissipation is 500 mW when mounted as recommended. Derate at 4 mW/°C for operation above 25°C. Note 2: Guaranteed by design.

# TK75020 ELECTRICAL CHARACTERISTICS (CONT.)

Test conditions:  $V_{CC} = 12 \text{ V}$ ,  $V_{EN} = 2.4 \text{ V}$ ,  $C_T = 360 \text{ pF}$ ,  $I_{TON/SS} = I_{TOFF(MAX)} = 50 \mu\text{A}$ , DRV is Open,  $T_A = \text{Full Operating Temperature Range}$ , Typical numbers apply at  $T_A = 25 \text{ °C}$ , unless otherwise specified.

| SYMBOL                    | PARAMETER                                 | TEST CONDITIONS                                                                               | MIN  | ТҮР  | MAX  | UNITS |

|---------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------|------|------|------|-------|

| DRIVE SEC                 | CTION (DRV PIN)                           |                                                                                               | 1    | 1    |      | 1     |

| <i>\</i> /                | Output Llink Valence                      | I <sub>DRV</sub> = -20 mA                                                                     | 9.0  | 10.0 |      | V     |

| $V_{\text{DRV(HIGH)}}$    | Output High Voltage                       | I <sub>DRV</sub> = -100 mA                                                                    |      | 9.8  |      | V     |

|                           | Output Low Voltage                        | I <sub>DRV</sub> = 20 mA                                                                      |      | 0.3  | 0.6  | V     |

| $V_{\text{DRV(LOW)}}$     |                                           | I <sub>DRV</sub> = 200 mA                                                                     |      | 1.8  | 2.5  | V     |

| DRV(LOW)                  |                                           | $I_{_{DRV}} = 20 \text{ mA}, \text{ V}_{_{CC}} = 0 \text{ V or}$<br>$V_{_{EN}} = 0 \text{ V}$ |      | 0.9  | 1.3  | V     |

| I<br>DRV(SRC,PK)          | Peak Source Current                       | C <sub>DRV</sub> = 10 nF                                                                      |      | 500  |      | mA    |

| DRV(SINK,PK)              | Peak Sink Current                         | C <sub>DRV</sub> = 10 nF                                                                      |      | 700  |      | mA    |

| t <sub>RISE</sub>         | Rise Time                                 | C <sub>DRV</sub> = 1 nF                                                                       |      | 70   | 120  | ns    |

| t <sub>FALL</sub>         | Fall Time                                 | C <sub>DRV</sub> = 1 nF                                                                       |      | 25   | 75   | ns    |

| ERROR A                   | IPLIFIER SECTION (EA <sub>INV</sub> AND E | A <sub>out</sub> PINS)                                                                        |      | •    |      | •     |

| $V_{\text{EA(ref)}}$      | Equivalent Internal Reference<br>Voltage  |                                                                                               | 1.19 | 1.26 | 1.30 | V     |

| I <sub>EA(INV)</sub>      | Bias Current                              |                                                                                               |      | 0.10 |      | μA    |

| V <sub>EA(OUT, LOW)</sub> | Output Voltage LOW                        | $I_{EA(OUT)} = -1 \text{ mA}, V_{INV} = 1.5 \text{ V}$                                        |      | 0.25 |      | V     |

| A <sub>OL</sub>           | Open Loop Gain                            | 15 k $\Omega$ From EA $_{_{OUT}}$ to T $_{_{ON}}$ / SS                                        |      | 70   |      | dB    |

| GBW                       | Gain-Bandwidth Product                    | 15 kΩ From EA <sub>OUT</sub> to $T_{ON}$ / SS, (Note 2)                                       |      | 2    |      | MHz   |

| PSSR                      | Power Supply Rejection Ratio              | $6 \text{ V} \le \text{V}_{cc} \le 16 \text{ V}$                                              |      | 65   |      | dB    |

| CURRENT                   | LIMIT SECTION (C <sub>L</sub> PIN)        |                                                                                               |      |      |      |       |

| I <sub>CL</sub>           | Bias Current                              | $V_{CL} = 0 V$                                                                                |      | -0.2 |      | μA    |

| V <sub>CL(TH)</sub>       | Threshold Voltage                         |                                                                                               | 180  | 210  | 240  | mV    |

| t <sub>CL(DRV)</sub>      | Delay to DRV                              | V <sub>cL</sub> Steps From 0 to 400 mV                                                        |      | 150  |      | ns    |

|                           | ETTING AND SOFT-START SECT                | TION (T <sub>on</sub> / SS PIN)                                                               |      |      |      |       |

| ITON / SS (SC)            | Short Circuit Current                     | $V_{TON/SS} = 0 V$                                                                            |      | -2.5 |      | mA    |

| V <sub>TON/SS</sub>       | Pin Voltage                               | $I_{\text{TON/SS}} = 0 \text{ mA}$                                                            | 1.8  | 2.0  | 2.2  | V     |

| V <sub>SS(TH)</sub>       | Soft-Start Threshold                      |                                                                                               | 0.40 | 0.65 | 0.90 | V     |

| V <sub>DCH(TH)</sub>      | ODP Discharge Threshold                   |                                                                                               | 1.0  | 1.4  | 1.9  | V     |

January 1999 TOKO, Inc.

# TK75020 ELECTRICAL CHARACTERISTICS (CONT.)

Test conditions:  $V_{CC} = 12 \text{ V}$ ,  $V_{EN} = 2.4 \text{ V}$ ,  $C_T = 360 \text{ pF}$ ,  $I_{TON/SS} = I_{TOFF(MAX)} = 50 \mu\text{A}$ , DRV is Open,  $T_A = \text{Full Operating Temperature Range}$ , Typical numbers apply at  $T_A = 25 \text{ °C}$ , unless otherwise specified.

| SYMBOL                   | PARAMETER                                                      | TEST CONDITIONS                                            | MIN  | ТҮР      | MAX  | UNITS |

|--------------------------|----------------------------------------------------------------|------------------------------------------------------------|------|----------|------|-------|

| MAXIMUM C                | DFF-TIME SETTING SECTION (T <sub>or</sub>                      | F(MAX) PIN)                                                | 1    | <u> </u> |      | 1     |

| I <sub>T(OFF, MAX)</sub> | Short Circuit Current                                          | V <sub>T(OFF, MAX)</sub> = 0 V                             |      | 2.5      |      | mA    |

| V <sub>T(OFF, MAX)</sub> | Pin Voltage                                                    | I <sub>T(OFF, MAX)</sub> = 0 mA                            | 1.8  | 2.0      | 2.2  | V     |

| TIMING SEC               | CTION (C <sub>T</sub> PIN)                                     |                                                            |      |          |      |       |

| V <sub>CT(LOW)</sub>     | Low Threshold Voltage                                          |                                                            | 0.9  | 1.0      | 1.1  | V     |

| $V_{\rm CT(\rm HIGH)}$   | High Threshold Voltage                                         |                                                            | 2.7  | 3.0      | 3.3  | V     |

| f                        | Oscillator Frequency                                           |                                                            | 115  | 140      | 165  | kHz   |

| CTR                      | Current Transfer Ratio to $C_{\tau}$ Pin, On-time Setting      | $V_{cT} = 4 V$                                             | -6.2 | -5.5     | -4.8 |       |

| CTR <sub>TOFF(MAX)</sub> | Current Transfer Ratio to $C_{\tau}$ Pin, Max Off-time Setting | $V_{ct} = 0 V$                                             | 4.75 | 5.25     | 5.75 |       |

| ZERO VOLT                | AGE DETECTOR SECTION (ZVD                                      | PIN)                                                       |      |          |      |       |

| V <sub>ZVD(TH)</sub>     | Detector Low Threshold                                         | T <sub>A</sub> = 25 ° C                                    | 1.8  | 2.0      | 2.2  | V     |

| I <sub>ZVD</sub>         | Input Current                                                  | V <sub>ZVD</sub> =2 V                                      | -50  |          | 0    | μA    |

| t <sub>ZVD(DRV)</sub>    | Delay to DRV                                                   | $V_{zVD}$ Steps From 5 to 0 V,<br>$C_{DRV} = 1 \text{ nF}$ |      | 170      | 300  | ns    |

| OVERDISSI                | PATION DETECTOR SECTION (O                                     | DP PIN)                                                    |      | I        |      | 1     |

| V <sub>ODP(TH)</sub>     | Detection Threshold Volage                                     |                                                            | 0.45 | 0.70     | 0.95 | V     |

| I <sub>ODP(AVG)</sub>    | Average Current                                                | f = 100 kHz, $T_{OVERLAP}$ = 200 ns                        |      | 0.6      |      | μA    |

| OVERVOLT                 | AGE DETECTOR SECTION (OVP                                      | PIN)                                                       |      |          |      |       |

| V <sub>OVP(TH)</sub>     | Detection Threshold Volage                                     |                                                            | 3.6  | 4.0      | 4.3  | V     |

| t <sub>ovp(D)</sub>      | Dealy to DRV                                                   |                                                            |      | 350      | 800  | ns    |

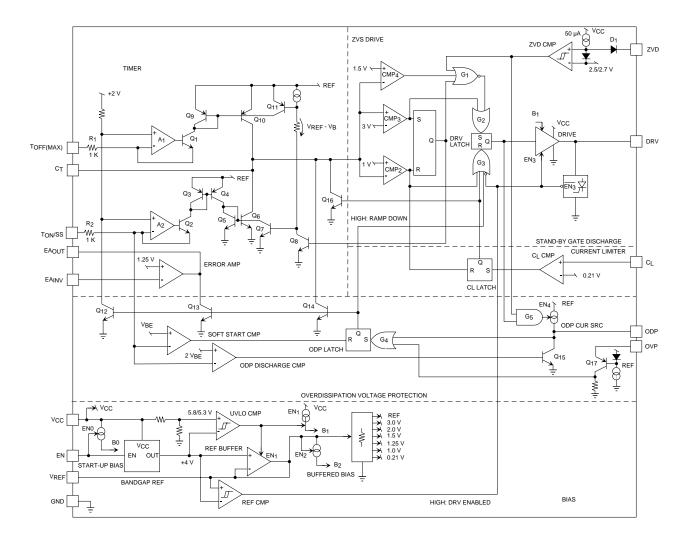

# **BLOCK DIAGRAM**

### **PIN DESCRIPTION**

#### SUPPLY VOLTAGE PIN (V<sub>cc</sub>)

This pin is connected to the supply voltage. The IC begins normal operation when two conditions are met: 1) the V<sub>CC</sub> voltage exceeds 5.6 V and 2) the voltage of the enable pin exceeds 2.2 V. Operation ceases and the IC goes into a UVLO mode when the V<sub>CC</sub> voltage drops below 5.3 V. When the voltage at the enable pin becomes less than 0.4 V, the IC is turned off ("off" mode). In UVLO mode the current consumption is less than 300  $\mu$ A, in off mode it is further reduced to below 3  $\mu$ A. The operating voltage range is 6 V to 14 V. The tolerances of the start and stop voltages are 5.6  $\pm$  0.4 V and 5.3  $\pm$  0.3 V, respectively. During normal operation the total IC current consumption is less than 8 mA (no load, 100 kHz operation).

When  $V_{CC}$  is applied to the device with the enable pin pulled above 2.2 V ("on" mode), the following events will occur:

First, a trimmed bandgap reference voltage will be generated as soon as  $V_{CC}$  reaches about 4.8 V. This reference will be used to determine the UVLO thresholds. When  $V_{CC}$  reaches the upper threshold of the undervoltage lockout comparator, that comparator enables the reference buffer. When the voltage at the output of the buffer, i.e. on the  $V_{REF}$  pin, becomes higher than about 3.7 V, an enable signal is generated for the drive stage through gate G<sub>3</sub>.

Normal operation may be interrupted at any time by pulling the enable pin below 0.4 V. When  $V_{CC}$  is reduced below the lower threshold of the undervoltage lockout, the internal 4 V bias is disabled and the drive output is quickly turned off. The bandgap reference remains active as long as  $V_{CC}$  is above 4.8 V. Special care has been taken to keep the drive output low even at a lower level of  $V_{CC}$  in order to prevent unwanted turn-on of the external MOSFET.

#### ENABLE (ON/OFF) PIN (EN)

The enable pin is used to enable or disable the IC. The IC is guaranteed to turn on (i.e., to enter the "on" mode) when the pin voltage is above 2.2 V and is guaranteed to turn off when the pin voltage is below 0.4 V. If the On/Off feature is not needed, the pin can be connected directly to the supply voltage. The enable pin is internally equivalent to a 200 k $\Omega$  resistor in series with two diodes.

#### **GROUND PIN (GND)**

This pin provides ground return connection for the IC.

#### **DRIVE PIN (DRV)**

This pin drives the external MOSFET. During standby, the DRV pin provides at least 20 mA current sinking capability with less than 1 V difference between the ground and the DRV pin. The internal circuitry connected to the DRV pin is designed to deliver a peak output voltage of 4 V above ground when the device operates at a minimum supply voltage of 6 V. An internal clamp circuit, however, ensures that the peak output voltage will never exceed 13 V. The DRV pin goes high only if the following five conditions are met simultaneously: 1) the drive (DRV) latch is set, 2) the overdissipation protection latch (ODP) is reset, 3) the current limit latch ( $C_L$ ) is reset, 4) the enable pin is pulled high, and 5) the output of the reference comparator is high, i.e., it detects that the voltage at the V<sub>ref</sub> pin is sufficiently high.

#### CURRENT LIMIT PIN (C<sub>L</sub>)

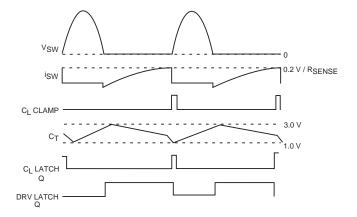

The C<sub>L</sub> pin is used for high-speed, cycle-by-cycle overload protection. When the voltage of the C<sub>L</sub> pin exceeds 0.2 V above ground, the current limit latch is set by the C<sub>L</sub> comparator and the output stage is forced low. At the same time, the timing capacitor is quickly discharged with transistor Q<sub>16</sub>. Note that a quick discharge is necessary in order to reduce the "on" time (and the duty ratio) without a significant increase in the effective "off" time. The current limit latch is reset when the output of the drive latch goes low, i.e., when the off time is over and the output of the C<sub>L</sub> comparator goes high.

#### REFERENCE PIN (V<sub>ref</sub>)

The bandgap reference, an internal 4 V source, is buffered by a reference buffer, whose output is connected to the V<sub>ref</sub> pin. The V<sub>ref</sub> pin voltage is enabled to develop when the upper threshold of the UVLO comparator is passed by V<sub>CC</sub>.

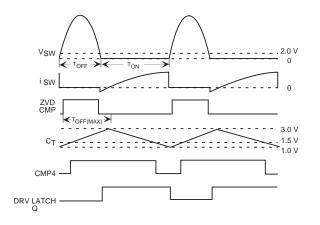

#### TIMING CAPACITOR PIN ( $C_T$ )

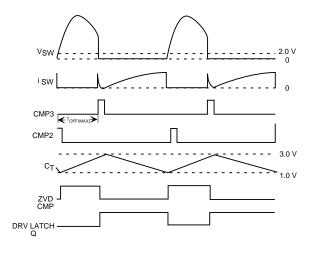

The external timing capacitor is connected to the  $C_T$  pin. The voltage across the timing capacitor oscillates between an upper level of 3 V and a lower level of 1 V. During the time the voltage of the timing capacitor is rising (due to the charging current set by the resistor between ground and the  $T_{OFF(MAX)}$  pin), the drive latch is in the reset state and

## **PIN DESCRIPTION (CONT.)**

the DRV pin is held low. The drive latch may be set either by the output of comparator  $CMP_3$  through the two-input OR gate  $G_2$  or by the ZVD comparator through  $G_1$  and  $G_2$ .  $CMP_3$  detects if the timing voltage reached 3 V, the ZVD comparator detects if the voltage at the ZVD pin dropped below 2 V. Note that gate  $G_1$  allows setting the drive latch through the ZVD pin only when the voltage at the  $C_T$  pin is higher than 1.5 V and the current limit latch is in the reset state. The reason for disabling the ZVD path at  $C_T$  pin voltages lower than 1.5 V is to prevent an immediate turnon of the MOSFET after it was turned off.  $CMP_4$  is used to detect if the  $C_T$  pin voltage is higher than 1.5 V.

When the voltage of the timing capacitor is falling (due to the discharging current set by the external resistors between the output of the error amplifier and the  $T_{ON}/SS$  pin, as well as between the  $T_{ON}/SS$  pin and ground), the DRV pin is allowed to go high. The charge and discharge currents are enabled exclusively.

#### ZERO VOLTAGE DETECTION PIN (ZVD)

This pin is connected to the drain of the power MOSFET switch of the converter or inverter through a high value resistor or a diode. When the MOSFET is turned off, the drain voltage increases at first and then decreases, due to the resonant action in the loading network of the switch. When the drain voltage is above the supply voltage of the IC, the ZVD pin voltage is clamped to the supply voltage through the internal diode D<sub>1</sub>. As the drain voltage drops below the supply voltage, the voltage of the ZVD pin begins to follow it. When the ZVD pin voltage drops below 2 V, the output of the ZVD comparator goes high and sets the drive latch through gates G<sub>1</sub> and G<sub>2</sub>. Unless there is a fault condition, the DRV pin goes high and turns on the MOSFET switch. By having the ZVD feature, the circuit automatically sets the optimum off time, essentially independently from the value of the resistor between the T<sub>OFF(MAX)</sub> pin and ground.

#### ERROR AMPLIFIER PIN (EA<sub>OUT</sub>)

The  $EA_{OUT}$  pin is the output of the internal error amplifier. The output stage of the amplifier is an open-collector transistor. It is normally connected to the  $T_{ON}$ /SS pin via an external resistor. The non-inverting input of the error amplifier is internally tied to a trimmed 1.25 V reference. The error amplifier is short-circuit protected.

#### ERROR AMPLIFIER INPUT PIN (EAINV)

The EA<sub>INV</sub> pin (the inverting input of the error amplifier) serves for receiving either an external voltage-feedback or an external current-feedback signal. The compensating network of the feedback loop is usually connected between the EA<sub>INV</sub> and the EA<sub>OUT</sub> pins.

#### TURN-ON TIMING / SOFT-START PIN (T<sub>ON</sub> / SS)

The on-time is inversely proportional to the current flowing in the resistor connected between this pin and the EA<sub>OUT</sub> pin. The T<sub>ON</sub>/SS pin is also useful for providing Soft-Start at turn-on. Soft-Start can be achieved by connecting the series combination of a resistor and capacitor between the T<sub>ON</sub>/SS pin and ground. When the normal operation of the IC is enabled (either because the V<sub>CC</sub> voltage exceeds the upper UVLO threshold or because the IC is turned on by the Enable pin), the Soft-Start capacitor, which was initially discharged, begins to charge up through the series resistor. The charging current adds to the current flowing in the on-time-setting resistor and sets a shorter on time. As the voltage builds up across the soft-start capacitor the charging current gradually decreases and the on time gradually increases.

At normal operation a voltage-to-current converter formed by A<sub>2</sub> and Q<sub>2</sub> keeps the voltage of the T<sub>ON</sub>/SS pin at 2 V. The current flowing through R<sub>2</sub> and the external resistor connected to the T<sub>ON</sub>/SS pin and ground is mirrored with Q<sub>3</sub> and Q<sub>4</sub> into a second mirror formed by Q<sub>5</sub> and Q<sub>6</sub>. The diode-connected section of the second mirror is shorted with the transistor Q<sub>7</sub> via Q<sub>8</sub> when the current switch latch is reset.

#### MAXIMUM TURNOFF TIMING PIN (T<sub>OFF(MAX)</sub>)

An external resistor connected between this pin and ground sets the current that charges the timing capacitor. The maximum possible off time is inversely proportional to the value of that current. As discussed previously, when the off period is terminated by the zero-voltage detector, the actual off time becomes shorter than the value set by this resistor.

At normal operation the voltage of the  $T_{OFF(MAX)}$  pin is kept at 2 V with the help of a voltage-to-current converter formed by the amplifier A<sub>1</sub> and transistor Q<sub>1</sub>. The current flowing through the off time setting resistor and R<sub>1</sub> is

January 1999 TOKO, Inc.

# **PIN DESCRIPTION (CONT.)**

mirrored by the transistors  $Q_9$  and  $Q_{10}$  and it charges the timing capacitor. The incoming mirror current is diverted from the mirror with transistor  $Q_{11}$  when the drive latch is set.

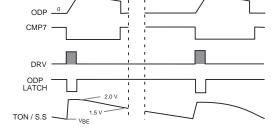

#### **OVERDISSIPATION PROTECTION PIN (ODP)**

The ODP pin is used to realize a protection against overdissipation of the power MOSFET due to the loss or absence of zero-voltage switching (ZVS). (ZVS can be lost if the load or the input voltage changes too much. ZVS is absent if the component values of the load network are far from optimal, or if the ZVD function is not implemented and the set off time is either too short or too long.) If ZVS is not present in a converter or inverter that was originally meant to operate with it, the MOSFET is turned on with a substantial voltage across it and the capacitor in parallel with it. Due to the periodic discharge of the parallel capacitor, a significant dissipation appears in the MOSFET. That dissipation is proportional to the switching frequency, the capacitance value, and the square of the voltage across the MOSFET at the instant of turn-on. The overdissipation protection works as follows: a current source is enabled when the MOSFET drain voltage is above the ZVD comparator threshold when the DRV pin voltage goes high. A short current pulse flows into the parallel combination of a resistor and capacitor connected between the ODP pin and ground and gradually begins to raise the pin voltage. When the pin voltage reaches about 0.7 V, the ODP latch is set via gate  $G_{4}$ . The output signal of the ODP latch inhibits gate G<sub>3</sub> and forces the drive output low. The output of the ODP latch also turns on transistors Q12-Q14. Q<sub>12</sub> removes the 2 V reference signal from the noninverting input of amplifiers  $A_1$  and  $A_2$ .  $Q_{13}$  pulls down the EA OUT pin. The Soft-Start capacitor connected to the TON SS pin begins to discharge through the soft-start resistor (see application circuit) and the on-time setting resistor. When the voltage at the  $T_{ON}/SS$  pin drops below 2  $V_{BE}$ , the ODP discharge comparator turns on Q<sub>15</sub>, which pulls down the ODP pin voltage and discharges the capacitor connected to that pin. When the voltage at the  $T_{ON}/SS$  pin drops below a V<sub>BE</sub>, voltage the Soft-Start comparator resets the ODP latch. At that time the 2 V reference is enabled and a new Soft-Start cycle begins. The turnoff/soft restart cycle repeats until zero-voltage switching is reestablished.

#### OVERVOLTAGE PROTECTION PIN (OVP)

The OVP pin is used to monitor the voltage across a

winding of the transformer in the CCFL inverter. When the OVP comparator detects an overvoltage, it initiates a shutdown via  $G_4$  and a Soft-Start cycle begins.

## **APPLICATION INFORMATION**

NORMAL OPERATION

#### CYCLE-BY-CYCLE CURRENT LIMIT

**OPERATION WITHOUT ZVD**

#### **OVERDISSIPATION PROTECTION**

# **APPLICATION INFORMATION (CONT.)**

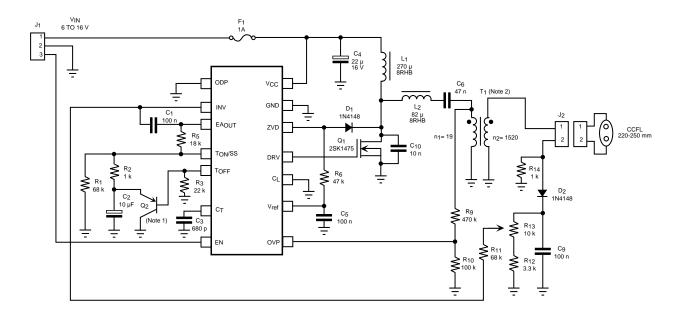

Gen. Note: Q<sub>2</sub> is not required if Q<sub>1</sub> is an avalanche rated FET Gen. Note: Part #CTX01-13154 (Call Toko Technical Support (719) 528-2200).

#### LAPTOP DISPLAY BACKLIGHTING EXAMPLE

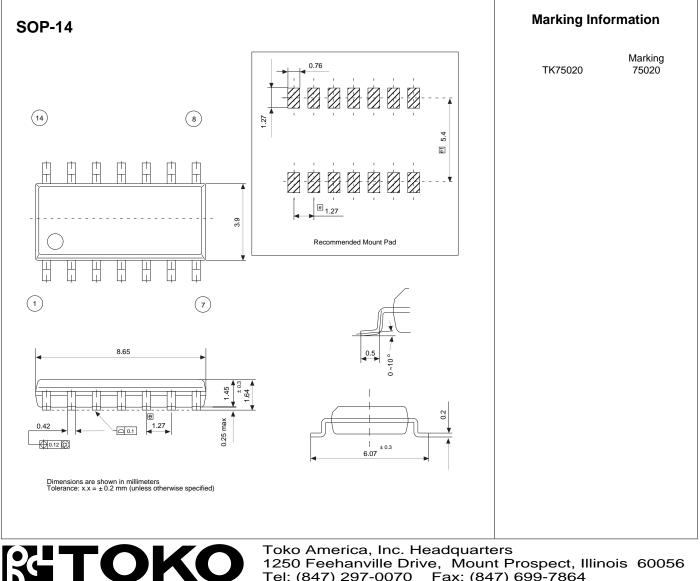

# PACKAGE OUTLINE

Fax: (847) 699-7864 Tel: (847) 297-0070

#### TOKO AMERICA REGIONAL OFFICES

Midwest Regional Office Toko America, Inc. 1250 Feehanville Drive Mount Prospect, IL 60056 Tel: (847) 297-0070 Fax: (847) 699-7864

Western Regional Office Toko America, Inc. 2480 North First Street, Suite 260 San Jose, CA 95131 Tel: (408) 432-8281 Fax: (408) 943-9790

Eastern Regional Office Toko America, Inc. 107 Mill Plain Road Danbury, CT 06811 Tel: (203) 748-6871 Fax: (203) 797-1223

Semiconductor Technical Support Toko Design Center 4755 Forge Road Colorado Springs, CO 80907 Tel: (719) 528-2200 Fax: (719) 528-2375

#### Visit our Internet site at http://www.tokoam.com

The information furnished by TOKO, Inc. is believed to be accurate and reliable. However, TOKO reserves the right to make changes or improvements in the design, specification or manufacture of is products without further notice. TOKO does not assume any liability arising from the application or use of any product or circuit described herein, nor for any infringements of patents or other rights of third parties which may result from the use of its products. No license is granted by implication or otherwise under any patent or patent rights of TOKO, Inc.

January 1999 TOKO, Inc. © 1999 Toko, Inc. All Rights Reserved

IC-122-TK75020 0798O0.0K