#### 1.0 Features

- Phase-locked loop (PLL) device synthesizes output clock frequency from crystal oscillator or external reference clock

- On-chip tunable voltage-controlled crystal oscillator • (VCXO) allows precise system frequency tuning

- Typically used for generation of MPEG-2 decoder . clock

- 3.3V supply voltage •

- Small circuit board footprint (8-pin 0.150" SOIC)

- Custom frequency selections available contact your local AMI Sales Representative for more information

## XOUT XIN 8 VSS VDD XTUNE 6 n/c VSS CLK 8-pin (0.150") SOIC Figure 2: Block Diagram XIN VCXO PLL DIVIDER XOUT **XTUNE** FS6128

#### **Figure 1: Pin Configuration**

# **ISC9001**

#### 2.0 Description

The FS6128 is a monolithic CMOS clock generator IC designed to minimize cost and component count in digital video/audio systems.

At the core of the FS6128 is circuitry that implements a voltage-controlled crystal oscillator when an external resonator (nominally 13,5MHz) is attached. The VCXO allows device frequencies to be precisely adjusted for use in systems that have frequency matching requirements, such as digital satellite receivers.

A high-resolution phase-locked loop generates an output clock (CLK) through a post-divider. The CLK frequency is ratiometrically derived from the VCXO frequency. The locking of the CLK frequency to other system reference frequencies can eliminate unpredictable artifacts in video systems and reduce electromagnetic interference (EMI) due to frequency harmonic stacking.

### Table 1: Crystal / Output Frequencies

| DEVICE f <sub>XIN</sub> (MHz) | CLK (MHz) | XTUNE Range |

|-------------------------------|-----------|-------------|

| FS6128-01 13.5                | 27        | 0-2 V       |

CLK

#### Table 2: Pin Descriptions

Key: AI = Analog Input; AO = Analog Output; DI = Digital Input; DI<sup>U</sup> = Input with Internal Pull-Up; DI<sub>D</sub> = Input with Internal Pull-Down; DIO = Digital Input/Output; DI-3 = Three-Level Digital Input, DO = Digital Output; P = Power/Ground; # = Active Low pin

| PIN | TYPE | NAME  | DESCRIPTION          |

|-----|------|-------|----------------------|

| 1   | AI   | XIN   | VCXO Feedback        |

| 2   | Р    | VDD   | Power Supply (+3.3V) |

| 3   | AI   | XTUNE | VCXO Tune            |

| 4   | Р    | VSS   | Ground               |

| 5   | DO   | CLK   | Clock Output         |

| 6   | -    | n/c   | No Connection        |

| 7   | DO   | VSS   | Ground               |

| 8   | AO   | XOUT  | VCXO Drive           |

|     |      |       |                      |

### 3.0 Functional Block Description

#### 3.1 Phase-Locked Loop (PLL)

The on-chip PLL is a standard frequency- and phaselocked loop architecture. The PLL multiplies the reference oscillator to the desired frequency by a ratio of integers. The frequency multiplication is exact with a zero synthesis error.

#### 3.2 Voltage-Controlled Crystal Oscillator (VCXO)

The VCXO provides a tunable, low-jitter frequency reference for the rest of the FS6128 system components. Loading capacitance for the crystal is internal to the FS6128. No external components (other than the resonator itself) are required for operation of the VCXO.

Continuous fine-tuning of the VCXO frequency is accomplished by varying the voltage on the XTUNE pin. The value of this voltage controls the effective capacitance presented by the VCXO to the crystal.

When using a crystal with a VCXO, it is important that the crystal load capacitance (as specified in Table 4: Operating Conditions be matched to the load capacitance as presented by the VCXO. The crystal must be specified with the correct load capacitance to obtain the maximum tuning range. The oscillator operates the crystal resonator in the parallel-resonant mode. Crystal warping, or the "pulling" of the crystal oscillation frequency, is accomplished by altering the effective load capacitance presented to the crystal by the oscillator circuit. The actual amount that changing the load capacitance alters the oscillator frequency will be dependent on the characteristics of the crystal as well as the oscillator circuit itself.

Specifically, the motional capacitance of the crystal (usually referred to by crystal manufacturers as  $C_1$ ), the static capacitance of the crystal ( $C_0$ ), and the load capacitance ( $C_L$ ) of the oscillator determine the warping capability of the crystal in the oscillator circuit.

A simple formula to obtain the warping capability of a crystal oscillator is:

$$\Delta f(ppm) = \frac{C_1 \times (C_{L2} - C_{L1}) \times 10^6}{2 \times (C_0 + C_{L2}) \times (C_0 + C_{L1})}$$

where  $C_{L1}$  and  $C_{L2}$  are the two extremes of the applied load capacitance.

EXAMPLE: A crystal with the following parameters is used. With  $C_1 = 0.02pF$ ,  $C_0 = 5pF$ ,  $C_{L1} = 13pF$ , and  $C_{L2} = 35pF$ , the coarse tuning range is

$$\Delta f = \frac{0.02 \times (35 - 13) \times 10^6}{2 \times (5 + 35) \times (5 + 13)} \approx 305 \, ppm \,.$$

**ISC9001**

### 4.0 Electrical Specifications

### **Table 3: Absolute Maximum Ratings**

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These conditions represent a stress rating only, and functional operation of the device at these or any other conditions above the operational limits noted in this specification is not implied. Exposure to maximum rating conditions for extended conditions may affect device performance, functionality, and reliability.

| PARAMETER                                                                          | SYMBOL             |                      | MAX.                 | UNITS |

|------------------------------------------------------------------------------------|--------------------|----------------------|----------------------|-------|

| Supply Voltage (V <sub>SS</sub> = ground)                                          | V <sub>DD</sub>    | V <sub>ss</sub> -0.5 | 7                    | V     |

| Input Voltage, dc                                                                  | Vi                 | V <sub>ss</sub> -0.5 | V <sub>DD</sub> +0.5 | V     |

| Output Voltage, dc                                                                 | Vo                 | V <sub>ss</sub> -0.5 | V <sub>DD</sub> +0.5 | V     |

| Input Clamp Current, dc (V <sub>I</sub> <0 or V <sub>I</sub> >V <sub>DD</sub> )    | LIK /              | -50                  | 2 50                 | mA    |

| Output Clamp Current, dc (V <sub>I</sub> < 0 or V <sub>I</sub> > V <sub>DD</sub> ) | (I <sub>ok</sub> ) | <50                  | 50                   | mA    |

| Storage Temperature Range (non-condensing)                                         | Тs                 | -65                  | 150                  | °C    |

| Ambient Temperature Range, Under Bias                                              | Т_ 🔿               | -55                  | 125                  | °C    |

| Junction Temperature                                                               | TJ                 | $\mathcal{S}$        | 125                  | °C    |

| Lead Temperature (soldering, 10s)                                                  | $\mathbb{S}$       | $\checkmark$         | 260                  | °C    |

| Input Static Discharge Voltage Protection (MIL-STD 883E, Method 3015.7)            |                    |                      | 2                    | kV    |

#### CAUTION: ELECTROSTATIC SENSITIVE DEVICE

Permanent damage resulting in a loss of functionality or performance may occur if this device is subjected to a high-energy electrostatic discharge.

### Table 4: Operating Conditions

| PARAMETER                              | SYMBOL               | CONDITIONS/DESCRIPTION | MIN. | TYP. | MAX. | UNITS |

|----------------------------------------|----------------------|------------------------|------|------|------|-------|

| Supply Voltage                         | VDD                  | 3.3V ± 10%             | 3.0  | 3.3  | 3.6  | V     |

| Ambient Operating Temperature Range    | T₄                   |                        | 0    |      | 70   | °C    |

| Crystal Resonator Frequency            | f <sub>XTAL</sub>    | Fundamental Mode       | 5    | 13.5 | 18   | MHz   |

| Crystal Resonator Motional Capacitance | C <sub>1(xtal)</sub> | AT cut                 |      | 25   |      | fF    |

| Crystal Loading Capacitance            | $C_{L(xtal)}$        | AT cut                 |      | 20   |      | pF    |

#### **Table 5: DC Electrical Specifications**

COLLEGO

Unless otherwise stated,  $V_{DD} = 3.3V \pm 10\%$ , no load on any output, and ambient temperature range  $T_A = 0^{\circ}C$  to 70°C. Parameters denoted with an asterisk ( ) represent nominal characterization data and are not production tested to any specific limits. Where given, MIN and MAX characterization data are  $\pm 3\sigma$  from typical. Negative currents indicate current flows out of the device.

| PARAMETER                                       | SYMBOL               | CONDITIONS/DESCRIPTION                                                     | MIN.                        | түр. | MAX. | UNITS |

|-------------------------------------------------|----------------------|----------------------------------------------------------------------------|-----------------------------|------|------|-------|

| Overall                                         |                      |                                                                            | $\langle \langle C \rangle$ | ソ    |      |       |

| Supply Current, Dynamic, with Loaded<br>Outputs | I <sub>DD</sub>      | f <sub>XTAL</sub> = 13.5MHz; C <sub>L</sub> = 10pF, V <sub>DD</sub> = 3.6V | $\langle \rangle \rangle$   | 30   |      | mA    |

| Supply Current, Static                          | I <sub>DD</sub>      | XIN = 0V, V <sub>DD</sub> = 3.6V                                           | $\vee$                      | 3    |      | mA    |

| Voltage Controlled Crystal Oscillator           |                      |                                                                            |                             |      |      |       |

| Crystal Loading Capacitance                     | C <sub>L(xtal)</sub> | As seen by a crystal connected to XIN and XOUT (@ $V_{XTUNE} = 1V$ )       | 6                           | 20   |      | pF    |

| Crystal Resonator Motional Capacitance          | C <sub>1(xtal)</sub> | AT cut                                                                     | $\langle \rangle$           | 25   |      | fF    |

| VCXO Tuning Range                               |                      | $f_{XTAL} = 13.5 MHz; C_{L(xtal)} = 20pF; C_{1(xtal)} = 25 fF$             | $\mathbb{N}$                | 300  |      | ppm   |

| VCXO Tuning Characteristic                      |                      | Note: positive change of XTUNE ≠ positive change of VCXO frequency         |                             | 150  |      | ppm/V |

| Crystal Drive Level                             |                      | $R_{XTAL}=20\Omega; C_L=20pF$                                              | $\mathcal{D}$               | 200  |      | uW    |

| Clock Output (CLK)                              |                      |                                                                            |                             |      |      |       |

| High-Level Output Source Current *              | I <sub>он</sub>      | V6=2.0V                                                                    |                             | -40  |      | mA    |

| Low-Level Output Sink Current *                 | loy                  | V <sub>0</sub> = 0.4V                                                      |                             | 17   |      | mA    |

| Output langed an ex *                           | ZOH                  | $V_{O} = 0.1 V_{DD}$ ; output driving high                                 |                             | 25   |      | 0     |

| Output Impedance *                              | ZOL                  | $V_{O} = 0.1 V_{DD}$ ; output driving low                                  |                             | 25   |      | Ω     |

| Short Circuit Source Current *                  | V <sub>OSH</sub>     | $V_0 = 0V$ ; shorted for 30s, max.                                         |                             | -55  |      | mA    |

| Short Circuit Sink Current *                    | HOSL                 | $V_0 = 3.3V$ ; shorted for 30s, max.                                       |                             | 55   |      | mA    |

#### **Table 6: AC Timing Specifications**

Unless otherwise stated,  $V_{DD}$  = 3.3V ± 10%, no load on any output, and ambient temperature range  $T_A$  = 0°C to 70°C. Parameters denoted with an asterisk ( ) represent nominal characterization data and are not production tested to any specific limits. Where given, MIN and MAX characterization data are ± 3 $\sigma$  from typical.

| $\frac{t_{VCXOSTB}}{t_{PLLSTB}}$ $t_{j(\Delta P)}$ $t_{j(LT)}$ $t_{r}$ $t_{r}$ | From power validFrom VCXO stable(unless otherwise noted in Frequency Table)Ratio of high pulse width (as measured from rising<br>edge to next falling edge at $V_{DD}/2$ ) to one clock periodFrom rising edge to next rising edge at $V_{DD}/2$ ,<br>$C_L = 10pF$ From 0-500µs at $V_{0D}/2$ , $C_L = 10pF$ From 0-500µs at $V_{0D}/2$ , $C_L = 10pF$ VDD = 3.3V; $V_0 = 0.8V$ to 3.0V; $C_L = 10pF$ VDD = 3.3V; $V_0 = 0.8V$ to 0.3V; $C_L = 10pF$ | 10<br>500<br>390<br>155<br>1.7<br>1.7 | 55 | ms<br>us<br>ppm<br>%<br>ps<br>ps<br>ps<br>ns<br>ns |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----|----------------------------------------------------|

| $t_{PLLSTB}$<br>$t_{j(\Delta P)}$<br>$t_{j(LT)}$<br>$t_{r}$                    | From VCXO stable         (unless otherwise noted in Frequency Table)         Ratio of high pulse width (as measured from rising edge to next falling edge at $V_{DD}/2$ ) to one clock period         From rising edge to next rising edge at $V_{DD}/2$ , $C_L = 10pF$ From 0-500µs at $V_{0D}/2$ , $C_L = 10pF$ VDD = 3.3V; $V_0 = 0.8V$ to 3.0V; $C_L = 10pF$                                                                                     | 500<br>390<br>155<br>1.7              |    | us<br>ppm<br>%<br>ps<br>ps<br>ns                   |

| t <sub>j(ΔP)</sub><br>t <sub>j(LT)</sub><br>t <sub>r</sub>                     | (unless otherwise noted in Frequency Table)Ratio of high pulse width (as measured from rising<br>edge to next falling edge at $V_{DD}/2$ ) to one clock periodFrom rising edge to next rising edge at $V_{DD}/2$ ,<br>$C_L = 10pF$ From 0-500µs at $V_{0D}/2$ , $C_L = 10pF$ compared to ideal clock source $V_{DD} = 3.3V$ ; $V_Q = 0.8V$ to $3.0V$ ; $C_L = 10pF$                                                                                  | 390<br>155<br>1.7                     |    | ppm<br>%<br>ps<br>ps<br>ns                         |

| t <sub>j(LT)</sub>                                                             | Ratio of high pulse width (as measured from rising<br>edge to next falling edge at $V_{DD}/2$ ) to one clock period45From rising edge to next rising edge at $V_{DD}/2$ ,<br>$C_L = 10pF$ 7From 0-500 µs at $V_{DD}/2$ , $C_L = 10pF$ 7V_{DD} = 3.3V; $V_Q = 0.8V$ to 3.0V; $C_L = 10pF$                                                                                                                                                             | 390<br>155<br>1.7                     |    | %<br>ps<br>ps<br>ns                                |

| t <sub>j(LT)</sub>                                                             | edge to next falling edge at $V_{DD}/2$ to one clock period<br>From rising edge to next rising edge at $V_{DB}/2$ ,<br>$C_L = 10pF$<br>From 0-500µs at $V_{0D}/2$ , $C_L = 10pF$<br>compared to ideal clock source<br>$V_{DD} = 3.3V$ ; $V_Q = 0.8V$ to 3.0V; $C_L = 10pF$                                                                                                                                                                           | 390<br>155<br>1.7                     | 55 | ps<br>ps<br>ns                                     |

| t <sub>j(LT)</sub>                                                             | edge to next falling edge at $V_{DD}/2$ to one clock period<br>From rising edge to next rising edge at $V_{DB}/2$ ,<br>$C_L = 10pF$<br>From 0-500µs at $V_{0D}/2$ , $C_L = 10pF$<br>compared to ideal clock source<br>$V_{DD} = 3.3V$ ; $V_Q = 0.8V$ to 3.0V; $C_L = 10pF$                                                                                                                                                                           | 390<br>155<br>1.7                     | 55 | ps<br>ps<br>ns                                     |

| t <sub>j(LT)</sub>                                                             | $C_{L} = 10 \text{pF}$ From 0-500 µs at V <sub>0D</sub> /2, $C_{L} = 10 \text{pF}$ compared to ideal clock source $V_{DD} = 3.3 \text{V}; V_{Q} = 0.8 \text{V} \text{ to } 3.0 \text{V}; C_{L} = 10 \text{pF}$                                                                                                                                                                                                                                       | 155<br>1.7                            |    | ps<br>ns                                           |

| tr                                                                             | compared to ideal clock source $V_{DD} = 3.3V; V_O = 0.8V$ to 3.0V; $C_L = 10pF$                                                                                                                                                                                                                                                                                                                                                                     | 1.7                                   |    | ns                                                 |

|                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |    | -                                                  |

| t <sub>f</sub>                                                                 | $V_{DD} = 3.3V; V_0 = 3.0V$ to 0.3V; $C_L = 10pF$                                                                                                                                                                                                                                                                                                                                                                                                    | 1.7                                   |    | ns                                                 |

|                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |    | -                                                  |

|                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |    |                                                    |

|                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |    |                                                    |

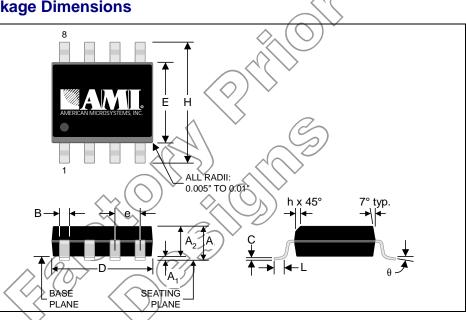

### 5.0 Package Information

### Table 7: 8-pin SOIC (0.150") Package Dimensions

|    |           | DIMEN  | SIONS       |            |  |

|----|-----------|--------|-------------|------------|--|

|    | INC       | HES    | MILLIMETERS |            |  |

|    | MIN.      | MAX.   | MIN.        | MAX.       |  |

| А  | 0.061     | 0.068  | 1.55        | 1.73       |  |

| A1 | 0.004     | 0.0098 | 0.102       | 0.249      |  |

| A2 | 0.055     | 0.061  | 1.40        | 1.55       |  |

| В  | 0.013     | 0.019  | 0.33        | 0.49       |  |

| С  | 0.0075    | 0.0098 | 0.191       | 0.249      |  |

| D  | 0.189     | 0.196  | 4.80        | 4.98       |  |

| Е  | 0.150     | 0.157  | 3.81        | 3.99       |  |

| е  | 0.050 BSC |        | 1.27        | BSC        |  |

| Н  | 0.230     | 0.244  | 5.84        | 6.20       |  |

| h  | 0.010     | 0.016  | 0.25        | 0.41       |  |

| L  | 0.016     | 0.035  | 0.41        | 0.89       |  |

| Θ  | 0°        | 8°     | 0°          | <b>8</b> ° |  |

## Table 8: 8-pin SOIC (0.150") Package Characteristics

| PARAMETER                                                    | SYMBOL            |                               | TYP. | UNITS |

|--------------------------------------------------------------|-------------------|-------------------------------|------|-------|

| Thermal Impedance, Junction to Free-Air<br>8-pin 0.150" SOIC | ALO               | Air flow = 0 m/s              | 110  | °C/W  |

| Lood Inductorian Calif                                       |                   | Corner lead                   | 2.0  | - nH  |

| Lead Inductance, Self                                        | 11                | Center lead                   | 1.6  |       |

| Lead Inductance, Mutual                                      | ) L <sub>12</sub> | Any lead to any adjacent lead | 0.4  | nH    |

| Lead Capacitance, Bulk                                       | C <sub>11</sub>   | Any lead to V <sub>SS</sub>   | 0.27 | pF    |

|                                                              |                   |                               |      |       |

### 6.0 Ordering Information

#### Table 9: Device Ordering Codes

|               |               |                                                |                                | $\searrow$                |

|---------------|---------------|------------------------------------------------|--------------------------------|---------------------------|

| ORDERING CODE | DEVICE NUMBER | PACKAGE TYPE                                   | OPERATING<br>TEMPERATURE RANGE | SHIPPING<br>CONFIGURATION |

| 11640-101     | FS6128-01     | 8-pin (0.150") SOIC<br>(Small Outline Package) | 0°C to 70°C (Commercial)       | Tape and Reel             |

| 11640-111     | FS6128-01     | 8-pin (0.150") SOIC<br>(Small Outline Package) | 0°C to 70°C (Commercial)       | Tubes                     |

|               |               |                                                |                                | 1                         |

$\mathcal{S}$

### 7.0 Revision Information

| DATE    | PAGE | DESCRIPTION             |

|---------|------|-------------------------|

| 4/24/00 | 5, 7 | Fixed formatting errors |

|         |      |                         |

#### Copyright © 2000 American Microsystems, Inc.

Devices sold by AMI are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. AMI makes no warranty, express, statutory implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. AMI makes no warranty of merchantability or fitness for any purposes. AMI reserves the right to discontinue production and change specifications and prices at any time and without notice. AMI's products are intended for use in commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment, are specifically not recommended without additional processing by AMI for such applications.

American Microsystems, Inc., 2300 Buckskin Rd., Pocatello, ID 83201, (208) 233-4690, FAX (208) 234-6796, WWW Address: <u>http://www.amis.com</u> E-mail: <u>tgp@amis.com</u>