# **AK8823**

# HDTV & NTSC/PAL Multi-Format Encoder SDTV/HDTV x2 OverSampling 5ch DACs

## **General Description**

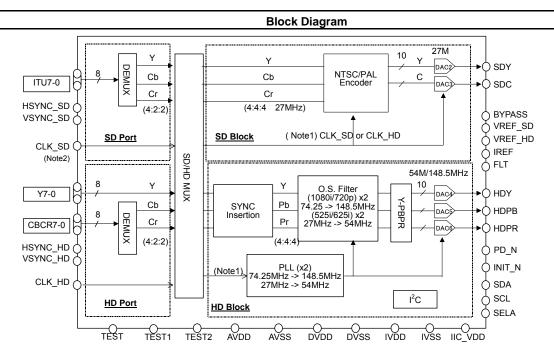

The AK8823 is a HD / SD Simultaneous Output Video Encoder with on-chip 5 Channel 10 Bit DACs.

As input data, in SD block, SMPTE-125M-1995 / ITU-R BT. 601, 656 compatible Y / Cb / Cr 4:2:2 formats ( 8 bit ) are accepted and, in HD block, SMPTE-274M-1998 ( 1080i ), SMPTE-296M-2001 ( 720p ) compatible Y / Cb / Cr 4:2:2 formats ( 8 bit x 2 ) are accepted.

As input data capture method, <u>either</u> a Synchronous mode to be made by detecting encoded EAV signal <u>or</u> a mode to synchronize with externally-fed H / V SYNC signals is selectable.

Outputs of SDY / SDC and HDY / HDPB / HDPR signals can be independently controlled by turning ON /OFF corresponding DACs.

VBI signal and Macrovision signal can be also superimposed on output in addition to Video signals, by register setting.

## **Features**

HD

Compatible input data : SMPTE125M-1995 / ITU-R BT601(525i/625i)

SMPTE274M-1998 (1080i) SMPTE296M-2001 (720p)

• Input Signal Formats : Y/Cb/Cr 4:2:2 (8bit x 2)

- 525i / 625i- 525p / 625p- 1080i / 720p

(note) ITU-R656-4 compatible mode in 525i / 625i formats

Output Signals : Y/Pb/Pr Interlace (EIA 770.1-A) (EIA 770.3-A)

Y/Pb/Pr Progressive (EIA 770.2-A) (EIA 770.3-A)

On chip out-put limiter

• Input Signal Synchronization : - EAV Decode (\*)

- Slave Operation by HSYNC / VSYNC signals

- VBID ( CGMS-A ), CC / XDS, WSS

- Macrovision 525i / 625i Rev. 7.1.1L and 525p / 625p Macrovision Progressive 1.2

- On-Chip Color Bar Generator

- On-Chip Black Burst Generator

- Adjustable YPbPr Delay Function

#### SD NTSC/PAL Encoder

- NTSC-M, PAL-B, D, G, H, I. M, N Encoding

- S-Video Output

- On-chip out-put limiter

- ITU-R BT.656, 4:2:2, 8 Bit Parallel Input (EAV Decoding)

- Slave Operation by HSYNC / VSYNC Signals

- •VBID (CGMS-A), CC/XDS, WSS

- Macrovision Anti-Taping Rev. 7.1.1L

- I2C Bus I / F ( 400 KHz )

- Power-Down Mode

- On-Chip VREF

- 3.0 V, 1.8 V CMOS

- 65 Pin BGA

<sup>(\*)</sup> Violation of EAV decode is on 625p video mode. Refers to p.38.

SD Side Input Video Port and HD Side Input Video Port are independently equipped.

525i / 625i signals on SD Input Port can be processed at HD Block ,or D1 signal on HD Input Port can be processed at SD Block.

(Note 1) in the Block diagram, denotes a clock to be used internally.

Either of the two Ports can be selected by register setting. A clock in the selected Port is used which is assigned by bit 7 VPRTSD of Video Process 4 Register at address 0x14 for SD Block or bit 5 VPRT of HD DAC Control Register at address 0x05 for HD Block. Video Signal is processed in the same manner. (Note 2) When video data on HD port is transferred to SD block, the same clock in CLK\_HD pin must be fed to CLK\_SD pin.

MS0549-E-02 2 2006/10

# **Table Of Contents**

| 1. Electrical Characteristics                                                    | 4                       |

|----------------------------------------------------------------------------------|-------------------------|

| 2. Pin Functional Description                                                    | 8                       |

| 3. Pin Layout                                                                    | 10                      |

| 4. Video Signal Filter HD (HDY/HDPbPr) / SD ( SDY )                              | 11                      |

| 5. CbCr ( 4:2:2 → 4:4:4 ) Filter (SD )                                           |                         |

| 6. C x2 Filter (SD)                                                              |                         |

| 7. Video Input / Output Outline                                                  |                         |

| 8. PLL function                                                                  |                         |

| 9. Video DAC                                                                     |                         |

| 10. Operation Mode [ HD Control ]                                                |                         |

| 11. Operation Mode [ SD Control ]                                                |                         |

| 12. Power-Down                                                                   |                         |

| 13. Initialization                                                               |                         |

| 14. Power-up Sequence                                                            |                         |

| 15. HD Block                                                                     |                         |

| 15-1. Video Interface Timing (HD)                                                |                         |

| (1) 525i (480i) / 60Hz (HD)                                                      |                         |

| (2) 625i(576i) / 50Hz HD                                                         |                         |

| (3) 525p(480p) / 60Hz : HD                                                       |                         |

| (4) 625p(576p) / 50Hz : HD                                                       |                         |

| (5) 1080i / 60Hz : HD                                                            |                         |

| (6) 1080i / 50Hz : HD                                                            |                         |

| (7) 720p / 60Hz : HD                                                             |                         |

| (8) 720p / 50Hz : HD                                                             |                         |

| 15-2. Signal Relations in EAV Decoding                                           |                         |

| 15-3. Setting Functions of V-Blank Interval and Output Mode ( HD )               |                         |

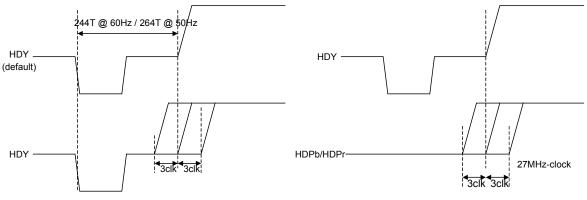

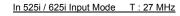

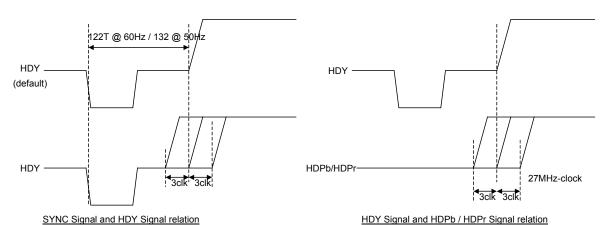

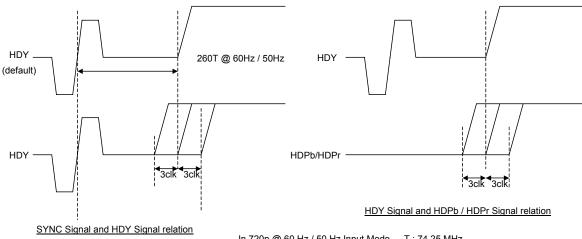

| 15-4. Adjustable Timing Function Between SYNC Signal and HDY Signal, and Between | en HDPB Signal and HDPR |

| Signal ( HD )                                                                    | 42                      |

| 15-5. Set-Up Process Function ( HD )                                             | 43                      |

| 15-6. On chip out-put Video Limiter ( HD, SD Modes )                             | 43                      |

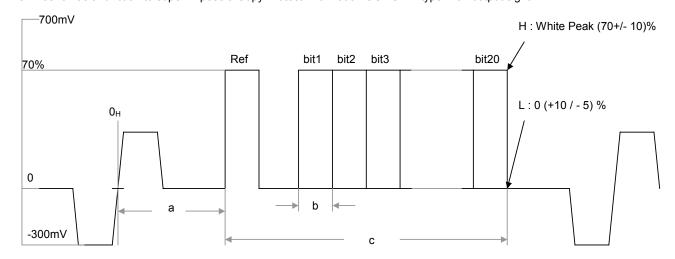

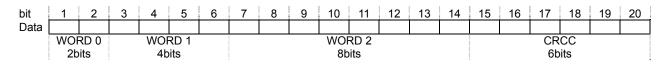

| 15-7. Black Burst Signal Generator Function ( HD )                               |                         |

| 15-8. Color Bar Signal Generator Function ( HD )                                 |                         |

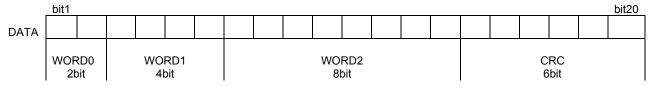

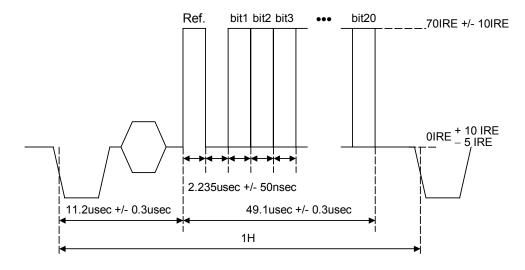

| 15-9. Video ID(HD)                                                               |                         |

| 15-10. Closed Caption(HD)                                                        |                         |

| 15-11. WSS Function ( HD D1/50Hz )                                               |                         |

| 16. SD Block                                                                     |                         |

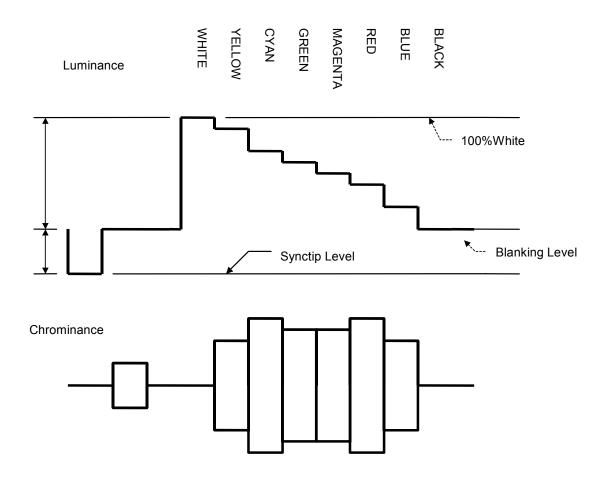

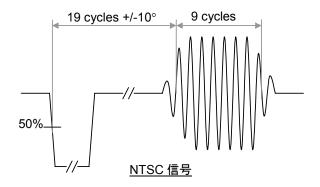

| 16-1. Color Burst Signal ( SD )                                                  |                         |

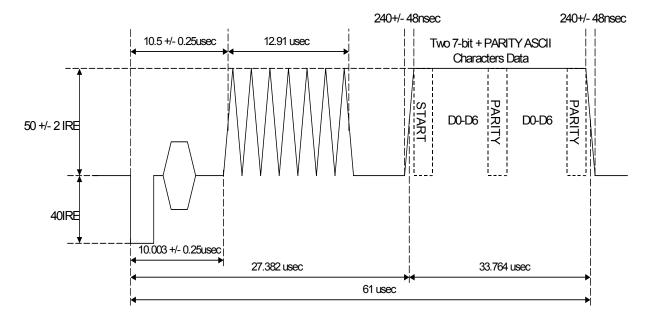

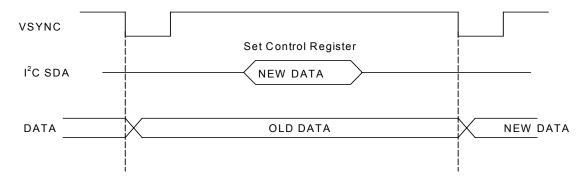

| 16-2. Closed Caption(SD)                                                         |                         |

| 16-3. Video ID ( SD )                                                            |                         |

| 16-4. WSS Function (SD)                                                          |                         |

| 16-5. Slave Mode ( SD )                                                          |                         |

| 16-6. On-chip Color Bar ( SD )                                                   |                         |

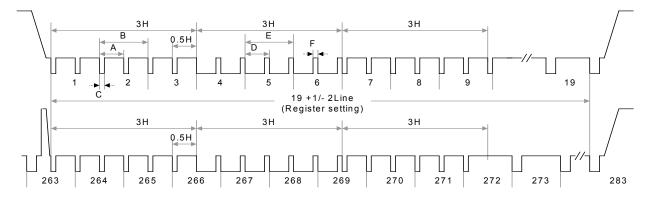

| 16-7. Black Burst Signal Generator Function (SD)                                 |                         |

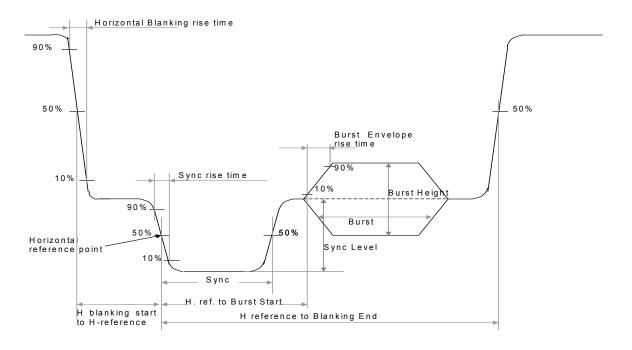

| 16-8. SYNC Signal Waveform . Burst Waveform ( SD )                               |                         |

| 17. Device Control Interface                                                     |                         |

| 18. Register Map                                                                 |                         |

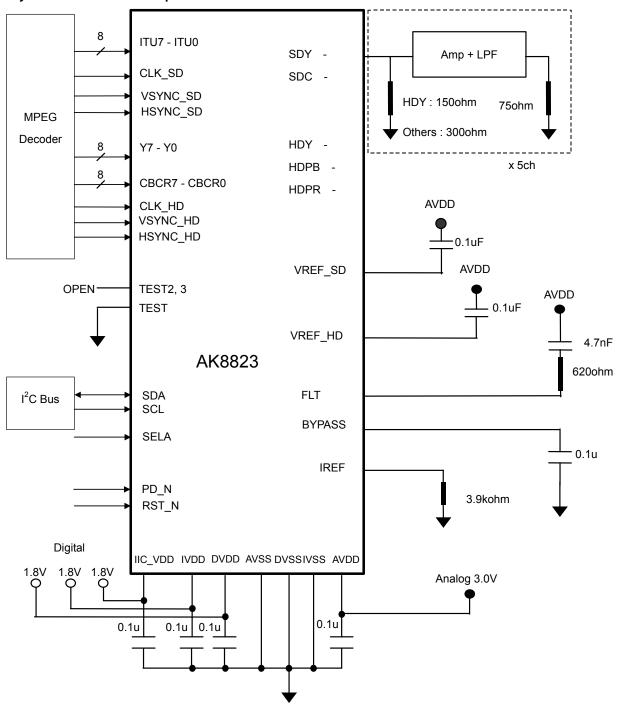

| 19. System Connection Example                                                    |                         |

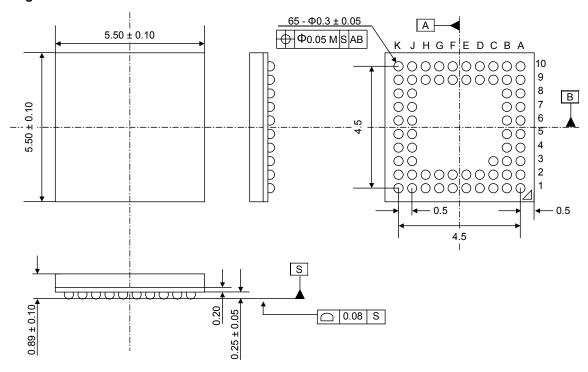

| 20. Package Outline Dimensions                                                   |                         |

| 21. Package Marking                                                              | 79                      |

#### 1. Electrical Characteristics

Absolute Maximum Ratings (all voltages are referenced to ground level, AVSS = DVSS = 0V)

| Item                                                                                                            | Min. | Max.                        | Units |

|-----------------------------------------------------------------------------------------------------------------|------|-----------------------------|-------|

| Power Supplies (VDD)  AVDD (DAC,PLL, VREF)  DVDD (Digital Core)  IVDD (Digital I/O)  IIC_VDD (I2C Power Supply) | -0.3 | 4.2<br>2.2<br>2.2<br>4.2    | ٧     |

| Input Pin Voltage (VIN)                                                                                         | -0.3 | IVDD + 0.3<br>IIC_VDD + 0.3 | V     |

| Input Current (IIN)                                                                                             |      | +/- 10                      | mA    |

| Storage Temperature                                                                                             | -40  | 125                         | °C    |

( note ) Operation under a condition exceeding above limits may cause permanent damage to the device. Normal operation is not guaranteed under the above, extreme conditions.

**Recommended Operating Conditions**

| Item                       | Min. | Тур. | Max. | Units |

|----------------------------|------|------|------|-------|

| Power Supply (VDD)         |      |      |      |       |

| AVDD                       | 2.66 | 3.0  | 3.45 | \/    |

| DVDD = IVDD                | 1.65 | 1.8  | 2.0  | V     |

| IIC_VDD                    | DVDD | 1.8  | 3.45 |       |

| Operating Temperature (TA) | -20  |      | 85   | °C    |

Analog Characteristics and Power Dissipation (AVDD = 3.0V, DVDD = IVDD = IIC VDD = 1.8V, Ta= 25°C)

| Item                                 | Min. | Тур.       | Max. | Units  | Condition                                             |

|--------------------------------------|------|------------|------|--------|-------------------------------------------------------|

| DAC Resolution                       |      | 10         |      | bit    |                                                       |

| Integral Non-Linearity Error INL     |      | +/- 1.5    |      | LSB    | note 1)                                               |

| Differential Non-Linearity Error DNL |      | +1.0/- 1.0 |      | LSB    | note 1)                                               |

| Output Full Scale Voltage            | 1.15 | 1.28       | 1.41 | V      | HDY output = 150 ohms,<br>all other outputs= 300 ohms |

| DAC SNR                              |      | 70         |      | dB     | 50 % Gray Scale                                       |

| Output Bandwidth                     |      | +/- 1      |      | dB     | note 2)                                               |

| Variations among DACs                |      | 1.5        | TBD  | %      | note 3)                                               |

| On-Chip Reference Voltage            |      | 1.43       |      | V      |                                                       |

| Reference Voltage Drift              |      | 350        |      | ppm/°C |                                                       |

| Current Consumption of Analog part   |      | 49         | 70   | mA     | note 4)                                               |

| Current Consumption of Digital part  |      | 50         | 79   | mA     | note 4)                                               |

| Power-Down Current                   |      | 100        | 1000 | uA     | PD_N : at " L " setting note 5 )                      |

note 1 ) operation at HD DAC : 148 MHz, SD DAC : 27 MHz

(AVDD = 2.66 ~ 3.45V, IVDD = DVDD = 1.65 ~ 2.0V, IIC VDD = DVDD ~ 3.45V, Ta= -20~ 85°C)

| Item                         | Symbol | Condition                                                                                           | Min.        | Тур. | Max.        | Units |

|------------------------------|--------|-----------------------------------------------------------------------------------------------------|-------------|------|-------------|-------|

| High Level Input Voltage     | VIH    | ITU7-0, Y7-0, CBCR7-0 CLK_SD, CLK_HD HSYNC_SD, VSYNC_SD HSYNC_HD, VSYNC_HD INIT_N, PD_N             | 0.77IVDD    |      |             | ٧     |

| Low Level Input Voltage      | VIL    | ITU7-0, Y7-0, CBCR7-0<br>CLK_SD, CLK_HD<br>HSYNC_SD, VSYNC_SD<br>HSYNC_HD, VSYNC_HD<br>INIT_N, PD_N |             |      | 0.21IVDD    | V     |

| Input pin Leakage Current    | ILIKG  | I2C and digital input pins (test pins excluded)                                                     |             |      | +/-10       | uA    |

| I2C High Level Input Voltage | VIH2   | SELA, SDA, SCL                                                                                      | 0.77IIC_VDD |      |             | V     |

| I2C Low Level Input Voltage  | VIL2   | SELA, SDA, SCL                                                                                      |             |      | 0.21IIC_VDD | V     |

| I2C Low Level Output Voltage | VOL2   | SDA, IOL = 3mA                                                                                      |             |      | 0.4         | V     |

note 2 ) Output Bandwidth 30 MHz : at 148 MHz operation, HDY ( load resistor at 150 ohms ) channel only, external load capacitance (  $\mathsf{TBD}\ \mathsf{pF}\ \mathsf{pF}$  )

note 3) variation when a 700 mV equivalent code is input on DACs. Specified in each of SD and HD groups.

note 4 ) DAC 5 channels "ON" (SD: on-chip color bar HD: 30 MHz - 1 dB FS)

note 5 ) values are after initialization of internal filter by either INT\_N or by register setting, and before the Power-down. Digital Input / Output DC Characteristics

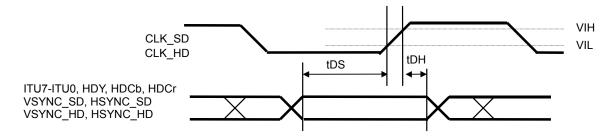

## **AC Timing**

$(AVDD = 2.66V \sim 3.45V, DVDD = IVDD = 1.65V \sim 2.0V, Ta = -20 \sim +85^{\circ}C)$

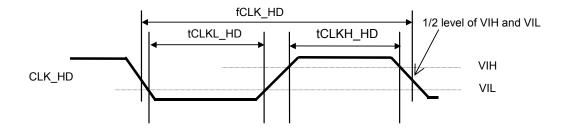

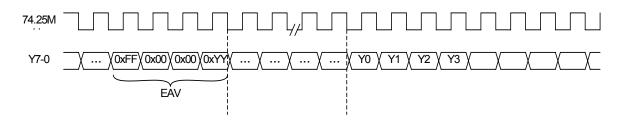

## (1) CLK\_HD at 74.25 MHz operation

| Item                 | Symbol   | Min. | Тур.  | Max. | Units | Condition         |

|----------------------|----------|------|-------|------|-------|-------------------|

| CLK_HD               | fCLK_HD  |      | 74.25 |      | MHz   | 74.25 / 74.175MHz |

| CLK_HD pulse width H | tCLKH_HD | 4.04 |       |      | nsec  |                   |

| CLK_HD pulse width L | tCLKL_HD | 4.04 |       |      | nsec  |                   |

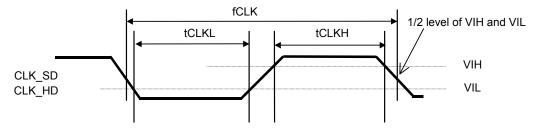

## (2) CLK\_SD / CLK\_HD t 27 MHz operation

| Item                          | Symbol                      | Min. | Тур. | Max. | Units | Condition      |    |  |        |                   |

|-------------------------------|-----------------------------|------|------|------|-------|----------------|----|--|--------|-------------------|

| CLK_SD                        | fCLK_SD                     |      | 27   |      | MHz   | 27MHz ( note ) |    |  |        |                   |

| CLK_HD                        | fCLK_HD                     |      | 21   | 21   | 21    | 21             | 21 |  | IVITIZ | 27 WIFIZ ( Hote ) |

| CLK_SD / CLK_HD pulse width H | th H tCLKH_SD 15.0          |      |      | ncoo |       |                |    |  |        |                   |

| CLK_SD / CLK_HD pulse width H | tCLKH_HD                    | 15.0 |      |      | nsec  |                |    |  |        |                   |

| CLK SD / CLK HD pulse width I | pulse width L tCLKL_SD 15.0 |      | naaa |      |       |                |    |  |        |                   |

| CLK_SD / CLK_HD pulse width L | tCLKL_HD                    | 15.0 |      |      | nsec  |                |    |  |        |                   |

( note ) if this frequency shifts, color is not retrieved in SD mode in a display monitor. The AK8823 operation is not affected, though.

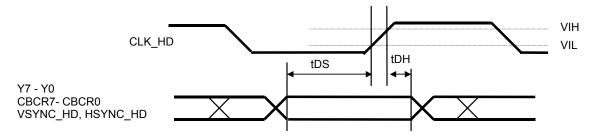

## (3) Pixel Data Input Timing -- (1) at 74.25 MHz clock operation

| Parameter        | Symbol | Min. | Тур. | Max. | Unit |

|------------------|--------|------|------|------|------|

| Data Set-up Time | tDS_HD | 4.4  |      |      | nsec |

| Data Hold Time   | tDH_HD | 1.45 |      |      | nsec |

( note ) polarities of VSYNC\_HD, HSYNC\_HD are pre-settable by register [ Address 0x05 bit 6 HVINV ].

## (4) Pixel Data Input Timing (2) at 27 MHz clock operation

( note ) polarities of VSYNC\_HD, HSYNC\_HD are pre-settable by register [ Address 0x05 bit 6 HVINV ].

| Parameter        | Symbol | Min. | Тур. | Max. | Unit |

|------------------|--------|------|------|------|------|

| Data Sat un Tima | tDS_SD | 5.0  |      |      | nsec |

| Data Set-up Time | tDS_HD |      |      |      |      |

| Data Hald Time   | tDH_SD | 5.0  |      |      | nsec |

| Data Hold Time   | tDH_HD |      |      |      |      |

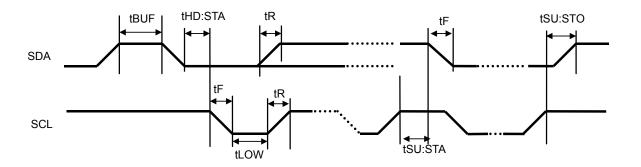

(5) I2C Timing (5-1) Timing 1

| Parameter                   | Symbol  | Min. | Max. | Unit |

|-----------------------------|---------|------|------|------|

| Bus Free Time               | tBUF    | 1.3  |      | usec |

| Hold Time (Start Condition) | tHD:STA | 0.6  |      | usec |

| Clock Pulse Low Time        | tLOW    | 1.3  |      | usec |

| Input Signal Rise Time      | tR      |      | 300  | nsec |

| Input Signal Fall Time      | tF      |      | 300  | nsec |

| Setup Time(Start Condition) | tSU:STA | 0.6  |      | usec |

| Setup Time(Stop Condition)  | tSU:STO | 0.6  |      | usec |

The above I2C Bus related timings are I2C Bus specifications, and they are not the device limits. For details, refer to I2C Bus Specifications.

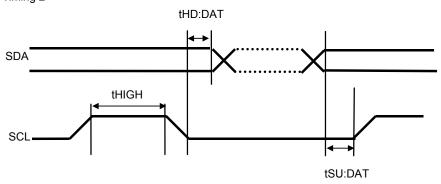

## (5-1) Timing 2

| Parameter             | Symbol  | Min.        | Max.        | Unit |

|-----------------------|---------|-------------|-------------|------|

| Data Setup Time       | tSU:DAT | 100 (note1) |             | nsec |

| Data Hold Time        | tHD:DAT | 0.0         | 0.9 (note2) | usec |

| Clock Pulse High Time | tHIGH   | 0.6         |             | usec |

note 1 : when to use in I2C Bus Standard mode, tSU : DAT > = 250nsec must be satisfied.

note 2 : when the AK8823 is used on the not-extended tLOW Bus ( used at tLOW = minimum specification ), this condition must be satisfied.

No external clock is required to write into / read from registers via I2C interface.

Each operation completes with SCL clock only.

However, a 27MHz clock is required to enable SD block when to access such registers in SD block as VBID / CC / WSS (Addresses  $0x18,0x19,0x26 \sim 0x2B$ ) and Status (at 0x34).

When a 27 MHz clock is stopped once and when to access those registers again, it should be executed after waiting 2 Frame time after the recovery of clock.

# 2. Pin Functional Description

| ITU7                                                                                                                    |                    |  |  |

|-------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|

| ITU5                                                                                                                    |                    |  |  |

| ITU4                                                                                                                    |                    |  |  |

| ITU3                                                                                                                    |                    |  |  |

| ITU2 J6 J4                                                                                                              |                    |  |  |

|                                                                                                                         |                    |  |  |

|                                                                                                                         |                    |  |  |

| ITU1 K3                                                                                                                 |                    |  |  |

| ITU0 J3                                                                                                                 |                    |  |  |

| Y7 D10                                                                                                                  |                    |  |  |

| Y6 D9                                                                                                                   |                    |  |  |

| Y5 F9                                                                                                                   |                    |  |  |

| Y4 I G10 IVDD Y Data Input pins in HD Block mode                                                                        |                    |  |  |

| Y3   1   G9   1   Data Input pins in AD Block fillode                                                                   |                    |  |  |

| Y2 H10                                                                                                                  |                    |  |  |

| Y1 H9                                                                                                                   |                    |  |  |

| Y0 J10                                                                                                                  |                    |  |  |

| CBCR7 B3                                                                                                                |                    |  |  |

| CBCR6 A4                                                                                                                |                    |  |  |

| CBCR5 B4                                                                                                                |                    |  |  |

| CBCR4 I A5 IVDD Cb / Cr Time-Division ( multiplexed ) Data Input pins                                                   |                    |  |  |

| CBCR3 I B5 IVDD Cb / Cr Time-Division ( multiplexed ) Data Input pins                                                   | •                  |  |  |

| CBCR2 B9                                                                                                                |                    |  |  |

| CBCR1 B10                                                                                                               |                    |  |  |

| CBCB0 C10                                                                                                               |                    |  |  |

| CLK_SD I K8 IVDD Clock Input pin for SD Block. 27MHz                                                                    |                    |  |  |

| CLK_HD I A2 IVDD Clock Input pin for HD Block. 27MHz / 74.25( 74.12                                                     |                    |  |  |

| HSYNC_SD I K2 IVDD HSYNC Timing Input pin for SD Block in Slave Mode Connect to IVSS when not in use                    |                    |  |  |

| VSYNC_SD I J2 IVDD VSYNC Timing Input pin for SD Block in Slave Mode Connect to IVSS when not in use                    | e operation.       |  |  |

| HSYNC_HD I A7 IVDD HSYNC Timing Input pin for HD Block in Slave Mode Connect to IVSS when not in use                    | e operation.       |  |  |

| VSYNC_HD I B6 IVDD VSYNC Timing Input pin for HD Block in Slave Mode Connect to IVSS when not in use                    | e operation.       |  |  |

| BYPASS O H2 AVDD Output pin to output On-Chip VREF voltage. Should be connected to Analog ground via a capacitor.       | larger-than 0.1 uF |  |  |

| IREF O H1 AVDD Reference Current Output pin for DACs Should be connected to AVSS via a 3.9kohm (+/-1%                   | % ) resistor.      |  |  |

| FLT O B2 AVDD Filter pin for PLL                                                                                        | •                  |  |  |

| HDY O D1 AVDD DAC Output pin for Y signal in HD block                                                                   |                    |  |  |

| HDPB O D2 AVDD DAC Output pin for Pb signal in HD block                                                                 |                    |  |  |

| HDPR O C1 AVDD DAC Output pin for Pr signal in HD block                                                                 |                    |  |  |

| SDY O F1 AVDD DAC Output pin for S-pin Luminance signal in SD blo                                                       | ock                |  |  |

| SDC O F2 AVDD DAC Output pin for S-pin Chroma signal in SD block                                                        |                    |  |  |

| SCL I B7 IIC_VDD I2C Bus Clock pin                                                                                      |                    |  |  |

| SDA I/O A8 IIC_VDD I2C Bus Data pin                                                                                     |                    |  |  |

| SELA I B8 IIC_VDD I2C Bus Address Select pin Low : 40H High : 42H                                                       |                    |  |  |

| PD_N I C3 IVDD Power-Down Control pin. L : PDN, H : normal operat                                                       | tion               |  |  |

| INIT_N I A3 IVDD To initialize internal Digital filter. Initialization at "low To be pulled-up to IVDD when not in use. |                    |  |  |

| VREF_HD I C2 AVDD To be connected to AVDD via a 0.1 uF capacitor                                                        |                    |  |  |

| VREF_SD I G1 AVDD To be connected to AVDD via a 0.1 uF capacitor                                                        |                    |  |  |

| Pin name | I/O | Pin No.                | Power supply to used | Functional outline                                                                             |

|----------|-----|------------------------|----------------------|------------------------------------------------------------------------------------------------|

| IIC_VDD  | Р   | A9                     |                      | I2C power supply pin. Decoupling capacitor should be connected between this pin and IVSS pin   |

| IVDD     | Р   | J9                     |                      | Power Supply pin for I / O part                                                                |

| IVSS     | Р   | K9                     |                      | Ground pin for I / O part                                                                      |

| DVDD     | Р   | F10, K4                |                      | Digital Power Supply pins                                                                      |

| DVSS     | Р   | E9, E10, J5,<br>K5     |                      | Digital Ground pins                                                                            |

| AVDD     | Р   | E1                     |                      | Analog Power Supply pin                                                                        |

| AVSS     | Р   | E2, J1                 |                      | Analog Ground pins                                                                             |

| TEST2    | -   | B1                     |                      | left open                                                                                      |

| TEST3    | -   | G2                     |                      | left open                                                                                      |

| TEST     | 1   | A6                     |                      | Test pin Should be connected to IVSS. This pin has on-chip pull-down resistor ( 100kohm typ.). |

| NC       |     | A1, A10,<br>C9,K1, K10 |                      | NC pins. left open.                                                                            |

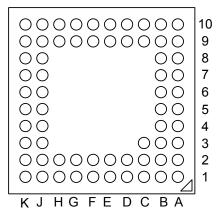

## 3. Pin Layout

Bottom view

#### Bottom view

|    | К        | J        | Н      | G       | F    | E    | D    | С       | В        | Α        |

|----|----------|----------|--------|---------|------|------|------|---------|----------|----------|

| 10 | NC       | Y0       | Y2     | Y4      | DVDD | DVSS | Y7   | CBCR0   | CBCR1    | NC       |

| 9  | IVSS     | IVDD     | Y1     | Y3      | Y5   | DVSS | Y6   | NC      | CBCR2    | IIC_VDD  |

| 8  | CLK_SD   | ITU7     |        |         |      |      |      |         | SELA     | SDA      |

| 7  | ITU6     | ITU5     |        |         |      |      |      |         | SCL      | HSYNC_HD |

| 6  | ITU4     | ITU3     |        |         |      |      |      |         | VSYNC_HD | TEST     |

| 5  | DVSS     | DVSS     |        |         |      |      |      |         | CBCR3    | CBCR4    |

| 4  | DVDD     | ITU2     |        |         |      |      |      |         | CBCR5    | CBCR6    |

| 3  | ITU1     | ITU0     |        |         |      |      |      | PD_N    | CBCR7    | INIT_N   |

| 2  | HSYNC_SD | VSYNC_SD | BYPASS | TEST3   | SDC  | AVSS | HDPB | VREF_HD | FLT      | CLK_HD   |

| 1  | NC       | AVSS     | IREF   | VREF_SD | SDY  | AVDD | HDY  | HDPR    | TEST2    | NC       |

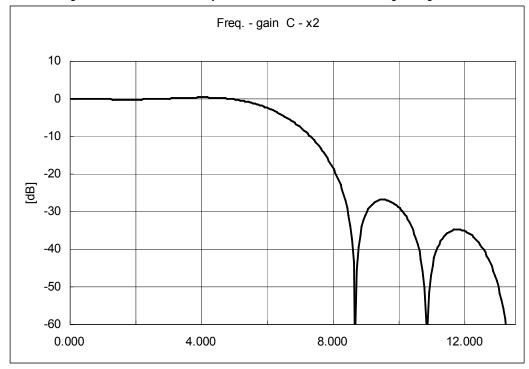

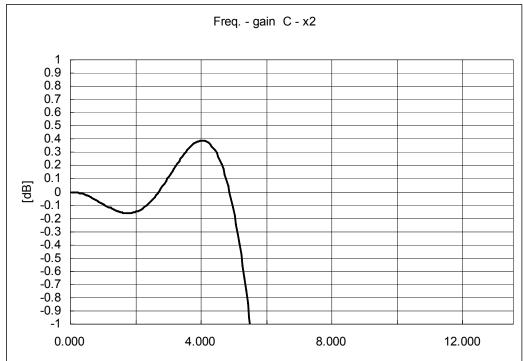

## 4. Video Signal Filter HD (HDY/HDPbPr) / SD ( SDY )

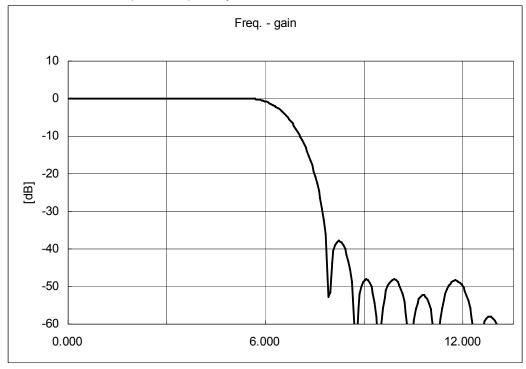

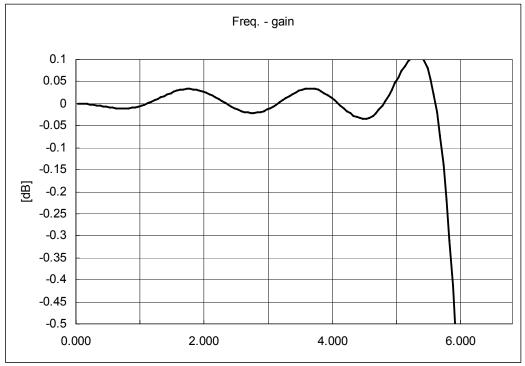

Shown below is an example of normal over-sampling Filter Characteristics for Y /Pb / Pr and RGB signals for HD, and Luma signal for SD (Figures below show a 13.5MHz example at the right-end frequency scale when Y signal and Luma signal in 525i mode are up-sampled to 27MHz).

Similarly, the right-end frequency scale should be read as 27MHz in 525p mode and 74.25MHz in 1080i / 720p respectively. As for PbPr signal case, the right-end frequency should be scaled to 6.75MHz in 525i / 625i mode, 13.5MHz in 525p / 625p mode, and 37.125MHz in 1080i / 720p mode respectively.

Filter Selection.

Above is the normal filter for Luminance signal pass, another two types filters, Mild and soft could be selected.

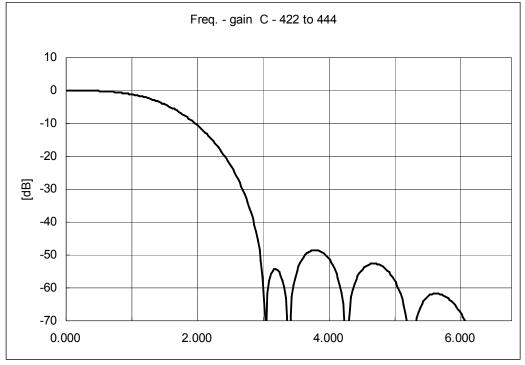

## 5. CbCr (4:2:2 → 4:4:4) Filter (SD)

A 6.75 MHz rate CbCr Data is rated up to 13.5 MHz.

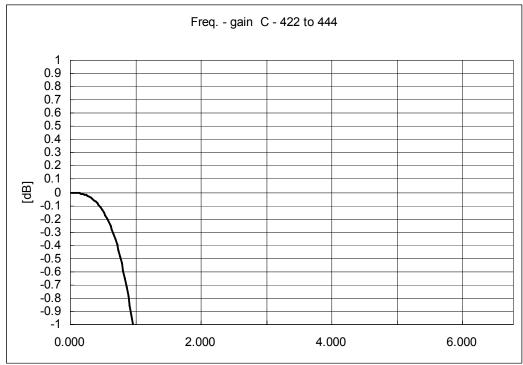

## 6. C x2 Filter (SD)

A 13.5 MHz rate CbCr signal is balance-modulated by the Color Sub-Carrier and the C signal is generated.

#### 7. Video Input / Output Outline

The AK8823 equips 8Bit SD Input Port ( SD Port ) at SD Block, and 16Bit HD Input Port ( HD Port ) at HD Block. Signal Capture Synchronization is selectable from 2 modes by register setting – one is to decode EAV code which is encoded on Input signal, or the other is to synchronize with HSYNC\_SD / VSYNC\_SD or HSYNC\_HD / VSYNC\_HD signals.

SD Block operation sets NTSC / PAL mode, and with HD Video input, input signal types ( SD / (525i / 625i) / (525p / 625p) / 1080i / 720p) and Frame Rates ( 50 Hz / 60 Hz) are set. Signals on SD Port can be transferred to HD Block by proper setting, and vice versa ( HD Port signal to SD Block is also possible ). But it is only true with D1 signal on HD Input Port (Note) When video data on HD port is transferred to SD block, the same clock in CLK\_HD pin must be fed to CLK\_SD pin.

#### (1) Input pin

| Input Format              | Bit | Input Pins   |

|---------------------------|-----|--------------|

| SD Port<br>(ITU-R.BT 656) | 8   | ITU7-ITU0    |

| HD Port                   | 16  | Y7-Y0        |

| HD POIL                   | 10  | CBCR7- CBCR0 |

#### (2) Input Rate

| ( - )      |                 |                      |       |

|------------|-----------------|----------------------|-------|

| Video Mode | Format          | CLK                  | Notes |

| SD Port    |                 |                      |       |

| NTSC/PAL   | 4:2:2           | 27MHz                |       |

| HD Port    |                 |                      |       |

| 525i/625i  | Y/CBCR 4:2:2    | 27MHz                |       |

| 1080i/720p | Y 4<br>CBCR 2:2 | 74.25MHz<br>74.25MHz |       |

The AK8823 can output SD Video and HD Video signals simultaneously.

| Input   |      |      | SD block  |

|---------|------|------|-----------|

| Iliput  | DAC2 | DAC3 | DAC_CLOCK |

| SD Port | SDY  | SDC  | 27MHz     |

| HD Port | SDY  | SDC  | 27MHz     |

|                | HD block |        |       |                        |  |  |  |  |  |

|----------------|----------|--------|-------|------------------------|--|--|--|--|--|

|                |          | Output |       | DAC CLOCK              |  |  |  |  |  |

| Input          | DAC 4    | DAC 5  | DAC 6 | DAC_CLOCK              |  |  |  |  |  |

| SD Port        | HDY      | HDPB   | HDPR  | 54MHz ( CLK_SD x2 )    |  |  |  |  |  |

| HD Port        | HDY      | HDPB   | HDPR  | FAMU- ( CLK UD v2 )    |  |  |  |  |  |

| 525i/625i      | זטח      | прев   | прек  | 54MHz ( CLK_HD x2 )    |  |  |  |  |  |

| HD Port        | HDY      | HDPB   | HDPR  | 54MHz ( CLK HD x2 )    |  |  |  |  |  |

| 525p/625p      | זטח      | прев   | прек  | 54WINZ ( CLK_ND XZ )   |  |  |  |  |  |

| HD Port        | HDY      | HDPB   | HDPR  | 148.5MHz ( CLK HD x2 ) |  |  |  |  |  |

| ( 1080i/720p ) | пот      | прев   | HUFK  | 146.5WHZ ( CEN_HD XZ ) |  |  |  |  |  |

The AK8823 has on-chip PLL.

Description with parenthesis ( x 2 etc. ), following frequency value in DAC\_CLOCK column shows an integer- multiple number ( multiplier ) and the selected input clock source.

#### 8. PLL function

The AK8823 has on-chip PLL for clock multiplier.

When HD block is enabled, frequency-multiplied operation as described above is executed while 27 MHz is used in SD block as its input clock.

#### 9. Video DAC

The AK8823 has 10-bit resolution, discrete 2 channel Current Drive DACs which run at 27MHz, and discrete 3 channel DACs which run at 150MHz.

These DACs are designed to output 1.28V o-p Full Scale with load resistors of 150ohm (+/-1 %) on HDY Output DAC and 300ohm (+/-1 %) on all other DACs when a 3.9kohm (+/-1 %) resistor is connected between IREF pin and ground.

AK8823 [ASAHI KASEI]

## 10. Operation Mode [ HD Control ]

|            | SD block            |               |         | HD                  | block           |                          |              |                        |                      | I2C register             | settings                   |                      |                     |

|------------|---------------------|---------------|---------|---------------------|-----------------|--------------------------|--------------|------------------------|----------------------|--------------------------|----------------------------|----------------------|---------------------|

| Mode<br>No | Mode & output clock | CLK_HD MHz    | In Port | Video<br>processing | VBID processing | output<br>clock<br>[MHz] | Macrovision  | 0x11<br>bit[3:2]<br>VM | 0x00 bit[0]<br>RFRSH | 0x00 bit[2:1]<br>MODE1,0 | 0x06<br>bit[1;0]<br>BLKCNT | 0x07 bit[]<br>VRATIO | 0x05 bit[5]<br>VRPT |

|            |                     |               |         |                     |                 | Refres                   | sh rate 60Hz |                        |                      |                          |                            |                      |                     |

| 1          |                     | (CLK_SD)      | SD      | YpbPr (525i)(*)     | CGMA-A/CC       |                          | 7.1.1L       |                        |                      |                          | [0:0]                      | 1                    | 1                   |

| 2          |                     | (CLK_SD)      | SD      | YpbPr (525i)        | CGMA-A/CC       |                          | 7.1.1L       |                        |                      | [0:0]                    | [0:0]                      | 0                    | 1                   |

| 3          | NTSC or             | 27            | HD      | YpbPr (525i)(*)     | CGMA-A/CC       | 54                       | 7.1.1L       |                        |                      | [0.0]                    | [0:0]                      | 1                    | 0                   |

| 4          | PAL60               | 27            | HD      | YpbPr (525i)        | CGMA-A/CC       |                          | 7.1.1L       | [0:0]or[0:1]           | 0                    |                          | [0:0]                      | 0                    | 0                   |

| 5          | 27MHz               | 27            | HD      | YpbPr (525p)        | CGMA-A          |                          | 1.2          |                        |                      | [0:1]                    | [0:0]                      | 0                    | 0                   |

| 6          |                     | 74.25(74.175) | HD      | YpbPr (1080i)       | CGMA-A          | 148.5                    | -            |                        |                      | [1:0]                    | [0:0]                      | 0                    | 0                   |

| 7          |                     | 74.25(74.175) | HD      | YpbPr (720p)        | CGMA-A          | 148.5                    | -            |                        |                      | [1:1]                    | [0:0]                      | 0                    | 0                   |

| 8          |                     | (CLK_SD)      | SD      | YpbPr (525i)(*)     | CGMA-A/CC       |                          | 7.1.1L       |                        |                      |                          | [0:1]                      | 1                    | 1                   |

| 9          |                     | (CLK_SD)      | SD      | YpbPr (525i)        | CGMA-A/CC       |                          | 7.1.1L       |                        |                      | [0:0]                    | [0:1]                      | 0                    | 1                   |

| 10         | D                   | 27            | HD      | YpbPr (525i)(*)     | CGMA-A/CC       | 54                       | 7.1.1L       |                        |                      | [0.0]                    | [0:1]                      | 1                    | 0                   |

| 11         | Power<br>Down       | 27            | HD      | YpbPr (525i)        | CGMA-A/CC       |                          | 7.1.1L       | *                      | 0                    |                          | [0:1]                      | 0                    | 0                   |

| 12         | DOWII               | 27            | HD      | YpbPr (525p)        | CGMA-A          |                          | 1.2          |                        |                      | [0:1]                    | [0:1]                      | 0                    | 0                   |

| 13         |                     | 74.25(74.175) | HD      | YpbPr (1080i)       | CGMA-A          | 148.5                    | -            |                        |                      | [1:0]                    | [0:1]                      | 0                    | 0                   |

| 14         |                     | 74.25(74.175) | HD      | YpbPr (720p)        | CGMA-A          | 140.5                    | -            |                        |                      | [1:1]                    | [0:1]                      | 0                    | 0                   |

| 15         | 27MHz               |               |         | Power               | Down            |                          |              | [0:0]or[0:1]           | *                    | *                        | [1:0]                      | *                    | *                   |

|            |                     |               |         |                     |                 | Refres                   | sh rate 50Hz |                        |                      |                          |                            |                      |                     |

| 16         |                     | (CLK_SD)      | SD      | YpbPr (625i)        | WSS/CC          |                          | 7.1.1L       |                        |                      | [0:0]                    | [0:0]                      | 0                    | 1                   |

| 17         |                     | 27            | HD      | YpbPr (625i)        | WSS/CC          | 54                       | 7.1.1L       |                        |                      | [0.0]                    | [0:0]                      | 0                    | 0                   |

| 18         | PAL                 | 27            | HD      | YpbPr (576p)        | -               |                          | 1.2          | [1:1]                  | 1                    | [0:1]                    | [0:0]                      | 0                    | 0                   |

| 19         |                     | 74.25(74.175) | HD      | YpbPr (1080i)       | -               |                          | -            |                        |                      | [1:0]                    | [0:0]                      | 0                    | 0                   |

| 20         |                     | 74.25(74.175) | DH      | YpbPr (720p)        | -               |                          | -            |                        |                      | [1:1]                    | [0:0]                      | 0                    | 0                   |

| 21         |                     | (CLK_SD)      | SD      | YpbPr (625i)        | WSS/CC          | 148.5                    | 7.1.1L       |                        |                      | [0:0]                    | [0:1]                      | 0                    | 1                   |

| 22         | D                   | 27            | HD      | YpbPr (625i)        | WSS/CC          |                          | 7.1.1L       |                        |                      | [0:0]                    | [0:1]                      | 0                    | 0                   |

| 23         | Power<br>Down       | 27            | HD      | YpbPr (576p)        | -               |                          | 1.2          |                        | 1                    | [0:1]                    | [0:1]                      | 0                    | 0                   |

| 24         | 2011                | 74.25(74.175) | HD      | YpbPr (1080i)       | -               | 148.5                    | -            |                        | ]                    | [1:0]                    | [0:1]                      | 0                    | 0                   |

| 25         |                     | 74.25(74.175) | HD      | YpbPr (720p)        | -               | 140.3                    | -            |                        |                      | [1:1]                    | [0:1]                      | 0                    | 0                   |

| 26         | 27MHz               |               |         | Powe                | r Down          |                          | •            | [1:1]                  | *                    | *                        | [1:0]                      | *                    | *                   |

MS0549-E-02 15 2006/09

<sup>(</sup>  $^{\star}$  ) mark in the table In D1 ( 60 Hz ) mode, 286 / 714 amplitude ratio ( EIA 770. 1-A Output compatible )

<sup>\*</sup> Do not care bit

[ASAHI KASEI] AK8823

## 11. Operation Mode [ SD Control ]

| Mode | HD block                           |                   |         | SD block        |                       |                          |                      | I2C register set        | tings                  |                       |

|------|------------------------------------|-------------------|---------|-----------------|-----------------------|--------------------------|----------------------|-------------------------|------------------------|-----------------------|

| No   | Mode & output clock                | CLK_SD<br>MHz     | In Port | VBID processing | output clock<br>[MHz] | 0x00 bit[2:1]<br>MODE1,0 | 0x00 bit[0]<br>RFRSH | 0x06 bit[1;0]<br>BLKCNT | 0x11 bit[3:2]<br>VM3:2 | 0x14 bit[7]<br>VPRTSD |

|      |                                    |                   |         |                 | Refresh rate 60Hz     |                          |                      |                         |                        |                       |

| 1    |                                    | (CLK_HD<br>27MHz) | HD      |                 |                       |                          |                      |                         |                        | 1                     |

| 2    | D1 54MHz                           | 27                | SD      |                 |                       | [0:0]                    |                      | [0:0]                   | [0:0]or[0:1]           | 0                     |

| 3    | D2 54MHz<br>D3 148MHz<br>D4 148MHz | 27                | SD      | VBID/CC         | 27                    | [0 :1]<br>[1:0]<br>[1:1] | 0                    |                         | [0.0]0[[0.1]           |                       |

| 4    | Power                              | (CLK_HD<br>27MHz) | HD      |                 |                       | *                        |                      | [1:0]                   |                        | 1                     |

| 5    | Down                               | 27                | SD      |                 |                       |                          |                      |                         |                        | 0                     |

| 6    |                                    |                   |         | Power Down      |                       |                          | *                    | [11]                    | *                      | *                     |

|      |                                    |                   |         |                 | Refresh rate 50Hz     |                          |                      |                         |                        |                       |

| 7    | D1 54MHz                           | (CLK_SD)<br>27MHz | SD      |                 |                       | [0:0]                    |                      |                         |                        |                       |

| 8    |                                    | 27                | HD      |                 |                       |                          |                      | [0:0]                   |                        | 1                     |

| 9    | D2 54MHz<br>D3 148MHz<br>D4 148MHz | 27                | SD      | VBID/CC/WSS     | 27                    | [0 :1]<br>[1:0]<br>[1:1] | 1                    | [0.0]                   | [1:1]                  |                       |

| 10   | Power                              | (CLK_HD<br>27MHz) | HD      |                 |                       |                          |                      | [1:0]                   |                        | 1                     |

| 11   | Down                               | 27                | SD      |                 |                       | *                        |                      |                         |                        | 0                     |

| 12   |                                    |                   | •       | Power Down      |                       |                          | *                    | [11]                    | *                      | *                     |

MS0549-E-02 16 2006/09

#### 12. Power-Down

PD\_N L: Power-Down H: normal operation

PLL clock generator and registers are initialized (into default value setting) at power-down.

Hi-Z input compatible pins are as follows during this power-down.

When device output pins those are connected to the AK8823 input pins become Hi-Z conditions such as a case at the power-on etc., the AK8823 should be powered-up in power-down condition.

This pin controls to power-down all the blocks and puts the device into the minimum power mode (Refer to item 14.Power –up Sequence).

[ Hi-Z Compatible Input pins ]

ITU7 ~ ITU0, Y7 ~ Y0, CBCR7 ~ CBCR0

HSYNC\_SD, VSYNC\_SD, HSYNC\_HD, VSYNC\_HD

INIT\_N, CLK\_SD, CLK\_HD

SCL, SELA

In order to put the device into the minimum power mode in normal operation ( PD\_N " H " ), input clocks ( CLK\_SD, CLK\_HD ) should be stopped ( either " L " or " H " ) in addition to the following register settings.

Register Setting to put into minimum power mode

Address 0x05 bit 2 ~ 0 [ 000 ] Address 0x06 bit 2 [ 0 ], bit 1 ~ 0 [ 11 ] Address 0x15 bit 1 ~ 0 [ 00 ]

#### 13. Initialization

INIT N "L" initialization

Video Process Digital Filter is initialized.

PLL Clock Generator and I2C register are not initialized by INIT\_N.

Video Process Digital Filter can be also initialized by register (HD\_SINIT\_N, SD\_SINIT\_N), instead of INIT\_N pin control.

Set INIT\_N pin to "H (IVDD)" when it is not used.

PLL can be also reset by register PLL\_SPD\_N.

[Initialization Registers]

HD\_SINIT\_N Address 0x05 bit 7

PLL\_SPD\_N Address 0x06 bit 2

SD SINIT N Address 0x15 bit 4

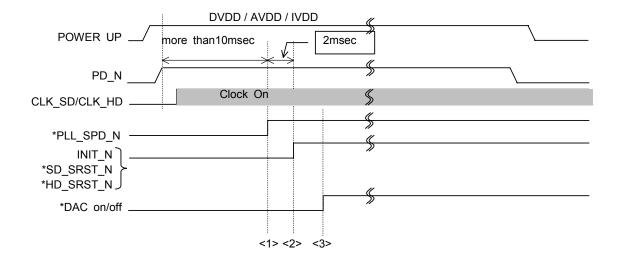

## 14. Power-up Sequence

#### Control of Power Supply power-up and power-down

When the power supplies become stable, release PD\_N pin and wait for 10 msec.

Set mode of HD / SD Blocks, then enable PLL operation first and turn on DACs.

By releasing PD\_N after the power-on, rise time variations of power supplies ( DVDD / AVDD / IVDD ) are tolerated.

Wait for longer than 10 msec after PD\_N is released, then enable PLL.

When to power-down, power supplies should be turned off after PD\_N is activated.

#### When to power-up

Following timing sequence should be made after 10 msec time from the release of power-down and after input clock becomes stable.

A longer than 2 msec transition time is required from sequence <2> to sequence <3> below.

- <1> Mode setting  $\rightarrow$  start of PLL operation ( PLL\_SPD\_N : 1 )

- <2> initialization of internal filter ( INIT\_N pin " L " or SD\_SRST\_N / HD\_SRST\_N : 0 ) release ( note 1 ) operation which is described below.

- <3> turn on DAC

#### (note 1)

INIT\_N pin is used to initialize internal digital filter. Clock input is required.

Initialization at "L" and normal operating condition at "H".

Instead of controlling this pin, same initialization function is executed by manipulating registers SD\_SRST\_N, HD\_SRST\_N. When to manipulate registers, set INIT\_N pin to " H ".

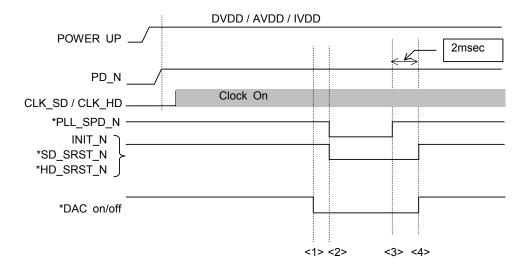

#### When to change mode by register setting

When a mode change is made, involving( accompanied with ) PLL oscillator frequency change, following timing sequence should be met.

A longer than 2 msec transition time is required from sequence <3> to sequence <4> below.

- <1> DAC off

- <2> PLL operation off ( PLL\_SPD\_N : 0 ) → initialization of internal filter ( INIT\_N pin " L " or SD\_SRST\_N / HD\_SRST\_N : 0 )

- → mode change setting ( D1 to D3 change, CLK\_HD frequency is also changed during this period )

- <3> start PLL operation ( PLL SPD N: 1 )

- <4> release of internal filter initialization ( INIT\_N pin " H " or SD\_SRST\_N / HD\_SRST\_N : 1 ) → DAC on

When a Video Mute Circuit etc is externally equipped and used, DAC manipulation of sequences <1> and <4> above can be eliminated.

It is also true that its manipulation can be eliminated when the internal filter initialization register is always used in operating condition "1".

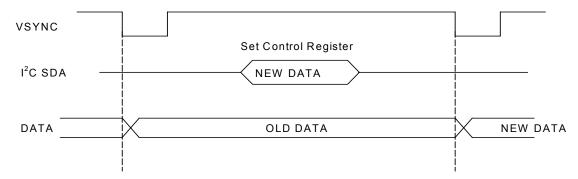

## Register setting via I2C interface ( all other register change )

Access to the AK8823 registers is possible even when CLK\_SD or CLK\_HD clocks are not fed.

The AK8823 register manipulation can be made anytime, but care must be taken when the power is up or when the internal PLL oscillating frequency is changed or when the input clock is changed.

In Macrovision setting mode and VBID setting mode where changes of PLL oscillating frequency are not involved, target registers can be directly accessed.

## 15. HD Block

#### 15-1. Video Interface Timing (HD)

The AK8823 has 2 types of Video Interfaces, EAV Decode mode and Slave SYNC mode.

#### EAV SYNC mode

( HD ) [ Mode Register ] ( Sub Address 0x00 ) set by EAVDEC ( bit 4 )

#### Slave SYNC mode

The AK8823 can also synchronize with externally-fed HSYNC signal and VSYNC signal as Slave SYNC mode operation.

HSYNC becomes Pixel Counter Reference Point within a Line and VSYNC becomes Line Counter Reference Point within a Frame.

Polarities of HSYNC\_HD, VSYNC\_HD are pre-settable.

When an interlaced signal is input, the First and the Second Fields are recognized from HSYNC and VSYNC relation.

In this mode, the AK8823 also complies with EIA / CEA 861B compatible timing.

(HD) [Mode Register] (Sub Address 0x00) CEA 861B (bit 3)

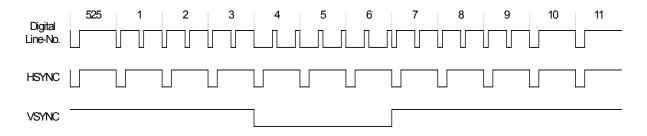

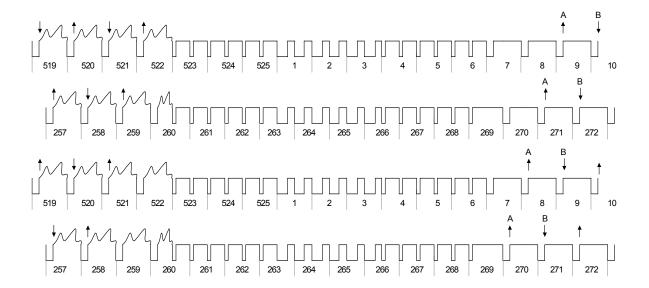

#### (1) 525i (480i) / 60Hz (HD)

(1-1) Data Capture

(1-1-2) EAV Decode ( Capture ): 525i ( 480i ) / 60 Hz ( HD )

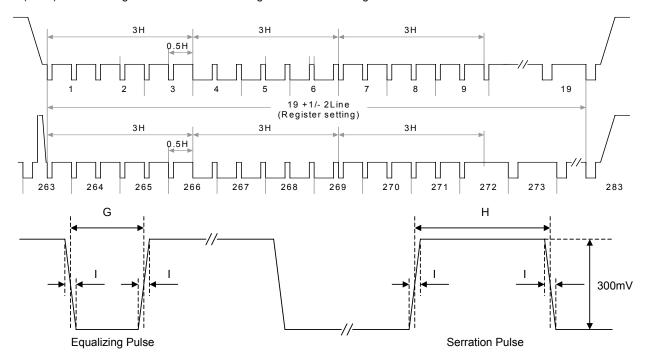

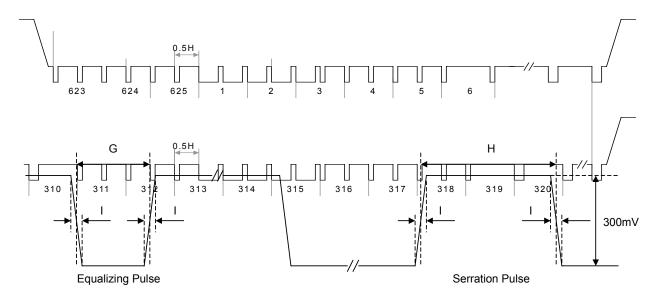

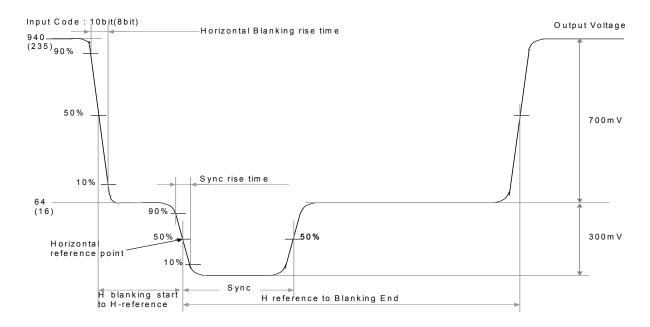

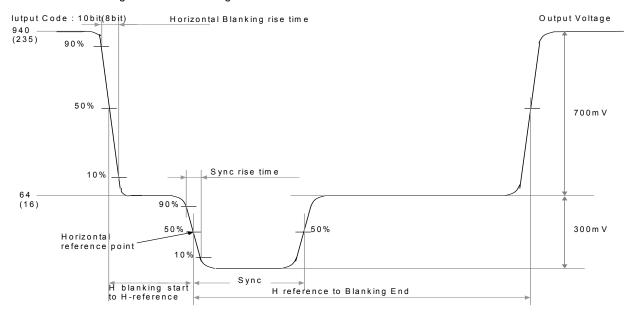

(1-2) Analog Output: 525i (480i) / 60 Hz (HD)

(1-2-1) Frame Configuration: Vertical SYNC Signal Waveform Timing

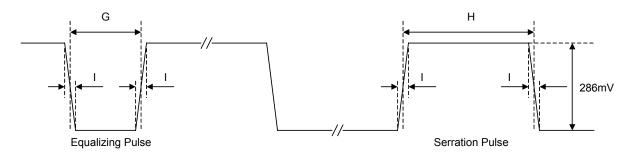

**Equalizing Pulse and Serration Pulse**

| Symbol |                                                       | Measurement point | Value           | Recommended tolerance | units |

|--------|-------------------------------------------------------|-------------------|-----------------|-----------------------|-------|

|        | Field Period (derived)                                |                   | 16.6833         |                       | msec  |

|        | Frame period (derived)                                |                   | 33.3667         |                       | msec  |

|        | Vertical blanking start before first equalizing pulse | 50%               | 1.5             | +/- 0.1               | usec  |

|        | Vertical blanking                                     |                   | 19* lines + 1.5 | 0                     | lines |

|        | (63.556usec x 20lines + 1.5usec)                      |                   | usec            | +/- 0.1               | usec  |

|        | Pre-equalizing duration                               |                   | 3               |                       | lines |

| G      | Pre-equalizing pulse width                            | 50%               | 2.3             | +/- 0.1               | usec  |

|        | Vertical sync duration                                |                   | 3               |                       | lines |

| Н      | Vertical serration pulse width                        | 50%               | 4.7             | +/- 0.1               | usec  |

|        | Post-equalizing duration                              |                   | 3               |                       | lines |

| G      | Post-equalizing pulse width                           | 50%               | 2.3             | +/- 0.1               | usec  |

|        | Sync rise time                                        |                   | 140             | +/- 20                | nsec  |

<sup>\*</sup> there is a case of V-Blank of 20 lines. This value is pre-settable by register.

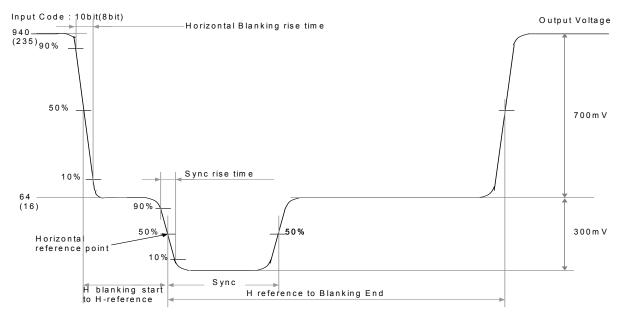

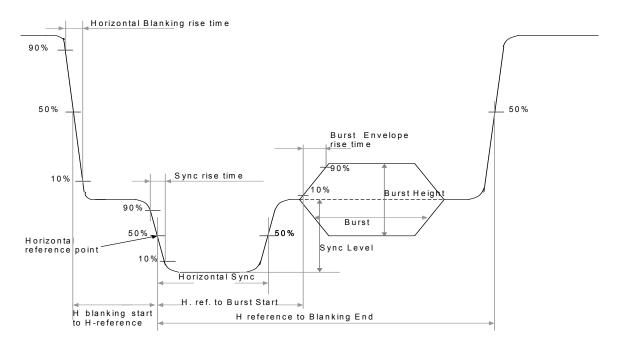

|                                 | measurement point | value  | Recommended tolerance | units |

|---------------------------------|-------------------|--------|-----------------------|-------|

| Total line period(derived)      |                   | 63.556 |                       | usec  |

| Horizontal Blanking rise time   | 10% - 90%         | 140    | +/- 20                | nsec  |

| Sync rise time                  | 10% - 90%         | 140    | +/- 20                | nsec  |

| H-Blanking start to H-reference | 50%               | 1.5    | +/- 0.1               | usec  |

| Horizontal Sync                 | 50%               | 4.7    | +/- 0.1               | usec  |

| H reference to H-blanking end   | 50%               | 9.2    | + 0.2 / - 0.1         | usec  |

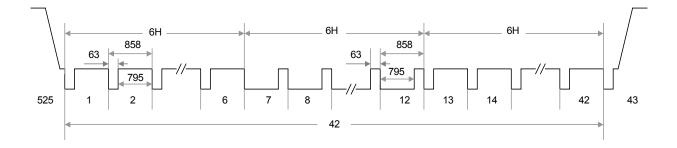

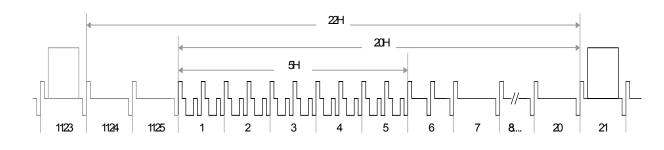

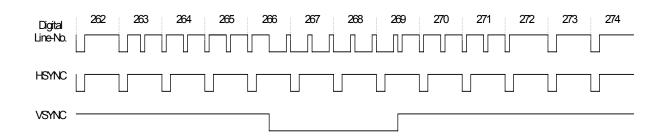

## (2) 625i(576i) / 50Hz HD

(2-1) Data Capture

(2-1-1) EAV Decode (Capture): 625i (576i)/50 Hz HD

(2-2) Analog Output: 625i (576i) / 50 Hz HD

(2-2-1) Frame Configuration : Vertical SYNC Signal Waveform Timing

**Equalizing Pulse and Serration Pulse**

| Symbol |                                | Measurement | Value | Recommended | units |  |

|--------|--------------------------------|-------------|-------|-------------|-------|--|

| - ,    |                                | point       |       | tolerance   |       |  |

| G      | Pre-equalizing pulse width     | 50%         | 2.35  | +/- 0.1     | usec  |  |

| Н      | Vertical serration pulse width | 50%         | 4.7   | +/- 0.2     | usec  |  |

| G      | Post-equalizing pulse width    | 50%         | 2.35  | +/- 0.1     | usec  |  |

|        | Sync rise time                 |             | 200   | MAX300      | nsec  |  |

<sup>\*</sup> there is case where tolerance of Sync rise time is added to Pulse width tolerance.

## (2-2-2) Waveform Levels (Codes):

SYNC Signal Waveform : 625i ( 576i ) / 50 Hz  $\;$  HD SYNC signal is super-imposed on Luminance signal ( Y ).

|                               | measurement point | value | Recommended tolerance | units |

|-------------------------------|-------------------|-------|-----------------------|-------|

| Total line period(derived)    |                   | 64.0  |                       | usec  |

| Horizontal Blanking rise time | 10% - 90%         | 0.3   | +/- 0.1               | usec  |

| Sync rise time                | 10% - 90%         | 0.2   | +/- 0.1               | usec  |

| H-Blanking start to           | 50%               | 1.5   | +/- 0.3               | usec  |

| H-reference                   |                   |       |                       |       |

| Horizontal Sync               | 50%               | 4.7   | +/- 0.2               | usec  |

| H reference to H-blanking end | 50%               | 10.5  |                       | usec  |

## (3) 525p(480p) / 60Hz : HD

(3-1) Data Capture

(3-1-1) EAV Decode (Capture) 525p (480p)/60 Hz HD

(3-2) Analog Output: 525p (480p) / 60 Hz HD

(3-2-1) Frame Configuration: Vertical SYNC Signal Waveform Timing

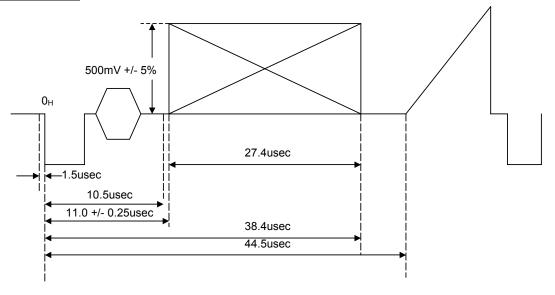

( 3-2-2 ) Waveform Levels ( Codes ) : SYNC Signal Waveform : 525p (480p) / 60 Hz HD SYNC signal is super-imposed on Luminance signal ( Y ).

## Horizontal SYNC Signal Waveform Timing

|                                 | measurement point | value  | Recommended tolerance | units |

|---------------------------------|-------------------|--------|-----------------------|-------|

| Total line period(derived)      |                   | 31.776 |                       | usec  |

| Horizontal Blanking rise time   | 10% - 90%         | 70     | +/- 10                | nsec  |

| Sync rise time                  | 10% - 90%         | 70     | +/- 10                | nsec  |

| H-Blanking start to H-reference | 50%               | 0.59   | +/- 0.05              | usec  |

| Horizontal Sync                 | 50%               | 2.33   | +/- 0.05              | usec  |

| H reference to H-blanking end   | 50%               | 4.52   | + 0.1 / - 0.05        | usec  |

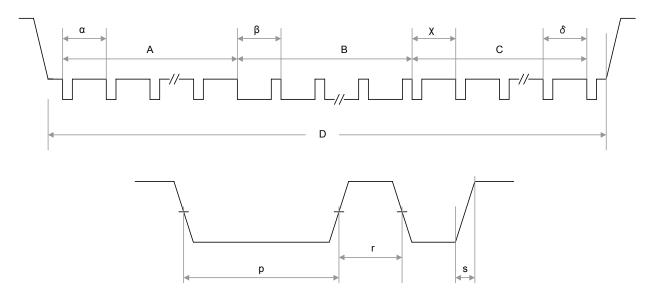

## (4) 625p(576p) / 50Hz : HD

(4-1) Data Capture

(4-1-1) EAV Decode (Capture): 625p (576p)/50 Hz HD

( 4-2 ) Analog Output : 625p ( 576p ) / 50 Hz HD

(4-2-1) Frame Configuration: Vertical SYNC Signal Waveform Timing

| Symbol | Characteristics                                                                                                  | 625/50/1:1 |

|--------|------------------------------------------------------------------------------------------------------------------|------------|

| V      | Nominal frame period (ms)                                                                                        | 20         |

| D      | Vertical blanking interval                                                                                       | 49H+α*     |

| -      | Build-up time (10 to 90%) of the edges of vertical blanking pulse (us)                                           | 0.15±0.05  |

| А      | Interval between front edges of vertical blanking interval and front edges of first vertical synchronizing pulse | 5H*        |

| С      | Interval between back edges of last vertical synchronizing pulse and back edge of vertical blanking interval     | 39H*       |

| В      | Duration of sequence of vertical synchronizing pulses                                                            | 5H*        |

| р      | Duration of vertical synchronizing pulse (us)                                                                    | 29.65±0.1  |

| r      | Interval between vertical synchronizing pulse(us)                                                                | 2.35±0.1   |

| S      | Build-up time (10 to 90%) og the vertical synchronizing pulses (us)                                              | 0.1±0.05   |

<sup>\*</sup> For H and a, see Table 1 (ITU-R BT.1358)

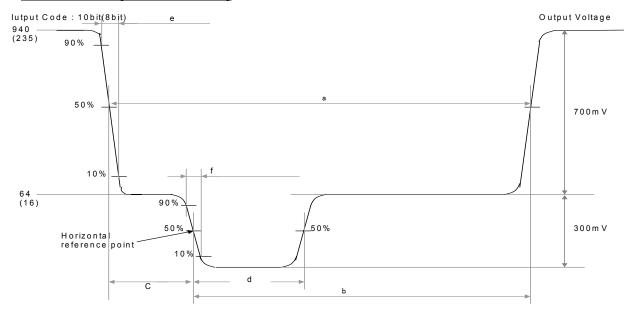

(4-2-2) Waveform Levels ( Codes ): SYNC Signal Waveform ( BT. 1368 ): 625p ( 576p ) / 50 Hz HD SYNC signal is super-imposed on Luminance signal ( Y ).

## Horizontal SYNC Signal Waveform Timing

| Symbol | Characteristics                                                                    | 625/50/1:1      |

|--------|------------------------------------------------------------------------------------|-----------------|

| Н      | Nominal line period (us)                                                           | 32              |

| а      | Horizontal blanking interval(us)                                                   | $6.0 \pm 1.5$   |

| b      | Interval between time datum (0H) and back edge of horizontal blanking pulse (us)   | 5.25            |

| С      | Front porch (us)                                                                   | $0.75 \pm 0.15$ |

| d      | Synchronizing pulse (us)                                                           | $2.35 \pm 0.1$  |

| е      | Build-up time (10 to 90%) of the edges of the horizontal blanking pulse (us)       | 0.15±0.05       |

| f      | Build-up time (10 to 90%) of the edges of the horizontal synchronizing pulses (us) | 0.1±0.05        |

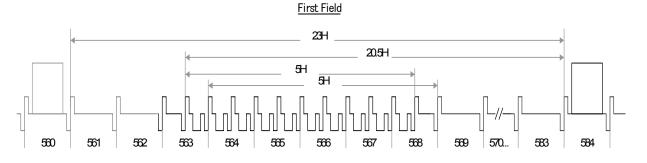

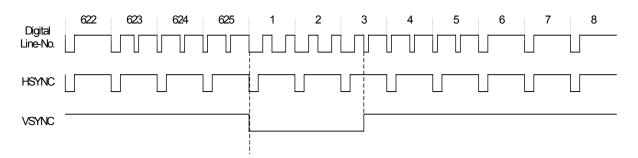

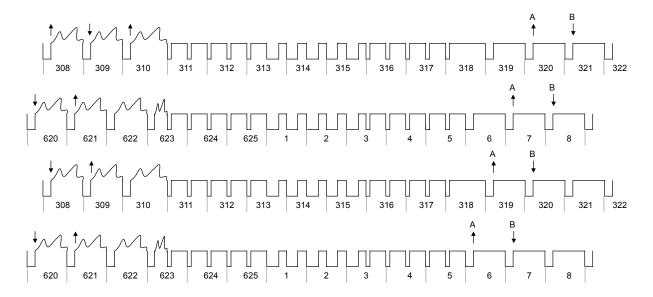

## (5) 1080i / 60Hz : HD

(5-1) Data Capture

(5-1-1) EAV Decode (Capture): 1080i / 60 Hz HD

( 5-2 ) Analog Output : 1080i / 60 Hz HD

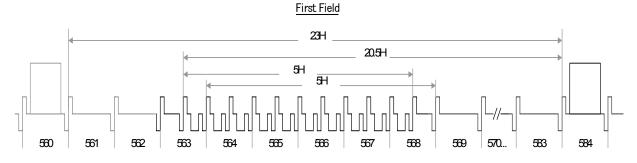

(5-2-1) Frame Configuration : <u>Vertical SYNC Timing</u>

Second Field

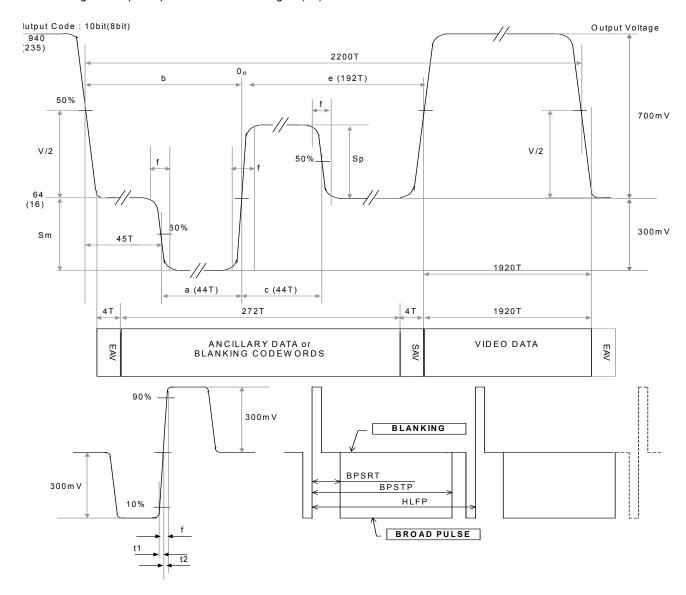

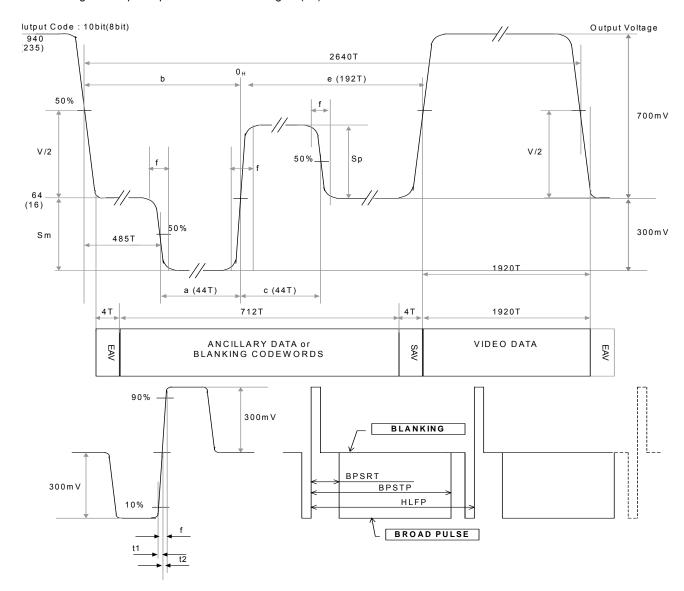

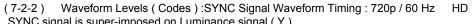

(5-2-2) Waveform Levels (Codes): SYNC Signal Waveform Timing: 1080i / 60 Hz HD SYNC signal is super-imposed on Luminance signal (Y).

| Symbol  | Characteristics             | Nominal value | Reference clock Interval | Tolerance<br>CLK | Tolerance        |

|---------|-----------------------------|---------------|--------------------------|------------------|------------------|

| а       | Negative line sync width    | 0.593 [usec]  | 44                       | +/- 3            | +/- 0.040 [usec] |

| b       | End of active video         | 1.120 [usec]  | 89                       |                  | +0.080 [usec]    |

| С       | positive line sync width    | 0.593 [usec]  | 44                       | +/- 3            | +/- 0.040 [usec] |

| е       | Start of active video       | 2.589 [usec]  | 192                      | -0 / + 6         | +0.080 [usec]    |

| f       | Rise/fall time              | 0.054 [usec]  | 4                        | +/- 1.5          | +/- 0.020 [usec] |

| t2 - t1 | Symmetry of rising edge     | -             | -                        |                  | +/- 0.002 [usec] |

| Sm      | Amplitude of negative pulse | 300 [mV]      | -                        |                  | +/- 6mV          |

| Sp      | Amplitude of positive pulse | 300 [mV]      | -                        |                  | +/- 6mV          |

| V       | Amplitude of video signal   | 700 [mV]      | -                        |                  |                  |

| -       | Field-blanking interval     | 45 [H/field]  | 99000                    |                  |                  |

|         | H Total                     |               | 2200                     |                  |                  |

|         | H Active                    |               | 1920                     |                  |                  |

| BPSRT   | Broad pulse start pos       |               | 132                      |                  | -3 ~ +3          |

| BPSTP   | Broad pulse stop pos        |               | 1012                     |                  | -3 ~ +3          |

| HLFP    | H/2 pos                     |               | 1100                     |                  | -3 ~ +3          |

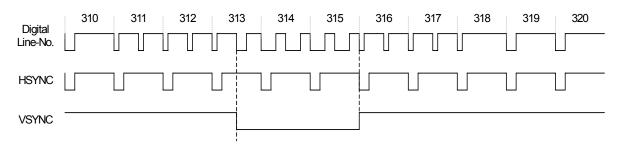

## (6) 1080i / 50Hz : HD

(6-1) Data Capture

(6-1-1) EAV Decode (Capture): 1080i / 50 Hz HD

( 6-2 ) Analog Output : 1080i / 50 Hz HD

(6-2-1) Frame Configuration: <u>Vertical SYNC Timing</u>

Second Field

(6-2-2) Waveform Levels (Codes): SYNC Signal Waveform Timing: 1080i / 50 Hz HD SYNC signal is super-imposed on Luminance signal (Y).

| Symbol  | Characteristics             | Nominal value | Reference clock Interval | Tolerance<br>CLK | Tolerance        |

|---------|-----------------------------|---------------|--------------------------|------------------|------------------|

| а       | Negative line sync width    | 0.593 [usec]  | 44                       | +/- 3            | +/- 0.040 [usec] |

| b       | End of active video         | 1.120 [usec]  | 529                      |                  | +0.080 [usec]    |

| С       | positive line sync width    | 0.593 [usec]  | 44                       | +/- 3            | +/- 0.040 [usec] |

| е       | Start of active video       | 2.589 [usec]  | 192                      | -0 / + 6         | +0.080 [usec]    |

| f       | Rise/fall time              | 0.054 [usec]  | 4                        | +/- 1.5          | +/- 0.020 [usec] |

| t2 - t1 | Symmetry of rising edge     | -             | =                        |                  | +/- 0.002 [usec] |

| Sm      | Amplitude of negative pulse | 300 [mV]      | =                        |                  | +/- 6mV          |

| Sp      | Amplitude of positive pulse | 300 [mV]      | =                        |                  | +/- 6mV          |

| >       | Amplitude of video signal   | 700 [mV]      | ı                        |                  |                  |

| ı       | Field-blanking interval     | 45 [H/field]  | 99000                    |                  |                  |

|         | H Total                     |               | 2640                     |                  |                  |

|         | H Active                    |               | 1920                     | -12, +0          |                  |

| BPSRT   | Broad pulse start pos       |               | 132                      |                  | -3 ~ +3          |

| BPSTP   | Broad pulse stop pos        |               | 1012                     |                  | -3 ~ +3          |

| HLFP    | H/2 pos                     |               | 1320                     |                  | -3 ~ +3          |

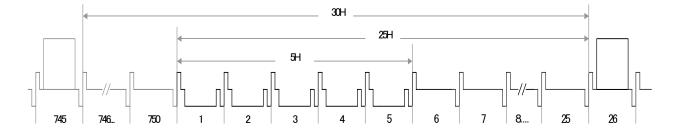

## (7) 720p / 60Hz : HD

(7-1) Data Capture

( 7-1-1 )  $\;$  EAV Decode ( Capture ) : 750p ( 720p ) / 60 Hz  $\;$  HD

( 7-2 ) Analog Output : 720p / 60 Hz HD

(7-2-1) Frame Configuration: <u>Vertical SYNC Timing</u>

| Symbol  | Characteristics             | Nominal value | Reference clock Interval | Tolerance<br>CLK | Tolerance |

|---------|-----------------------------|---------------|--------------------------|------------------|-----------|

| а       | Negative line sync width    | [usec]        | 40                       |                  | [usec]    |

| b       | End of active video         | [usec]        | 111                      |                  | [usec]    |

| С       | positive line sync width    | [usec]        | 40                       |                  | [usec]    |

| е       | Start of active video       | [usec]        | 260                      |                  | [usec]    |

| f       | Rise/fall time              | [usec]        | 4                        |                  | [usec]    |

| t2 - t1 | Symmetry of rising edge     | -             | -                        |                  | [usec]    |

| Sm      | Amplitude of negative pulse | 300 [mV]      | -                        |                  | +/- 6mV   |

| Sp      | Amplitude of positive pulse | 300 [mV]      | -                        |                  | +/- 6mV   |

| V       | Amplitude of video signal   | 700 [mV]      | -                        |                  |           |

|         | H Total s                   |               | 1650                     |                  |           |

|         | H Active                    |               | 1280                     |                  |           |

| BPSRT   | Broad pulse start pos       |               | 260                      |                  | 0 ~ +6    |

| BPSTP   | Broad pulse stop pos        |               | 1540                     |                  | -6 ~ 0    |

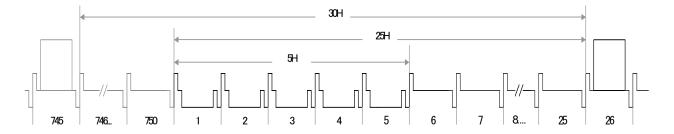

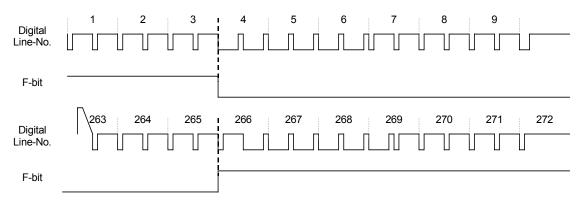

## (8) 720p / 50Hz : HD

(8-1) Data Capture

(8-1-1) EAV Decode (Capture): 720p / 50 Hz HD

(8-2) Analog Output: 720p / 50 Hz HD

(8-2-1) Frame Configuration : <u>Vertical SYNC Timing</u>

| Symbol  | Characteristics             | Nominal value | Reference clock Interval | Tolerance<br>CLK | Tolerance |

|---------|-----------------------------|---------------|--------------------------|------------------|-----------|

| а       | Negative line sync width    | [usec]        | 40                       |                  | [usec]    |

| b       | End of active video         | [usec]        |                          |                  | [usec]    |

| С       | positive line sync width    | [usec]        | 40                       |                  | [usec]    |

| е       | Start of active video       | [usec]        |                          |                  | [usec]    |

| f       | Rise/fall time              | [usec]        | 4                        |                  | [usec]    |

| t2 - t1 | Symmetry of rising edge     | -             | -                        |                  | [usec]    |

| Sm      | Amplitude of negative pulse | 300 [mV]      | -                        |                  |           |

| Sp      | Amplitude of positive pulse | 300 [mV]      | -                        |                  |           |

| V       | Amplitude of video signal   | 700 [mV]      | -                        |                  |           |

|         | H Total                     |               | 1980                     |                  |           |

|         | H Active                    |               | 1280                     | •                |           |

| BPSRT   | Broad pulse start pos       |               | 260                      |                  | 0 ~ +6    |

| BPSTP   | Broad pulse stop pos        |               | 1540                     |                  | -6 ~ 0    |

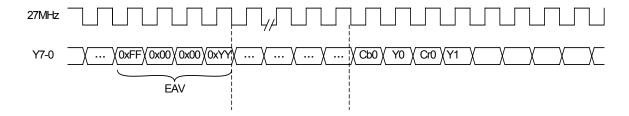

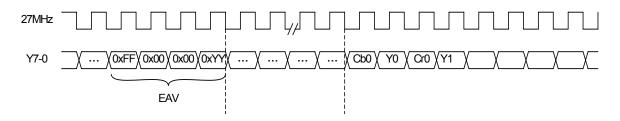

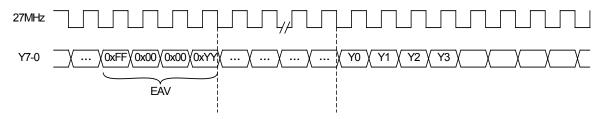

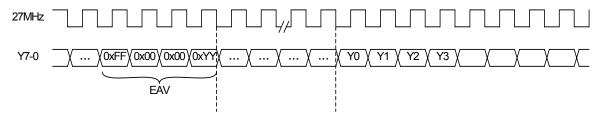

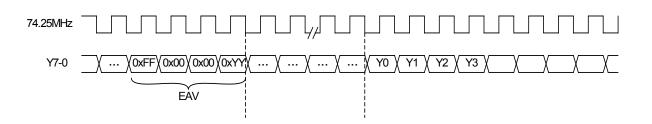

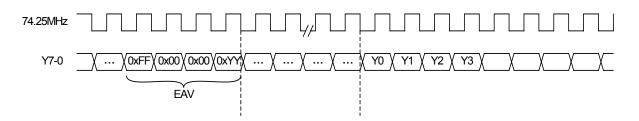

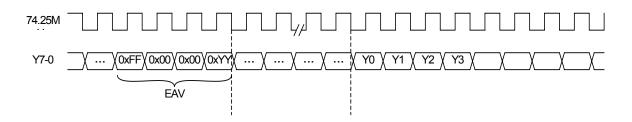

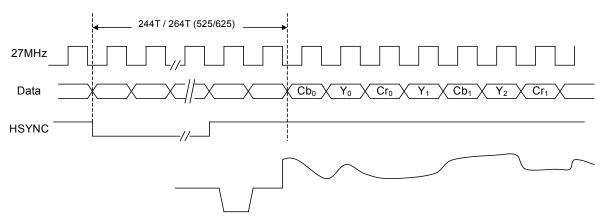

### 15-2. Signal Relations in EAV Decoding

(1) EAV Synchronization (HD)

EAV code which is encoded on input signal is decoded, and the device makes synchronization with its timing.

In 2 channel input case, synchronization is made with EAV of the Y7 ~ Y0 signal, and it is not referenced to the EAV / SAV

which are contained in CBCR7 ~ 0 signal.

#### EAV / SAV Codes

Those codes succeeding 0xFF ~ 0x00 ~ 0x00 which are fed as input data become EAV / SAV codes.

EAV /SAV codes have following meanings, starting with MSB.

| В   | t Numb | er   | MSB |   |   |   |    |    |    | LSB |

|-----|--------|------|-----|---|---|---|----|----|----|-----|

| WOF | D VA   | ALUE | 7   | 6 | 5 | 4 | 3  | 2  | 1  | 0   |

| 0   | 0      | )xFF | 1   | 1 | 1 | 1 | 1  | 1  | 1  | 1   |

| 1   | C      | 00x0 | 0   | 0 | 0 | 0 | 0  | 0  | 0  | 0   |

| 2   | C      | 00x0 | 0   | 0 | 0 | 0 | 0  | 0  | 0  | 0   |

| 3   | (      | Эххх | 1   | F | V | Н | P3 | P2 | P1 | P0  |

Here, F = 0: Field 1

F = 1 : Field 2

But, in Progressive Output Modes 525p (480p) / 720p, F-bit is always set to "zero".

V = 0 : other than Field Blanking (V - Blanking)

V = 1 : Field Blanking (V - Blanking)

H = 0 : SAV H = 1 : EAV

P3, P2, P1, P0: Protection bits. Those bits are ignored in the AK8823.

In 525i (480i) / 625i (576i) input cases

| 111 0201 ( 1001 )  | 601 / 7 6261 \ 67 61 / 11 put 64666 |          |      |      |      |      |     |      |      |          |      |     |    |     |    |

|--------------------|-------------------------------------|----------|------|------|------|------|-----|------|------|----------|------|-----|----|-----|----|

| Y port data        | Cr359                               | Y719     | 0xFF | 0x00 | 0x00 | 0xXX |     | 0xFF | 0x00 | 0x00     | 0xXX | Cb0 | Y0 | Cr0 | Y1 |

| Pixel<br>No.(60Hz) | 1438                                | 1439     | 1440 | 1441 | 1442 | 1443 |     | 272  | 273  | 1714     | 1715 | 0   | 1  | 2   | 3  |

| Pixel<br>No.(50Hz) | 1438                                | 1439     | 1440 | 1441 | 1442 | 1443 |     | 284  | 285  | 1716     | 1727 | 0   | 1  | 2   | 3  |

|                    |                                     | <u> </u> | EAV  |      |      |      | SAV |      |      | <u> </u> |      |     |    |     |    |

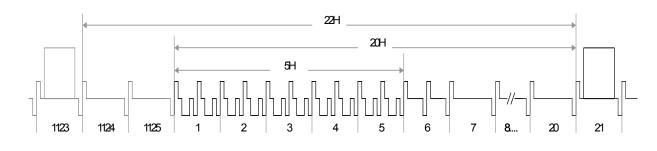

In 525p (480p) / 625p (576p) input cases

| ш о∠ор ( тоор      | 220 Y 100 P / 1020 Y 01 0 P / 11 Pat 00000 |      |      |      |      |      |       |      |      |      |      |    |    |    |    |

|--------------------|--------------------------------------------|------|------|------|------|------|-------|------|------|------|------|----|----|----|----|

| Y port data        | Y718                                       | Y719 | 0xFF | 0x00 | 0x00 | 0xXX |       | 0xFF | 0x00 | 0x00 | 0xXX | Y0 | Y1 | Y2 | Y3 |

| Pixel<br>No.(60Hz) | 718                                        | 719  | 720  | 721  | 722  | 723  |       | 854  | 855  | 856  | 857  | 0  | 1  | 2  | 3  |

| Pixel<br>No.(50Hz) | 718                                        | 719  | 720  | 721  | 722  | 723  | ••••• | 860  | 861  | 862  | 863  | 0  | 1  | 2  | 3  |

|                    | EAV                                        |      |      |      |      |      |       | 9    | SAV  |      |      |    |    |    |    |

In 1080i input case

| Y port data        | Υ    | Υ    | 0xFF | 0x00 | 0x00 | 0xXX | 0xFF     | 0x00 | 0x00 | 0xXX | Y0 | Y1 | Y2 | Y3 |

|--------------------|------|------|------|------|------|------|----------|------|------|------|----|----|----|----|

| Pixel<br>No.(60Hz) | 1918 | 1919 | 1920 | 1921 | 1922 | 1923 | 2196     | 2197 | 2198 | 2199 | 0  | 1  | 2  | 3  |

| Pixel<br>No.(50Hz) | 1918 | 1919 | 1920 | 1921 | 1922 | 1923 | <br>2636 | 2637 | 2638 | 2639 | 0  | 1  | 2  | 3  |

| TRS                |      |      |      | E/   | ٩V   |      |          | SA   | ٩V   |      |    |    |    |    |

In 720pi input case

| Y port data        | Υ    | Υ    | 0xFF | 0x00 | 0x00 | 0xXX | 0xFF     | 0x00 | 0x00 | 0xXX | Y0 | Y 1 | Y 2 | Υ3 |

|--------------------|------|------|------|------|------|------|----------|------|------|------|----|-----|-----|----|

| Pixel<br>No.(60Hz) | 1278 | 1279 | 1280 | 1281 | 1282 | 1283 | 1646     | 1647 | 1648 | 1649 | 0  | 1   | 2   | 3  |

| Pixel<br>No.(50Hz) | 1278 | 1279 | 1280 | 1281 | 1282 | 1283 | <br>1976 | 1977 | 1978 | 1979 | 0  | 1   | 2   | 3  |

| TRS                |      |      |      | E    | ٩V   |      |          | S    | ٩V   |      |    |     |     |    |

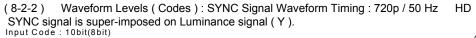

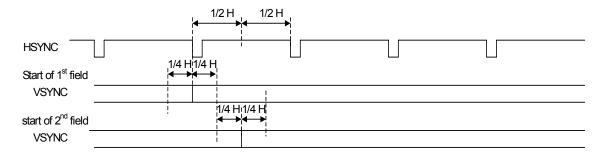

#### (2) EAV / SAV Codes and Line Synchronization (HD)

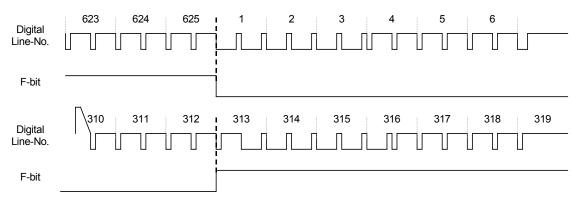

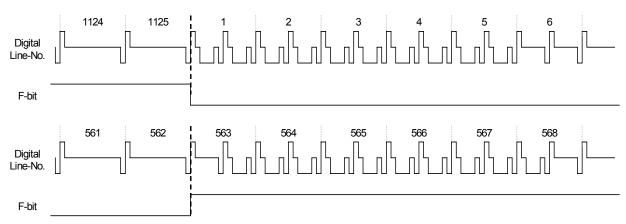

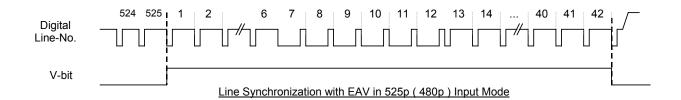

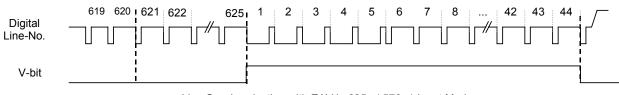

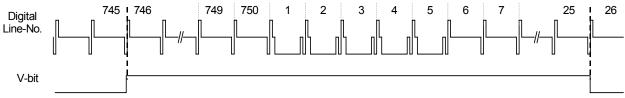

The AK8823 makes Vertical Synchronization (Line Synchronization) with either F-bit or V-bit of EAV.

In the Interlaced input signal case, it is synchronized with F-bit.

In the Progressive input signal case, it is synchronized with V-bit.

#### F-bit of EAV / SAV and Line relation is as follows.

|   | F-bit | 525i(480i)                         | 625i(576i)        | 525P/625P       | 1080i              | 720P            |

|---|-------|------------------------------------|-------------------|-----------------|--------------------|-----------------|

| Ī | 0     | Line4 - Line265                    | Line1 - Line312   |                 | Line1 - Line563    |                 |