### PLL0305A

Serial Input PLL Frequency Synthesizer

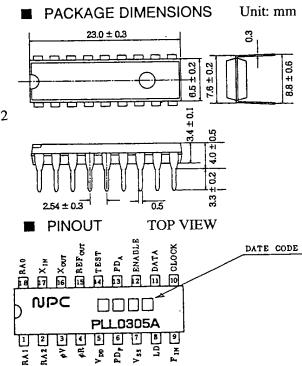

#### VIEW

305A is a PLL synthesizer LSI fabricated using NPC's original molybdenum-gate CMOS. The input frequency divider ratio can be set by externally inputting serial data. The frequency divider ratio can be selected from 8 choices stored in the built-in ROM.

## URES 1Hz

der ratios

(5 V, Fin)

$\mathbf{MHz} \qquad \qquad (5 \text{ V}, \mathbf{X}_{\text{IN}})$

rence frequency

16, 512, 1024, 2048,

3668, 4096, 6144, 8192

t frequency divider

S

5 to 16383

k detector pin

be used with active or passive filters

#### **ICATIONS**

nning receivers

ateur radios

lios

er

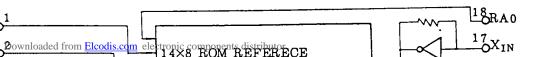

CK DIAGRAM

### PLL0305A

### N DESCRIPTION

| E                                                                                      | .,                                                                                           | DES                                           | CRIPI                         | ION                                       |                                                     | NAME<br>(No.)                 | DESCRIPTION                                                                                                                                                                                                                                                |  |  |  |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------|-------------------------------------------|-----------------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                        | Input pins used to select the reference frequency divider ratio from the table.              | RA2<br>0<br>0<br>0<br>0<br>1<br>1<br>1        | RA1 0 0 1 1 0 0 1 1 1 0 1 1 1 | RAO 0 1 0 1 0 1 0 1 0 1 1 1 1 1 1 1 1 1 1 | Divider ratio  16 512 1024 2048 3668 4096 6144 8192 | CLOCK<br>(10)<br>DATA<br>(11) | Shift register data and clock input. Data shifts by 1 bit when CLOCK changes from "L" to "H".  The shift register configuration is shown below.  Make the input data format coincide with the shift register configuration.  Input frequency divider ratio |  |  |  |

|                                                                                        | Outputs for a lesingle-ended, to use to the corresponding PDP passive PDA active ØV, ØR diff | ristate o<br>espondi<br>ve filter<br>e filter | outputs<br>ng out             | . Com<br>put pin                          | nect the filter in                                  | ENABLE (12) TEST (14)         | Shift direction  14 bits  Latch write signal. When "H", writing is enabled. Internal pull-up resistor.  Test pin. Should be left open during normal operation. Internal pull-down resistor.                                                                |  |  |  |

|                                                                                        | Power supply Ground                                                                          | 4.5 to 5                                      | 5.5 V                         |                                           |                                                     | REFour                        | Buffered reference oscillator (XIN, XOUT) output. Recommend to connect a load to this pin for stable oscillation.                                                                                                                                          |  |  |  |

|                                                                                        | Unlock detecti<br>When locked,                                                               |                                               |                               | locked                                    | , it is "L."                                        | Xout (16) Xin (17)            | Pin for a quartz crystal oscillator. Internal feedback resistor is provided for AC coupling. Input an external clock to the XIN pin via a capacitor.                                                                                                       |  |  |  |

| Input frequency divider (N COUNTER) input. Internal feedback resistor for AC coupling. |                                                                                              |                                               |                               |                                           |                                                     |                               |                                                                                                                                                                                                                                                            |  |  |  |

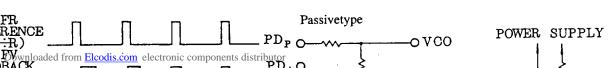

# HASE DETECTOR TIMING CHART

# LOWPASS FILTER

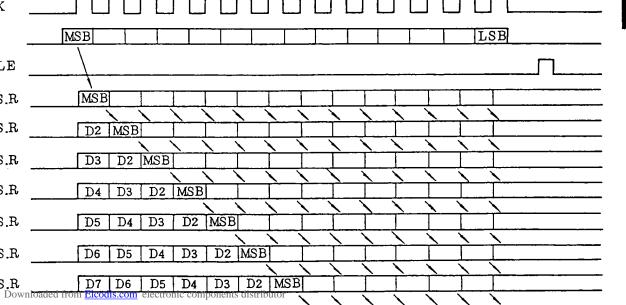

IING CHART Input frequency divider data setting 1 2 3 4 5 6 7 8 9 10 11 12 13 NEW DATA OLDDATA MSB D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 LSB MSB D2 D3 D4 D5 put data MSB first.

ata is input on the rising edge of CLOCK, so it is necessary to change data on the falling edge of LOCK.

PLL0305A

Thile the ENABLE signal is "H", data is transferred from the shift register to the input frequency ivider's latch. Therefore, ENABLE must go "L" while data is being written into the shift register.

#### PLL0305A

## ABSOLUTE MAXIMUM RATINGS

| ITEM               | SYMBOL                           | RATING                        | UNIT |

|--------------------|----------------------------------|-------------------------------|------|

| oly voltage        | V <sub>DD</sub> -V <sub>SS</sub> | -0.3 to +7.0                  | y    |

| t voltage          | Vin                              | $V_{SS}$ -30 to $V_{DD}$ +0.3 | V    |

| rating temperature | TOPR                             | -30 to +80                    | °C   |

| age temperature    | Tsrg                             | -40 to +125                   | °C   |

| lering temperature | Tsld                             | 260±5                         | °C _ |

| lering time        | tsin                             | 10                            | Sec  |

Setup time, hold time

# LECTRICAL CHARACTERISTICS

$V_{SS} = 0V$ ,  $V_{DD} = 4.5$  to 5.5V, Ta = -30 to +80 °C

|                          | T                  | ,                                                                                 | LIMITS                                           |       |                      |      |                   |

|--------------------------|--------------------|-----------------------------------------------------------------------------------|--------------------------------------------------|-------|----------------------|------|-------------------|

| ITEM                     | SYMBOL             | CONDITIONS                                                                        | MIN                                              | TYP   | MAX                  | UNIT | REMARKS           |

| ply voltage              | V <sub>DD</sub>    |                                                                                   | 4.5                                              |       | 5.5                  | V    |                   |

| rent consumption         | IDD                | Fin=sine wave 30MHz 500mV <sub>p-p</sub><br>Xin=sine wave 15MHz 1V <sub>p-p</sub> |                                                  | 4.0   | 8.0                  | mA   | * Output pin open |

| kimum operating uency 1  | FMAXI              | Fin=sine wave 500mV <sub>p-p</sub>                                                | 30                                               | 50    |                      | MHz  | Fin               |

| ximum operating quency 2 | FMAX2              | X <sub>IN</sub> =sine wave 1V <sub>p-p</sub>                                      | 15                                               | 50    |                      | MHz  | Xin               |

| ut voltage               | Vinac              | Fin=AC coupling                                                                   | 0.5                                              |       | V <sub>DD</sub> -0.5 | V    | Fin               |

| Ü                        |                    | X <sub>IN</sub> =AC coupling                                                      | 1.0                                              |       | V <sub>DD</sub> -0.5 |      | Xin               |

| ut voltage               | ViH                |                                                                                   | V <sub>DD</sub> -0.3                             |       | V <sub>DD</sub>      | V    | RA0 to<br>RA2DAT, |

| · ·                      | VIL                |                                                                                   | 0                                                |       | 0.5                  |      | CLK, LE           |

| ut current 1             | Ііні               | V <sub>IHI</sub> =V <sub>DD</sub>                                                 |                                                  |       | 15                   | μА   | Fin, Xin          |

|                          | IıLı               | V <sub>IL1</sub> =0V                                                              | <del>                                     </del> |       | 15                   |      |                   |

| ut current 2             | I <sub>1L2</sub>   | V <sub>1L2</sub> =0V                                                              |                                                  |       | 30                   | μA   | ENABLE            |

| ut current 3             | Іінз               | V <sub>IH3</sub> =V <sub>DD</sub> Ta=25°C                                         |                                                  | 0.001 | 0.1                  | μΑ   | RA0 to RA2        |

|                          | III.3              | V <sub>1L3</sub> =0V Ta=25°C                                                      |                                                  | 0.001 | 0.1                  |      | DAT, CLK          |

| tput current             | Іон                | Voh=Vdd-0.4V                                                                      | 0.4                                              |       | ļ                    | μA   | øV, øR, PDp       |

| A, REFOUT                | IoL                | VoL=0.4V                                                                          | 0.4                                              |       |                      |      | PDA, REFOUT       |

| tout leak current        | ILH                | V <sub>LH</sub> =V <sub>DD</sub> Ta=25°C                                          |                                                  | 0.001 | 0.1                  | μА   | PDp               |

| Downloaded from Elco     | <u>dis.com</u> ele | ctronic components distributor                                                    |                                                  | 0.001 | 0.1                  |      | PDA               |