# **Data Sheet: ACD82124**

24 Ports 10/100 Fast Ethernet Switch Controller

Rev.1.1.1.F Last Update: November 5, 1998 Subject to Change

Please check ACD's website for update information before starting a design

Web site: http://www.acdcorp.com

#### or Contact ACD at:

Email: support@acdcorp.com Tel: 408-433-9898x115 Fax: 408-545-0930

## **ACD Confidential Material**

For ACD authorized customer use only. No reproduction or redistribution without ACD's prior permission.

## **Table of Contents**

| Sec | tion                                        | Page |

|-----|---------------------------------------------|------|

| 1   | General Description                         | 3    |

| 2   | Main Features                               | 3    |

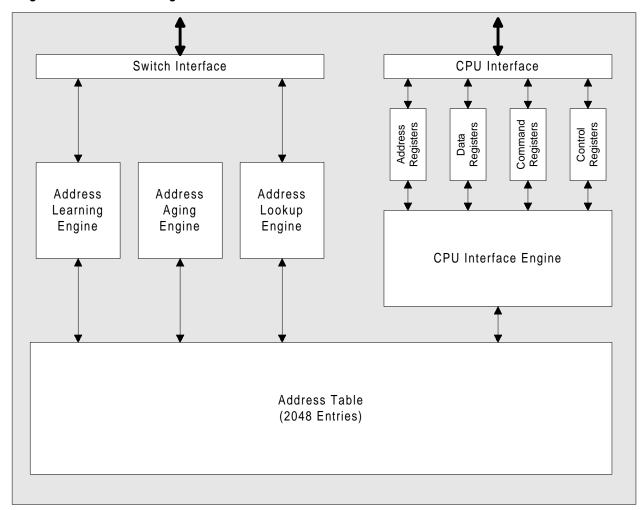

| 3   | System Block Diagram                        | 3    |

| 4   | System Description                          | 4    |

| 5   | Functional Description                      | 4    |

| 6   | Interface Description                       | 10   |

| 7   | Register Description                        | 16   |

| 8   | Pin Description                             | 27   |

| 9   | Timing Description                          | 32   |

| 10  | Electrical Specifications                   | 38   |

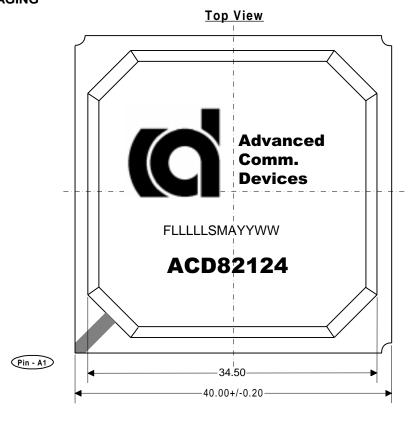

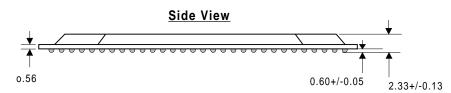

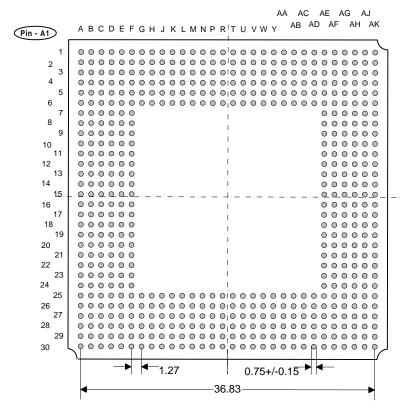

| 11  | Packaging                                   | 39   |

|     | Appendix                                    |      |

| A1  | Address Resolution Logic (The built-in ARL) | 40   |

#### 1. GENERAL DESCRIPTION

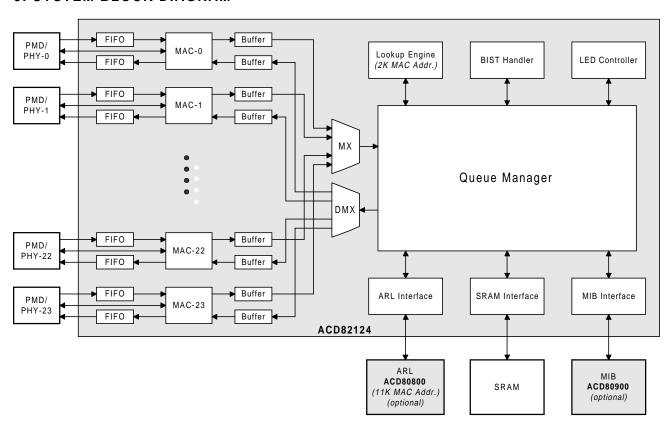

The ACD82124 is a single chip implementation of a 24 port 10/100 Ethernet switch system intended for IEEE 802.3 and 802.3u compatible networks. The device includes 24 independent 10/100 MACs. Each MAC interfaces with an external PMD/PHY device through a standard MII interface. Speed can be automatically configured through the MDIO port. Each port can operate at either 10Mbps or 100Mbps. The core logic of the ACD82124, implemented with patent pending BASIQ (Bandwidth Assured Switching with Intelligent Queuing) technology, can simultaneously process 24 asynchronous 10/100Mbps port traffic. The Queue Manager inside the ACD82124 provides the capability of routing traffic with the same order of sequence, without any packet loss.

A complete 24 port 10/100 switch can be built with the use of the ACD82124, 10/100 PHY and ASRAM. The MAC addresses can be expanded from the built-in 2K to 11K by the use of ACD's external ARL chip (ACD80800 Address Resolution Logic). Advanced network management features can be supported with the use of ACD's MIB (ACD80900 Management Information Base) chip.

#### 2. FEATURES

- 24 ports 10/100 auto-sensing with MII interface

- Half-duplex operation, with optional full-duplex configuration by combining 2 adjacent ports

- 2.4 Gbps aggregated throughput

- True non-blocking switch architecture

- Flexible port configuration (up to 12 full duplex 10/ 100 ports, up to 24 half duplex 10/100 ports)

- Built-in storage of 2,000 MAC address

- Automatic source address learning

- Zero-Packet Loss back-pressure flow control

- Store-and-forward switch mode

- Port based V-LAN support

- UART type CPU management interface

- Supports up to 11K MAC addresses with the ACD80800

- RMON and SNMP support with ACD80900

- Status LEDs: Link, Speed, Full Duplex, Transmit, Receive, Collision and Frame Error

- Reversible MII option for CPU and expansion port interface

- Wire speed forwarding rate

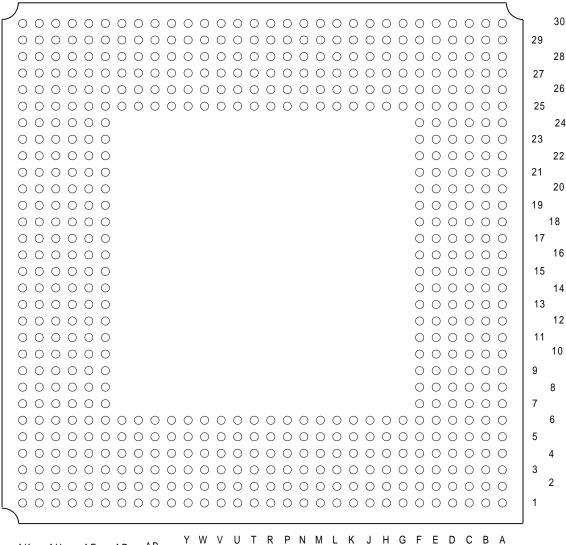

- 576 pin BGA package

- 3.3V power supply, 3.3V I/O with 5V tolerance

#### 3. SYSTEM BLOCK DIAGRAM

#### 4. SYSTEM DESCRIPTION

The ACD82124 is a single chip implementation of a 24-port Fast Ethernet switch. Together with external ASRAM and transceiver devices, it can be used to build a complete desktop class Fast Ethernet switch. Each individual port can be either auto-sensed or manually selected to run at 10 Mbps or 100 Mbps speed rate, under Half Duplex mode.

The ACD82124 Ethernet switch contains three major functional blocks: the Media Access Controller (MAC), the Queue Manager, and the Lookup Engine.

There are 24 independent MACs within the ACD82124. The MAC controls the receiving, transmitting, and deferring process of each individual port, in accordance to IEEE 802.3 and 802.3u standard. The MAC logic also provides framing, FCS checking, error handling, status indication and back-pressure flow control functions. Each MAC interfaces with an external transceiver through standard MII interface.

The device utilizes ACD's proprietary BASIQ (Bandwidth Assured Switching with Intelligent Queuing) technology. It is a technology to enforce the first-in-first-out rule of Ethernet Bridge-type devices in a very efficient way. The technology enables a true non-blocking frame switching operation at wire speed for a high throughput and high port density Ethernet switch.

The on-chip 2,000 MAC addresses Lookup Engine maps each destination address into a destination port. Each port's MAC address is automatically learned by the Lookup Engine when it receives a frame with no error. Therefore, the ACD82124 alone can be used to build a desktop class Fast Ethernet switch without any additional switching devices.

The MAC address space can be expanded from 2,000 to 8,000 per system by using the ACD80800. The ACD82124 has a proprietary ARL interface that allows direct connection with ACD80800. System designers can also use this ARL interface to implement a vendor-specific address resolution algorithm.

The ACD82124 provides management support through its MIB (Management Information Base) interface. The MIB interface can be used to monitor all traffic activities of the switch system. ACD's supporting chip (the ACD80900) provides a full set of statistical counters to support both SNMP and RMON network management. The MIB interface can also be used by system designers to implement vendor-specific network management functionality.

Among the 24 MII interfaces, 10 of them can be configured as reversed MII, to connect directly with standalone MAC controller devices. A MAC in the ACD82124 can be viewed logically as a PHY device if it is configured as a reversed MII interface. The reversed MII is intended for a CPU network interface, or expansion port interface.

A system CPU can access various registers inside the ACD82124 through a serial CPU management interface. The CPU can configure the switch by writing into the appropriate registers, or retrieve the status of the switch by reading the corresponding registers. The CPU can also access the registers of external transceiver (PHY) devices through the CPU management interface.

#### 5. FUNCTIONAL DESCRIPTION

The MAC controller performs transmit, receive, and defer functions, in accordance to IEEE 802.3 and 802.3u standard specification. The MAC logic also handles frame detection, frame generation, error detection, error handling, status indication and flow control functions.

#### Frame Format

The ACD82124 assumes that the received data packet will have the following format:

## Preamble SFD DA SA Type/Len Data FCS

#### Where,

- Preamble is a repetitive pattern of '1010....' of any length with nibble alignment.

- SFD (Start Frame Delimiter) is defined as an octet pattern of 10101011.

- DA (Destination Address) is a 48-bit field that specifies the MAC address of the destined DTE. If the first bit of DA is 1, the ACD82124 will treat the frame as a broadcast/multicast frame and will forward the frame to all ports within the source port's VLAN except the source port itself or BPDU address.

- SA (Source Address) is a 48-bit field that contains the MAC address of the source DTE that is transmitting the frame to the ACD82124. After a frame is received with no error, the SA is learned as the port's MAC address.

- Type/Len field is a 2-byte field that specifies the type (DIX Ethernet frame) or length (IEEE 802.3 frame) of the frame. The ACD82124 does not process this information.

- Data is the encapsulated information within the Ethernet Packet. The ACD82124 does not process any of the data information in this field.

- FCS (Frame Check Sequence) is a 32-bit field of a CRC (Cyclic Redundancy Check) value based on the destination address, the source address, the type/length and the data field. The ACD82124 will verify the FCS field for each frame. The procedure of computing FCS is described in section of "FCS Calculation."

#### Start of Frame Detection

When a port's MAC is idle, assertion of the RXDV in the MII interface will cause the port to go into the receive state. The MII presents the received data in 4-bit nibbles that are synchronous to the receive clock (25Mhz or 2.5MHz). The ACD82124 will convert this data into a serial bit stream, and attempt to detect the occurrence of the SFD (10101011) pattern. All data prior to the detection of SFD are discarded. Once SFD is detected, the following frame data are forwarded and stored in the buffer of the switch.

#### Frame Reception

Under normal operating conditions, the ACD82124 expects a received frame to have a minimum inter frame gap (IFG). The minimum IFG required by the device is 80 BT (Bit Time).

In the event the ACD82124 receives a packet with IFG less than 80BT, the ACD82124 does not guarantee to be able to receive the frame. The packet will be dropped if the ACD82124 cannot receive the frame.

The device will check all received frames for errors such as symbol error, FCS error, short event, runt, long event, jabber etc. Frames with any kind of error will not be forwarded to any port.

#### Preamble Bit Processing

The preamble bit in the header of each frame will be used to synchronize the MAC logic with the incoming bit stream. The minimum length of the preamble is 0 bits and there is no limitation on the maximum length of preamble. After the receive data valid signal RXDV is asserted by the external PHY device, the port will wait for the occurrence of the SFD pattern (10101011) and then start a frame receiving process.

#### Source Address and Destination Address

After a frame is received by the ACD82124, the embedded destination address and source address are retrieved. The destination address is passed to the lookup table to find the destination port. The source address is automatically stored into the address lookup table. For applications that use an external ARL, the ACD82124 will disable the internal lookup table and pass the DA and SA to the external ARL for address lookup and learning.

A port's MAC address register is cleared on powerup, hardware reset, or when the port enters into Link Fail state. If the SA aging option is enabled (*Register-*16 bit 4), the learned SA will be cleared if it does not reappear within five minutes.

During the receive process, the Lookup Engine will attempt to match the destination address with the addresses stored in the address table. If a match is found, a link between the source port and the destination port is established. If an external ARL is used, the ACD82124 indicates the presence of a 48-bit DA through the status line of the ARL interface. The external ARL will use the value of DA for address comparison and return a result of the lookup to the ACD82124.

#### Frame Data

Frame data are transparent to the ACD82124. The ACD82124 will forward the data to the destination port(s) without interpreting the content of the frame data field.

#### **FCS Calculation**

Each port of the ACD82124 has CRC checking logic to verify if the received frame has a correct FCS value. A wrong FCS value is an indication of a fragmented frame or a frame with frame bit error. The method of calculating the CRC value is using the following polynomial,

$$G(x) = x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^{8} + x^{7} + x^{5} + x^{4} + x^{2} + x + 1$$

as a divider to divide the bit sequence of the incoming frame, beginning with the first bit of the destination address field, to the end of the data field. The result of the calculation, which is the residue after the polynomial division, is the value of the frame check sequence. This value should be equal to the FCS field appended at the end of the frame. If the value does not match the FCS field of the frame, the Frame Bit Error LED of the port will be turned on once and the packet will be dropped.

#### Frame Length

During the receiving process, the MAC will monitor the length of the received frame. Legal Ethernet frames should have a length of not less than 64 bytes and no more than 1518 bytes. If the carrier sense signal of a frame is asserted for less than 76 BT, the frame is flagged with short event error. If the length of a frame

is less then 64 bytes, the frame is flagged with runt error.

In order to support an application where extra byte length is required, an Extra-Long-Frame option is provided. When the Extra long frame option is enabled (*Table 12: CFG7*), only frames longer than 1530 bytes are marked with a long event error. Frame length is measured from the first byte of DA to the last byte of FCS.

#### Frame Filtering

Frames with any kind of error will be filtered. Types of error include code error (indicated by assertion of RXER signal), FCS error, alignment error, short event, runt, and long event.

Any frame heading to its own source port will be filtered. If external ARL is used, the ACD82124 will filter the frame as directed by the external ARL.

If the *Spanning Tree Support* option is enabled, frames containing DA equal to any reserved Bridge Management Group Address specified in Table 3.5 of IEEE 802.1d will not be forwarded to any ports, except the Port-23, which may receive BPDU frames. If spanning tree support is not enabled, frames with DA equal to the reserved Group Address for PBDU will be broadcasted to all ports in the same VLAN of the source port.

#### **Jabber Lockup Protection**

If a receiving port is active continuously for more than 50,000 BT, the port is considered to be jabbering. A jabbering port will automatically be partitioned from the switch system in order to prevent it from impairing the performance of the network. The partitioned port will be re-activated as soon as the offending signal discontinues.

#### Excessive Collision

In the event that there are more than 16 consecutive collision, the ACD82124 will reset the counter to zero and retransmit the packet. This implementation insures there is no packet loss even under channel capture situation. However, ACD82124 has an option to drop the packet on excessive collision. When this option is enabled (*Table 12: CG11*), the frame will be dropped after 16 consecutive collisions.

#### **False Carrier Events**

If the RXER signal in the MII interface is asserted when the receive data valid (RXDV) signal is not asserted, the port is considered to have a false carrier event. If a port has more than two consecutive false carrier events, the port will automatically be partitioned from the switch system. The partitioned port will be re-activated if it has been idling for 33,000 BT or it has received a valid frame.

#### Frame Forwarding

If the first bit of the destination address is 0, the frame is handled as a unicast frame. The destination address is passed to the Address Resolution Logic, which returns a destination port number to identify which port the frame should be forwarded to. If Address Resolution Logic cannot find any match for the destination address, the frame will be treated as a frame with unknown DA. The frame will be processed in one of two ways. If the option flood-to-all-port is enabled, the switch will forward the frame to all ports within the same VLAN of the source port, except the source port itself. If the option is not enabled, the frame will be forwarded to the 'dumping port' of the source port VLAN only. The dumping port is determined by the VLAN ID of the source port. If the source port belongs to multiple VLANs, a frame with unknown DA will then be forwarded to multiple dumping ports of the VLANs.

If the first bit of the destination address is a 1, the frame is handled as a multicast or broadcast frame. The ACD82124 does not differentiate a multicast packet from a broadcast packet except the reserved bridge management group address, as specified in table 3.5 of the IEEE 802.1d standard. The destination ports of the broadcast frame is all ports within the same VLAN except the source port itself.

The order of all broadcast frames with respect to the unicast frames is strictly enforced by the ACD82124.

#### Frame Transmission

The ACD82124 transmits all frames in accordance to IEEE 802.3 standard. The ACD82124 will send the frames with a guaranteed minimum interframe gap of 96 BT, even if the received frames have an IFG less than the minimum requirement. Before the transmit process is started, the MAC logic will check if the channel has been silent for more than 64 BT. Within the 64 BT silent window, the transmission process will defer on any receiving process. If the channel has been silent for more than 64 BT, the MAC will wait an addi-

tional 32 BT before starting the transmit process. In the event that the carrier sense signal is asserted by the MII during the wait period, the MAC logic will generate a JAM signal to cause a forced collision.

The MAC logic will abort the transmit process if a collision is detected through the assertion of the Col signal of the MII. Re-transmission of the frame is scheduled in accordance to IEEE 802.3's truncated binary exponential backoff algorithm. If the transmit process has encountered 16 consecutive collisions, an excessive collision error is reported, and the ACD82124 will try to re-transmit the frame, unless the drop-on-excessive-collision option of the port is enabled. It will first reset the number of collisions to zero and then start the transmission after 96 BT of interframe gap. If dropon-excessive-collision is enabled, the ACD82124 will not try to re-transmit the frame after 16 consecutive collisions. If a collision is detected after 512 BT of the transmission, a late collision error will be reported, but the frame will still be retransmitted after proper backoff time.

#### Frame Generation

During a transmit process, frame data is read out from the memory buffer and is forwarded to the destination port's PHY device in nibbles. 7 bytes of preamble signal (10101010) will be generated first followed by the SFD (10101011), and then the frame data and 4 bytes of FCS are sent out last.

#### Frame Buffer

All ports of the ACD82124 work in Store-And-Forward mode so that all ports can support both 10Mbps and 100Mbps data speed. The ACD82124 utilizes a global memory buffer pool, which is shared by all ports. The device has a unique architecture that inherits the advantage of both output buffer-based and input buffer-based switches. An output buffer-based switch stores the received data only once into the memory, and hence has a short latency. Whereas an input buffer-based switch typically has more efficient flow control.

#### Flow Control

Under half duplex mode of operation, when the switch cannot handle the receiving of an incoming frame, a collision is generated by sending a jam pattern to the sending party to force it to back off and re-transmit the frame later. Back pressure flow control is applied to a port when its reserved-buffer is full and no more shared buffer is available, or when starvation control is active.

This process is used to ensure that there are no dropped frames. *Backpressure flow control* can be disabled by setting the corresponding bit of the *register-21*.

### VLAN Support (register 23 & 24)

The ACD82124 can support up to 4 port-based security VLANs. Each port of the ACD82124 can be assigned up to four VLAN. On power up, every port is assigned to VLAN-0 as default VLAN. Frames from the source port will only be forwarded to destination ports within the same VLAN domain. A broadcast/ multicast frame will be forwarded to all ports within the VLAN(s) of the source port. A unicast frame will be forwarded to the destination port only if the destination port is in the same VLAN as the source port. Otherwise, the frame will be treated as a frame with unknown DA. Each VLAN can be assigned with a dedicated dumping port. Multiple VLANs can also share a dumping port. Unicast frames with unknown destination addresses will be forwarded to the dumping port of the source port VLAN.

Security VLAN can be disabled by setting the corresponding bit in the system configuration register (bit 8 of Register 16). When security VLAN is disabled, each VLAN becomes a leaky VLAN and is equivalent to a broadcast domain. Four dumping ports of four different virtual VLAN can be grouped together to form a fat pipe uplink (For example, if port 0&1, port 2&3, port 3&4, port 5&6 are combined to form 4 full duplex ports with 200Mbps per port throughput, these 4 full duplex ports can be grouped to form an 800 Mbps uplink port). When multiple dumping ports are grouped as a single pipe, each port has to be assigned to one and only one VLAN. A unicast frame with a matched DA will be forwarded to any destination, even if the VLAN ID is different. All unmatched DA packets will be forwarded to the designated dumping port of the source port VLAN. The broadcast and multicast packets will only be forwarded to the ports in the same VLAN of the source port. Therefore, a 200 to 800 Mbps pipe can be established by carefully grouping the dumping ports, and connects directly with the segmentation switches.

#### **Dumping Port**

Each VLAN can be assigned with a dedicated dumping port. Multiple VLANs can share a dumping port. Each dumping port can be used for up-link connection or for DTE connection. That is, the dumping port can be used to connect the switch with a computer repeater hub, a workgroup switch, a router, or any type of interconnecting device compliant with the IEEE

802.3 standard. The ACD82124 will direct the following frames to the dumping port:

- frame with unicast destination address that does not match with any port's source address within the VLAN of the source port

- frame with broadcast/multicast destination address\*

- \* See Spanning Tree Support

If the device is configured to work under Flood-to-All-Port mode (*Register 25, bit 8*), frames listed above will be forwarded to all the ports in the VLAN(s) of the source port except the source port itself.

#### Mode of Operation

By default, all ports of the ACD82124 work in half duplex mode. A full-duplex port can be configured by combining two half-duplex ports. In this case, the operation mode of the port is determined by the port's PHY device through auto-negotiation. The mode of a port can also be assigned by the duplex mode indication/assignment register (*Register 27*).

#### Spanning Tree Support

The ACD82124 supports Spanning Tree protocol. When Spanning Tree Support is enabled (Register 16 bit 1), frames from the CPU port (port 23) having a DA equal to the reserved Bridge Management Group Address for BPDU will be forwarded to the port specified by the CPU. Frames from all other ports with a DA equal to the Reserved Group Address for BPDU will be forwarded to the CPU port if the port is in the same VLAN of the CPU port. Port 23 is designed as the default CPU port. When Spanning Tree Support is disabled, all reserved group addresses for Bridge Management is treated as broadcast address.

Every port of the ACD82124 can be set to block-andlisten mode through the CPU interface. In this mode, incoming frames with DA equal to the reserved Group Address for BPDU will be forwarded to the CPU port. Incoming frames with all other DA value will be dropped. Outgoing frames with DA value equal to the Group Address for BPDU will be forwarded to the attached PHY device; all other outgoing frames will be filtered.

#### Queue Management

Each port of the ACD82124 has its own individual transmission queue. All frames coming into the ACD82124 are stored into the shared memory buffer,

and are lined up in the transmission queues of the corresponding destination port. The order of all frames, unicast or broadcast, is strictly enforced by the ACD82124. The ACD82124 is designed with a non-blocking switching architecture. It is capable of achieving wire-speed frame forwarding rate and handling maximum traffic load.

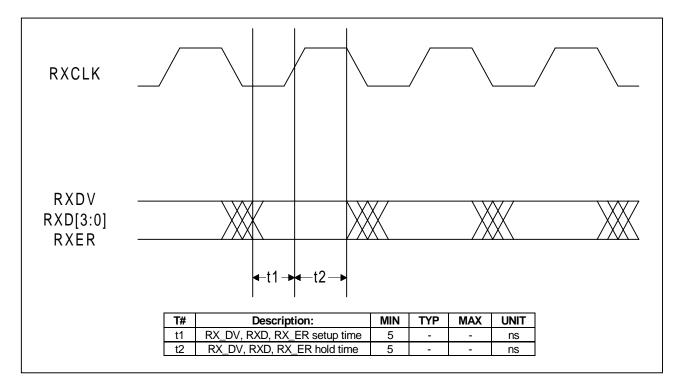

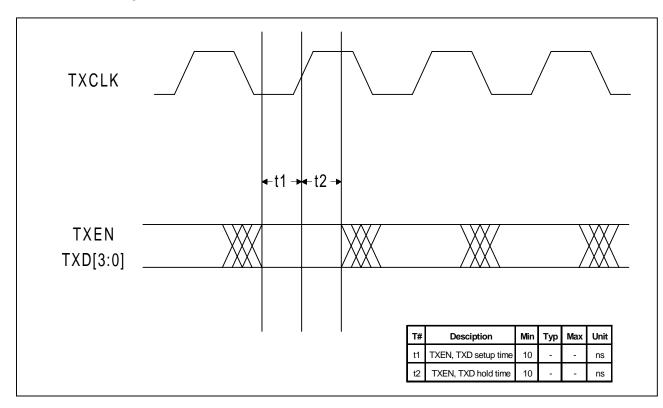

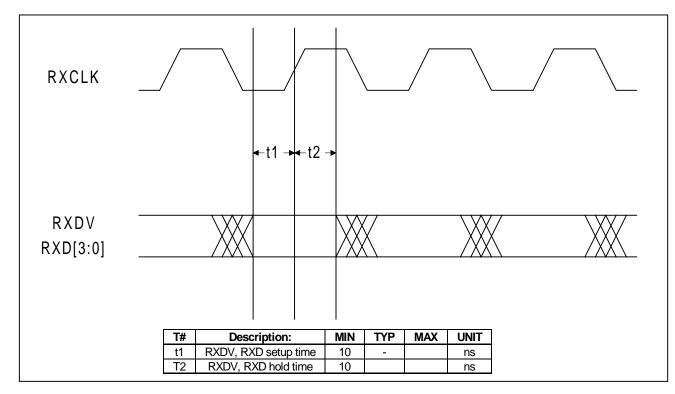

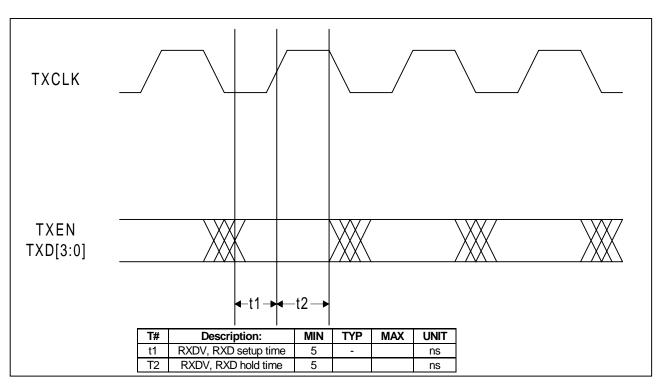

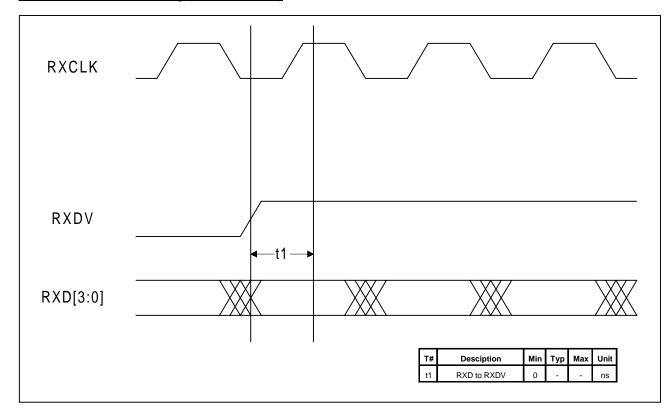

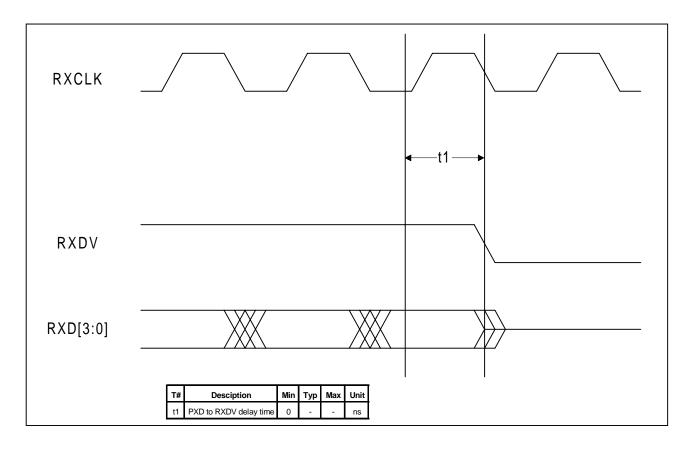

#### MII Interface

The MAC of each port of the ACD82124 interfaces with the port's PHY device through the standard MII interface. For reception, the received data (RXD) can be sampled by the rising edge (default) or the falling edge of the receive clock (RXCLK). Assertion of the receive data valid (RXDV) signal will cause the MAC to look for start of Frame Delimiter (SFD). For transmission, the transmit data enable (TXEN) signal is asserted when the first preamble nibble is sent on the transmit data (TXD) lines. The transmit data are clocked out by the falling edge of the transmit clock (TXCLK).

The ACD82124 supports PHY device management through the serial MDIO and MDC signal lines. The ACD82124 can continuously poll the status of the PHY devices through the serial management interface, without CPU intervention. The ACD82124 will also configures the PHY capability field to ensure proper operation of the link. The ACD82124 also enables the CPU to access any registers in the PHY devices through the CPU interface.

#### Reversed MII Interface

Ten ports of the ACD82124 can be configured as reversed MII interface. Reversed MII behaves as a PHY MII, that the TXCLK, COL, RXD<3:0>, RXCLK, RXDV, CRS signals (names specified by IEEE 802.3u) become output signals of the ACD82124, and the TXER, TXD<3:0>, TXEN, RXER, signals (names specified by IEEE 802.3u) become input signals of the ACD82124. Reversed MII interface enables an external MAC device to be connected directly with the ACD82124.

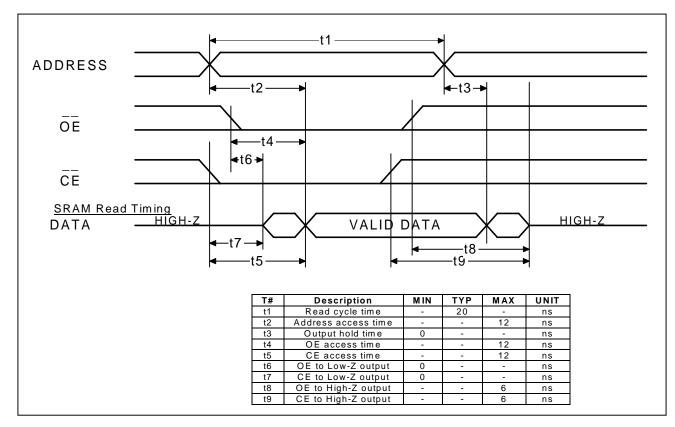

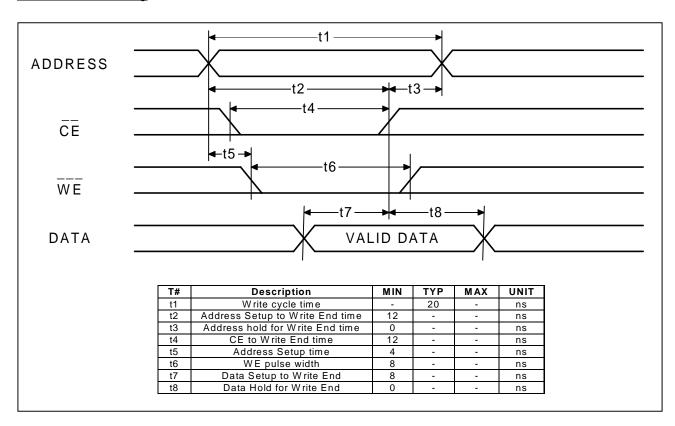

#### **ASRAM Interface**

The ACD82124 requires the use of asynchronous SRAM as a memory buffer. Each read or write cycle takes up to 20 ns. An ASRAM chip with access speed at 12 ns or faster should be used. The ASRAM interface contains a 52-bit data bus, a 17-bit address bus and 4 chip-select signals.

#### **CPU Interface**

The ACD82124 does not require a microprocessor for operation. Initialization and most configurations can be done with the use of external hardware pins. However, the ACD82124 provides a CPU interface for a microprocessor to access some of its control registers and status registers. The microprocessor can send a read command to retrieve the status of the switch, or send a write command to configure the switch through a serial interface. This interface is a commonly used UART type interface. The CPU interface can also be used to access the registers inside each PHY device connected with the ACD82124.

#### **ARL Interface**

The ACD82124 has a built-in ARL that can store up to 2,000 MAC addresses. It is actually a subset of the full ACD80800 ARL IC. For detailed description, please refer to the ACD80800 Data Sheet. The UARTID for this built-in ARL is shared with the ACD82124 (CFG16 & 17).

The ACD82124 also provides an ARL interface (*Table 12: CFG9*) for supporting additional MAC addresses. Through the ARL interface, the external ARL (ACD80800) device can tap the value of DA out from the data bus in the ASRAM interface, and execute a lookup process to map the value of DA into a port number. The external ARL device also learns the SA values embedded in the received frames via the ARL interface. The value of SA is used to build up the address lookup table.

## MIB Interface

Traffic activities on all ports of the ACD82124 can be monitored through the MIB interface. Through the MIB interface, a MIB device can view what the source port is receiving, or what the destination port is transmitting. Therefore, the MIB device can maintain a record of traffic statistics for each port to support network management. Since all received data are stored into the memory buffer, and all transmitted data are retrieved from the memory buffer, the data of the activities can also be captured from the data bus of ASRAM interface. The status of each data transaction between the ACD82124 and the ASRAM is displayed by some dedicated status signal pins of the ACD82124.

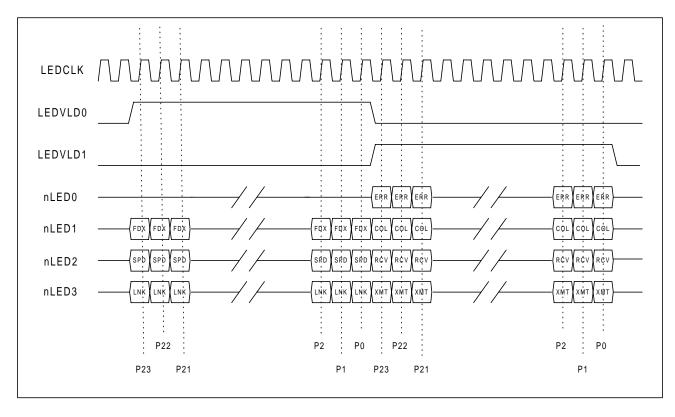

#### **LED Interface**

The ACD82124 provides a wide variety of LED indicators for simple system management. The update of the LED is completely autonomous and merely requires low speed TTL or CMOS devices as LED drivers. The status display is designed to be flexible to allow the system designer to choose those indicators appropriate for the specification of the equipment.

There are two LED control signals, LEDVLD0 and LEDVLD1, used to indicate the start and end of the LED data signal. LEDCLK signal is a 2.5MHz clock signal. The rising edge of LEDCLK should be used to latch the LED data signal into the LED driver circuitry.

The LED data signals contain Lnk, Xmt, Rcv, Col, Err, Adr, Fdx and Spd, which represent Link status, Transmit status, Receive status, Collision indication, Frame error indication, Port Address learning status, Full duplex operation and Operational Speed status respectively. These status signals are sent out sequentially from port 23 to port 0, once every 50ms. For details about the timing diagrams of the LED signals, refer to the chapter of "Timing Description"

#### Life Pulse

The ACD82124 continuously sends out life pulses to the WCHDOG pin when it is operating properly. In a catastrophic event, the ACD82124 will not send the life pulse to cause the external watchdog circuitry to time-up and reset the switch system.

#### 6. INTERFACE DESCRIPTION

#### MII Interface (MII)

The ACD82124 communicates with the external 10/100 Ethernet transceivers through standard MII interface. The signals of MII interface are described in *table-6.1*:

Table-6.1: MII Interface Signals

| Table-6.1. Will interface Signals |      |                             |  |  |  |  |

|-----------------------------------|------|-----------------------------|--|--|--|--|

| Name                              | Туре | Description                 |  |  |  |  |

| PxCRS                             | I    | Carrier sense               |  |  |  |  |

| PxRXDV                            | I    | Receive data valid          |  |  |  |  |

| PxRXCLK                           | I    | Receive clock (25/2.5 MHz)  |  |  |  |  |

| PxRXERR                           | I    | Receive error               |  |  |  |  |

| PxRXD0                            | I    | Receive data bit 0          |  |  |  |  |

| PxRXD1                            | I    | Receive data bit 1          |  |  |  |  |

| PxRXD2                            | I    | Receive data bit 2          |  |  |  |  |

| PxRXD3                            | I    | Receive data bit 3          |  |  |  |  |

| PxCOL                             | I    | Collision indication        |  |  |  |  |

| PxTXEN                            | 0    | Transmit data valid         |  |  |  |  |

| PxTXCLK                           | I    | Transmit clock (25/2.5 MHz) |  |  |  |  |

| PxTXD0                            | 0    | Transmit data bit 0         |  |  |  |  |

| PxTXD1                            | 0    | Transmit data bit 1         |  |  |  |  |

| PxTXD2                            | 0    | Transmit data bit 2         |  |  |  |  |

| PxTXD3                            | 0    | Transmit data bit 3         |  |  |  |  |

For MII interface, signal PxRXDV, PxRXER and PxRXD0 through PxRXD3 are sampled by the rising edge of PxRXCLK. Signal PxTXEN, and PxTXD0 through PxTXD3 are clocked out by the falling edge of PxTXCLK. The detailed timing requirement is described in the chapter of "Timing Description"

Ports 0,1, 2, 3, 4, 5, 6, 7, 22 and 23 can be configured as reversed MII ports (*Register 28*, the Reversed MII Enable register). These ports, when configured as "normal" MII, have the same characteristics as all other MII ports. However, when configured as reversed MII interface, they will behave logically like a PHY device, and can interface directly with a MAC device. The signal of reversed MII interface are described by *table-6.2*:

Note: \* *Collision Indication* for half-duplex mode. *Not-Ready (output)* for full duplex mode.

Table-6.2: Reversed MII Interface Signals

| Name     | Туре | Description                 |

|----------|------|-----------------------------|

| PxCRSR   | 0    | Carrier sense               |

| PxRXDVR  | I    | Transmit data valid         |

| PxRXCLKR | 0    | Transmit clock (25/2.5 MHz) |

| PxRXERR  | I    | Not-Ready (Input)           |

| PxRXD0R  | I    | Transmit data bit 0         |

| PxRXD1R  | I    | Transmit data bit 1         |

| PxRXD2R  | I    | Transmit data bit 2         |

| PxRXD3R  | I    | Transmit data bit 3         |

| PxCOLR   | 0    | Collision Indication/       |

| TAGGER   |      | Not-Ready (Output)          |

| PxTXENR  | 0    | Receive data valid          |

| PxTXCLKR | 0    | Receive clock (25/2.5 MHz)  |

| PxTXD0R  | 0    | Receive data bit 0          |

| PxTXD1R  | 0    | Receive data bit 1          |

| PxTXD2R  | 0    | Receive data bit 2          |

| PxTXD3R  | 0    | Receive data bit 3          |

For reversed MII interface, signal PxRXDVR, and PxRXD0R through PxRXD3R are clocked out by the falling edge of PxRXCLKR. Signal PxTXENR, and PxTXD0R through PxTXD3R can be sampled by the falling edge or rising edge of PxTXCLKR, depends on the setting of bit 9 of *Register 16*. The timing behavior is described in the chapter of "Timing Description."

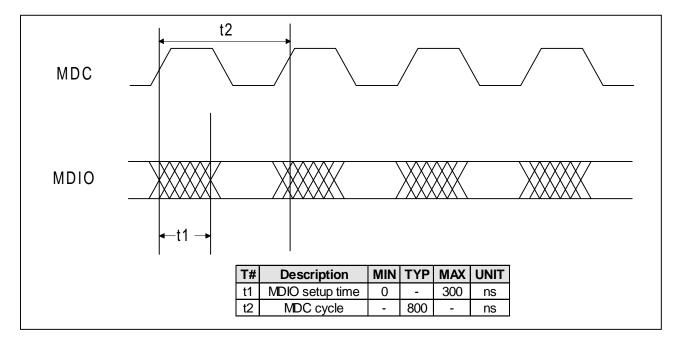

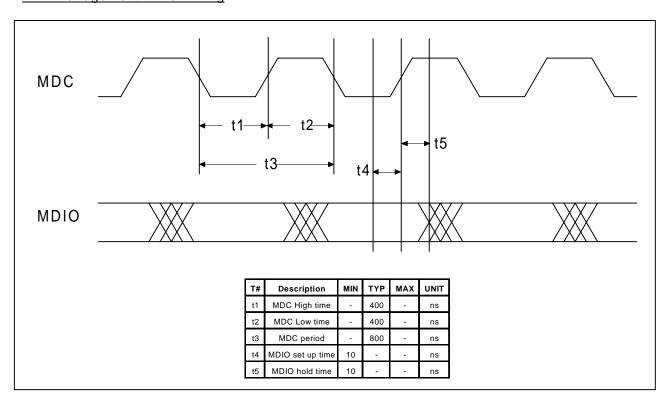

#### PHY Management Interface

All control and status registers of the PHY devices are accessible through the PHY management interface. The interface consists of two signals: MDC and MDIO, which are described in *Table-6.3*.

**Table-6.3: PHY Management Interface Signals**

| Name | Туре | Description                    |

|------|------|--------------------------------|

| MDC  | 0    | PHY management clock (1.25MHz) |

| MDIO | I/O  | PHY management data            |

Frames transmitted on MDIO has the following format (*Table-6.4*):

Table-6.4: MDIO Format

|           | 1400 0111 111210 1 0111144 |    |    |        |        |    |      |      |

|-----------|----------------------------|----|----|--------|--------|----|------|------|

| Operation | PRE                        | ST | OP | PHY-ID | REG-AD | TA | DATA | IDLE |

| Write     | 11                         | 01 | 01 | aaaaa  | rrrrr  | 10 | dd   | Z    |

| Read      | 11                         | 01 | 10 | aaaaa  | rrrrr  | Z0 | dd   | Z    |

Prior to any transaction, the ACD82124 will output thirty-two bits of '1' as a preamble signal. After the preamble, a '01' signal is used to indicate the start of the frame.

For a write operation, the device will send a '01' to signal a write operation. Following the '01' write signal will be the 5 bit ID address of the PHY device and the 5 bit register address. A '10' turn around signal is then followed. After the turn around, the 16 bit of data will be written into the register. After the completion of the write transaction, the line will be left in a high impedance state.

For a read operation, the ACD82124 will output a '10' to indicate read operation after the start of frame indicator. Following the '10' read signal will be the 5-bit ID address of the PHY device and the 5-bit register address. Then, the ACD82124 will cease driving the MDIO line, and wait for one BT. During this time, the MDIO should be in a high impedance state. The ACD82124 will then synchronize with the next bit of '0' driven by the PHY device, and continue on to read 16 bits of data from the PHY device.

The system designer should set the ID of the PHY devices as '1' for port-0, '2' for port-1, ... and '24' for port-23. The detail timing requirement on PHY management signals are described in the chapter of "Timing Description."

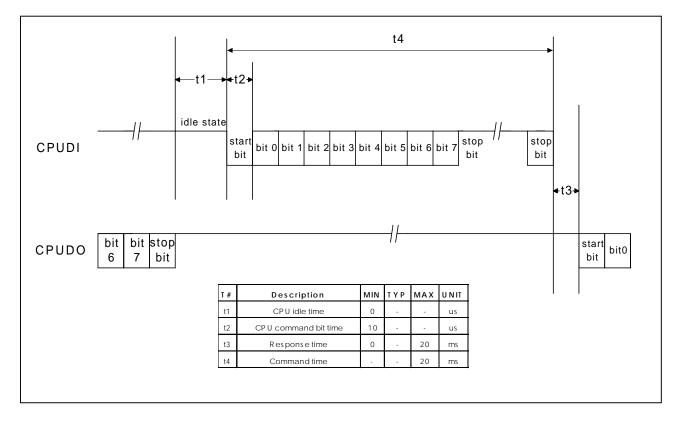

#### **CPU Interface**

The ACD82124 includes a CPU interface to enable an external CPU to access the internal registers of the ACD82124. The protocol used in the CPU is the asynchronous serial signal (UART). The baud rate can be from 1200 bps to 76800 bps. The ACD82124 automatically detects the baud rate for each command, and returns the result at the same baud rate. The signals in CPU interface are described in *Table-6.5*.

Table-6.5: CPU Interface Signals

| Name   | Туре | Description           |

|--------|------|-----------------------|

| CPUDI  | I    | CPU data input        |

| CPUDO  | 0    | CPU data output       |

| CPUIRQ | 0    | CPU interrupt request |

A command sent by CPU comes through the CPUDI line. The command consists of 9 octets. Command frames transmitted on CPUDI have the following format (*Table-6.6*):

Table-6.6: CPU Command Format

| Operation | Command  | Register | Index | Data   | Checksum |

|-----------|----------|----------|-------|--------|----------|

| Write     | 0010XX11 | 8-bit    | 8-bit | 24-bit | 8-bit    |

| Read      | 0010XX01 | 8-bit    | 8-bit | 24-bit | 8-bit    |

The byte order of data in all fields follows the big-endian convention, i.e. most significant octet first. The bit order is least significant order first. The Command octet specifies the type of the operation. Bit 2 and bit 3 of the command octet is used to specify the device ID of the chip. They are set by bit 16 and bit 17 of the *Register 25* at power on strobing. The address octet specifies the type of the register. The index octet specifies the ID of the register in a register array. For write operation, the Data field is a 4-octet value to specify what to write into the register. For read operation, the Data field is a 4-octet 0 as padded data. The checksum value is an 8-bit value of exclusive-OR of all octets in the frame, starting from the Command octet.

The ACD82124 will respond to each valid command received by sending a response frame through the CPUDO line. The response frames have the following format (*Table-6.7*):

Table-6.7: Response Format

| Response | Command  | Result | Data   | Checksum |

|----------|----------|--------|--------|----------|

| Write    | 00100011 | 8-bit  | 24-bit | 8-bit    |

| Read     | 00100001 | 8-bit  | 24-bit | 8-bit    |

The command octet specifies the type of the response. The result octet specifies the result of the execution.

The Result field in a response frame is defined as:

- 00 for no error

- 01 for Checksum

- 10 for address incorrect

- 11 for MDIO waiting time-out

For response to a read operation, the Data field is a 3octet value to indicate the content of the register. For response to a write operation, the Data field is 24 bits of 0. The checksum value is an 8-bit value of exclusive-OR of all octets in the response frame, starting from the Command octet. CPUIRQ is used to inform the CPU of some special status has been encountered by the ACD82124, like port partition, fatal system error, etc. By clearing the appropriate bit in the interrupt mask register, one can stop the specific source from generating an interrupt request. Reading the interrupt source register retrieves the source of the interrupt and clears the interrupt source register.

#### **ASRAM Interface**

All received frames are stored into the shared memory buffer through the ASRAM interface. When the destination port is ready to transmit the frame, data is read from the shared memory buffer through the ASRAM interface. The signals in ASRAM interface are described in *Table-6.8*.

**Table-6.8: ASRAM Interface**

| Name         | Туре | Description                      |

|--------------|------|----------------------------------|

| DATA0-DATA51 | 1/0  | memory data bus                  |

| ADDR0-ADDR16 | 0    | memory address bus               |

| nOE          | 0    | output enable, low active        |

| nWE          | 0    | write enable, low active         |

| nCS0 - nCS3  | 0    | chip select signals, low active. |

Data is written into the ASRAM or read from the ASRAM in 52-bit wide words. The data is a 48-bit wide value and the control is a 4 bit-wide value. ADDR specifies the address of the word, and DATA contains the content of the word. Bit 0  $\sim$  47 of DATA bus are used to pass 48-bit frame data. Bit 48 are used to indicate the start and end of a frame. Bit 49  $\sim$  51 are used to indicate the length of actual data presented on DATA0  $\sim$  DATA47.

nOE and nWE are used to control the timing of read or write operation respectively. nCSx selects the ASRAM chip corresponding to the word address. The timing requirement on ASRAM access is described in the chapter-9 "Timing Description".

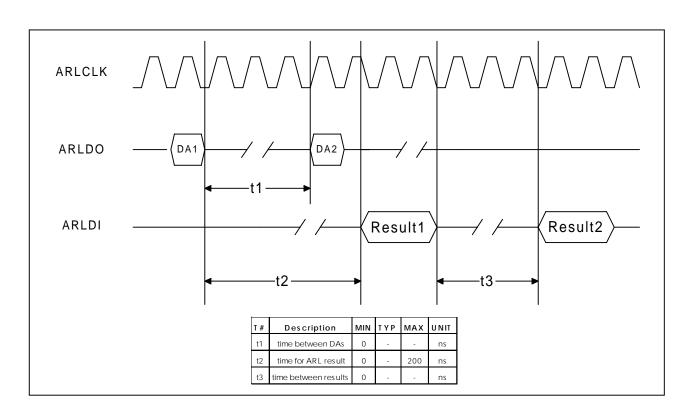

#### **ARL Interface**

ARL interface provides a communication path between the ACD82124 and an ARL device, which can provide up to 8K of additional address lookup function. As the ACD82124 receives a frame, the destination address and source address of the frame are displayed on the ARLDO data lines for the external ARL device. After the external ARL finds the corresponding destination port, it returns the result through the ARLDIx lines to

the ACD82124. The timing requirement on ARL signals is described in *Chapter-9* "Timing Description." *Table-6.9* shows the associated signals in ARL interface

Table-6.9: ARL Interface Signals

| Name            | Туре | Description                  |

|-----------------|------|------------------------------|

| ARLDO0-RLDO51   | 0    | ARL data output, shared with |

|                 |      | DATA 0 - DATA 51             |

| ARLDIR1-ARLDIR0 | 0    | ARL data direction indicator |

|                 |      | 00 for idle                  |

|                 |      | 01 for receive               |

|                 |      | 10 for transmit              |

|                 |      | 11 for control               |

| ARLSYNC         | 0    | ARL port synchronization     |

| ARLSTAT0-       | 0    | ARL data state indicator     |

| ARLSTAT3        |      |                              |

| ARLCLK          | 0    | ARL clock                    |

| ARLDIO - ARLDI3 | I    | ARL data input               |

| ARLDIV          | I    | ARL input data valid         |

The data signal is tapped from the DATA bus of ASRAM interface. Since all data of the received frames will be written into the shared memory through the DATA bus, the bus can be used to monitor occurrences of DA and SA values, indicated by the status signal of ARLSTAT. Therefore, ARLD0 through ARLD51 are the same signals of DATA0 through DATA47.

ARLDIR1 and ARLDIR0 are used to indicate the direction of data on the ARLDO bus:

- 00: Idle

- 01: for receiving data

- 10: for transmitting data

- 11: Header

ARLSYNC is used to indicate port 0 is driving the DATA bus. Since the bus is pre-allocated in time division multiplexing manner, the ARL device can determine which port is driving the DATA bus.

ARLSTAT are used to indicate the status of the data shown on the first 48 bits of DATA bus. The 4-bit status is defined as:

- 0000 Idle

- 0001 First word (DA)

- 0010 Second word (SA)

- 0011 Third through last word

- 0100 Filter Event

- 0101 Drop Event

- 0110 Jabber

- 0111 False Carrier/Deferred Transmission\*

- 1000 Alignment error/Single Collision\*

**Table-11: LED Interface Signals**

| Name    | Туре | Description            | Signal Group 1                  | Signal Group 2        |

|---------|------|------------------------|---------------------------------|-----------------------|

| LEDVLD0 | 0    | LED signal valid #0    | 1                               | 0                     |

| LEDVLD1 | 0    | LED signal valid #1    | 0                               | 1                     |

| nLEDCLK | 0    | 2.5 MHz LED clock      | -                               | -                     |

| nLED0   | 0    | Dual purpose indicator | address learning status         | frame error indicator |

| nLED1   | 0    | Dual purpose indicator | full duplex indication          | collision indication  |

| nLED2   | 0    | Dual purpose indicator | port speed (1=10Mbps,0=100Mbps) | receiving activity    |

| nLED3   | 0    | Dual purpose indicator | Link status                     | transmit activity     |

- 1001 Flow Control/Multiple Collision\*

- 1010 Short Event/Excessive Collision<sup>\*</sup>

- 1011 Runt/Late Collision<sup>2</sup>

- 1100 Symbol Error

- 1101 FCS Error

- 1110 Long Event

- 1111 Reserved

ARLDIx is used to receive the lookup result from the external ARL. Result is returned by external ARL device through the ARLDIx lines. Returned data is sampled by the rising edge of ARLCLK. The ARL result has the following format:

| SID | RSLT | חוח |

|-----|------|-----|

#### Where

- SID is a 5-bit ID of the source port (0 23)

- RSLT is a 2-bit result, defined as:

- 00 reserved

- 01 matched

- 10 not matched

- 11 forced discard

- DID is a 5-bit ID of the destination port (0 23)

The start of each ARL result is indicated by assertion of ARLDIV signal.

#### **LED Interface**

The signals in the LED interface is described in *table-6.10*:

The status of each port is displayed on the LED interface for every 50ms. LEDVLD0 and LEDVLD1 are used to indicate the start and end of the LED data. LED data is clocked out by the falling edge of LEDCLK, and should be sampled by the rising edge of LEDCLK. LED data of port 23 are clocked out first, followed by port 22 down to port 0. All LED signals are low active.

<sup>\*</sup>Note: error type depends on whether the port is receiving or transmitting.

#### Configuration Interface

There are 20 pins whose pull-up or pull-down state will be used as Power-On-Strobing configuration data (*Register 25*, & *CFG0 - CFG19*) to specify various working modes of the ACD82124. The CFG pins are shared with other functional pins of the ACD82124. The pull-high or pull-low status of the CFG pins are used to indicate specific configuration settings, described in *Table-6.11*. The register description section will provide more details about the *POS Configuration register*.

Table-6.11: Configuration Interface

| Pin Name | Register #     | Bit # | Setting       |

|----------|----------------|-------|---------------|

| P7TXD0   |                | 0     |               |

| P7TXD1   |                | 1     | 1             |

| P7TXD2   |                | 2     |               |

| P7TXD3   |                | 3     | 1             |

| P6TXD0   |                | 4     |               |

| P6TXD1   |                | 5     |               |

| P6TXD2   |                | 6     |               |

| P6TXD3   |                | 7     |               |

| LEDCLK   |                | 8     | See Table-    |

| LEDVLD0  | 25             | 9     | 7.25          |

| LEDVLD1  |                | 10    | 7.25          |

| nLED3    |                | 11    |               |

| nLED2    |                | 12    |               |

| nLED1    |                | 13    |               |

| nLED0    |                | 14    |               |

| P5TXD0   |                | 15    | 1             |

| P5TXD1   |                | 16    |               |

| P5TXD2   |                | 17    | 1             |

| P5TXD3   |                | 18    |               |

| P2TxD0   |                | 0     |               |

| P2TxD1   |                | 1     | 1             |

| P2TxD2   |                | 2     |               |

| P2TxD3   |                | 3     |               |

| P3TxD0   |                | 4     |               |

| P3TxD1   | 26             | 5     | See Table-    |

| P3TxD2   | 20             | 6     | 7.26          |

| P3TxD3   |                | 7     |               |

| P4TxD0   |                | 8     |               |

| P4TxD1   |                | 9     |               |

| P4TxD2   |                | 10    |               |

| P4TxD3   |                | 11    |               |

| P0TXD0   |                | 0     |               |

| P0TXD1   |                | 1     |               |

| P0TXD2   |                | 2     |               |

| P0TXD3   | 30             | 3     | See Table-    |

| P1TXD0   | 30             | 4     | 7.30          |

| P1TXD1   |                | 5     |               |

| P1TXD2   |                | 6     | ]             |

| P1TXD3   |                | 7     |               |

| P23TXD0R |                | 0     | See Appendix- |

| P23TXD1R | 20, inside the | 1     | A1            |

| P23TXD2R | Internal ARL   | 2     | 0             |

| P23TXD3R |                | 3     | U U           |

Other Interface (Table-6.12)

Table-6.12: Other Interface

| Name   | Туре | Description                 |

|--------|------|-----------------------------|

| CLK50  | I    | 50 MHz clock input          |

| nRESET | I    | hardware reset              |

| WCHDOG | 0    | watch dog life pulse signal |

| VDD    | -    | 3.3 V power                 |

| VSS    | -    | ground                      |

CLK50 should come from a clock oscillator, with 0.01% (100 ppm) accuracy.

Assertion of the nRESET pin will cause the ACD82124 to go through the power-up initialization process. All registers are set to their default value after reset.

When the ACD82124 is working properly, it will generate pulses from the WCHDOG pin continuously. It is used as a safeguard, so that in case something unexpected happens, the external watchdog circuit will reset the switch system.

VDD is 3.3V power supply. VSS is power ground.

#### 7. REGISTER DESCRIPTION

Registers in the ACD82124 are used to define the operation mode of various function modules of the switch controller and the peripheral devices. Default values at power-on are defined by the factory. The management CPU (optional) can read the content of all registers and modify some of the registers to change the operation mode. Table-7.0 lists all the registers inside the switch controller.

#### **INTSRC** register (register 1)

The INTSRC register indicates the source of the interrupt request. Before the CPU starts to respond to an interrupt request, it should read this register to find out the interrupt source. This register is automatically cleared after each read. Table-7.1 lists all the bits of this register.

## SYSERR register (register 2)

The SYSERR register indicates the presence of sys-

Table-7.1: INTSRC Register

| Bit | Description                     | Default |

|-----|---------------------------------|---------|

| 0   | System initialization completed | 0       |

| 1   | System error occurred           | 0       |

| 2   | Port partition occurred         | 0       |

| 3   | ARL Interrupt                   | 0       |

| 4   | Reserved                        | 0       |

| 5   | Reserved                        | 0       |

| 6   | Reserved                        | 0       |

| 7   | Reserved                        | 0       |

tem errors. It is automatically cleared after each read. Table-7.2 lists all kind of system error.

Table-7.2: SYSERR Register

| Bit | Description             | Default |

|-----|-------------------------|---------|

| 0   | BIST failure indication | 0       |

| 1   | Reserved                | 0       |

| 2   | Reserved                | 0       |

| 3   | Reserved                | 0       |

| 4   | Reserved                | 0       |

| 5   | Reserved                | 0       |

| 6   | Reserved                | 0       |

| 7   | Reserved                | 0       |

| 8   | Reserved                | 0       |

Table-7.0: Register List

| Address | Name   | Туре | Size   | Depth | Description                          |

|---------|--------|------|--------|-------|--------------------------------------|

| 0       |        |      | •      | Reser | ved                                  |

| 1       | INTSRC | R    | 8 Bit  | 1     | Interrupt Source                     |

| 2       | SYSERR | R    | 24 Bit | 1     | System Error                         |

| 3       | PAR    | R    | 24 Bit | 1     | Port Partition Indication            |

| 4       | PMERR  | R    | 24 Bit | 1     | PHY Management Error                 |

| 5       | ACT    | R    | 24 Bit | 1     | Port Avtivity                        |

| 6-15    |        |      |        | Reser | ved                                  |

| 16      | SYSCFG | R/W  | 16 Bit | 1     | System Configuration                 |

| 17      | INTMSK | R/W  | 8 Bit  | 1     | Interrupt Mask                       |

| 18      | SPEED  | R/W  | 24 Bit | 1     | Port Speed                           |

| 19      | LINK   | R/W  | 24 Bit | 1     | Port Link                            |

| 20      | nFWD   | R/W  | 24 Bit | 1     | Port Forward Disable                 |

| 21      | nBP    | R/W  | 24 Bit | 1     | Port Back Pressure Disable           |

| 22      | nPORT  | R/W  | 24 Bit | 1     | Port Disable                         |

| 23      | PVID   | R/W  | 4 Bit  | 24    | Port VLAN ID                         |

| 24      | VPID   | R/W  | 5 Bit  | 4     | VLAN Dumping Port                    |

| 25      | POSCFG | R/W  | 19 Bit | 1     | Power-On-Strobe Configuration        |

| 26      | nPAUSE | R/W  | 24 Bit | 1     | Port Pause Frame Disable             |

| 27      | DPLX   | R/W  | 24 Bit | 1     | Port Duplex Mode                     |

| 28      | RVSMII | R/W  | 5 Bit  | 1     | Reversed MII Selection               |

| 29      | nPM    | R/W  | 24 Bit | 1     | Port PHY Management Disable          |

| 30      | ERRMSK | R/W  | 8 Bit  | 1     | Error Mask                           |

| 31      | CLKADJ | R/W  | 4 Bit  | 1     | ARL Clock Delay Adjustment           |

| 32-63   | PHYREG | R/W  | 16 Bit | 24    | Registers in PHY device, (REG# - 32) |

#### PAR register (register 3)

The PAR register indicates the presence of the partitioned ports and the port ID. A port can be automatically partitioned if there is a consecutive false carrier event, an excessive collision or a jabber. This register is automatically cleared after each read. Table-7.3 lists all the bits of this register.

Table-7.3: PAR Register

| Bit | Description                                           | Default |

|-----|-------------------------------------------------------|---------|

| 0   | 0 - Port 0 not partitioned.                           |         |

| U   | 1 - Port 0 partitioned.                               |         |

| 1   | 0 - Port 1 not partitioned.                           |         |

|     | 1 - Port 1 partitioned.                               |         |

| 2   | 0 - Port 2 not partitioned.                           |         |

|     | 1 - Port 2 partitioned.                               |         |

| 3   | 0 - Port 3 not partitioned.                           |         |

|     | 1 - Port 3 partitioned.                               |         |

| 4   | 0 - Port 4 not partitioned.                           |         |

|     | 1 - Port 4 partitioned.                               |         |

| 5   | 0 - Port 5 not partitioned.                           |         |

|     | 1 - Port 5 partitioned.                               |         |

| 6   | 0 - Port 6 not partitioned.                           |         |

|     | 1 - Port 6 partitioned.                               |         |

| 7   | 0 - Port 7 not partitioned.                           |         |

|     | 1 - Port 7 partitioned.                               |         |

| 8   | 0 - Port 8 not partitioned.                           |         |

|     | 1 - Port 8 partitioned.                               |         |

| 9   | 0 - Port 9 not partitioned.                           |         |

|     | 1 - Port 9 partitioned.                               |         |

| 10  | 0 - Port 10 not partitioned.                          |         |

|     | 1 - Port 10 partitioned.                              |         |

| 11  | 0 - Port 11 not partitioned.                          |         |

|     | 1 - Port 11 partitioned.                              | 0       |

| 12  | 0 - Port 12 not partitioned.                          |         |

|     | 1 - Port 12 partitioned.                              |         |

| 13  | 0 - Port 13 not partitioned.                          |         |

|     | 1 - Port 13 partitioned. 0 - Port 14 not partitioned. |         |

| 14  | 1 - Port 14 partitioned.                              |         |

|     | 0 - Port 15 not partitioned.                          |         |

| 15  | 1 - Port 15 partitioned.                              |         |

|     | 0 - Port 16 not partitioned.                          |         |

| 16  | 1 - Port 16 partitioned.                              |         |

|     | 0 - Port 17 not partitioned.                          |         |

| 17  | 1 - Port 17 partitioned.                              |         |

|     | 0 - Port 18 not partitioned.                          |         |

| 18  | 1 - Port 18 partitioned.                              |         |

| 40  | 0 - Port 19 not partitioned.                          |         |

| 19  | 1 - Port 19 partitioned.                              |         |

|     | 0 - Port 20 not partitioned.                          |         |

| 20  | 1 - Port 20 partitioned.                              |         |

| 24  | 0 - Port 21 not partitioned.                          |         |

| 21  | 1 - Port 21 partitioned.                              |         |

| 22  | 0 - Port 22 not partitioned.                          |         |

| 22  | 1 - Port 22 partitioned.                              |         |

| 23  | 0 - Port 23 not partitioned.                          |         |

| 23  | 1 - Port 23 partitioned.                              |         |

## PMERR register (register 4)

The PMERR register indicates the presence of PHYs that have failed to respond to the PHY Management command issued through the MDIO line. This register is automatically cleared after each read. Table-7.4 describes all the bit of this register.

Table-7.4: PMERR Register

| Table-7.4: PMERR Register |                                                                |         |  |  |

|---------------------------|----------------------------------------------------------------|---------|--|--|

| Bit                       | Description                                                    | Default |  |  |

| 0                         | 0 - Port 0 PHY responded                                       |         |  |  |

|                           | 1 - Port 0 PHY failed to respond                               |         |  |  |

| 1                         | 0 - Port 1 PHY responded                                       |         |  |  |

| '                         | 1 - Port 1 PHY failed to respond                               |         |  |  |

| 2                         | 0 - Port 2 PHY responded                                       |         |  |  |

|                           | 1 - Port 2 PHY failed to respond                               |         |  |  |

| 3                         | 0 - Port 3 PHY responded                                       |         |  |  |

|                           | 1 - Port 3 PHY failed to respond                               |         |  |  |

| 4                         | 0 - Port 4 PHY responded                                       |         |  |  |

|                           | 1 - Port 4 PHY failed to respond                               |         |  |  |

| 5                         | 0 - Port 5 PHY responded                                       |         |  |  |

|                           | 1 - Port 5 PHY failed to respond                               |         |  |  |

| 6                         | 0 - Port 6 PHY responded                                       |         |  |  |

|                           | 1 - Port 6 PHY failed to respond                               |         |  |  |

| 7                         | 0 - Port 7 PHY responded                                       |         |  |  |

| •                         | 1 - Port 7 PHY failed to respond                               |         |  |  |

| 8                         | 0 - Port 8 PHY responded                                       |         |  |  |

|                           | 1 - Port 8 PHY failed to respond                               |         |  |  |

| 9                         | 0 - Port 9 PHY responded                                       |         |  |  |

|                           | 1 - Port 9 PHY failed to respond                               |         |  |  |

| 10                        | 0 - Port 10 PHY responded                                      |         |  |  |

|                           | 1 - Port 10 PHY failed to respond                              |         |  |  |

| 11                        | 0 - Port 11 PHY responded                                      |         |  |  |

|                           | 1 - Port 11 PHY failed to respond                              | 0       |  |  |

| 12                        | 0 - Port 12 PHY responded                                      |         |  |  |

|                           | 1 - Port 12 PHY failed to respond                              |         |  |  |

| 13                        | 0 - Port 13 PHY responded                                      |         |  |  |

|                           | 1 - Port 13 PHY failed to respond<br>0 - Port 14 PHY responded |         |  |  |

| 14                        | 1 - Port 14 PHY failed to respond                              |         |  |  |

|                           | 0 - Port 15 PHY responded                                      |         |  |  |

| 15                        | 1 - Port 15 PHY failed to respond                              |         |  |  |

|                           | 0 - Port 16 PHY responded                                      |         |  |  |

| 16                        | 1 - Port 16 PHY failed to respond                              |         |  |  |

|                           | 0 - Port 17 PHY responded                                      |         |  |  |

| 17                        | 1 - Port 17 PHY failed to respond                              |         |  |  |

|                           | 0 - Port 18 PHY responded                                      | 1       |  |  |

| 18                        | 1 - Port 18 PHY failed to respond                              |         |  |  |

|                           | 0 - Port 19 PHY responded                                      |         |  |  |

| 19                        | 1 - Port 19 PHY failed to respond                              |         |  |  |

|                           | 0 - Port 20 PHY responded                                      |         |  |  |

| 20                        | 1 - Port 20 PHY failed to respond                              |         |  |  |

| 21                        | 0 - Port 21 PHY responded                                      |         |  |  |

|                           | 1 - Port 21 PHY failed to respond                              |         |  |  |

| 00                        | 0 - Port 22 PHY responded                                      | 1       |  |  |

| 22                        | 1 - Port 22 PHY failed to respond                              |         |  |  |

| 00                        | 0 - Port 23 PHY responded                                      | 1       |  |  |

| 23                        | 1 - Port 23 PHY failed to respond                              |         |  |  |

|                           |                                                                |         |  |  |

The ACT register indicates the presence of transmit or receive activities of each port since the register was last read. This register is automatically cleared after each read. Table-7.5 describes all the bits of this register.

Table-7.5: ACT Register

| Bit      | Description              | Default |

|----------|--------------------------|---------|

| 0        | 0 - Port 0 no activity   |         |

|          | 1 - Port 0 has activity  |         |

| 1        | 0 - Port 1 no activity   |         |

| '        | 1 - Port 1 has activity  |         |

| 2        | 0 - Port 2 no activity   |         |

|          | 1 - Port 2 has activity  |         |

| 3        | 0 - Port 3 no activity   |         |

| 3        | 1 - Port 3 has activity  |         |

| 4        | 0 - Port 4 no activity   |         |

| 4        | 1 - Port 4 has activity  |         |

| 5        | 0 - Port 5 no activity   |         |

|          | 1 - Port 5 has activity  |         |

| 6        | 0 - Port 6 no activity   |         |

|          | 1 - Port 6 has activity  |         |

| 7        | 0 - Port 7 no activity   |         |

| ,        | 1 - Port 7 has activity  |         |

| 8        | 0 - Port 8 no activity   |         |

|          | 1 - Port 8 has activity  |         |

| 9        | 0 - Port 9 no activity   |         |

|          | 1 - Port 9 has activity  |         |

| 10       | 0 - Port 10 no activity  |         |

| 10       | 1 - Port 10 has activity |         |

| 11       | 0 - Port 11 no activity  |         |

|          | 1 - Port 11 has activity | 0       |

| 12       | 0 - Port 12 no activity  | U       |

| 12       | 1 - Port 12 has activity |         |

| 13       | 0 - Port 13 no activity  |         |

|          | 1 - Port 13 has activity |         |

| 14       | 0 - Port 14 no activity  |         |

|          | 1 - Port 14 has activity |         |

| 15       | 0 - Port 15 no activity  |         |

|          | 1 - Port 15 has activity |         |

| 16       | 0 - Port 16 no activity  |         |

|          | 1 - Port 16 has activity |         |

| 17       | 0 - Port 17 no activity  |         |

|          | 1 - Port 17 has activity |         |

| 18       | 0 - Port 18 no activity  |         |

|          | 1 - Port 18 has activity |         |

| 19       | 0 - Port 19 no activity  |         |

|          | 1 - Port 19 has activity |         |

| 20       | 0 - Port 20 no activity  |         |

|          | 1 - Port 20 has activity |         |

| 21       | 0 - Port 21 no activity  |         |

|          | 1 - Port 21 has activity |         |

| 22       | 0 - Port 22 no activity  |         |

| <u> </u> | 1 - Port 22 has activity |         |

| 23       | 0 - Port 23 no activity  |         |

|          | 1 - Port 23 has activity |         |

#### SYSCFG register (register 16)

The SYSCFG register specifies certain system configurations. The system options are described in the chapter of "Function Description." Table-7.16 describes all the bit of this register.

Table-7.16: SYSCFG Register

| Iak      | Table-7.16: SYSCFG Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|

| Bit      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Default  |  |  |  |  |

| 0        | 0 - BIST enabled;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0        |  |  |  |  |