# MOS INTEGRATED CIRCUIT $\mu$ PD720113

# **USB 2.0 HUB CONTROLLER**

The  $\mu$ PD720113 is a USB 2.0 hub device that complies with the Universal Serial Bus (USB) Specification Revision 2.0 and works up to 480 Mbps. USB 2.0 compliant transceivers are integrated for upstream and all downstream ports. The  $\mu$ PD720113 works backward compatible either when any one of the downstream ports is connected to a USB 1.1 compliant device, or when the upstream port is connected to a USB 1.1 compliant host.

Detailed function descriptions are provided in the following user's manual. Be sure to read the manual before designing.  $\mu$ PD720113 User's Manual: S16619E

### **FEATURES**

- Compliant with Universal Serial Bus Specification Revision 2.0 (Data Rate 1.5/12/480 Mbps)

- Certified by USB implementers forum and granted the USB 2.0 high-speed Logo

- High-speed or full-speed packet protocol sequencer for Endpoint 0/1

- 7 (Max.) downstream facing ports

- All downstream facing ports can handle high-speed (480 Mbps), full-speed (12 Mbps), and low-speed (1.5 Mbps) transaction.

- Supports split transaction to handle full-speed and low-speed transaction on downstream facing ports when Hub controller is working in high-speed mode.

- One Transaction Translator per Hub and supports four non-periodic buffers

- · Support self-powered mode

- · Supports Over-current detection and Individual or ganged power control

- Supports configurable vendor ID, product ID, string descriptors and others with external Serial ROM

- Supports "non-removable" attribution on individual port

- Uses 30 MHz X'tal, or clock input

- 2.5 V and 3.3 V power supplies

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.

Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

# ORDERING INFORMATION

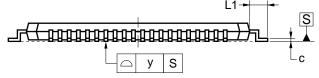

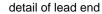

|   | Part Number       | Package                                           | Remark            |

|---|-------------------|---------------------------------------------------|-------------------|

|   | μPD720113GK-9EU   | 80-pin plastic TQFP (Fine pitch) (12 $\times$ 12) |                   |

| * | μPD720113GK-9EU-A | 80-pin plastic TQFP (Fine pitch) (12 $\times$ 12) | Lead-free product |

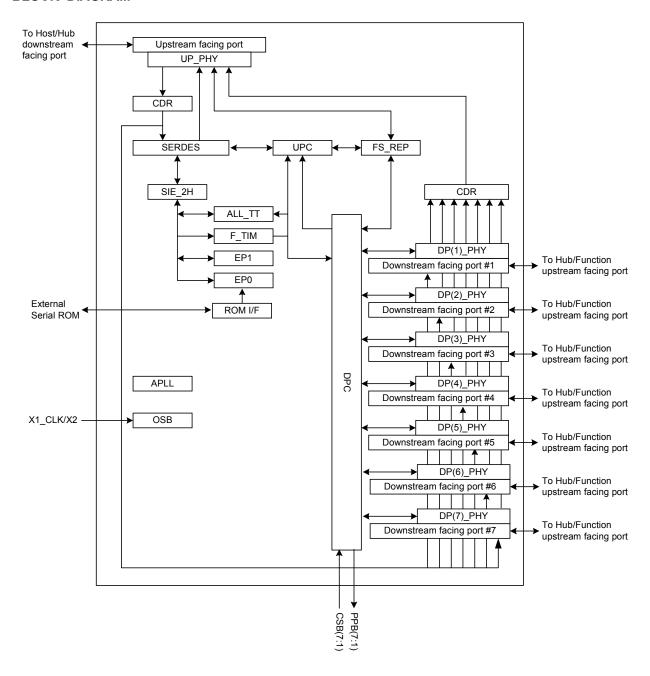

# **BLOCK DIAGRAM**

$\mu$ PD720113

APLL : Generates all clocks of Hub.

ALL\_TT : Translates the high-speed transactions (split transactions) for full/low-speed device

to full/low-speed transactions. ALL\_TT buffers the data transfer from either upstream or downstream direction. For OUT transaction, ALL\_TT buffers data from upstream port and sends it out to the downstream facing ports after speed conversion from high-speed to full/low-speed. For IN transaction, ALL\_TT buffers data from downstream ports and sends it out to the upstream facing ports after

speed conversion from full/low-speed to high-speed.

CDR : Data & clock recovery circuit

DPC : Downstream Port Controller handles Port Reset, Enable, Disable, Suspend and

Resume

DP(n)\_PHY : Downstream transceiver supports high-speed (480 Mbps), full-speed (12 Mbps), and

low-speed (1.5 Mbps) transaction

EP0 : Endpoint 0 controller

EP1 : Endpoint 1 controller

F\_TIM (Frame Timer) : Manages hub's synchronization by using micro-SOF which is received at upstream

port, and generates SOF packet when full/low-speed device is attached to

downstream facing port.

FS\_REP : Full/low-speed repeater is enabled when the  $\mu$ PD720113 are worked at full-speed

mode

OSB : Oscillator Block

ROM I/F : Interface block for external Serial ROM which contains user-defined descriptors

SERDES : Serializer and Deserializer

SIE 2H : Serial Interface Engine (SIE) controls USB2.0 and 1.1 protocol sequencer.

UP\_PHY : Upstream Transceiver supports high-speed (480 Mbps), full-speed (12 Mbps)

transaction

UPC : Upstream Port Controller handles Suspend and Resume

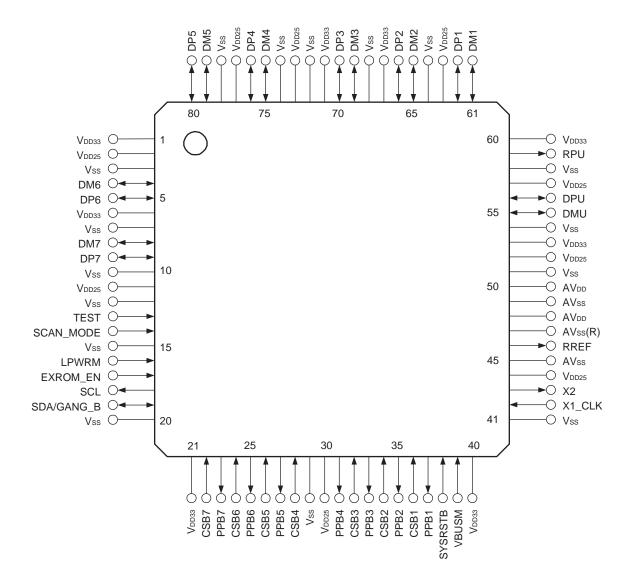

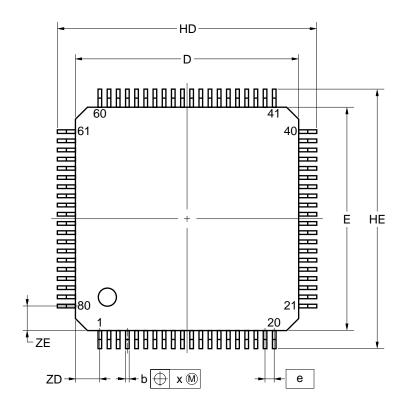

# PIN CONFIGURATION (TOP VIEW)

• 80-pin plastic TQFP (Fine pitch) (12 × 12)

μPD720113GK-9EU

**★** μPD720113GK-9EU-A

| Pin No. | Pin Name          |

|---------|-------------------|---------|-------------------|---------|-------------------|---------|-------------------|

| 1       | V <sub>DD33</sub> | 21      | V <sub>DD33</sub> | 41      | Vss               | 61      | DM1               |

| 2       | V <sub>DD25</sub> | 22      | CSB7              | 42      | X1_CLK            | 62      | DP1               |

| 3       | Vss               | 23      | PPB7              | 43      | X2                | 63      | V <sub>DD25</sub> |

| 4       | DM6               | 24      | CSB6              | 44      | V <sub>DD25</sub> | 64      | Vss               |

| 5       | DP6               | 25      | PPB6              | 45      | AVss              | 65      | DM2               |

| 6       | V <sub>DD33</sub> | 26      | CSB5              | 46      | RREF              | 66      | DP2               |

| 7       | Vss               | 27      | PPB5              | 47      | AVss(R)           | 67      | V <sub>DD33</sub> |

| 8       | DM7               | 28      | CSB4              | 48      | AV <sub>DD</sub>  | 68      | Vss               |

| 9       | DP7               | 29      | Vss               | 49      | AVss              | 69      | DM3               |

| 10      | Vss               | 30      | V <sub>DD25</sub> | 50      | AVDD              | 70      | DP3               |

| 11      | V <sub>DD25</sub> | 31      | PPB4              | 51      | Vss               | 71      | V <sub>DD33</sub> |

| 12      | Vss               | 32      | CSB3              | 52      | V <sub>DD25</sub> | 72      | Vss               |

| 13      | TEST              | 33      | PPB3              | 53      | V <sub>DD33</sub> | 73      | V <sub>DD25</sub> |

| 14      | SCAN_MODE         | 34      | CSB2              | 54      | Vss               | 74      | Vss               |

| 15      | Vss               | 35      | PPB2              | 55      | DMU               | 75      | DM4               |

| 16      | LPWRM             | 36      | CSB1              | 56      | DPU               | 76      | DP4               |

| 17      | EXROM_EN          | 37      | PPB1              | 57      | V <sub>DD25</sub> | 77      | V <sub>DD25</sub> |

| 18      | SCL               | 38      | SYSRSTB           | 58      | Vss               | 78      | Vss               |

| 19      | SDA/GANG_B        | 39      | VBUSM             | 59      | RPU               | 79      | DM5               |

| 20      | Vss               | 40      | V <sub>DD33</sub> | 60      | V <sub>DD33</sub> | 80      | DP5               |

**Remark** AVss(R) should be used to connect RREF through 1 % precision reference resistor of 2.43 k $\Omega$ .

# 1. PIN INFORMATION

| Pin Name          | I/O   | Buffer Type                  | Active<br>Level | Function                                                    |

|-------------------|-------|------------------------------|-----------------|-------------------------------------------------------------|

| X1_CLK            | I     | 2.5 V Input                  |                 | Crystal oscillator in or clock input                        |

| X2                | 0     | 2.5 V Output                 |                 | Oscillator out                                              |

| SYSRSTB           | I     | 5 V tolerant Schmitt Input   | Low             | Asynchronous chip reset                                     |

| RPU               | A (O) | USB Pull-up control          |                 | External 1.5 kΩ pull-up resistor control                    |

| DP(7:1)           | I/O   | USB D+ signal I/O            |                 | USB's downstream facing port D+ signal                      |

| DM(7:1)           | I/O   | USB D- signal I/O            |                 | USB's downstream facing port D– signal                      |

| DPU               | I/O   | USB D+ signal I/O            |                 | USB's upstream facing port D+ signal                        |

| DMU               | I/O   | USB D- signal I/O            |                 | USB's upstream facing port D- signal                        |

| LPWRM             | I     | 3.3 V Schmitt Input          |                 | Local power monitor                                         |

| RREF              | A (O) | Analog                       |                 | Reference resistor                                          |

| CSB(7:1)          | I     | 5 V tolerant Input           | Low             | Port's over-current status input                            |

| PPB(7:1)          | 0     | 5 V tolerant N-ch open drain | Low             | Port's power supply control output                          |

| VBUSM             | I     | 5 V tolerant Schmitt input   |                 | V <sub>BUS</sub> monitor                                    |

| SCL               | 0     | 3.3 V Output                 |                 | External serial ROM clock out                               |

| SDA/GANG_B        | I/O   | 3.3 V Schmitt I/O            |                 | External serial ROM data IO or power management mode select |

| EXROM_EN          | I     | 3.3 V Schmitt Input          |                 | External serial ROM input enable                            |

| TEST              | I     | 3.3 V Input                  |                 | Test signal                                                 |

| SCAN_MODE         | I     | 3.3 V Input                  |                 | Test signal                                                 |

| V <sub>DD33</sub> |       |                              |                 | 3.3 V V <sub>DD</sub>                                       |

| V <sub>DD25</sub> |       |                              |                 | 2.5 V V <sub>DD</sub>                                       |

| AV <sub>DD</sub>  |       |                              |                 | 2.5 V V <sub>DD</sub> for analog circuit                    |

| Vss               |       |                              |                 | Vss                                                         |

| AVss              |       |                              |                 | Vss for analog circuit                                      |

| AVss(R)           |       |                              |                 | Vss for reference resistor. Connect to AVss.                |

Remark "5 V tolerant" means that the buffer is 3 V buffer with 5 V tolerant circuit.

# 2. ELECTRICAL SPECIFICATIONS

# 2.1 Buffer List

2.5 V Oscillator interface

X1\_CLK, X2

• 5 V Schmitt input buffer

SYSRSTB, CSB(7:1), VBUSM

• 3.3 V Schmitt input buffer

**LPWRM**

• 3.3 V input buffer

EXROM\_EN, TEST, SCAN\_MODE

• 3.3 V IoL = 3 mA bi-directional Schmitt input buffer with input enable (OR-type)

SDA/GANG\_B

• 3.3 V IoL = 3 mA output buffer

SCL

• 5 V IoL = 12 mA N-ch open drain buffer

PPB(7:1)

USB2.0 interface

RPU, DPU, DMU, DP(7:1), DM(7:1), RREF

Above, "5 V" refers to a 3 V input buffer that is 5 V tolerant (has 5 V maximum input voltage). Therefore, it is possible to have a 5 V connection for an external bus.

# 2.2 Terminology

**Terms Used in Absolute Maximum Ratings**

| Parameter             | Symbol                 | Meaning                                                                                                                                                   |

|-----------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply voltage  | VDD33<br>VDD25<br>AVDD | Indicates voltage range within which damage or reduced reliability will not result when power is applied to a $V_{\text{DD}}$ pin.                        |

| Input voltage         | Vı                     | Indicates voltage range within which damage or reduced reliability will not result when power is applied to an input pin.                                 |

| Output voltage        | Vo                     | Indicates voltage range within which damage or reduced reliability will not result when power is applied to an output pin.                                |

| Output current        | lo                     | Indicates absolute tolerance values for DC current to prevent damage or reduced reliability when current flows out of or into an output pin.              |

| Operating temperature | TA                     | Indicates the ambient temperature range for normal logic operations.                                                                                      |

| Storage temperature   | Tstg                   | Indicates the element temperature range within which damage or reduced reliability will not result while no voltage or current are applied to the device. |

**Terms Used in Recommended Operating Range**

| Parameter                | Symbol                                               | Meaning                                                                                                                                        |

|--------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply voltage     | V <sub>DD33</sub> V <sub>DD25</sub> AV <sub>DD</sub> | Indicates the voltage range for normal logic operations to occur when $V_{\rm SS}$ = 0 $V_{\rm c}$                                             |

| High-level input voltage | VIH                                                  | Indicates the voltage, applied to the input pins of the device, which indicates the high level state for normal operation of the input buffer. |

|                          |                                                      | * If a voltage that is equal to or greater than the "MIN." value is applied, the<br>input voltage is guaranteed as high level voltage.         |

| Low-level input voltage  | VIL                                                  | Indicates the voltage, applied to the input pins of the device, which indicates the low level state for normal operation of the input buffer.  |

|                          |                                                      | * If a voltage that is equal to or less than the "MAX." value is applied, the<br>input voltage is guaranteed as low level voltage.             |

| Hysteresis voltage       | Vн                                                   | Indicates the differential between the positive trigger voltage and the negative trigger voltage.                                              |

| Input rise time          | tri                                                  | Indicates allowable input signal transition time from $0.1 \times V_{DD}$ to $0.9 \times V_{DD}$ .                                             |

| Input fall time          | tfi                                                  | Indicates allowable input signal transition time from $0.9 \times V_{DD}$ to $0.1 \times V_{DD}$ .                                             |

# **Terms Used in DC Characteristics**

| Parameter                        | Symbol | Meaning                                                                                                                                                                                                      |

|----------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Off-state output leakage current | loz    | Indicates the current that flows into a 3-state output pin when it is in a high-impedance state and a voltage is applied to the pin.                                                                         |

| Output short circuit current     | los    | Indicates the current that flows from an output pin when it is shorted to GND while it is at high-level.                                                                                                     |

| Input leakage current            | lı     | Indicates the current that flows into an input pin when a voltage is applied to the pin.                                                                                                                     |

| Low-level output current         | Ю      | Indicates the current that can flow into an output pin in the low-level state without raising the output voltage above the specified Vol.                                                                    |

| High-level output current        | Іон    | Indicates the current that can flow out of an output pin in the high-level state without reducing the output voltage below the specified Voh. (A negative current indicates current flowing out of the pin.) |

# 2.3 Electrical Specifications

# **Absolute Maximum Ratings**

| Parameter                  | Symbol            | Condition                                                                                                                  | Rating         | Unit           |

|----------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------|----------------|----------------|

| Power supply voltage       | V <sub>DD33</sub> |                                                                                                                            | -0.5 to +4.6   | V              |

|                            | V <sub>DD25</sub> |                                                                                                                            | -0.5 to +3.6   | V              |

|                            | AV <sub>DD</sub>  |                                                                                                                            | -0.5 to +3.6   | V              |

| Input/output voltage       | Vı/Vo             |                                                                                                                            |                |                |

| 2.5 V input/output voltage |                   | $2.3 \text{ V} \le \text{V}_{\text{DD25}} \le 2.7 \text{ V}$<br>V <sub>1</sub> /V <sub>0</sub> < V <sub>DD25</sub> + 0.9 V | -0.5 to +3.6   | V              |

| 3.3 V input/output voltage |                   | 3.0 V ≤ V <sub>DD33</sub> ≤ 3.6 V<br>V <sub>1</sub> /V <sub>0</sub> < V <sub>DD33</sub> + 1.0 V                            | -0.5 to +4.6   | V              |

| 5 V input/out voltage      |                   | $3.0 \text{ V} \le \text{V}_{\text{DD33}} \le 3.6 \text{ V}$<br>V <sub>I</sub> /V <sub>O</sub> < V <sub>DD33</sub> + 3.0 V | -0.5 to +6.6   | V              |

| Output current             | lo                | IoL = 3 mA<br>IoL = 6 mA<br>IoL = 12 mA                                                                                    | 10<br>20<br>40 | mA<br>mA<br>mA |

| Operating temperature      | TA                |                                                                                                                            | 0 to +70       | °C             |

| Storage temperature        | Tstg              |                                                                                                                            | -65 to +150    | °C             |

Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameters. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

The ratings and conditions indicated for DC characteristics and AC characteristics represent the quality assurance range during normal operation.

**Recommended Operating Ranges**

| Parameter                      | Symbol            | Condition                        | MIN. | TYP. | MAX.              | Unit |

|--------------------------------|-------------------|----------------------------------|------|------|-------------------|------|

| Operating voltage              | V <sub>DD33</sub> | 3.3 V for V <sub>DD33</sub> pins | 3.14 | 3.30 | 3.46              | V    |

|                                | V <sub>DD25</sub> | 2.5 V for V <sub>DD25</sub> pins | 2.3  | 2.5  | 2.7               | V    |

|                                | AV <sub>DD</sub>  | 2.5 V for AV <sub>DD</sub> pins  | 2.3  | 2.5  | 2.7               | V    |

| High-level input voltage       | VIH               |                                  |      |      |                   |      |

| 2.5 V High-level input voltage |                   |                                  | 1.7  |      | V <sub>DD25</sub> | V    |

| 3.3 V High-level input voltage |                   |                                  | 2.0  |      | V <sub>DD33</sub> | V    |

| 5.0 V High-level input voltage |                   |                                  | 2.0  |      | 5.5               | V    |

| Low-level input voltage        | VIL               |                                  |      |      |                   |      |

| 2.5 V Low-level input voltage  |                   |                                  | 0    |      | 0.7               | V    |

| 3.3 V Low-level input voltage  |                   |                                  | 0    |      | 0.8               | V    |

| 5.0 V Low-level input voltage  |                   |                                  | 0    |      | 0.8               | V    |

| Hysteresis voltage             | Vн                |                                  |      |      |                   |      |

| 5 V Hysteresis voltage         |                   |                                  | 0.3  |      | 1.5               | V    |

| 3.3 V Hysteresis voltage       |                   |                                  | 0.2  |      | 1.0               | V    |

| Input rise time for SYSRSTB    | trst              |                                  |      |      | 10                | ms   |

| Input rise time                | tri               |                                  |      |      |                   |      |

| Normal buffer                  |                   |                                  | 0    |      | 200               | ns   |

| Schmitt buffer                 |                   |                                  | 0    |      | 10                | ms   |

| Input fall time                | <b>t</b> fi       |                                  |      |      |                   |      |

| Normal buffer                  |                   |                                  | 0    |      | 200               | ns   |

| Schmitt buffer                 |                   |                                  | 0    |      | 10                | ms   |

# Two power supply rails limitation.

The  $\mu$ PD720113 has two power supply rails (2.5 V, 3.3 V). The system will require the time when power supply rail is stable at V<sub>DD</sub> level. And, there will be difference between the time of V<sub>DD25</sub> and V<sub>DD33</sub>. The  $\mu$ PD720113 requires that V<sub>DD25</sub> should be stable before V<sub>DD33</sub> becomes stable. At any case, the system must ensure that the absolute maximum ratings for V<sub>1</sub>/V<sub>0</sub> are not exceeded. System reset signaling should be asserted more than specified time after both V<sub>DD25</sub> and V<sub>DD33</sub> are stable.

# **DC Characteristics**

| Parameter                        | Symbol   | Condition                                         | MIN. | MAX. | Unit |

|----------------------------------|----------|---------------------------------------------------|------|------|------|

| Off-state output leakage current | loz      | Vo = V <sub>DD33</sub> , V <sub>DD25</sub> or Vss |      | ±10  | μΑ   |

| Output short circuit current     | los Note |                                                   |      | -250 | mA   |

| Low-level output current         | loL      |                                                   |      |      |      |

| 3.3 V low-level output current   |          | V <sub>OL</sub> = 0.4 V                           | 3    |      | mA   |

| 3.3 V low-level output current   |          | V <sub>OL</sub> = 0.4 V                           | 6    |      | mA   |

| 5.0 V low-level output current   |          | V <sub>OL</sub> = 0.4 V                           | 12   |      | mA   |

| High-level output current        | Іон      |                                                   |      |      |      |

| 3.3 V high-level output current  |          | V <sub>OH</sub> = 2.4 V                           | -3   |      | mA   |

| 3.3 V high-level output current  |          | V <sub>OH</sub> = 2.4 V                           | -6   |      | mA   |

| 5.0 V high-level output current  |          | V <sub>OH</sub> = 2.4 V                           | -2   |      | mA   |

| Input leakage current            | lı       |                                                   |      |      |      |

| 3.3 V buffer                     |          | VI = VDD or VSS                                   |      | ±10  | μΑ   |

| 5.0 V buffer                     |          | $V_{I} = V_{DD}$ or $V_{SS}$                      |      | ±10  | μΑ   |

Note The output short circuit time is measured at one second or less and is tested with only one pin on the LSI.

# **USB Interface Block**

| Parameter                                                        | Symbol     | Conditions                        | MIN   | MAX   | Unit |

|------------------------------------------------------------------|------------|-----------------------------------|-------|-------|------|

| Output pin impedance                                             | ZHSDRV     | Includes Rs resistor              | 40.5  | 49.5  | Ω    |

| Bus pull-up resistor on upstream facing port                     | Reu        |                                   | 1.425 | 1.575 | kΩ   |

| Bus pull-up resistor on downstream facing port                   | RPD        |                                   | 14.25 | 15.75 | kΩ   |

| Termination voltage for upstream facing port pullup (full-speed) | VTERM      |                                   | 3.0   | 3.6   | V    |

| Input Levels for Low-/full-speed:                                |            |                                   |       |       |      |

| High-level input voltage (drive)                                 | ViH        |                                   | 2.0   |       | V    |

| High-level input voltage (floating)                              | VIHZ       |                                   | 2.7   | 3.6   | V    |

| Low-level input voltage                                          | VIL        |                                   |       | 0.8   | V    |

| Differential input sensitivity                                   | Vdl        | (D+) – (D–)                       | 0.2   |       | V    |

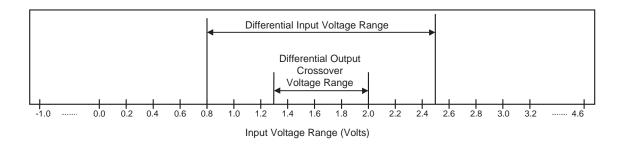

| Differential common mode range                                   | Vсм        | Includes V <sub>DI</sub> range    | 0.8   | 2.5   | V    |

| Output Levels for Low-/full-speed:                               |            |                                   |       |       |      |

| High-level output voltage                                        | Vон        | R <sub>L</sub> of 14.25 kΩ to GND | 2.8   | 3.6   | V    |

| Low-level output voltage                                         | Vol        | R∟ of 1.425 kΩ to 3.6 V           | 0.0   | 0.3   | V    |

| SE1                                                              | Vose1      |                                   | 0.8   |       | V    |

| Output signal crossover point voltage                            | Vcrs       |                                   | 1.3   | 2.0   | V    |

| Input Levels for High-speed:                                     |            |                                   |       |       |      |

| High-speed squelch detection threshold (differential signal)     | VHSSQ      |                                   | 100   | 150   | mV   |

| High-speed disconnect detection threshold (differential signal)  | VHSDSC     |                                   | 525   | 625   | mV   |

| High-speed data signaling common mode voltage range              | VHSCM      |                                   | -50   | +500  | mV   |

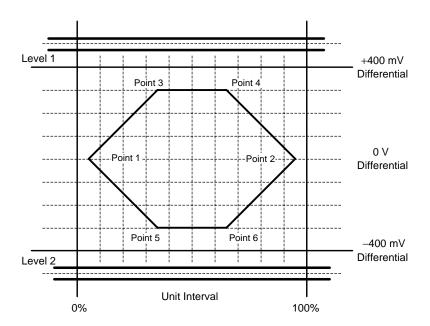

| High-speed differential input signaling levels                   | See Figure | e 2-4.                            |       |       |      |

| Output Levels for High-speed:                                    | •          |                                   |       |       |      |

| High-speed idle state                                            | VHSOI      |                                   | -10.0 | +10   | mV   |

| High-speed data signaling high                                   | Vнsон      |                                   | 360   | 440   | mV   |

| High-speed data signaling low                                    | VHSOL      |                                   | -10.0 | +10   | mV   |

| Chirp J level (different signal)                                 | Vchirpj    |                                   | 700   | 1100  | mV   |

| Chirp K level (different signal)                                 | Vchirpk    |                                   | -900  | -500  | mV   |

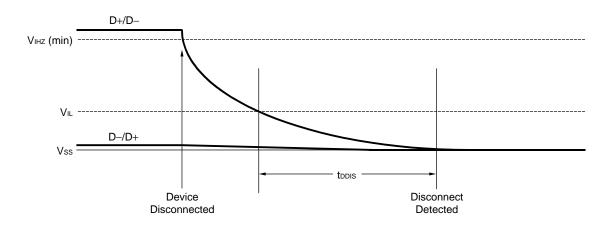

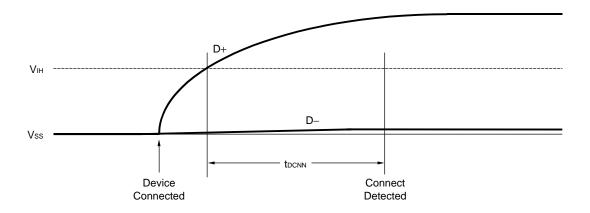

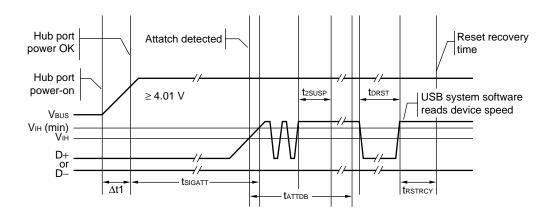

Figure 2-1. Differential Input Sensitivity Range for Low-/full-speed

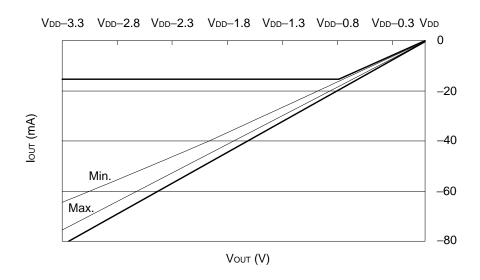

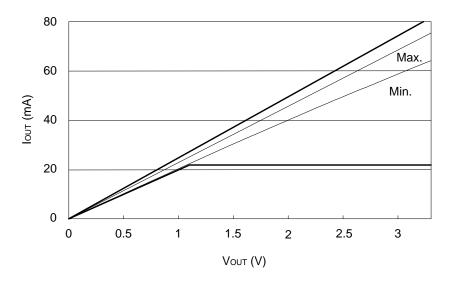

Figure 2-2. Full-speed Buffer VoH/loH Characteristics for High-speed Capable Transceiver

Figure 2-3. Full-speed Buffer VoL/IoL Characteristics for High-speed Capable Transceiver

Level 1 +400 mV Differential Point 3 Point 4 0 V Point 1 Point 2 Differential Point 5 Point 6 -400 mV Differential Level 2 0% Unit Interval 100%

Figure 2-4. Receiver Sensitivity for Transceiver at DP/DM

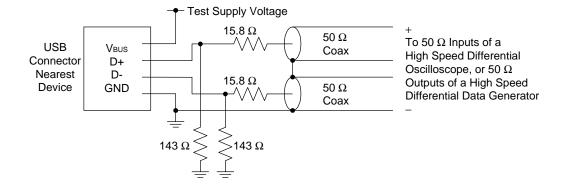

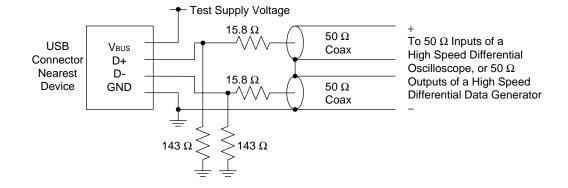

Figure 2-5. Receiver Measurement Fixtures

**Power Consumption**

| Parameter         | Symbol                                                                                                   | Condition                                                                                                  | TYP. | Unit       |

|-------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------|------------|

| Power Consumption | Pw-0                                                                                                     | The power consumption under the state without suspend.  All the ports do not connect to any function. Note |      |            |

|                   |                                                                                                          | Hub controller is operating at full-speed mode.                                                            | 44   | mA (2.5 V) |

|                   |                                                                                                          |                                                                                                            | 2.2  | mA (3.3 V) |

|                   |                                                                                                          | Hub controller is operating at high-speed mode.                                                            | 84   | mA (2.5 V) |

|                   |                                                                                                          |                                                                                                            | 23   | mA (3.3 V) |

|                   | Pw-5                                                                                                     | The power consumption under the state without suspend. The number of active ports is 5.                    |      |            |

|                   |                                                                                                          | Hub controller is operating at full-speed mode.                                                            | 44   | mA (2.5 V) |

|                   |                                                                                                          |                                                                                                            | 8.9  | mA (3.3 V) |

|                   |                                                                                                          | Hub controller is operating at high-speed mode.                                                            | 138  | mA (2.5 V) |

|                   |                                                                                                          |                                                                                                            | 85   | mA (3.3 V) |

|                   | P <sub>W-6</sub> The power consumption under the state without suspend. The number of active ports is 6. |                                                                                                            |      |            |

|                   |                                                                                                          | Hub controller is operating at full-speed mode.                                                            | 44   | mA (2.5 V) |

|                   |                                                                                                          |                                                                                                            | 10   | mA (3.3 V) |

|                   |                                                                                                          | Hub controller is operating at high-speed mode.                                                            | 148  | mA (2.5 V) |

|                   |                                                                                                          |                                                                                                            | 98   | mA (3.3 V) |

|                   | Pw-7                                                                                                     | The power consumption under the state without suspend. The number of active ports is 7.                    |      |            |

|                   |                                                                                                          | Hub controller is operating at full-speed mode.                                                            | 44   | mA (2.5 V) |

|                   |                                                                                                          |                                                                                                            | 12   | mA (3.3 V) |

|                   |                                                                                                          | Hub controller is operating at high-speed mode.                                                            | 158  | mA (2.5 V) |

|                   |                                                                                                          |                                                                                                            | 111  | mA (3.3 V) |

|                   | Pw_s                                                                                                     | The power consumption under suspend state.                                                                 | 0.68 | mA (2.5 V) |

|                   |                                                                                                          | The internal clock is stopped.                                                                             | 0.24 | mA (3.3 V) |

**Note** When any device is not connected to all the ports, the power consumption does not depend on the number of active ports.

**System Clock Ratings**

| Parameter        | Symbol        | Condition        | MIN.        | TYP. | MAX.        | Unit |

|------------------|---------------|------------------|-------------|------|-------------|------|

| Clock frequency  | fclk          | X'tal            | –500<br>ppm | 30   | +500<br>ppm | MHz  |

|                  |               | Oscillator block | –500<br>ppm | 30   | +500<br>ppm | MHz  |

| Clock Duty cycle | <b>t</b> DUTY |                  | 40          | 50   | 60          | %    |

- **Remarks 1.** Recommended accuracy of clock frequency is  $\pm$  100 ppm.

- **2.** Required accuracy of X'tal or oscillator block is including initial frequency accuracy, the spread of X'tal capacitor loading, supply voltage, temperature, and aging, etc.

# AC Characteristics (VDD = 3.14 to 3.46 V, TA = 0 to +70°C)

**System Reset Timing**

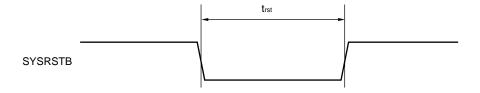

| Parameter                      | Symbol | Conditions | MIN. | MAX. | Unit |

|--------------------------------|--------|------------|------|------|------|

| Reset active time (Figure 2-6) | trst   |            | 5    |      | μs   |

Figure 2-6. System Reset Timing

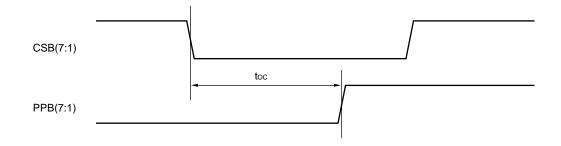

**Over-current Response Timing**

| Parameter                                                        | Symbol | Condition | MIN. | TYP. | MAX. | Unit |

|------------------------------------------------------------------|--------|-----------|------|------|------|------|

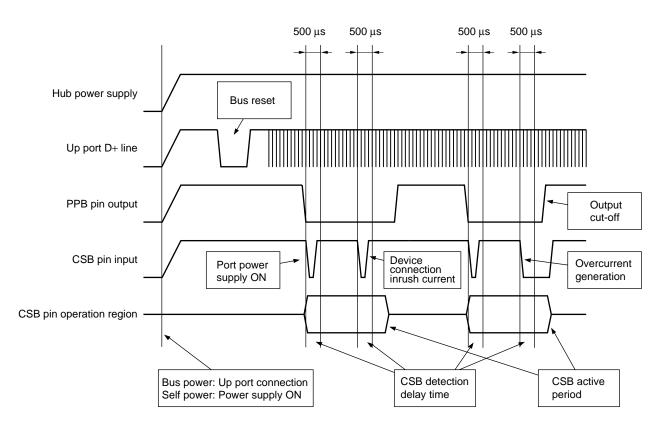

| Over-current response time from CSB low to PPB high (Figure 2-7) | toc    |           | 500  |      | 625  | μs   |

Figure 2-7. Over-current Response Timing

Figure 2-8. CSB/PPB Timing

**Remark** The active period of the CSB pin is in effect only when the PPB pin is ON. There is a delay time of approximately 500  $\mu$ s duration at the CSB pin.

**External Serial ROM Timing**

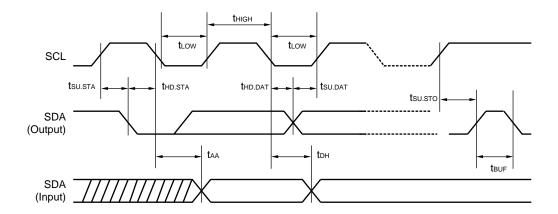

| Parameter                                                     | Symbol          | Condition | MIN. | TYP. | MAX. | Unit |

|---------------------------------------------------------------|-----------------|-----------|------|------|------|------|

| Clock frequency                                               | fscL            |           |      | 94.6 | 100  | kHz  |

| Clock pulse width low                                         | tLOW            |           | 4700 |      |      | ns   |

| Clock pulse width high                                        | <b>t</b> HIGH   |           | 4000 |      |      | ns   |

| Clock low to data out valid                                   | taa             |           | 100  |      | 3500 | ns   |

| Time the bus must be free before a new transmission can start | tbuf            |           | 4700 |      |      | ns   |

| Start hold time                                               | thd.sta         |           | 4000 |      |      | ns   |

| Start setup time                                              | tsu.sta         |           | 4700 |      |      | ns   |

| Data in hold time                                             | <b>t</b> hd.dta |           | 0    |      |      | ns   |

| Data in setup time                                            | tsu.dta         |           | 250  |      |      | ns   |

| Stop setup time                                               | tsu.sto         |           | 4700 |      |      | ns   |

| Data out hold time                                            | <b>t</b> DH     |           | 300  |      |      | ns   |

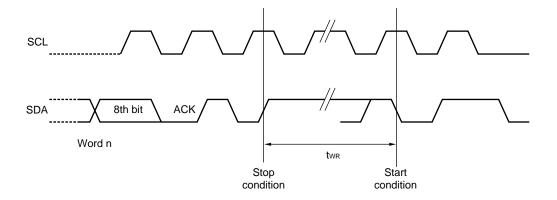

| Write cycle time                                              | twr             |           |      |      | 15   | ms   |

Figure 2-9. External Serial ROM Bus Timing

Figure 2-10. External Serial ROM Write Cycle Timing

# **USB Interface Block**

(1/4)

|                                                                                                                                                      |                  |                                             |              |              | (1/4)    |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------|--------------|--------------|----------|

| Parameter                                                                                                                                            | Symbol           | Conditions                                  | MIN.         | MAX.         | Unit     |

| Low-speed Electrical Characteristics                                                                                                                 |                  |                                             |              |              |          |

| Rise time (10% to 90%)                                                                                                                               | <b>t</b> LR      | C <sub>L</sub> = 200 pF to 600 pF           | 75           | 300          | ns       |

| Fall time (90% to 10%)                                                                                                                               | tlf              | C <sub>L</sub> = 200 pF to 600 pF           | 75           | 300          | ns       |

| Differential rise and fall time matching                                                                                                             | <b>t</b> LRFM    | (tlr/tlf) Note                              | 80           | 125          | %        |

| Low-speed data rate                                                                                                                                  | <b>t</b> ldraths | Average bit rate                            | 1.49925      | 1.50075      | Mbps     |

| Downstream facing port source jitter total (including frequency tolerance) (Figure 2-15):  To next transition                                        | •                |                                             | -25          | +25          |          |

| For paired transitions                                                                                                                               | tDDJ1            |                                             | -25<br>-14   | +25          | ns<br>ns |

| Downstream facing port differential receiver jitter total (including frequency tolerance) (Figure 2-17):  To next transition  For paired transitions | tujri<br>tujrz   |                                             | -152<br>-200 | +152<br>+200 | ns<br>ns |

| Source SE0 interval of EOP (Figure 2-16)                                                                                                             | <b>t</b> LEOPT   |                                             | 1.25         | 1.5          | μs       |

| Receiver SE0 interval of EOP (Figure 2-16)                                                                                                           | tLEOPR           |                                             | 670          | 1.0          | ns       |

| Width of SE0 interval during differential transition                                                                                                 | tlst             |                                             | 0.0          | 210          | ns       |

| Hub differential data delay (Figure 2-13)                                                                                                            | <b>t</b> LHDD    |                                             |              | 300          | ns       |

| Hub differential driver jitter (including cable) (Figure 2-13):                                                                                      |                  |                                             |              |              |          |

| Downstream facing port To next transition For paired transitions                                                                                     | t.онл1<br>t.онл2 |                                             | -45<br>-15   | +45<br>+15   | ns<br>ns |

| Upstream facing port To next transition For paired transitions                                                                                       | tгону1<br>tгону2 |                                             | -45<br>-45   | +45<br>+45   | ns<br>ns |

| Data bit width distortion after SOP (Figure 2-13)                                                                                                    | <b>t</b> LSOP    |                                             | -60          | +60          | ns       |

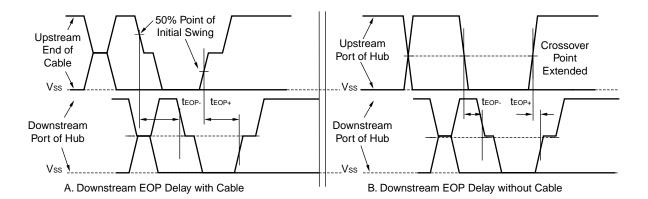

| Hub EOP delay relative to tho (Figure 2-14)                                                                                                          | <b>t</b> leopd   |                                             | 0            | 200          | ns       |

| Hub EOP output width skew (Figure 2-14)                                                                                                              | tlhesk           |                                             | -300         | +300         | ns       |

| Full-speed Electrical Characteristics                                                                                                                |                  |                                             |              |              |          |

| Rise time (10% to 90%)                                                                                                                               | <b>t</b> FR      | $C_L = 50 \text{ pF},$<br>$R_S = 36 \Omega$ | 4            | 20           | ns       |

| Fall time (90% to 10%)                                                                                                                               | tff              | C <sub>L</sub> = 50 pF,<br>Rs = 36 Ω        | 4            | 20           | ns       |

| Differential rise and fall time matching                                                                                                             | <b>t</b> frfm    | (tfr/tff)                                   | 90           | 111.11       | %        |

| Full-speed data rate                                                                                                                                 | <b>t</b> fdraths | Average bit rate                            | 11.9940      | 12.0060      | Mbps     |

| Frame interval                                                                                                                                       | <b>t</b> FRAME   |                                             | 0.9995       | 1.0005       | ms       |

**Note** Excluding the first transition from the Idle state.

(2/4)

|                                                                                        | 1                | I                   | ı                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | T                      | (2/4         |

|----------------------------------------------------------------------------------------|------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------|

| Parameter                                                                              | Symbol           | Conditions          | MIN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MAX.                   | Unit         |

| Full-speed Electrical Characteristics (Con                                             | tinued)          |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |              |

| Consecutive frame interval jitter                                                      | <b>t</b> RFI     | No clock adjustment |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 42                     | ns           |

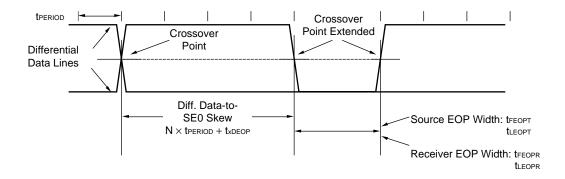

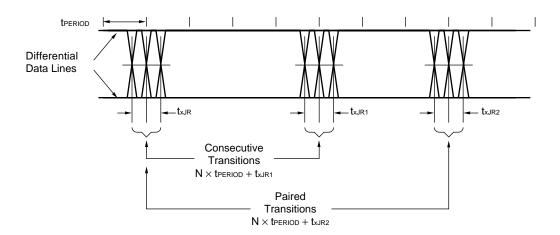

| Source jitter total (including frequency tolerance) (Figure 2-15):  To next transition | t <sub>DJ1</sub> | Note                | -3.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | +3.5                   | ns           |

| For paired transitions                                                                 | t <sub>DJ2</sub> |                     | -4.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | +4.0                   | ns           |

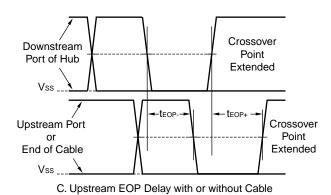

| Source jitter for differential transition to SE0 transition (Figure 2-16)              | <b>t</b> fdeop   |                     | -2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | +5                     | ns           |

| Receiver jitter (Figure 2-17): To Next Transition For Paired Transitions               | turi<br>turi     |                     | -18.5<br>-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | +18.5<br>+9            | ns<br>ns     |

| Source SE0 interval of EOP (Figure 2-16)                                               | <b>t</b> FEOPT   |                     | 160                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 175                    | ns           |

| Receiver SE0 interval of EOP (Figure 2-16)                                             | <b>t</b> FEOPR   |                     | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        | ns           |

| Width of SE0 interval during differential transition                                   | <b>t</b> FST     |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14                     | ns           |

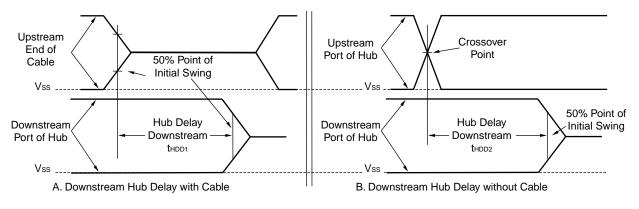

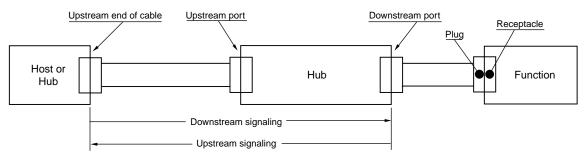

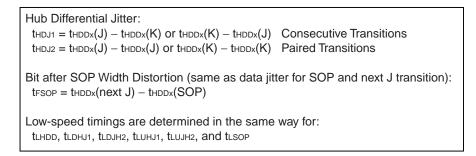

| Hub differential data delay (Figure 2-13)<br>(with cable)<br>(without cable)           | thdd1<br>thdd2   |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 70<br>44               | ns<br>ns     |