# MOS INTEGRATED CIRCUIT $\mu$ PD4702

# INCREMENTAL ENCODER 8-BIT UP/DOWN COUNTER CMOS INTEGRATED CIRCUITS

# DESCRIPTION

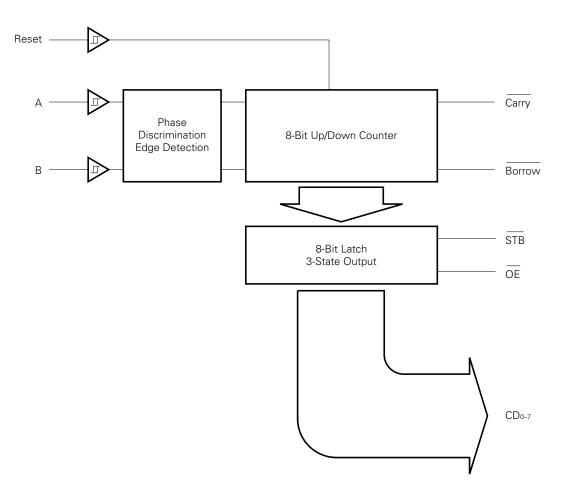

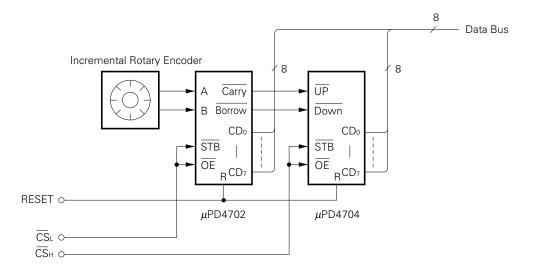

The  $\mu$ PD4702 is 8-bit up/down counters for an incremental encoder. Two-phase (A, B) incremental input signals are phase-differentiated, and on each signal edge, an up-count is executed if the A phase is leading, or a down-count if the B phase is leading. Eight-bit count data is output in real time. A carry output and borrow output are also provided for counter overflow and underflow.

The  $\mu$ PD4704 is also available; use of these enables the count width to be extended.

# **FEATURES**

- Incremental inputs (A, B)

- On-chip phase discrimination circuit (up-count mode when the phase order is A  $\rightarrow$  B, down-count mode when B  $\rightarrow$  A) 4-multiplication count method

- On-chip edge detection circuit

- 8-bit up/down counter latch output o Carry output, borrow output

- Count data output controllable (3-state output)

- CMOS, single +5 V power supply

# **ORDERING INFORMATION**

| Part Number | Package            |           |

|-------------|--------------------|-----------|

| μPD4702C    | 20-pin plastic DIP | (300 mil) |

| μPD4702G    | 20-pin plastic SOP | (300 mil) |

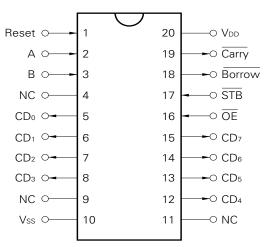

# **PIN CONFIGURATION (Top View)**

# **PIN NAMES**

| A<br>B | 2-phase incremental signal inputs |

|--------|-----------------------------------|

| Reset  | : Counter reset input             |

| STB    | : Latch strobe signal input       |

| OE     | : Output control signal input     |

| CD0-7  | : Count data outputs              |

| Carry  | : Carry pulse output              |

| Borrow | : Borrow pulse output             |

# **BLOCK DIAGRAM**

# **PIN FUNCTIONS**

| Pin Name | Input/Output        | Function                                                                                                           |

|----------|---------------------|--------------------------------------------------------------------------------------------------------------------|

| А, В     | Input<br>(Schmitt)  | Incremental signal A phase and B phase signal input pins (Schmitt input)                                           |

| D0 to 7  | Output<br>(3-state) | Count data output pins. Activated when $\overline{OE}$ is "L", high impedance outputs when $\overline{OE}$ is "H". |

| Carry    | Output              | 8-bit counter carry signal output pin (active-low)                                                                 |

| Borrow   | Output              | 8-bit counter borrow signal output pin (active-low)                                                                |

| RESET    | Input<br>(Schmitt)  | 8-bit counter reset signal output pin<br>Counter is reset when this pin is "H".                                    |

| ŌĒ       | Input               | Count data output control signal input pin                                                                         |

| STB      | Input               | Counter data output latch signal. Data is latched on the fall of $\overline{STB}$ , and is held while STB = "L".   |

| Vdd      |                     | Power supply input pin                                                                                             |

| GND      |                     | Ground pin                                                                                                         |

# 1. DESCRIPTION OF OPERATIONS

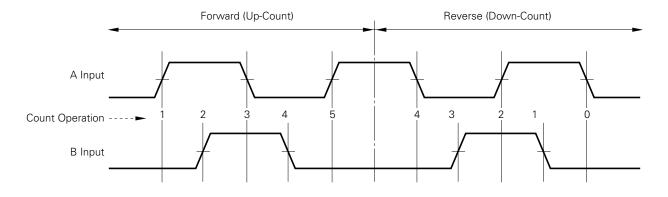

#### (1) Count operation

The  $\mu$ PD4702 incorporates a phase discrimination circuit, and counts by 4-multiplication of the A and B input 2-phase pulses. Therefore, a count operation is performed by an A input edge and a B input edge.

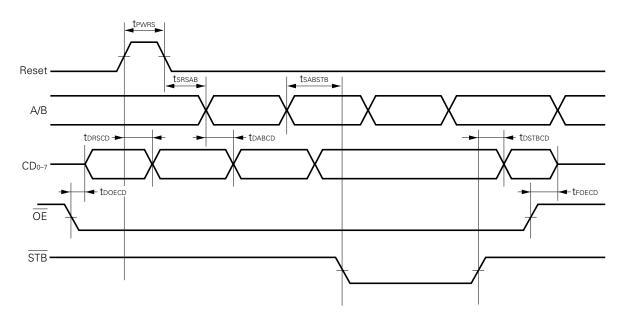

#### Fig. 1 Count Operation Timing Chart

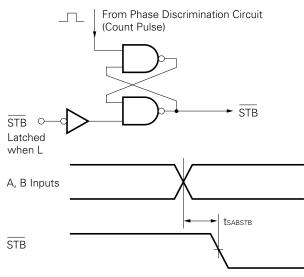

#### (2) Latch operation

An R-S flip-flop is inserted in the strobe input of the latch circuit as shown in Fig. 2, and when STB changes from "H" to "L" during a count operation, the internal latch signal  $\overline{STB}$  remains at "H" until the end of the count operation. Therefore, the count value is latched correctly even if  $\overline{STB}$  input is performed asynchronously from the A and B input (if  $\overline{STB}$  changes from "H" to "L" within tsABSTB (40 ns) after the A input or B input edge, the latch contents will be either the pre-count or post-count value). However, when a  $\mu$ PD4704 is added, the correct value cannot be latched if all digits are latched simultaneously when a carry or borrow is generated (the high-order digit may be latched before carry/borrow transmission).

#### Fig. 2 STB Input Circuit

If  $t_{\text{SABSTB}}$  is 40 ns or longer, the post-count value is input to the latch.

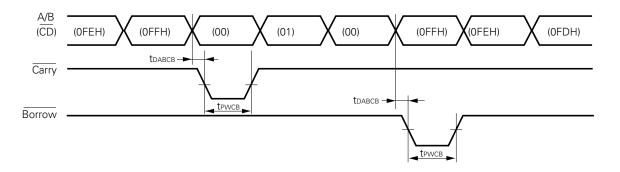

#### (3) Carry & borrow outputs

If the counter performs an up-count operation when the count value is  $0FF_H$ , an active-low pulse is output to the  $\overline{Carry}$  output (the pulse width is 25 ns MIN. 120 ns MAX. irrespective of the A/B phase input cycle. Similarly, if the counter performs a down-count operation when the count value is  $00_H$ , an active-low pulse is output to the Borrow output.

A Borrow pulse is also output if a down-count operation is performed while RESET is "H" (during a reset), and therefore, when a  $\mu$ PD4704 is added, a reset must be executed at the same time.

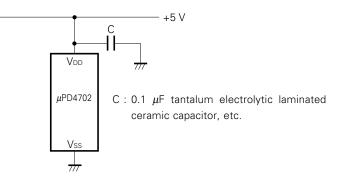

# 2. OPERATING PRECAUTIONS

As the  $\mu$ PD4702 incorporates an 8-bit counter, a large transient current flows in the case of a count value which changes all the bits (such as  $00H \leftrightarrow 0FFH$  or  $7FH \leftrightarrow 080H$ ). This will cause misoperation unless the impedance of the power supply line is sufficiently low. It is therefore recommended that a decoupling capacitor (of around 0.1  $\mu$ F) be connected between VDD and Vss right next to the IC as shown in Fig. 3.

#### Fig. 3 Decoupling Capacitor

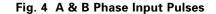

Also, if a pulse shorter than the phase difference time tsAB (70 ns) is input to the A/B phase inputs, this will result in a miscount. Therefore, if this kind of pulse is to be input because of encoder bounds, etc., a filter should be inserted in the A & B phase inputs.

If PW is at 70 ns or more, the count value remains the same before and after pulse input. (UP count  $\rightarrow$  DOWN count or DOWN count  $\rightarrow$  UP count is implemented, and therefore the the result is no change in the count value.)

# ABSOLUTE MAXIMUM RATINGS (TA = 25 °C, Vss = 0 V)

| PARAMETER             | SYMBOL | RATING                       |           | UNIT |

|-----------------------|--------|------------------------------|-----------|------|

| Supply voltage        | Vdd    | -0.5 to +7.0                 |           | V    |

| Input voltage         | Vı     | -1.0 to V <sub>DD</sub> +1.0 |           | V    |

| Output voltage        | Vo     | -0.5 to V <sub>DD</sub> +0.5 |           | V    |

| Operating temperature | Topt   | -40 to +85                   |           | °C   |

| Storage temperature   | Tstg   | -65 to +150                  |           | °C   |

| Permissible loss      | Po     | 500 (DIP)                    | 200 (SOP) | mW   |

# DC CHARACTERISTICS (TA = -40 to +85 °C, Vdd = +5 V $\pm 10$ %)

|                             | CVMDOL                 | SYMBOL TEST CONDITIONS                          | RAT                   |      |      |

|-----------------------------|------------------------|-------------------------------------------------|-----------------------|------|------|

| PARAMETER                   | SYMBOL TEST CONDITIONS |                                                 | MIN.                  | MAX. | UNIT |

| Input voltage high          | VIL                    |                                                 |                       | 0.8  | V    |

|                             | Vін                    | A, B, Reset                                     | 2.6                   |      | V    |

| Input voltage low           | Vih                    | Other than the above                            | 2.2                   |      | V    |

| Output voltage low          | Vol                    | loL = 12 mA                                     |                       | 0.45 | V    |

| Output voltage high         | Vон                    | Iон = -4 mA                                     | V <sub>DD</sub> - 0.8 |      | V    |

| Static consumption current  | ldd                    | VI = VDD, VSS                                   |                       | 50   | μΑ   |

| Input current               | h                      | VI = VDD, VSS                                   | -1.0                  | 1.0  | μΑ   |

| 3-state output leak current | IOFF                   |                                                 | -10                   | 10   | μΑ   |

| Dynamic consumption current | DD dyn                 | $f_{IN} = 3.6 \text{ MHz}, C_L = 50 \text{ pF}$ |                       | 12   | mA   |

| Hysteresis voltage          | Vн                     | A, B, Reset                                     | 0.2                   |      | V    |

# AC CHARACTERISTICS (TA = -40 to +85 °C, Vdd = +5 V $\pm 10$ %)

|                  | PARAMETER             | SYMBOL          | TEST CONDITIONS | MIN. | MAX. | UNIT |

|------------------|-----------------------|-----------------|-----------------|------|------|------|

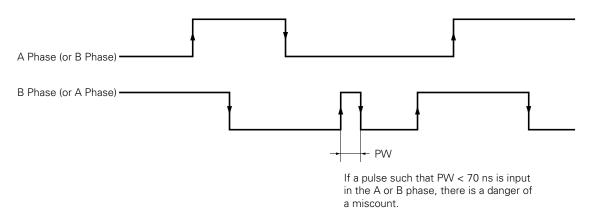

|                  | Cycle                 | tсуав           | fin = 3.6 MHz   | 280  |      | ns   |

|                  | High-level width      | tрwabh          |                 | 140  |      | ns   |

| А, В             | Low-level width       | <b>t</b> pwabl  |                 | 140  |      | ns   |

|                  | Phase difference time | tsab            |                 | 70   |      | ns   |

|                  | Setting time          | <b>t</b> srsab  |                 | 0    |      | ns   |

|                  | Reset time            | tdrscd          |                 |      | 60   | ns   |

|                  | Output delay          | <b>t</b> dabcd  |                 |      | 100  | ns   |

| <b>CD</b> 0 to 7 | Output delay          | <b>t</b> doecd  |                 |      | 50   | ns   |

|                  | Output delay          | <b>t</b> dstbcd |                 |      | 60   | ns   |

|                  | Float time            | <b>t</b> FOECD  |                 |      | 40   | ns   |

| Carry            | Output delay          | tdabcb          |                 |      | 120  | ns   |

| Borrow           | Output pulse width    | tрwcв           |                 | 25   | 120  | ns   |

| RESET            | Reset pulse width     | <b>t</b> PWRS   |                 | 40   |      | ns   |

| STB              | Setting time          | <b>t</b> sabstb |                 | 40   |      | ns   |

#### **AC Timings**

Fig. 3 Carry/Borrow Signal Output Timing

#### **Consumption Current Measurement Circuit**

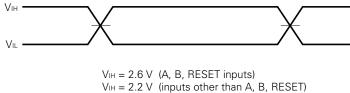

# **AC Test Input Waveform**

VIL = 0.8 V

Timing measurement is performed at 1.5 V.

#### **Sample Application Circuits**

#### 16-bit counter

The application circuits and their parameters are for references only and are not intended for use in actual design-in's.

# **RECOMMENDED SOLDERING CONDITIONS**

The following conditions (see table below) must be met when soldering this product.

Please consult with our sales offices in case other soldering process is used, or in case soldering is done under different conditions.

#### TYPES OF SURFACE MOUNT DEVICE

For more details, refer to our document "Semiconductor Device Mounting Technology Manual" (IEI-1207).

#### $\mu$ PD4702G

| Soldering process      | Soldering conditions                                                                                                                                               | Symbol    |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Infrared ray reflow    | Peak package's surface temperature: 235 °C or below,<br>Reflow time: 30 seconds or below (210 °C or higher),<br>Number of reflow process: 2, Exposure limit*: None | IR35-00-2 |

| VPS                    | Peak package's surface temperature: 215 °C or below,<br>Reflow time: 40 seconds or below (200 °C or higher),<br>Number of reflow process: 2, Exposure limit*: None | VP15-00-2 |

| Wave soldering         | Solder temperature: 260 °C or below,<br>Flow time: 10 seconds or below,<br>Number of flow process: 1, Exposure limit*: None                                        | WS60-00-1 |

| Partial heating method | Terminal temperature: 300 °C or below,<br>Flow time: 10 seconds or below,<br>Exposure limit*: None                                                                 |           |

Exposure limit before soldering after dry-pack package is opened.

Storage conditions: 25 °C and relative humidity at 65 % or less.

Note Do not apply more than a single process at once, except for "Partial heating method".

# TYPES OF THROUGH HOLE MOUNT DEVICE

#### μPD4702C

| Soldering process | Soldering conditions                                                   |  |

|-------------------|------------------------------------------------------------------------|--|

| Wave soldering    | Solder temperature: 260 °C or below,<br>Flow time: 10 seconds or below |  |

#### REFERENCE

| Dcodument name                                              | Document No. |

|-------------------------------------------------------------|--------------|

| NEC semiconductor device reliability/quality control system | IEI-1212     |

| Quality grade on NEC semiconductor devices                  | IEI-1209     |

| Semiconductor device mounting technology manual             | IEI-1207     |

| Semiconductor device package manual                         | IEI-1213     |

| Guide to quality assurance for semiconductor devices        | MEI-1202     |

| Semiconductor selection guide                               | MF-1134      |

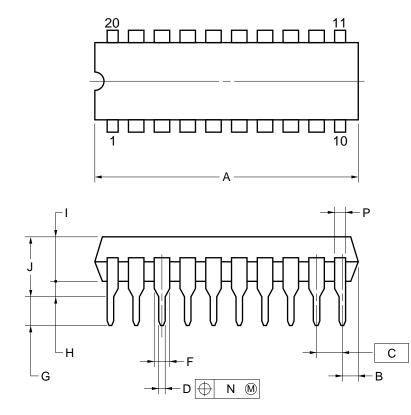

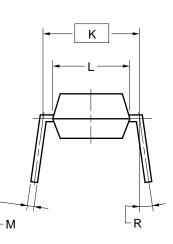

# 20PIN PLASTIC DIP (300 mil)

#### NOTES

- 1) Each lead centerline is located within 0.25 mm (0.01 inch) of its true position (T.P.) at maximum material condition.

- 2) Item "K" to center of leads when formed parallel.

| ITEM | MILLIMETERS            | INCHES                    |

|------|------------------------|---------------------------|

| А    | 25.40 MAX.             | 1.000 MAX.                |

| В    | 1.27 MAX.              | 0.050 MAX.                |

| С    | 2.54 (T.P.)            | 0.100 (T.P.)              |

| D    | 0.50±0.10              | $0.020^{+0.004}_{-0.005}$ |

| F    | 1.1 MIN.               | 0.043 MIN.                |

| G    | 3.5±0.3                | 0.138±0.012               |

| н    | 0.51 MIN.              | 0.020 MIN.                |

| I    | 4.31 MAX.              | 0.170 MAX.                |

| J    | 5.08 MAX.              | 0.200 MAX.                |

| К    | 7.62 (T.P.)            | 0.300 (T.P.)              |

| L    | 6.4                    | 0.252                     |

| М    | $0.25^{+0.10}_{-0.05}$ | $0.010^{+0.004}_{-0.003}$ |

| N    | 0.25                   | 0.01                      |

| Р    | 0.9 MIN.               | 0.035 MIN.                |

| R    | 0~15°                  | 0~15°                     |

|      | P2                     | 0C-100-3004 C-1           |

P20C-100-300A,C-1

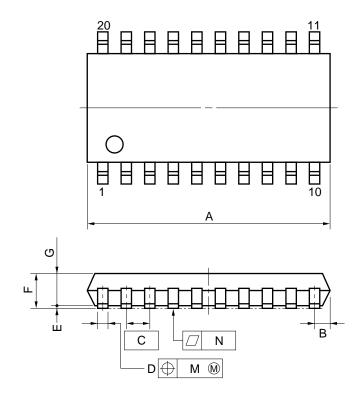

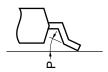

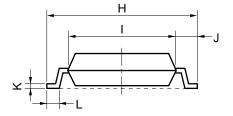

# 20 PIN PLASTIC SOP (300 mil)

detail of lead end

#### NOTE

Each lead centerline is located within 0.12 mm (0.005 inch) of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS            | INCHES                    |

|------|------------------------|---------------------------|

| А    | 13.00 MAX.             | 0.512 MAX.                |

| В    | 0.78 MAX.              | 0.031 MAX.                |

| С    | 1.27 (T.P.)            | 0.050 (T.P.)              |

| D    | $0.40^{+0.10}_{-0.05}$ | $0.016^{+0.004}_{-0.003}$ |

| E    | 0.1±0.1                | 0.004±0.004               |

| F    | 1.8 MAX.               | 0.071 MAX.                |

| G    | 1.55                   | 0.061                     |

| Н    | 7.7±0.3                | 0.303±0.012               |

| I    | 5.6                    | 0.220                     |

| J    | 1.1                    | 0.043                     |

| К    | $0.20^{+0.10}_{-0.05}$ | $0.008^{+0.004}_{-0.002}$ |

| L    | 0.6±0.2                | $0.024^{+0.008}_{-0.009}$ |

| М    | 0.12                   | 0.005                     |

| N    | 0.10                   | 0.004                     |

| Р    | 3°+7°<br>-3°           | 3° <sup>+7°</sup><br>-3°  |

|      | P20                    | GM-50-300B, C-4           |

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

M4 96.5