# YAMAHA L S I

**YMF754** DS-1E

Preliminary

# OVERVIEW

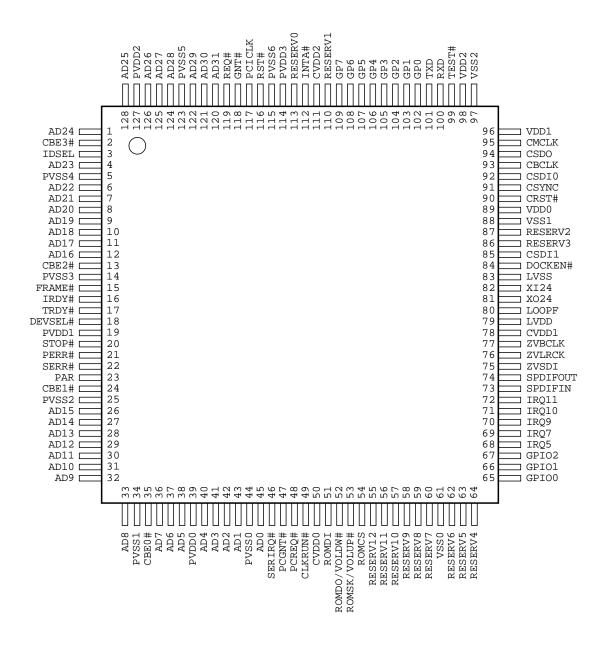

YMF754 (DS-1E) is a high performance audio controller for the PCI Bus. DS-1E consists of two separated functional blocks. One is the PCI Audio block and the other is the Legacy Audio block.

PCI Audio block provides 64-voice XG wavetable synthesizer with reverb and variation by using the software driver from YAMAHA. It also supports DirectSound hardware accelerator, Downloadable Sound (DLS) and DirectMusic accelerator.

Legacy Audio block supports FM synthesizer, Sound Blaster Pro, MPU401 UART mode and Joystick function in order to provide hardware compatibility for numerous PC games on real DOS without any software driver.

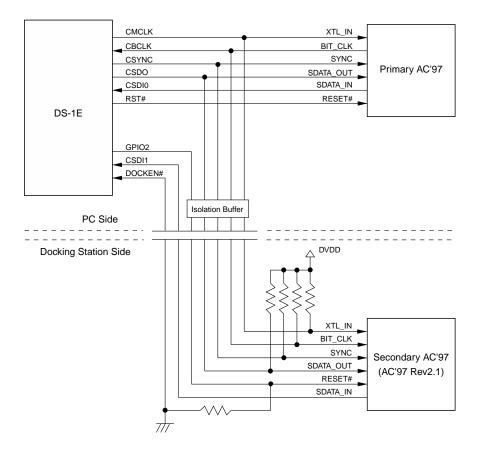

DS-1E supports the connection to AC'97 which provides high quality DAC, ADC and analog mixer, and it can connect two AC'97s. In addition, it supports consumer IEC958, Digital Audio Interface (SPDIF In/Out), to connect external audio equipment by digital.

In addition to support the same functions of YMF744B (DS-1S), DS-1E adds direct recording function for SPDIF In, and realizes to use SPDIF In and Zoomed Video Port at the same time. And, DS-1E is featured with the capability of dramatically reducing power consumption at normal operation.

## FEATURES

#### • PCI 2.2 Compliant

- PC98 / PC99 specification Compliant

- PCI Bus Power Management rev. 1.0 Compliant (Support D0, D2 and D3 state)

- · Supports clock run

- PCI Bus Master for PCI Audio

True Full Duplex Playback and Capture with different Sampling Rate

Maximum 64-voice XG capital Wavetable

- Synthesizer including GM compatibility

- DirectSound Hardware Acceleration

- DirectMusic Hardware Acceleration

- Downloadable Sound (DLS) level-1

- Legacy Audio compatibility

#### FM Synthesizer

Hardware Sound Blaster Pro compatibility MPU401 UART mode MIDI interface Joystick

• Supports PC/PCI and Distributed DMA for legacy DMAC (8237) emulation

- Supports Serialized IRQ

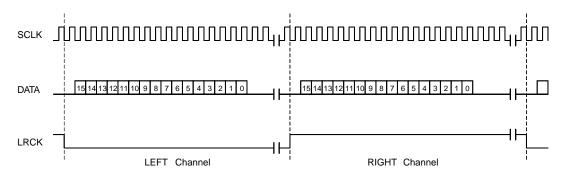

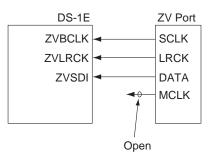

- Supports I<sup>2</sup>S serial input for Zoomed Video Port

- Supports Consumer IEC958 Port (SPDIF In/Out)

- Supports direct recording function for SPDIF In

- Capability for using SPDIF In and Zoomed Video Port at the same time.

- Supports AC'97 Interface (AC-Link) Revision 2.1

- AC'97 Digital Docking

- Supports 4-Channel Speaker

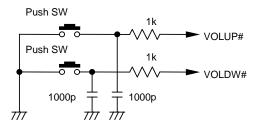

- Hardware Volume Control

- EEPROM Interface

- Single Crystal operation (24.576MHz)

- Power supply: 3.3V for I/O (5V tolerant), 2.5V for Internal core logic

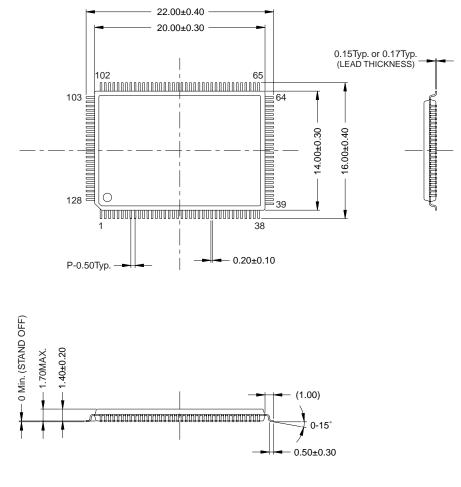

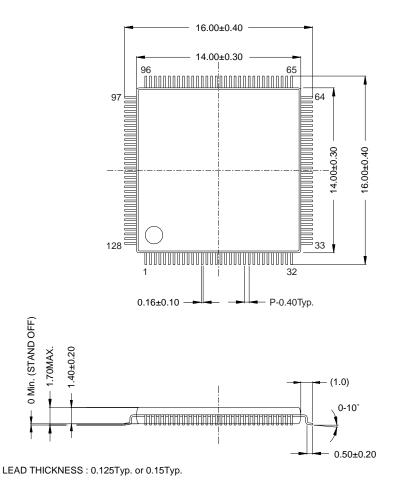

- 128-pin LQFP YMF754-V : 0.5mm pin pitch YMF754-R : 0.4mm pin pitch

The contents of this catalog are target specifications and are subject to change without prior notice. When using this device, please recheck the specifications.

# YAMAHA CORPORATION

YMF754 CATALOG CATALOG No.:LSI-4MF754A00 June 28, 1999

# YMF754

LOGOS

GENERAL MIDI logo is a trademark of Association of Musical Electronics Industry (AMEI), and indicates GM system level 1 Compliant.

XG logo is a trademark of YAMAHA Corporation.

SONDIUS-XG logo is a trademark that Stanford University in the United States and YAMAHA Corporation hold jointly.

Sensaura logo is a trademark of Central Research Laboratories Limited.

## 1. GM system level 1

GM system level 1 is a world standard format about MIDI synthesizer which provides voice arrangements and MIDI functions.

2. XG

XG is a format about MIDI synthesizer that is proposed by YAMAHA, and keeps the upper compatibility of GM system level 1. The good points are the voice arrangements kept extensively, a large number of the voices, modification of the voices, 3 kinds of effects, and so on.

3. SONDIUS-XG

Products bearing the SONDIUS-XG logo are licensed under patents of Stanford University and YAMAHA Corporation as listed on <http://www.sondius-xg.com>. The SONDIUS-XG produces acoustic sound outputs by running a virtual simulation of the actual acoustic instrument operation. Therefore, it provides much more real-world acoustic sound outputs fundamentally different from the Wavetable sound generator that simply processes the recorded acoustic sound sources only. The SONDIUS-XG adds the technology of virtual acoustic sound to the XG format.

4. Sensaura

Sensaura is a technology which provides 3D positional audio and moving effect by HRTF (Head Related Transfer Function) with 2 speakers or headphone. This feature makes it possible to enjoy invariable and unchangeable sound feelings in all-positional area covering as wide as 360 degrees.

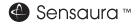

## PIN CONFIGURATION

YMF754-V (0.5mm pin pitch)

128 Pin LQFP Top View

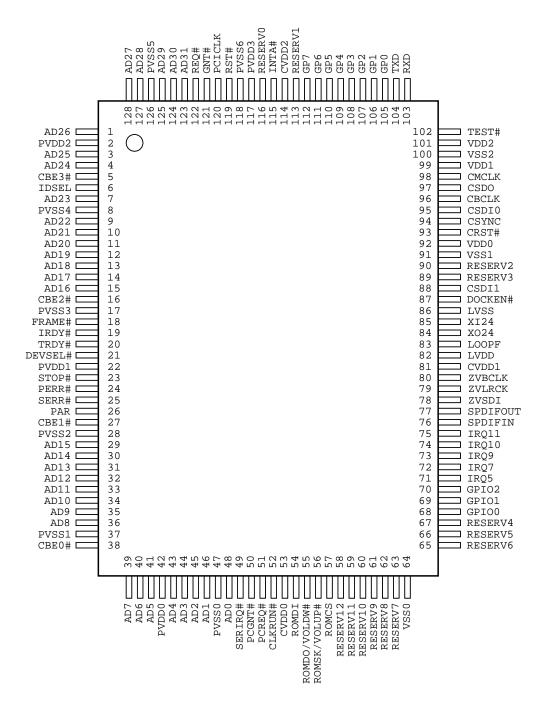

YMF754-R (0.4mm pin pitch)

**YMF754**

128 Pin LQFP Top View

# ■ PIN DESCRIPTION

# 1. PCI Bus Interface (54-pin)

| Name       | I/O | Туре | Size | Function                            |

|------------|-----|------|------|-------------------------------------|

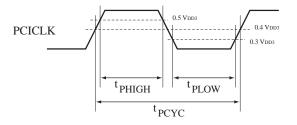

| PCICLK     | Ι   | Р    | -    | PCI Clock                           |

| RST#       | Ι   | Р    | -    | Reset                               |

| AD[31:0]   | Ю   | Ptr  | -    | Address / Data                      |

| C/BE[3:0]# | ΙΟ  | Ptr  | -    | Command / Byte Enable               |

| PAR        | ΙΟ  | Ptr  | -    | Parity                              |

| FRAME#     | ΙΟ  | Pstr | -    | Frame                               |

| IRDY#      | ΙΟ  | Pstr | -    | Initiator Ready                     |

| TRDY#      | ΙΟ  | Pstr | -    | Target Ready                        |

| STOP#      | ΙΟ  | Pstr | -    | Stop                                |

| IDSEL      | Ι   | Р    | -    | ID Select                           |

| DEVSEL#    | ΙΟ  | Pstr | -    | Device Select                       |

| REQ#       | 0   | Р    | -    | PCI Bus Master Request              |

| GNT#       | Ι   | Р    | -    | PCI Bus Master Grant                |

| PCREQ#     | 0   | Ptr  | -    | PC/PCI Request                      |

| PCGNT#     | Ι   | Ptr  | -    | PC/PCI Grant                        |

| PERR#      | Ю   | Pstr | -    | Parity Error                        |

| SERR#      | 0   | Pod  | -    | System Error                        |

| INTA#      | 0   | Pod  | -    | Interrupt signal output for PCI Bus |

| SERIRQ#    | ΙΟ  | Ptr  | -    | Serialized IRQ                      |

| CLKRUN#    | ΙΟ  | Ptr  | -    | Clock Run                           |

# 2. AC'97 Interface (8-pin)

| Name    | I/O | Туре | Size | Function                                           |  |  |  |  |  |

|---------|-----|------|------|----------------------------------------------------|--|--|--|--|--|

| CRST#   | 0   | Т    | 6mA  | Reset signal for AC'97                             |  |  |  |  |  |

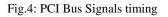

| CMCLK   | 0   | С    | -    | Master Clock for AC'97 (24.576MHz)                 |  |  |  |  |  |

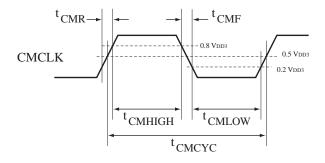

| CBCLK   | Ι   | Т    | -    | AC-link: Bit Clock for AC'97 audio data            |  |  |  |  |  |

| CSDO    | 0   | Т    | 6mA  | AC-link: AC'97 Serial audio output data            |  |  |  |  |  |

| CSYNC   | 0   | Т    | 6mA  | AC-link: AC'97 Synchronized signal                 |  |  |  |  |  |

| CSDI0   | Ι   | Т    | -    | AC-link: AC'97 Serial audio input data (Primary)   |  |  |  |  |  |

| CSDI1   | Ι   | Tup  | -    | AC-link: AC'97 Serial audio input data (Secondary) |  |  |  |  |  |

| DOCKEN# | Ι   | Tup  | -    | Secondary AC'97 Enable                             |  |  |  |  |  |

# 3. External Audio Interface (5-pin)

| Name     | I/O | Туре | Size | Function                       |  |  |  |  |  |

|----------|-----|------|------|--------------------------------|--|--|--|--|--|

| SPDIFOUT | 0   | Т    | 2mA  | Digital Audio Interface output |  |  |  |  |  |

| SPDIFIN  | Ι   | Tup  | -    | Digital Audio Interface input  |  |  |  |  |  |

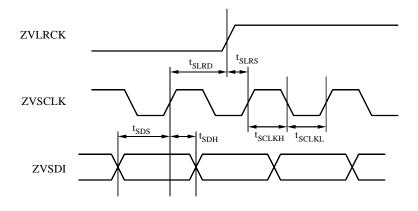

| ZVBCLK   | Ι   | Tup  | -    | Zoomed Video Port Bit Clock    |  |  |  |  |  |

| ZVLRCK   | Ι   | Tup  | -    | Zoomed Video Port L/R Clock    |  |  |  |  |  |

| ZVSDI    | Ι   | Tup  | -    | Zoomed Video Port Serial Data  |  |  |  |  |  |

# 4. Legacy Device Interface (15-pin)

| Name I/O Type Size |   |     |     | Function                                                                                               |  |  |  |  |  |

|--------------------|---|-----|-----|--------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| IRQ5               | 0 | Ttr | бmА | Interrupt 5 of Legacy Audio<br>It is directly connected to the interrupt signal of<br>System I/O chip. |  |  |  |  |  |

| IRQ7               | 0 | Ttr | 6mA | Interrupt 7 of Legacy Audio                                                                            |  |  |  |  |  |

| IRQ9               | 0 | Ttr | 6mA | Interrupt 9 of Legacy Audio                                                                            |  |  |  |  |  |

| IRQ10              | 0 | Ttr | 6mA | Interrupt 10 of Legacy Audio                                                                           |  |  |  |  |  |

| IRQ11              | 0 | Ttr | 6mA | Interrupt 11 of Legacy Audio.                                                                          |  |  |  |  |  |

| GP[3:0]            | Ι | А   | -   | Joystick Port                                                                                          |  |  |  |  |  |

| GP[7:4]            | Ι | Tup | -   | Joystick Port                                                                                          |  |  |  |  |  |

| RXD                | Ι | Tup | -   | MIDI Data Receive                                                                                      |  |  |  |  |  |

| TXD                | 0 | Т   | 2mA | MIDI Data Transfer                                                                                     |  |  |  |  |  |

# 5. Miscellaneous (11-pin)

| Name           | I/O Type S |     | Size | Function                                                                            |  |  |  |  |

|----------------|------------|-----|------|-------------------------------------------------------------------------------------|--|--|--|--|

| ROMCS          | 0          | Т   | 2mA  | Chip select for external EEPROM                                                     |  |  |  |  |

| ROMSK / VOLUP# | ΙΟ         | Tup | 2mA  | Serial clock for external EEPROM<br>or Hardware Volume (Up)                         |  |  |  |  |

| ROMDO / VOLDW# | Ю          | Tup | 2mA  | Serial data output for external EEPROM or Hardware Volume (Down)                    |  |  |  |  |

| ROMDI          | Ι          | Tup | -    | Serial data input for external EEPROM                                               |  |  |  |  |

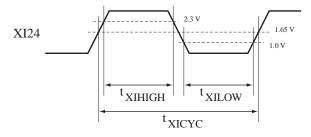

| XI24           | Ι          | С   | -    | 24.576 MHz Crystal                                                                  |  |  |  |  |

| XO24           | 0          | С   | -    | 24.576 MHz Crystal                                                                  |  |  |  |  |

| LOOPF          | Ι          | А   | -    | Capacitor for PLL                                                                   |  |  |  |  |

| GPIO[2:0]      | ΙΟ         | Tup | 6mA  | General purpose Input / Output<br>GPIO2 can use for a reset pin of Secondary AC'97. |  |  |  |  |

| TEST#          | Ι          | Tup | -    | LSI Test pin (Do not connect externally.)                                           |  |  |  |  |

# 6. Power Supply (22-pin)

| Name      | I/O | Туре | Size | Function                                |  |  |  |  |

|-----------|-----|------|------|-----------------------------------------|--|--|--|--|

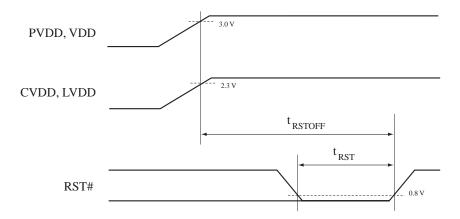

| PVDD[3:0] | -   | -    | -    | 3.3V Power supply for PCI Bus Interface |  |  |  |  |

| PVSS[6:0] | -   | -    | -    | Ground for PCI Bus Interface            |  |  |  |  |

| CVDD[2:0] | -   | -    | -    | 2.5V Power supply for Core logic        |  |  |  |  |

| VDD[2:0]  | -   | -    | -    | 3.3V Power supply                       |  |  |  |  |

| VSS[2:0]  | -   | -    | -    | Ground                                  |  |  |  |  |

| LVDD      | -   | -    | -    | 2.5V Power supply for PLL Filter        |  |  |  |  |

| LVSS      | -   | -    | -    | Ground for PLL Filter                   |  |  |  |  |

# 7. Reserve Pin (13-pin)

| Name         | I/O | Туре | Size | Function                                  |  |  |  |  |  |

|--------------|-----|------|------|-------------------------------------------|--|--|--|--|--|

| RESERV[12:0] | -   | -    | -    | Reserve pins (Do not connect externally.) |  |  |  |  |  |

## <u> TYPE</u>

| T : TTL                          | A : Analog | Ptr : Tri-State PCI           |

|----------------------------------|------------|-------------------------------|

| Ttr : Tri-State TTL              | C : CMOS   | Pstr : Sustained Tri-Sate PCI |

| Tup : Pull up (Max. 300kohm) TTL | P : PCI    | Pod : Open Drain PCI          |

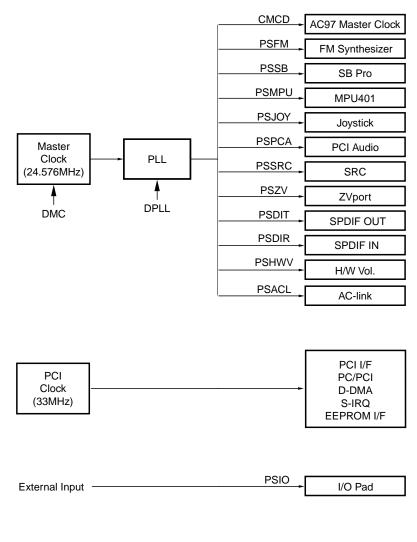

BLOCK DIAGRAM

## ■ FUNCTION OVERVIEW

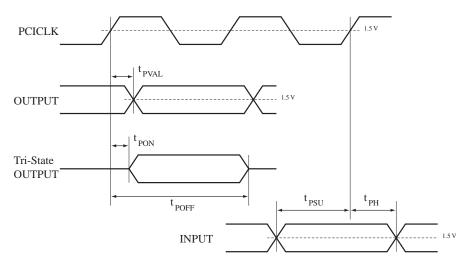

## 1. PCI INTERFACE

DS-1E supports the PCI bus interface and complies to PCI revision 2.2.

## 1-1. PCI Bus Command

DS-1E supports the following PCI Bus commands.

#### 1-1-1. Target Device Mode

| C/BE | [3:0]# |   |   | Command                                             |

|------|--------|---|---|-----------------------------------------------------|

| 0    | 0      | 0 | 0 | Interrupt Acknowledge (not support)                 |

| 0    | 0      | 0 | 1 | Special Cycle (not support)                         |

| 0    | 0      | 1 | 0 | I/O Read                                            |

| 0    | 0      | 1 | 1 | I/O Write                                           |

| 0    | 1      | 0 | 0 | reserved                                            |

| 0    | 1      | 0 | 1 | reserved                                            |

| 0    | 1      | 1 | 0 | Memory Read                                         |

| 0    | 1      | 1 | 1 | Memory Write                                        |

| 1    | 0      | 0 | 0 | reserved                                            |

| 1    | 0      | 0 | 1 | reserved                                            |

| 1    | 0      | 1 | 0 | Configuration Read                                  |

| 1    | 0      | 1 | 1 | Configuration Write                                 |

| 1    | 1      | 0 | 0 | Memory Read Multiple (alias to memory read)         |

| 1    | 1      | 0 | 1 | Dual Address Cycle (not support)                    |

| 1    | 1      | 1 | 0 | Memory Read Line (alias to memory read)             |

| 1    | 1      | 1 | 1 | Memory Write and Invalidate (alias to memory write) |

DS-1E does not assert DEVSEL# when accessed with commands that are indicated as (not supported) or reserved.

#### 1-1-2. Master Device Mode

| C/BE | [3:0]# |   |   | Command      |

|------|--------|---|---|--------------|

| 0    | 1      | 1 | 0 | Memory Read  |

| 0    | 1      | 1 | 1 | Memory Write |

When DS-1E becomes a Master Device, it generates only memory write and read cycle commands.

## 1-2. PCI Configuration Register

In addition to the Configuration Register defined by PCI Revision 2.2, DS-1E provides proprietary PCI Configuration Registers in order to control legacy audio function, such as FM Synthesizer, Sound Blaster Pro, MPU401 and Joystick. These additional registers are configured by BIOS or the configuration software from YAMAHA Corporation.

The following shows the overview of the PCI Configuration Register.

| P      |                   |                        |                                   |                |  |  |  |

|--------|-------------------|------------------------|-----------------------------------|----------------|--|--|--|

| Offset | b[3124]           | b[2316]                | b[158] b[70]                      |                |  |  |  |

| 00-03h | Devi              | ce ID                  | Vendor ID                         |                |  |  |  |

| 04-07h | Sta               | tus                    | Command                           |                |  |  |  |

| 08-0Bh | Base Class Code   | Sub Class Code         | Programming IF                    | Revision ID    |  |  |  |

| 0C-0Fh | Reserved          | Header Type            | Latency Timer                     | Reserved       |  |  |  |

| 10-13h |                   | PCI Audio Memo         | ry Base Address                   |                |  |  |  |

| 14-17h | Legacy Aud        | io I/O Base Address (I | Dummy for SB, FM, MI              | PU, D-DMA)     |  |  |  |

| 18-1Bh | Lega              | icy Audio I/O Base Ado | dress (Dummy for Joys             | stick)         |  |  |  |

| 1C-2Bh |                   | Rese                   | erved                             |                |  |  |  |

| 2C-2Fh | Subsys            | stem ID                | Subsystem                         | Vendor ID      |  |  |  |

| 30-33h |                   | Rese                   | erved                             |                |  |  |  |

| 34-37h |                   | Reserved               | Cap Pointer                       |                |  |  |  |

| 38-3Bh |                   | Rese                   | rved                              |                |  |  |  |

| 3C-3Fh | Maximum Latency   | Minimum Grant          | Interrupt Pin                     | Interrupt Line |  |  |  |

| 40-43h | Extended Legac    | cy Audio Control       | Legacy Audio Control              |                |  |  |  |

| 44-47h | Subsyster         | n ID Write             | Subsystem Vendor ID Write         |                |  |  |  |

| 48-4Bh | DS-1E Pow         | er Control 1           | DS-1E Control                     |                |  |  |  |

| 4C-4Fh | DS-1E Pow         | er Control 2           | D-DMA Slave Configuration         |                |  |  |  |

| 50-53h | Power Managen     | nent Capabilities      | Next Item Pointer                 | Capability ID  |  |  |  |

| 54-57h | Rese              | erved                  | Power Management Control / Status |                |  |  |  |

| 58-5Bh | DS-1E Secondary A | C'97 Power Control     | ACPI Mode                         |                |  |  |  |

| 5C-5Fh |                   | Rese                   | erved                             |                |  |  |  |

| 60-63h | Sound Blaster     | Base Address           | FM Synthesizer Base Address       |                |  |  |  |

| 64-67h | Joystick Ba       | se Address             | MPU401 Base Address               |                |  |  |  |

| 68-FFh |                   | Rese                   | erved                             |                |  |  |  |

**Reserved** registers are hardwired to "0". All data written to these registers are discarded. The values read from these registers are all zero.

DS-1E can be accessed by using any bus width, 8-bit, 16-bit or 32-bit.

## 00-01h: Vendor ID

| De  | ad Onl<br>fault: 1<br>cess B | 073h | dth: 8, | 16, 32· | -bit |    |    |    |    |    |    |    |    |    |    |

|-----|------------------------------|------|---------|---------|------|----|----|----|----|----|----|----|----|----|----|

| b15 | b14                          | b13  | b12     | b11     | b10  | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|     | Vendor ID                    |      |         |         |      |    |    |    |    |    |    |    |    |    |    |

## b[15:0] .....Vendor ID

This register contains the YAMAHA Vendor ID registered in Revision 2.2. This register is hardwired to **1073h**.

## 02-03h: Device ID

| De  | ad Onl<br>fault: 0<br>cess B | 012h | dth: 8, | 16, 32· | ·bit |    |      |       |    |    |    |    |    |    |    |

|-----|------------------------------|------|---------|---------|------|----|------|-------|----|----|----|----|----|----|----|

| b15 | b14                          | b13  | b12     | b11     | b10  | b9 | b8   | b7    | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|     |                              |      |         |         |      |    | Devi | ce ID |    |    |    |    |    |    |    |

## b[15:0] .....Device ID

This register contains the Device ID of DS-1E. This register is hardwired to 0012h.

## 04-05h: Command

Read / Write Default: 0000h Access Bus Width: 8, 16, 32-bit

| b15 | b14 | b13 | b12 | b11 | b10 | b9 | b8  | b7 | b6  | b5 | b4 | b3 | b2  | b1 | b0  |

|-----|-----|-----|-----|-----|-----|----|-----|----|-----|----|----|----|-----|----|-----|

| -   | -   | -   | -   | -   | -   | -  | SER | -  | PER | -  | -  | -  | BME | MS | IOS |

## b0.....IOS: I/O Space

This bit is a dummy one that is capable of writing. This bit indicates for BIOS or OS that DS-1E includes I/O devices.

## b1.....MS: Memory Space

This bit enables DS-1E to response to Memory Space Access.

"0": DS-1E ignores Memory Space Access. (default)

"1": DS-1E responds to Memory Space Access.

## b2.....BME: Bus Master Enable

This bit enables DS-1E to act as a master device on the PCI bus.

"0": Do not set DS-1E to be the master device. (default)

"1": Set DS-1E to be the master device.

#### b6.....PER: Parity Error Response

This bit enables DS-1E responses to Parity Error.

"0": DS-1E ignores all parity errors. (default)

"1": DS-1E performs error operation when DS-1E detects a parity error.

## b8.....SER: SERR# Enable

This bit enables DS-1E to drive SERR#.

"0": Do not drive SERR#. (default)

"1": Drives SERR# when DS-1E detects an Address Parity Error on normal target cycle or a Data Parity Error on special cycle.

#### 06-07h: Status

Read / Write Clear Default: 0210h Access Bus Width: 8, 16, 32-bit

|   | ACC | Cess B | <u>us vvic</u> | itn: 8, 1 | 16, 32- | DIt |    |     |    |    |    |     |    |    |    |    |

|---|-----|--------|----------------|-----------|---------|-----|----|-----|----|----|----|-----|----|----|----|----|

| ł | b15 | b14    | b13            | b12       | b11     | b10 | b9 | b8  | b7 | b6 | b5 | b4  | b3 | b2 | b1 | b0 |

| Γ | DPE | SSE    | RMA            | RTA       | STA     | DE  | VT | DPD | -  | -  | -  | CAP | -  | -  | -  | -  |

#### b4.....CAP: Capability (Read Only)

This bit indicates that DS-1E supports the capability register. This bit is read only. When 58-59h : ACPI Mode register, ACPI bit is "0", the bit is "1". When ACPI bit is "1", the bit is "0".

#### b8.....DPD: Data Parity Error Detected

This bit indicates that DS-1E detects a Data Parity Error during a PCI master cycle.

#### b[10:9] ......DEVT: DEVSEL Timing (Read Only)

This bit indicates that the decoding speed of DS-1E is Medium.

#### b11.....STA: Signaled Target Abort

This bit indicates that DS-1E terminates a transaction with Target Abort during a target cycle.

#### b12.....RTA: Received Target Abort

This bit indicates that a transaction is terminated with Target Abort while DS-1E is in the master memory cycle.

#### b13.....RMA: Received Master Abort

This bit indicates that a transaction is terminated with Master Abort while DS-1E is in the master memory cycle.

#### b14.....SSE: Signaled System Error

This bit indicates that DS-1E asserts SERR#.

#### b15.....DPE: Detected Parity Error

This bit indicates that DS-1E detects Address Parity Error or Data Parity Error during a transaction.

## 08h: Revision ID

| De | ad Onl<br>fault: 0<br>cess B | 0h | dth: 8, | 16, 32- | ·bit |    |    |

|----|------------------------------|----|---------|---------|------|----|----|

| b7 | b6                           | b5 | b4      | b3      | b2   | b1 | b0 |

|    |                              |    | Revis   | ion ID  |      |    |    |

## b[7:0] .....Revision ID

This register contains the revision number of DS-1E. This register is hardwired to **00h**.

## 09h: Programming Interface

|   | Def                   | ad Onl<br>fault: 0 | 0h            |         |         |      |    |    |  |

|---|-----------------------|--------------------|---------------|---------|---------|------|----|----|--|

|   | Acc                   | cess B             | <u>us Wic</u> | dth: 8, | 16, 32- | ·bit |    |    |  |

| b | 7                     | b6                 | b5            | b4      | b3      | b2   | b1 | b0 |  |

|   | Programming Interface |                    |               |         |         |      |    |    |  |

## b[7:0] .....Programming Interface

This register indicates the programming interface of DS-1E. This register is hardwired to **00h**.

## 0Ah: Sub-class Code

| De | ad Onl<br>fault: 0<br>cess B | ĺ1h | dth: 8, | 16, 32- | ·bit |  |  |  |  |  |  |  |  |

|----|------------------------------|-----|---------|---------|------|--|--|--|--|--|--|--|--|

| b7 |                              |     |         |         |      |  |  |  |  |  |  |  |  |

|    | Sub-class Code               |     |         |         |      |  |  |  |  |  |  |  |  |

## b[7:0] .....Sub-class Code

This register indicates the sub-class of DS-1E. This register is hardwired to **01h**. DS-1E belongs to the **Audio** Sub-class.

## 0Bh: Base Class Code

| De | ad Onl<br>fault: 0<br>cess B | 4h | dth: 8, <sup>-</sup> | 16, 32- | bit |  |  |  |  |  |  |  |  |

|----|------------------------------|----|----------------------|---------|-----|--|--|--|--|--|--|--|--|

| b7 |                              |    |                      |         |     |  |  |  |  |  |  |  |  |

|    | Base Class Code              |    |                      |         |     |  |  |  |  |  |  |  |  |

## b[7:0] .....Base Class Code

This register indicates the base class of DS-1E. This register is hardwired to **04h**. DS-1E belongs to the **Multimedia** Base Class.

## **0Dh: Latency Timer**

| De | ad / W<br>fault: 0<br>cess B | 0h | dth: 8, | 16. 32- | ·bit |    |    |

|----|------------------------------|----|---------|---------|------|----|----|

| b7 | b6                           | b5 | b4      | b3      | b2   | b1 | b0 |

|    |                              |    | Latenc  | y Timer |      |    |    |

## b[7:0] .....Latency Timer

When DS-1E becomes a Bus Master device, this register indicates the initial value of the Master Latency Timer.

## 0Eh: Header Type

| De | ad Onl<br>fault: 0 | 0h | 146. Q | 16 22         | hit. |    |    |

|----|--------------------|----|--------|---------------|------|----|----|

| b7 | b6                 | b5 | b4 b4  | 16, 32-<br>b3 | b2   | b1 | b0 |

|    |                    |    | Heade  | er Type       |      |    |    |

## b[7:0] .....Header Type

This register indicates the device type of DS-1E. This is hardwired to **00h**.

## 10-13h: PCI Audio Memory Base Address

| Read / Write                    |

|---------------------------------|

| Default: 00000000h              |

| Access Bus Width: 8, 16, 32-bit |

| / 101 | 766663 Du3 Width: 0, 10, 02 Dit |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|-------|---------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| b15   | b14                             | b13 | b12 | b11 | b10 | b9  | b8  | b7  | b6  | b5  | b4  | b3  | b2  | b1  | b0  |

| MBA   | -                               | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   |

| b31   | b30                             | b29 | b28 | b27 | b26 | b25 | b24 | b23 | b22 | b21 | b20 | b19 | b18 | b17 | b16 |

|       | MBA (higher)                    |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

## b[31:15] ......MBA: Memory Base Address

This register indicates the physical Memory Base address of the PCI Audio registers in DS-1E. The base address can be located anywhere in the 32-bit address space. Data in the DS-1E register is not prefetchable.

Size of the register to be mapped into the memory space is 32,768 bytes.

## 14-17h: Legacy Audio I/O Base Address (Dummy for SB, FM, MPU, D-DMA)

| De  | ad / W<br>fault: C<br>cess B | 00000 | -   | 16, 32- | bit  |     |     |     |     |     |     |     |     |     |     |

|-----|------------------------------|-------|-----|---------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| b15 | b14                          | b13   | b12 | b11     | b10  | b9  | b8  | b7  | b6  | b5  | b4  | b3  | b2  | b1  | b0  |

|     |                              |       |     | IOB     | ASE0 |     |     |     |     | -   | -   | -   | -   | -   | I/O |

| b31 | b30                          | b29   | b28 | b27     | b26  | b25 | b24 | b23 | b22 | b21 | b20 | b19 | b18 | b17 | b16 |

| -   | -                            | -     | -   | -       | -    | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   |

#### b0.....IO (Read Only)

This bit indicates that the base address is assigned to I/O. This bit is hardwired to "1".

#### b[15:6] .....IOBASE0

This register is used so that the OS may secure I/O resources for Sound Blaster Pro, FM Synthesizer, MPU401 and D-DMA controller. Because this register is a dummy one, each for the I/O addresses of the above blocks is assigned with the I/O addresses set to 4C-4Dh and 60-65h respectively by the software driver.

## 18-1Bh: Legacy Audio I/O Base Address (Dummy for Joystick)

| Read  | /Write |  |

|-------|--------|--|

| ILEau |        |  |

Default: 00000001h

Access Bus Width: 8, 16, 32-bit

| b15 | b14 | b13 | b12 | b11 | b10 | b9  | b8   | b7  | b6  | b5  | b4  | b3  | b2  | b1  | b0  |

|-----|-----|-----|-----|-----|-----|-----|------|-----|-----|-----|-----|-----|-----|-----|-----|

|     |     |     |     |     |     | IOB | ASE1 |     |     |     |     |     |     | -   | I/O |

| b31 | b30 | b29 | b28 | b27 | b26 | b25 | b24  | b23 | b22 | b21 | b20 | b19 | b18 | b17 | b16 |

| -   | -   | -   | -   | -   | -   | -   | -    | -   | -   | -   | -   | -   | -   | -   | -   |

#### b0.....IO (Read Only)

This bit indicates that the base address is assigned to I/O. This bit is hardwired to "1".

## b[15:2] .....IOBASE1

This register is used so that the OS may secure I/O resource for the joystick port. Because this register is a dummy one, the joystick I/O address is assigned with the I/O address set to 66-67h by the software driver.

## 2C-2Dh: Subsystem Vendor ID

| De  | ad Onl<br>fault: 1<br>cess B | 073h | dth: 8, | 16, 32- | ·bit |    |    |    |    |    |    |    |    |    |    |

|-----|------------------------------|------|---------|---------|------|----|----|----|----|----|----|----|----|----|----|

| b15 | b14                          | b13  | b12     | b11     | b10  | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|     | Subsystem Vendor ID          |      |         |         |      |    |    |    |    |    |    |    |    |    |    |

## b[15:0] ......Subsystem Vendor ID

This register contains the Subsystem Vendor ID. In general, this ID is used to distinguish adapters or systems made by different IHVs using the same chip by the same vendor. This register is read only. To write the IHV's Vendor ID, use 44-45h (Subsystem Vendor ID Write Register). IHVs must change this ID to their Vendor ID in the BIOS POST routine.

In case of the system such as Sound Card which BIOS can not control, this ID can be changed by connecting EEPROM externally. Then, Subsystem Vendor ID Write Register is invalid.

In case EEPROM is not externally, the default value is the YAMAHA's Vendor ID, 1073h.

## 2E-2Fh: Subsystem ID

| De  | ad Onl<br>fault: 0<br>cess B | 012h | dth: 8, | 16, 32 | -bit |    |    |    |    |    |    |    |    |    |    |

|-----|------------------------------|------|---------|--------|------|----|----|----|----|----|----|----|----|----|----|

| b15 | b14                          | b13  | b12     | b11    | b10  | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|     | Subsystem ID                 |      |         |        |      |    |    |    |    |    |    |    |    |    |    |

#### b[15:0] ......Subsystem ID

This register contains the Subsystem ID. In general, this ID is used to distinguish adapters or systems made by different IHVs using the same chip by the same vendor. This register is read only. To write the IHV's Device ID, use 46-47h (Subsystem ID Write Register). IHVs must change this ID to their ID in the BIOS POST routine.

In case of the system such as Sound Card which BIOS can not control, this ID can be changed by connecting EEPROM externally. Then, Subsystem ID Write Register is invalid.

In case EEPROM is not externally, the default value is the YAMAHA's Device ID, 0012h.

#### 34h: Capability Register Pointer

| De | ad Onl<br>fault: 5<br>cess B                                                                                              | 0h | th 8 | 16 32- | bit |  |  |  |  |  |

|----|---------------------------------------------------------------------------------------------------------------------------|----|------|--------|-----|--|--|--|--|--|

| b7 | Access Bus Width: 8, 16, 32-bit           b7         b6         b5         b4         b3         b2         b1         b0 |    |      |        |     |  |  |  |  |  |

|    | Capability Register Pointer                                                                                               |    |      |        |     |  |  |  |  |  |

#### b[7:0] .....Capability Register Pointer

This register indicates the offset address of the Capabilities register in the PCI Configuration register when 58-59h: ACPI Mode register, ACPI bit is "0". DS-1E provides PCI Bus Power Management registers as the capabilities. The Power Management registers are mapped to 50h - 55h in the PCI Configuration register, and this register indicates "50h".

When ACPI bit is "1", this register indicates "00h".

## 3Ch: Interrupt Line

|   | De                              | ad / W<br>fault: 0 | 00h | J46.0 | 40.00 | <b>L</b> :4 |  |  |  |  |  |

|---|---------------------------------|--------------------|-----|-------|-------|-------------|--|--|--|--|--|

| I | Access Bus Width: 8, 16, 32-bit |                    |     |       |       |             |  |  |  |  |  |

|   | b7 b6 b5 b4 b3 b2 b1 b0         |                    |     |       |       |             |  |  |  |  |  |

|   | Interrupt Line                  |                    |     |       |       |             |  |  |  |  |  |

## b[7:0] .....Interrupt Line

This register indicates the interrupt channel that INTA# is assigned to.

## 3Dh: Interrupt Pin

|     | Read Only<br>Default: 01h       |  |  |  |  |  |  |  |  |  |

|-----|---------------------------------|--|--|--|--|--|--|--|--|--|

| Ace | Access Bus Width: 8, 16, 32-bit |  |  |  |  |  |  |  |  |  |

| b7  | b7 b6 b5 b4 b3 b2 b1 b0         |  |  |  |  |  |  |  |  |  |

|     | Interrupt Pin                   |  |  |  |  |  |  |  |  |  |

## b[7:0] .....Interrupt Pin

DS-1E supports INTA# only. This register is hardwired to 01h.

## 3Eh: Minimum Grant

| De                              | ad Onl<br>fault: 0 | 5h |  | 40.00 | L:4 |  |  |  |  |

|---------------------------------|--------------------|----|--|-------|-----|--|--|--|--|

| Access Bus Width: 8, 16, 32-bit |                    |    |  |       |     |  |  |  |  |

| b7 b6 b5 b4 b3 b2 b1 b0         |                    |    |  |       |     |  |  |  |  |

| Minimum Grant                   |                    |    |  |       |     |  |  |  |  |

## b[7:0] .....Minimum Grant

This register indicates the length of the burst period required by DS-1E. This register is hardwired to **05h**.

## 3Fh: Maximum Latency

| De  | Read Only<br>Default: 19h       |  |  |  |  |  |  |  |  |  |

|-----|---------------------------------|--|--|--|--|--|--|--|--|--|

| Aco | Access Bus Width: 8, 16, 32-bit |  |  |  |  |  |  |  |  |  |

| b7  | b7 b6 b5 b4 b3 b2 b1 b0         |  |  |  |  |  |  |  |  |  |

|     | Maximum Latency                 |  |  |  |  |  |  |  |  |  |

## b[7:0] .....Maximum Latency

This register indicates how often DS-1E generates the Bus Master Request. This register is hardwired to **19h**.

## 40-41h: Legacy Audio Control

| Read / Write   |        |        |         |         |      |       |    |    |    |     |      |     |      |      |      |

|----------------|--------|--------|---------|---------|------|-------|----|----|----|-----|------|-----|------|------|------|

| Default: 907Fh |        |        |         |         |      |       |    |    |    |     |      |     |      |      |      |

| Ace            | cess B | us Wio | dth: 8, | 16, 32- | -bit |       |    |    |    |     |      |     |      |      |      |

| b15            | b14    | b13    | b12     | b11     | b10  | b9    | b8 | b7 | b6 | b5  | b4   | b3  | b2   | b1   | b0   |

| LAD            | SIEN   |        | MPUIRC  | λ       |      | SBIRQ |    | SD | MA | I/O | MIEN | MEN | JPEN | FMEN | SBEN |

#### b0.....SBEN: Sound Blaster Enable

This bit enables the mapping of the Sound Blaster Pro block in the I/O space specified by 62-63h: Sound Blaster Base Address register, when LAD is set to "0".

"0": Disable the mapping of the SB block to the I/O space

"1": Enable the mapping of the SB block to the I/O space (default)

#### b1.....FMEN: FM Synthesizer Enable

This bit enables the mapping of the FM Synthesizer block in the I/O space specified by 60-61h: FM Synthesizer Base Address register when LAD is set to "0". FM Synthesizer registers can be accessed via SB I/O space, while the SB block is enabled, even if FMEN is set to "0".

"0": Disable the mapping of the FM Synthesizer block to the FMIO space

"1": Enable the mapping of the FM Synthesizer block to the FMIO space (default)

After setting FMEN to "1", about 100 msec is necessary before accessing these I/O space.

#### b2.....JPEN: Joystick Port Enable

This bit enables the mapping of the Joystick block in the I/O space specified by 66-67h: Joystick Base Address register, when LAD is set to "0".

"0": Disable the mapping of the Joystick block

"1": Enable the mapping of the Joystick block (default)

## b3.....MEN: MPU401 Enable

This bit enables the mapping of the MPU401 block in the I/O space specified by 64-65h: MPU401 Base Address register, when LAD is set to "0".

"0": Disable the mapping of the MPU401 block

"1": Enable the mapping of the MPU401 block (default)

## b4.....MIEN: MPU401 IRQ Enable

This bit enables the interrupt service of MPU401, when LAD is set to "0" and MEN is set to "1". MPU401 generates an interrupt signal when it receives any kind of MIDI data from the RXD pin.

"0": The MPU401 block can not use the interrupt service.

"1": The MPU401 block can use interrupt signals determined by the MPUIRQ bits. (default)

#### b5.....I/O: I/O Address Aliasing Control

This bit selects the number of bits to decode for the I/O address of each block.

- "0": 16-bit address decode

- "1": 10-bit address decode (default)

#### b[7:6] .....SDMA: Sound Blaster DMA-8 Channel Select

These bits select the DMA channel for the Sound Blaster Pro block.

| "0": | DMA ch0 |

|------|---------|

| "1": | DMA ch1 |

| DMA ch1 | (default) |

|---------|-----------|

|         |           |

"2": reserved

"3": DMA ch3

## b[10:8] ......SBIRQ: Sound Blaster IRQ Channel Select

These bits select the interrupt channel for the Sound Blaster Pro block.

| IRQ5      | (default)                      |

|-----------|--------------------------------|

| IRQ7      |                                |

| IRQ9      |                                |

| IRQ10     |                                |

| IRQ11     |                                |

| reserved. |                                |

|           | IRQ7<br>IRQ9<br>IRQ10<br>IRQ11 |

## b[13:11] ......MPUIRQ: MPU401 IRQ Channel Select

When MIEN is set to "1", these bits select the interrupt channel for the MPU401 block.

| "0":       | IRQ5     |           |

|------------|----------|-----------|

| "1":       | IRQ7     |           |

| "2":       | IRQ9     | (default) |

| "3":       | IRQ10    |           |

| "4":       | IRQ11    |           |

| "5" - "7": | reserved |           |

|            |          |           |

Same interrupt channels can be assigned to SBIRQ and MPUIRQ.

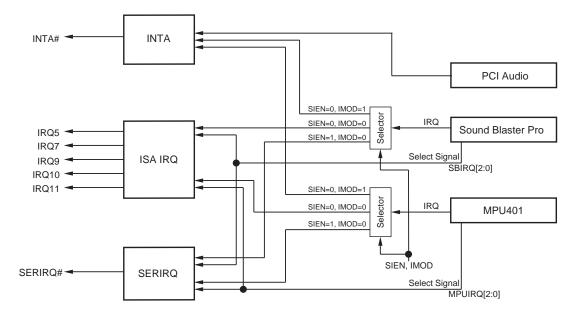

## b14.....SIEN: Serialized IRQ enable

DS-1E supports 3 types of interrupt protocols: PCI interrupt (INTA#), Legacy interrupt (IRQs) and Serialized IRQ. The interrupt protocol is selected with IMOD and SIEN as follows.

The interrupt channels for IRQs and Serialized IRQ are determined by SBIRQ and MPUIRQ,. Only one protocol can be used at once.

| SIEN | IMOD | Interrupt protocol      |           |

|------|------|-------------------------|-----------|

| 0    | 0    | Legacy interrupt (IRQs) | (default) |

| 0    | 1    | PCI interrupt (INTA#)   |           |

| 1    | 0    | Serialized IRQ          |           |

| 1    | 1    | reserved                |           |

## b15.....LAD: Legacy Audio Disable

This bit disables the Legacy Audio block.

"0": Enables the Legacy Audio block

"1": Disables the Legacy Audio block (default)

When this bit is set to "1", DS-1E does not respond to the I/O Target transaction for legacy I/O address on the PCI bus.

## 42-43h: Extended Legacy Audio Control

Read / Write

Default: 0000h

Access Bus Width: 8, 16, 32-bit

| / 101 |     |     | <i>i</i> un. 0, | 10, 02 | DIL |    |      |    |    |    |    |    |    |    |    |

|-------|-----|-----|-----------------|--------|-----|----|------|----|----|----|----|----|----|----|----|

| b15   | b14 | b13 | b12             | b11    | b10 | b9 | b8   | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| IMOD  | SB\ | /ER | SM              | OD     | -   | -  | MAIM | -  | -  | -  | -  | -  | -  | -  | -  |

#### b8.....MAIM: MPU401 Acknowledge Interrupt Mask

This bit determine whether interrupt is asserted when the acknowledge, which is occurred by changing

MPU401 mode form default to UART, is returned.

"0": Interrupt is asserted when the acknowledge is returned. (default)

"1": Interrupt is masked when the acknowledge is returned.

## b[12:11] .....SMOD: SB DMA mode

These bits determine the protocol to achieve the DMAC(8237) function on the PCI bus.

- "0": PC/PCI (default)

- "1": reserved

- "2": Distributed DMA (D-DMA)

- "3" reserved

## b[14:13] ......SBVER: SB Version Select

These bits set the version of the SB Pro DSP. The value set in these bits is returned by sending the E1h DSP command.

| "0": | ver 3.01 | (default) |

|------|----------|-----------|

| "1": | ver 2.01 |           |

| "2": | ver 1.05 |           |

| "3": | reserved |           |

#### b15.....IMOD: Legacy IRQ mode

The legacy interrupt protocol is selected with IMOD and SIEN. Refer to the explanation of SIEN bit.

## 44-45h: Subsystem Vendor ID Write

| De  | ad / W<br>fault: 1<br>cess B | 073h | dth: 16 | -bit |     |       |          |          |       |    |    |    |    |    |    |

|-----|------------------------------|------|---------|------|-----|-------|----------|----------|-------|----|----|----|----|----|----|

| b15 | b14                          | b13  | b12     | b11  | b10 | b9    | b8       | b7       | b6    | b5 | b4 | b3 | b2 | b1 | b0 |

|     |                              |      |         |      |     | Subsy | /stem Ve | endor ID | Write |    |    |    |    |    |    |

## b[15:0] ......Subsystem Vendor ID Write

This register sets the Subsystem Vendor ID that is read from 2C-2Dh (Subsystem Vendor ID register).

The default value is the YAMAHA Vendor ID, **1073h**. IHVs must change this ID to their Vendor ID in the BIOS POST routine.

In case EEPROM connects externally, this register is invalid, and do not reflect to Subsystem Vendor ID.

#### 46-47h: Subsystem ID Write

Read / Write Default: 0012h Access Bus Width: 16-bit

| AU  | Jess D | us vvic | un. 10 | -טונ |     |    |          |         |     |    |    |    |    |    |    |

|-----|--------|---------|--------|------|-----|----|----------|---------|-----|----|----|----|----|----|----|

| b15 | b14    | b13     | b12    | b11  | b10 | b9 | b8       | b7      | b6  | b5 | b4 | b3 | b2 | b1 | b0 |

|     |        |         |        |      |     | Su | ubsyster | n ID Wr | ite |    |    |    |    |    |    |

## b[15:0] ......Subsystem ID Write

This register sets the Subsystem ID that is read from 2E-2Fh (Subsystem ID register).

The default value is the DS-1E Device ID, **0012h**. IHVs must change this ID to their ID in the BIOS POST routine.

In case EEPROM connects externally, this register is invalid, and do not reflect to Subsystem ID.

## 48-49h: DS-1E Control

| De  | ad / W<br>fault: 0<br>cess B | 001h | dth: 8, | 16, 32- | -bit |    |    |    |    |    |    |      |      |    |      |

|-----|------------------------------|------|---------|---------|------|----|----|----|----|----|----|------|------|----|------|

| b15 | b14                          | b13  | b12     | b11     | b10  | b9 | b8 | b7 | b6 | b5 | b4 | b3   | b2   | b1 | b0   |

| -   | -                            | -    | -       | -       | -    | -  | -  | -  | -  | -  | -  | ACLS | WRST | -  | CRST |

#### b0.....CRST: AC'97 Software Reset Signal Control

This bit controls the CRST# signal.

"0": Inactive (CRST#=High)

"1": Active (CRST#=Low) (default)

#### b2.....WRST: AC'97 Warm Reset

This bit places the AC'97 in warm reset condition when the BIT\_CLK signal on the AC'97 remains in inactive state. If this bit is set to "1", it will automatically return to "0" after  $1.3\mu$ s time duration. This bit is valid only while the ACLS bit is set to "0". Except in this case, even if this bit is attempted to be set to "1", no warm reset will be generated (write operation of "1" remains disabled).

"0": Normal (default)

"1": AC'97 Warm Reset

#### b3.....ACLS: AC-Link Status (Read Only)

This bit indicates whether or not the AC-link is active. This bit is "1" when the AC-link remains in active state (the BIT\_CLK signal is active).

"0": AC'97 Inactive (default)

"1": AC'97 Active

#### 4A-4Bh: DS-1E Power Control 1

Read / Write Default: 0000h Access Bus Width: 8, 16, 32-bit

| b15 | b14 | b13 | b12 | b11 | b10 | b9  | b8  | b7 | b6  | b5 | b4 | b3 | b2   | b1 | b0  |

|-----|-----|-----|-----|-----|-----|-----|-----|----|-----|----|----|----|------|----|-----|

| PR7 | PR6 | PR5 | PR4 | PR3 | PR2 | PR1 | PR0 | -  | JSR | -  | -  | -  | DPLL | -  | DMC |

#### b0.....DMC: Disable Master Clock Oscillation

Setting this bit to "1" disables the oscillation of the Master Clock (24.576 MHz).

"0": Normal (default)

"1": Disable

## b2.....DPLL: Disable PLL Clock Oscillation

Setting this bit to "1" disables the oscillation of PLL.

"0": Normal (default)

"1": Disable

#### b6.....JSR: Joystick Reset

This bit controls reset of the flip-flop circuit following the analog comparator stage on the joystick port.

The Initial value is set to "0" immediately after power on reset or hardware reset.

"0": Normal (default)

"1": Resets the flip-flop circuit following the analog comparator stage on the joystick port

#### b8.....PR0: AC'97 Power Down Control 0

This bit controls the power state of the ADC and Input Mux in the Primary AC'97.

"0": Normal (default)

"1": Power down

#### b9.....PR1: AC'97 Power Down Control 1

This bit controls the power state of the **DAC** in the Primary AC'97.

"0": Normal (default)

"1": Power down

## b10.....PR2: AC'97 Power Down Control 2

This bit controls the power state of the **Analog Mixer (Vref still on)** in the Primary AC'97. This power state retains the Reference Voltage of the AC'97.

"0": Normal (default)

"1": Power down

## b11.....PR3: AC'97 Power Down Control 3

This bit controls the power state of the **Analog Mixer (Vref off)** in the Primary AC'97. This power state removes Reference Voltage of the AC'97.

"0": Normal (default)

"1": Power down

#### b12.....PR4: AC'97 Power Down Control 4

This bit controls the power state of the **AC-link** in the Primary AC'97.

"0": Normal (default)

"1": Power down

## b13.....PR5: AC'97 Power Down Control 5

Setting this bit to "1" disables the internal clock of the Primary AC'97. In case the AC'97 is used with DS-1E, the master clock is supplied from DS-1E. Therefore, when the clock is stopped completely, set PR5 bits to "1" firstly, then the CMCD bit should be set to "1" after duration of 1ms or longer.

"0": Normal (default)

"1": Disable

## b14.....PR6: AC'97 Power Down Control 6

This bit controls PR6 bit status of the power control register in the Primary AC'97.

## b15.....PR7: AC'97 Power Down Control 7

This bit controls PR7 bit status of the power control register in the Primary AC'97.

Respective data set to b[15:8] are correspondingly set into the "Power down Ctrl/Stat" register in the Primary AC'97 via the AC-Link. These are not set into the "Power down Ctrl/Stat" register in the Secondary AC'97.

## 4C-4Dh: D-DMA Slave Configuration

| De  | ad / W<br>fault: 0<br>cess B | 000h | dth: 8, | 16, 32 <sup>,</sup> | -bit   |        |    |    |    |    |    |    |    |    |    |

|-----|------------------------------|------|---------|---------------------|--------|--------|----|----|----|----|----|----|----|----|----|

| b15 | b14                          | b13  | b12     | b11                 | b10    | b9     | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|     |                              |      |         |                     | Base A | ddress |    |    |    |    |    | EA | Т  | s  | CF |

## b0.....CE: Channel Enable

This bit enables the Distributed DMA function.

"0": Disable Distributed DMA (default)

"1": Enable Distributed DMA

#### b[2:1] .....TS: Transfer Size (Read Only)

These bits indicate the size of the DMA transfer. Since DS-1E supports only 8-bit DMA transfer, the bits are hardwired to 00b.

#### b3.....EA: Extended Address (Read Only)

DS-1E does not support extended address mode. This bit is hardwired to 0b.

#### b[15:4] ......Base Address : D-DMA Slave Base Address

These bits indicate the D-DMA slave base address.

## 4E-4Fh: DS-1E Power Control 2

Read / Write Default: 0000h

| Acc | cess B | us Wid | dth: 8, 1 | <u>16, 32</u> . | -bit  |       |       |      |       |       |       |       |      |      |      |

|-----|--------|--------|-----------|-----------------|-------|-------|-------|------|-------|-------|-------|-------|------|------|------|

| b15 | b14    | b13    | b12       | b11             | b10   | b9    | b8    | b7   | b6    | b5    | b4    | b3    | b2   | b1   | b0   |

| -   | -      | -      | PSHWV     | PSIO            | PSACL | PSDIR | PSDIT | PSZV | PSSRC | PSPCA | PSJOY | PSMPU | PSSB | PSFM | CMCD |

#### b0.....CMCD: CODEC Master Clock Disable

Setting this bit to "1" disables the oscillation of the CMCLK. To stop a clock, when the CMCLK is supplied to the AC'97, it is required that b13:PR5 bit of 4A-4Bh register is set to "1". (If the Secondary AC'97 is used, it is also necessary that b5:SPR5 bit of 5A-5Bh register is set to "1".)

"0": Normal (default)

"1": Disable

#### b1.....PSFM: Power Save FM Synthesizer

Setting this bit to "1" stops a clock supplied to the FM synthesizer block.

"0": Normal (default)

"1": Disable

## b2.....PSSB: Power Save Sound Blaster

Setting this bit to "1" stops a clock supplied to the Sound Blaster block.

"0": Normal (default)

"1": Disable

#### b3.....PSMPU: Power Save MPU401

Setting this bit to "1" stops a clock supplied to the MPU401 block. "0": Normal (default) "1": Disable

#### b4.....PSJOY: Power Save Joystick

Setting this bit to "1" disables the comparator of the Joystick block.

"0": Normal (default) "1": Disable

## b5.....PSPCA: Power Save PCI Audio

Setting this bit to "1" stops a clock supplied to the PCI Audio block. "0": Normal (default)

"1": Disable

## b6.....PSSRC: Power Save SRC

Setting this bit to "1" stops a clock supplied to the SRC block.

"0": Normal (default) "1": Disable

#### b7.....PSZV: Power Save Zoomed Video port

Setting this bit to "1" stops a clock supplied to the Zoomed Video port block. "0": Normal (default) "1": Disable

#### b8.....PSDIT: Power Save Digital Audio Interface Transmitter

Setting this bit to "1" stops a clock supplied to the DIT (SPDIF OUT) block. "0": Normal (default) "1": Disable

#### b9.....PSDIR: Power Save Digital Audio Interface Receiver

Setting this bit to "1" stops a clock supplied to the DIR (SPDIF IN) block. "0": Normal (default) "1": Disable

## b10.....PSACL: Power Save AC-Link

Setting this bit to "1" stops a clock supplied to the AC-Link block. "0": Normal (default) "1": Disable

## b11.....PSIO: Power Save I/O Pad

Setting this bit to "1" cuts the pull up resistor of the input pins except for the PCI interface and AC-Link.

The input signals keep the level before PSIO bit is set from "0" to "1". In case the input level is only "low", the pull up resistor is cut.

"0": Normal (default)

"1": Cuts the pull up resistor

## b12.....PSHWV: Power Save Hardware Volume

Setting this bit to "1" stops a clock supplied to the Hardware Volume block.

"0": Normal (default)

"1": Disable

Power Management Block

## 50h: Capability ID

|   | De            | ad Onl<br>fault: 0<br>cess B | ĺ1h | dth: 8, | 16, 32- | ·bit |    |    |  |  |  |

|---|---------------|------------------------------|-----|---------|---------|------|----|----|--|--|--|

|   | b7            | b6                           | b5  | b4      | b3      | b2   | b1 | b0 |  |  |  |

| ĺ | Capability ID |                              |     |         |         |      |    |    |  |  |  |

## b[7:0] .....Capability ID: Capability Identifier

This register indicates that the new capability register is for Power Management control. This register is hardwired to **01h**.

## 51h: Next Item Pointer

| De  | ad Onl<br>fault: 0              | ĺ0h |  |  |  |  |  |  |  |  |  |  |

|-----|---------------------------------|-----|--|--|--|--|--|--|--|--|--|--|

| Aco | Access Bus Width: 8, 16, 32-bit |     |  |  |  |  |  |  |  |  |  |  |

| b7  | b7 b6 b5 b4 b3 b2 b1 b0         |     |  |  |  |  |  |  |  |  |  |  |

|     | Next Item Pointer               |     |  |  |  |  |  |  |  |  |  |  |

## b[7:0] .....Next Item Pointer

DS-1E does not provide other new capability besides Power Management. This register is hardwired to **00h**.

## 52-53h: Power Management Capabilities

|   | De  | ad Onl<br>fault: 0<br>cess B | 401h | dth: 8, | 16, 32· | -bit |    |    |    |    |    |    |    |    |         |    |

|---|-----|------------------------------|------|---------|---------|------|----|----|----|----|----|----|----|----|---------|----|

|   | b15 | b14                          | b13  | b12     | b11     | b10  | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1      | b0 |

| ſ | -   | -                            | -    | -       | -       | D2S  | -  | -  | -  | -  | -  | -  | -  |    | Version |    |

## b[2:0] .....Version

These bits contain the revision number of the Power Management Interface Specification. They are hardwired to **001b**.

## b10.....D2S: D2 Support

This bit indicates that DS-1E support "D2" of the power state. It is hardwired to "1".

## 54-55h: Power Management Control / Status

|   | Re                              | Read / Write |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|---|---------------------------------|--------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|   | Default: 0000h                  |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| _ | Access Bus Width: 8, 16, 32-bit |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   | b15                             |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| ſ | -                               | -            | - | - | - | - | - | - | - | - | - | - | - | - | Р | S |

#### b[1:0] .....PS: Power State

These bits determine the power state of DS-1E. DS-1E supports the following power states:

| "0": | D0                |                 |

|------|-------------------|-----------------|

| "1": | D1                | (not supported) |

| "2": | D2                |                 |

| "3": | $D3_{\text{hot}}$ |                 |

When the power state is changed from  $D3_{hot}$  to D0, DS-1E resets the PCI Configuration register 00-3Fh. DS-1E transits to D0 Uninitialized state.

Though the power state of this register is changed, the power consumption of DS-1E is not changed. To support low power, Windows driver controls DS-1E Power Control 1 / DS-1E Power Control 2 / DS-1E Control / DS-1E Secondary AC'97 Power Control registers.

DS-1E can support the power state of D0, D1, D2 and D3 with ACPI. In this case, set ACPI bit (58-59h: ACPI Mode Register) to "1" to disable Capabilities of PCI Bus Power Management.

## 58-59h: ACPI Mode

Read / Write Default: 0000h Access Bus Width: 8, 16, 32-bit

| AU  |     |     |     |     |     |    |    |    |    |    |    |    |    |    |      |

|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|------|

| b15 | b14 | b13 | b12 | b11 | b10 | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0   |

| -   | -   | -   | -   | -   | -   | -  | -  | -  | -  | -  | -  | -  | -  | -  | ACPI |

#### b0.....ACPI: ACPI Mode Select

This bit select either PCI Bus Power Management or ACPI Mode for power management of DS-1E.

"0": PCI Bus Power Management is used. CAP bit (06-07h: Status Register) and Capabilities Pointer (34h) are enabled. (default)

"1": ACPI Mode is used. CAP bit and Capabilities Pointer are hardwired "0", and disabled.

## 5A-5Bh: DS-1E Secondary AC'97 Power Control

Read / Write Default: 0000h

Access Bus Width: 8, 16, 32-bit

| 7.00 |     |     |     | 10, 02 |     |    |    |      |      |      |      |      |      |      |      |

|------|-----|-----|-----|--------|-----|----|----|------|------|------|------|------|------|------|------|

| b15  | b14 | b13 | b12 | b11    | b10 | b9 | b8 | b7   | b6   | b5   | b4   | b3   | b2   | b1   | b0   |

| -    | -   | -   | -   | -      | -   | -  | -  | SPR7 | SPR6 | SPR5 | SPR4 | SPR3 | SPR2 | SPR1 | SPR0 |

#### b0.....SPR0: Secondary AC'97 Power Down Control 0

This bit controls the power state of the ADC and Input Mux in the Secondary AC'97.

"0": Normal (default)

"1": Power down

#### b1.....SPR1: Secondary AC'97 Power Down Control 1

This bit controls the power state of the **DAC** in the Secondary AC'97.

"0": Normal (default)

"1": Power down

#### b2.....SPR2: Secondary AC'97 Power Down Control 2

This bit controls the power state of the **Analog Mixer** (**Vref still on**) in the Secondary AC'97. This power state retains the Reference Voltage of the AC'97.

"0": Normal (default)

"1": Power down

#### b3.....SPR3: Secondary AC'97 Power Down Control 3

This bit controls the power state of the **Analog Mixer (Vref off)** in the Secondary AC'97. This power state removes Reference Voltage of the AC'97.

"0": Normal (default)

"1": Power down

#### b4.....SPR4: Secondary AC'97 Power Down Control 4

This bit controls the power state of the **AC-link** in the Secondary AC'97.

"0": Normal (default)

"1": Power down

#### b5.....SPR5: Secondary AC'97 Power Down Control 5

Setting this bit to "1" disables the internal clock of the Secondary AC'97. In case the AC'97 is used with DS-1E, the master clock is supplied from DS-1E. Therefore, when the clock is stopped completely, set SPR5 bits to "1" firstly, then the CMCD bit should be set to "1" after duration of 1ms or longer.

"0": Normal (default)

"1": Disable

#### b6.....SPR6: Secondary AC'97 Power Down Control 6

This bit controls PR6 bit status of the power control register in the Secondary AC'97.

#### b7.....SPR7: Secondary AC'97 Power Down Control 7

This bit controls PR7 bit status of the power control register in the Secondary AC'97.

Respective data set to b[7:0] are correspondingly set into the "Power down Ctrl/Stat" register in the Secondary AC'97 via the AC-Link. These are not set into the "Power down Ctrl/Stat" register in the Primary AC'97.

## 60-61h: FM Synthesizer Base Address

|   | De                                                    | ad / W<br>fault: 0<br>cess B | 388h | dth: 8, | 16, 32· | -bit |  |  |  |  |  |  |   |   |  |

|---|-------------------------------------------------------|------------------------------|------|---------|---------|------|--|--|--|--|--|--|---|---|--|

| ĺ | b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0 |                              |      |         |         |      |  |  |  |  |  |  |   |   |  |

| ſ | FM Synthesizer Base Address                           |                              |      |         |         |      |  |  |  |  |  |  | - | - |  |

## b[15:2] ......FM Synthesizer Base Address

This register sets the base address of the FM synthesizer. If b5:I/O bit of 40h register is set to "1", b[9:2] bits are decoded by ignoring b[15:10] bits.

## 62-63h: Sound Blaster Base Address

| De  | ad / W<br>fault: 0<br>cess B | 220h | dth: 8, | 16, 32 | -bit |  |  |  |  |  |  |  |   |   |   |

|-----|------------------------------|------|---------|--------|------|--|--|--|--|--|--|--|---|---|---|

| b15 |                              |      |         |        |      |  |  |  |  |  |  |  |   |   |   |

|     | Sound Blaster Base Address   |      |         |        |      |  |  |  |  |  |  |  | - | - | - |

## b[15:4] ......Sound Blaster Base Address

This register sets the base address of the Sound Blaster. If b5:I/O bit of 40h register is set to "1", b[9:4] bits are decoded by ignoring b[15:10] bits.

## 64-65h: MPU401 Base Address

| De                                           | ad / W<br>fault: 0<br>cess B | 330h | dth: 8, | 16, 32 <sup>.</sup> | -bit |  |  |  |  |  |  |  |

|----------------------------------------------|------------------------------|------|---------|---------------------|------|--|--|--|--|--|--|--|

| b15 b14 B13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 |                              |      |         |                     |      |  |  |  |  |  |  |  |

|                                              | MPU401 Base Address          |      |         |                     |      |  |  |  |  |  |  |  |

#### b[15:1] ...... MPU401 Base Address

This register sets the base address of the MPU401. If b5:I/O bit of 40h register is set to "1", b[9:1] bits are decoded by ignoring b[15:10] bits.

## 66-67h: Joystick Base Address

| De  | ad / W<br>fault: 0<br>cess B | 201h | dth: 8, | 16, 32· | -bit |  |  |  |  |  |  |  |  |  |  |

|-----|------------------------------|------|---------|---------|------|--|--|--|--|--|--|--|--|--|--|

| b15 |                              |      |         |         |      |  |  |  |  |  |  |  |  |  |  |

|     | Joystick Base Address        |      |         |         |      |  |  |  |  |  |  |  |  |  |  |

#### b[15:0] .....Joystick Base Address

This register sets the base address of the Joystick. If b5:I/O bit of 40h register is set to "1", b[9:0] bits are decoded by ignoring b[15:10] bits.

b2

b1

b0

# 2. ISA Compatible Device

DS-1E contains the following functions to maintain the compatibility with the past ISA Sound Devices. These devices are considered Legacy devices and the functions are referred to as Legacy Audio.

Legacy Audio is independent from PCI Audio and can be used simultaneously.

The configuration is set in the Legacy Audio Control Register in the PCI Configuration Register space. Basically, these registers are configured by the BIOS.

Also, logical device IDs are assigned to the devices to support Plug and Play. Yamaha defines the following logical IDs.

To control the device with the BIOS, the logical device IDs must be defined in the PnP BIOS extended ROM space. The logical IDs are determined by how it is configured. IDs and configuration are as follows.

|                   |                   | Functions use | ed (Block)            |          |

|-------------------|-------------------|---------------|-----------------------|----------|

| Logical Device ID | FM <sup>(*)</sup> | MPU401        | SB Pro <sup>(*)</sup> | Joystick |

| YMH0100           | О                 | О             | Ο                     |          |

| YMH0101           |                   |               |                       | 0        |

| YMH0102           | 0                 |               |                       |          |

| YMH0103           |                   | 0             |                       |          |

| YMH010A           | 0                 | 0             |                       |          |

\* The blocks pertain to the following.

FM: Points to the FM synthesizer mapped to AdLibBase (0x0388).

SB Pro: Points to the Voice Playback section only.

These devices are independent from each other, and can be Enabled/Disabled individually. However, both AdLib and Sound Blaster must be disabled to disable the internal FM Synthesizer. Disabling just AdLib only masks the access.

The driver by Yamaha supports logical device ID, YMH0100, YMH0102, YMH0103 and YMH010A. For YMH0101, use the driver provided by Microsoft.

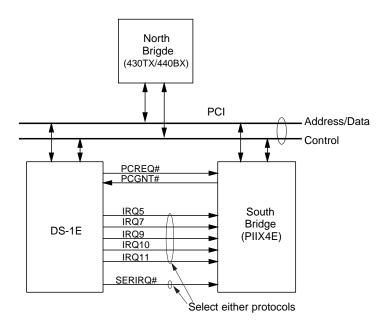

DS-1E supports PC/PCI and D-DMA protocols to emulate the DMA of SB Pro on the PCI. In addition, DS-1E supports the old type of interrupts used by ISA and the Serialized IRQ protocol.

The combination of PC/PCI and Serialized IRQ is recommended for DS-1E. The system block diagram when using Intel chip set is shown below.

The PCI-to-ISA bridge needs to support PC/PCI. IRQ is directly connected to the IRQ input pins on the PCI-to-ISA bridge.

## 2-1. FM Synthesizer Block

FM Synthesizer Block is register compatible with YMF289B. However, Power Management register has been deleted because it is now controlled by the PCI Configuration Register.

The following shows the FMBase I/O map of FM Synthesizer.

| FMBase   | (R)   | Status Register port              |

|----------|-------|-----------------------------------|

| FMBase   | (W)   | Address port for Register Array 0 |

| FMBase+1 | (R/W) | Data port                         |

| FMBase+2 | (W)   | Address port for Register Array 1 |

| FMBase+3 | (R/W) | Data port                         |

The following shows the FM Synthesizer Block registers.

## 2-1-1. Status Register

#### FM Synthesizer Status Register (RO):

| Address | D7  | D6  | D5  | D4 | D3 | D2   | D1 | D0   |

|---------|-----|-----|-----|----|----|------|----|------|

| xxh     | IRQ | FT1 | FT2 | -  | -  | BUSY | -  | BUSY |

## 2-1-2. FM Synthesizer Data Register

## FM Synthesizer Data Register Array 0 (R/W):

| Address                | D7        | D6      | D5  | D4    | D3 | D2  | D1   | D0    |

|------------------------|-----------|---------|-----|-------|----|-----|------|-------|

| 00-01h                 | LSI TEST  |         |     |       |    |     |      |       |

| 02h                    | TIMER 1   |         |     |       |    |     |      |       |

| 03h                    |           | TIMER 2 |     |       |    |     |      |       |

| 04h                    | RST       | MT1     | MT2 | -     | -  | -   | ST2  | ST1   |

| 08h                    | -         | NTS     | -   | -     | -  | -   | -    | -     |

| 20-35h <sup>(*1)</sup> | AM        | VIB     | EGT | KSR   |    | ML  | JLT  |       |

| 40-55h <sup>(*2)</sup> | K         | SL      | TL  |       |    |     |      |       |

| 60-75h <sup>(*3)</sup> | AR DR     |         |     |       | R  |     |      |       |

| 80-95h <sup>(*4)</sup> | SL        |         |     | RR    |    |     |      |       |

| A0-A8h                 | F-NUM (L) |         |     |       |    |     |      |       |

| B0-B8h                 | B0-B8h    |         | KON | BLOCK |    |     | F-NU | M (H) |

| BDh                    | DAM       | DVB     | RHY | BD    | SD | ТОМ | TC   | НН    |

| C0-C8h                 | (*6)      | (*6)    | CHR | CHL   |    | FB  |      | CNT   |

| E0-F5h <sup>(*5)</sup> | -         | -       | -   | -     | -  |     | WS   |       |

## FM Synthesizer Data Register Array 1 (R/W)

| Address                | D7        | D6   | D5        | D4             | D3   | D2   | D1    | D0  |  |

|------------------------|-----------|------|-----------|----------------|------|------|-------|-----|--|

| 00-01h                 | LSI TEST  |      |           |                |      |      |       |     |  |

| 04h                    | -         | -    |           | CONNECTION SEL |      |      |       |     |  |

| 05h                    | -         | -    | -         | -              | -    | (*6) | (*6)  | NEW |  |

| 20-35h <sup>(*1)</sup> | AM        | VIB  | EGT       | KSR            | MULT |      |       |     |  |

| 40-55h <sup>(*2)</sup> | KSL       |      |           |                | TL   |      |       |     |  |

| 60-75h <sup>(*3)</sup> | AR        |      |           |                | DR   |      |       |     |  |

| 80-95h <sup>(*4)</sup> | SL        |      |           |                | RR   |      |       |     |  |

| A0-A8h                 | F-NUM (L) |      |           |                |      |      |       |     |  |

| B0-B8h                 | -         | -    | KON BLOCK |                |      | F-NU | M (H) |     |  |

| C0-C8h                 | (*6)      | (*6) | CHR       | CHL            |      | FB   |       | CNT |  |

| E0-F5h <sup>(*5)</sup> | -         | -    | -         | -              | -    |      | WS    |     |  |

- \*1 : 26h, 27h, 2Eh and 2Fh do not exist.

- \*2 : 46h, 47h, 4Eh and 4Fh do not exist.

- \*3 : 66h, 67h, 6Eh and 6Fh do not exist.

- \*4 : 86h, 87h, 8Eh and 8Fh do not exist.

- \*5 : E6h, E7h, EEh and EFh do not exist.

- \*6 : The bits exist, but do not function.

## 2-2. Sound Blaster Pro Block

Sound Blaster Pro block emulates the DSP commands of Sound Blaster and Sound Blaster Pro. Only playback functions are supported (record functions are not supported). However, to maintain compatibility for games, it is designed so that every DSP command receives a correct response. The DMA transfer of this block uses PC/PCI or D-DMA protocol.

The following shows the SBBase I/O map of SB Pro.

| SBBase    | (R)   | FM Synthesizer Status port                       |

|-----------|-------|--------------------------------------------------|

| SBBase    | (W)   | FM Synthesizer Address port for Register Array 0 |

| SBBase+1h | (R/W) | FM Synthesizer Data register                     |

| SBBase+2h | (W)   | FM Synthesizer Address port for Register Array 1 |

| SBBase+3h | (R/W) | FM Synthesizer Data port                         |

| SBBase+4h | (R/W) | SB Mixer Address port                            |

| SBBase+5h | (R/W) | SB Mixer Data port                               |

| SBBase+6h | (W)   | SB DSP Reset port                                |

| SBBase+8h | (R)   | FM Synthesizer Status port                       |

| SBBase+8h | (W)   | FM Synthesizer Address port for Register Array 0 |

| SBBase+9h | (R/W) | FM Synthesizer Data port                         |

| SBBase+Ah | (R)   | DSP Read Data port                               |

| SBBase+Ch | (R)   | DSP Write-buffer status port                     |

| SBBase+Ch | (W)   | DSP Write Command/Data port                      |

| SBBase+Eh | (R)   | DSP Read-buffer status port                      |

#### 2-2-1. DSP Command

The following shows the list of DSP Commands that are supported by the SB Pro engine. Both SB and SB Pro commands are supported.

| CMD | Support | Function |  |

|-----|---------|----------|--|

|-----|---------|----------|--|

| ONID    | ouppon |                                                                                |

|---------|--------|--------------------------------------------------------------------------------|

| 10h     | 0      | 8bit direct mode single byte digitized sound output                            |

| 14h     | 0      | 8bit single-cycle DMA mode digitized sound output                              |

| 16h     |        | 8bit to 2bit ADPCM single-cycle DMA mode digitized sound output                |

| 17h     |        | 8bit to 2bit ADPCM single-cycle DMA mode digitized sound output with ref. byte |

| 1Ch     | 0      | 8bit auto-init DMA mode digitized sound output                                 |

| 1Fh     |        | 8bit to 2bit ADPCM auto-init DMA mode digitized sound output with ref. byte    |

| 20h(*1) | 0      | 8bit direct mode single byte digitized sound input                             |

| 24h(*1) | 0      | 8bit single-cycle DMA mode digitized sound input                               |

| 2Ch(*1) | 0      | 8bit auto-init DMA mode digitized sound input                                  |

| 30h     | 0      | Polling mode MIDI input                                                        |

| 31h     | 0      | Interrupt mode MIDI input                                                      |

| 34h     | 0      | UART polling mode MIDI I/O                                                     |

| 35h     | 0      | UART interrupt mode MIDI I/O                                                   |

| 36h(*2) | 0      | UART polling mode MIDI I/O with time stamping                                  |

| 37h(*2) | 0      | UART interrupt mode MIDI I/O with time stamping                                |

| 38h     | 0      | MIDI output                                                                    |

| 40h     | 0      | Set digitized sound transfer Time Constant                                     |

| 48h     | 0      | Set DSP block transfer size                                                    |

| 74h     | 0      | 8bit to 4bit ADPCM single-cycle DMA mode digitized sound output                |

| 75h     | 0      | 8bit to 4bit ADPCM single-cycle DMA mode digitized sound output with ref. byte |

| 76h     |        | 8bit to 3bit ADPCM single-cycle DMA mode digitized sound output                |

| 77h     |        | 8bit to 3bit ADPCM single-cycle DMA mode digitized sound output with ref. byte |

| 7Dh     | 0      | 8bit to 4bit ADPCM auto-init DMA mode digitized sound output with ref. byte    |

| 7Fh     |        | 8bit to 3bit ADPCM auto-init DMA mode digitized sound output with ref. byte    |

| 80h     | 0      | Pause DAC for a duration                                                       |

| 90h     | 0      | 8bit high-speed auto-init DMA mode digitized sound output                      |

| 91h     | 0      | 8bit high-speed single-cycle DMA mode digitized sound output                   |

| 98h(*1) | 0      | 8bit high-speed auto-init DMA mode digitized sound input                       |

| 99h(*1) | 0      | 8bit high-speed single-cycle DMA mode digitized sound input                    |

| A0h(*1) |        | Set input mode to mono                                                         |

| A8h(*1) | 0      | Set input mode to stereo                                                       |

| D0h     | 0      | Pause 8bit DMA mode digitized sound I/O                                        |

| D1h(*3) |        | Turn on speaker                                                                |

| D3h(*3) | 0      | Turn off speaker                                                               |

| D4h     | 0      | Continue 8bit DMA mode digitized sound I/O                                     |

| D8h     | 0      | Get speaker status                                                             |

| DAh     | 0      | Exit 8bit auto-init DMA mode digitized sound I/O                               |