# YAMAHA L S I

# **YM3436D**

### DIR<sub>2</sub>

Digital audio Interface Receiver

#### OUTLINE

The YM3436D(DIR2) receives and demodulates the digital audio interface format signals, conforming with the EIAJ CP-340 or AES/EBU. Comparing to the YM3623B(DIR), external synchronization and error processing functions are further improved and it is made applicable more widely by using the channel status and user data outputs.

#### FEATURES

- Capable to accept the A/D input and asynchronous input as well as the digital audio interface signal input.

- As a phase comparator and VCO are built in, a PLL circuit synchronized with the external input can be formed easily (fs=32kHz~48kHz)

- Capable to demodulate the digital audio interface signal and output 24-bit 2-channel audio data and control data.

- As a clock master, it supplies various kinds of clock signals to the other LSIs.

- The built-in asynchronous buffer enables the output phase to be retained even on clock switching. Also capable of easy interface between the equipments where full synchronization is impossible such as when several digital audio interface signals are received simultaneously.

- Detects transmission errors and reception errors and executes error processing of data hold and muting.

- Executes decoding and output of the validity flag, channel status, user data as control data. Especially, the channel status conforms with both Consumer use and Professional use formats. Also, information can be read out microprocessor interface.

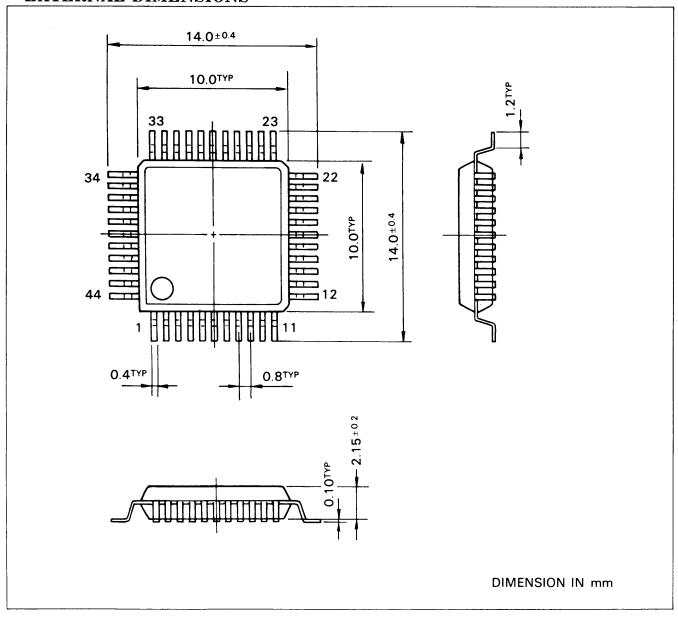

- 5V power supply, Si-gate CMOS, 44-pin QFP.

YAMAHA CORPORATION

YM3436C CATALOG CATALOG No.: LSI-213436D2

1995. 12

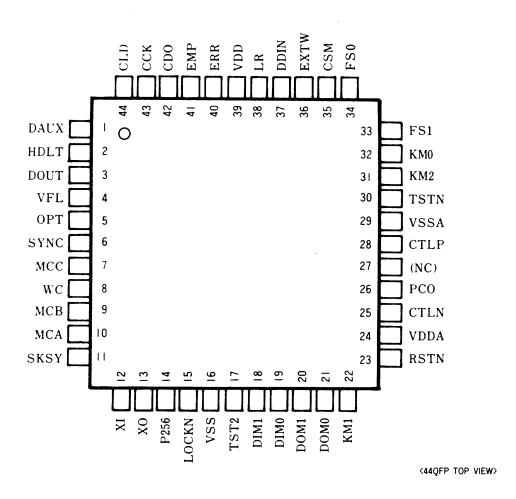

#### ■ PIN CONFIGURATION

## **YM3436D**

#### ■ PIN DESCRIPTIONS

| No. | Name  | I/O | Description                                                        |

|-----|-------|-----|--------------------------------------------------------------------|

| 1   | DAUX  | I   | Audio data auxiliary input                                         |

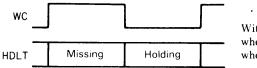

| 2   | HDLT  | О   | Asynchronous buffer operation flag output                          |

| 3   | DOUT  | О   | Audio data output                                                  |

| 4   | VFL   | О   | Validity flag output                                               |

| 5   | ОРТ   | О   | Synchronous signal output (fs) for DAC                             |

| 6   | SYNC  | О   | Synchronous signal output (fs) for DSP                             |

| 7   | MCC   | О   | Bit clock output (64fs)                                            |

| 8   | WC    | О   | Word clock output (fs)                                             |

| 9   | мсв   | О   | Bit clock output (128fs)                                           |

| 10  | MCA   | О   | Bit clock output (256fs)                                           |

| 11  | SKSY  | I   | Clock synchronous control input                                    |

| 12  | ΧI    | I   | Crystal oscillator connection, or external clock input (256fs)     |

| 13  | xo    | О   | Crystal oscillator connection                                      |

| 14  | P256  | О   | VCO clock output (256fs when locked)                               |

| 15  | LOCKN | О   | PLL lock flag output ('L'; when locked, 'H'; when unlocked)        |

| 16  | vss   | _   | Ground (for logic block)                                           |

| 17  | TST2  | О   | LSI test terminal (usually disconnected)                           |

| 18  | DIM1  | I   | Data input mode select 1                                           |

| 19  | DIMO  | I   | Data input mode select 0                                           |

| 20  | DOM1  | I   | Data output mode select 1                                          |

| 21  | DOM0  | I   | Data output mode select 0                                          |

| 22  | KM1   | I   | Clock mode select 1 ('H'; PLL auto switching, 'L'; XI fixed)       |

| 23  | RSTN  | I   | System reset input ('L' active)                                    |

| 24  | VDDA  | _   | +5V power supply (for VCO block connected with VDD externally)     |

| 25  | CTLN  | I   | VCO control input                                                  |

| 26  | PCO   | O   | PLL phase comparator output                                        |

| 27  | (NC)  |     | (Disconnected externally)                                          |

| 28  | CTLP  | l   | VCO adjustment input (usually connected with VSSA)                 |

| 29  | VSSA  | _   | Ground (for VCO block, connected with VSS externally)              |

| 30  | TSTN  | I   | LSI test terminal (usually disconnected)                           |

| 31  | KM2   | I   | Clock mode select 2 ('H'; PLL synchronized, 'L'; XI synchronized)  |

| 32  | KM0   | I   | Clock mode select 0 ('H'; EXTW input, 'L'; DDIN input)             |

| 33  | FS1   | 0   | Sampling frequency code output 1/channel status output             |

| 34  | FS0   | О   | Sampling frequency code output 0/user data output                  |

| 35  | CSM   | I   | Channel status, user data output select                            |

| 36  | EXTW  | I   | Audio data auxiliary input word clock                              |

| 37  | DDIN  | I   | EIAJ(AES/EBU) digital audio interface signal input                 |

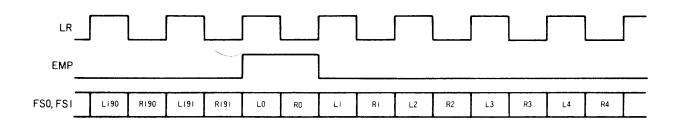

| 38  | LR    | 0   | PLL word clock output (fs when locked)                             |

| 39  | VDD   | _   | +5V power supply (for logic block)                                 |

| 40  | ERR   | О   | Data error flag output                                             |

| 41  | EMP   | 0   | Emphasis control code output/block start synchronous signal output |

| 42  | CDO   | O   | Microprocessor interface data output                               |

| 43  | CCK   | I   | Microprocessor interface clock input                               |

| 44  | CLD   | I   | Microprocessor interface load input                                |

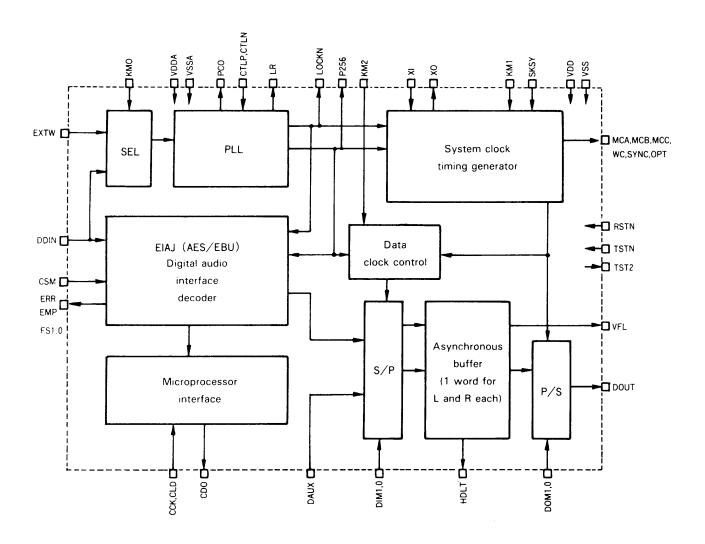

#### ■ BLOCK DIAGRAM

#### ■ FUNCTION DESCRIPTION

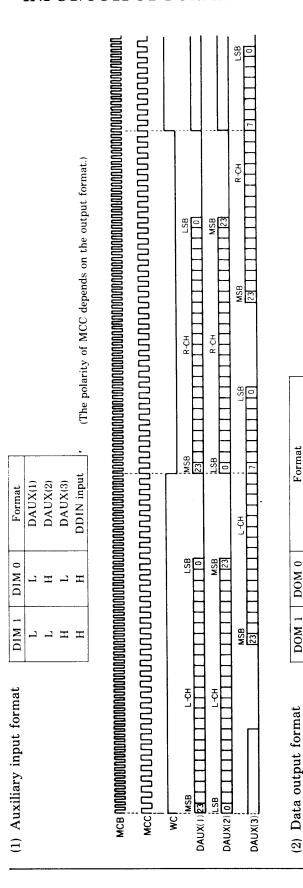

#### 1. Data input DDIN, DAUX, DIM1, DIM0

The digital audio interface signal (hereinafter referred to as "DAIF signal") of EIAJ(AES/EBU) format is inputted into the DDIN terminal. In addition to that, this LSI has an auxiliary input terminal DAUX for the audio data to which signals from the A/D converter and DSP can be inputted. The input format for the DAUX is selected by DIM0 and DIM1 terminals.

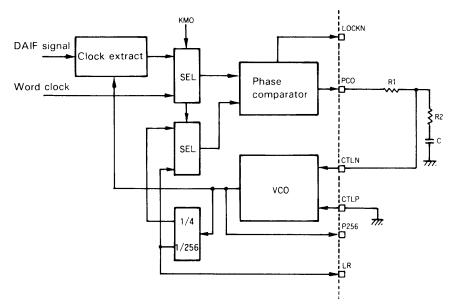

#### 2. PLL block PCO, CTLN, CTLP, P256, LR, LOCKN, KM0, KM2, EXTW

DIR2 has a phase comparator and VCO to regenerate the clock signals synchronized with the input rate. The output of the phase comparator is output from the PCO terminal. With an appropriate time constant attached externally, and by applying input to the CTLN terminal, the PLL clock regeneration circuit is formed. The CTLP terminal is for VCO adjustment. Usually it should be grounded. The VCO oscillation frequency is 256fs and output from the P256 terminal. The clock signal obtained by dividing the VCO clock by 256 is output from the LR terminal. Whether the PLL is locked or not is checked inside and the LOCKN terminal becomes 'L' when it is locked.

Normally, the PLL circuit synchronizes with the DAIF signal which is inputted to the DDIN terminal but it can also synchronize with the duty 50% word clock(fs) which is inputted to the EXTW terminal. Which signal to be synchronized with is selected by the KM0 terminal.

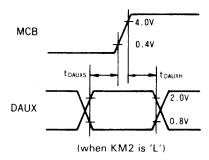

However, when accepting the data from the LSI which operates according to the clock singnals of DIR2, such as A/D converter, interfacing without using the PLL circuit can be also selected by the KM2 terminal.

KM0: Synchronized signal select

'L'=DDIN input

'H'=EXTW input

KM2; DAUX synchronization select

'L'=XI clock synchronization

'H'=PLL clock synchronization

(invalid at DIM1, 0 = H', H')

#### 3. System clocks output XI, XO, MCA, MCB, MCC, WC, SYNC, OPT, KM1, SKSY

A 256fs crystal oscillation circuit is formed at XI and XO terminals to generate the XI clock. This is used as the system clock for defaulting when the internal reset cycle or signal to be synchronized with are not inputted. The XI clock signal should be supplied constantly. As a clock master, this LSI outputs various system clock signals to the other LSIs. The clock source of the system clock is selected by the KM1 terminal.

KM1; Clock source select

L'=XI clock fixed

'H'=VCO clock automatic switching

(automatically switched to the XI clock when the PLL is not locked)

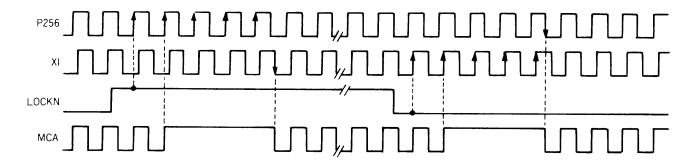

The MCA outputs 256fs clock and then MCB, MCC, WC, SYNC and OPT are outut by dividing the MCA.

When in the VCO clock automatic switching mode, continuity of the system clock is maintained except only 3-cycle stop of the MCA clock when the VI and VCO clock are switched.

In this case, however, the phase relation between the word clock which was synchronized newly and the former word clock becomes undefined. For this reason, the data reception block and the data output block are connected by asynchronous buffer of L and R one word each. Thus even when there is a phase difference between the input and output, if their sampling frequencies are the same, data can be output continuously without missing any data. Also, the system clock divider can be reset by the SKSY terminal setting, if necessary.

SKSY; System clock reset control select

When KM1='L'; The system clock divider is reset at the fall timing of the SKSY.

(When the data must be output according to the system timing)

When KM1='H'; When the SKSY is set to 'L', the system clock divider is reset by the word clock signal which is synchronized with the PLL.

(When SKSY is 'H', the continuity of the system clock is maintained.)

#### 4. Data output DOUT, DOM0, DOM1, VFL, HDLT

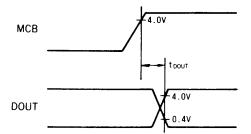

After undergoing buffering at the asynchronous buffer, the audio data is output from the DOUT terminal. The data format is selected by DOM0 and DOM1 terminals. The output timing is synchronized with the MCB. When the DAIF signal is received, the validity flag is output from the VFL terminal for each sub-frame, otherwise, the VFL is 'L'.

When the sampling frequency differs between the PLL and the system, holding or missing of the data occurs and such asynchronous buffer condition is output from the HDLT terminal.

With HDLT='H'.

when WC='L': Data is held.

when WC='H': Missing of data occurs.

#### 5. Error processing ERR

Any error that has occurred in the transmission circuit and reception stage is detected by the lock condition of the PLL and pality check. When an error has occurred, the audio data is held for L and R respectively up to 1 sample. If it is more than that, L and R are muted simultaneously. Muting is not cancelled till 4096 samples are processed without any error for both L and R channels. The ERR terminal output becomes 'H' when the PLL is unlocked and a parily error has occurred. It is possible to monitor the DAIF signal state even when an auxiliary input of the A/D or such is selected.

#### 6. Channel status and user data output CSM, EMP, FS0, FS1

The channel status and user data included in the DAIF signal are decoded and output from each of the EMP, FS0 and FS1 terminals. It is also readable through the microprocessor interface. There are two output forms and their selection is done by the CSM terminal.

#### • CSM='L'; Latch mode

The emphasis control code and sampling frequency code are latched and output for each block.

EMP; Emphasis control code output

FS0, FS1; Sampling frequency code output

| FS1 | FS0  | Sampling frequency |                      |  |  |  |

|-----|------|--------------------|----------------------|--|--|--|

| rsi | 1.20 | For Consumer use   | For Professional use |  |  |  |

| L   | L    | 44.1KHz            |                      |  |  |  |

| L   | Н    | 48 KHz             | 48 KHz               |  |  |  |

| Н   | L    |                    | 44.1KHz              |  |  |  |

| Н   | Н    | 32 KHz             | 32 KHz               |  |  |  |

#### • CSM='H'; Synchronous output mode

All bits of the channel status and user data are output continuously for each sub-frame.

EMP; Block start synchronous signal

FS1; Channel status continuous output

FS0; User data continuous output

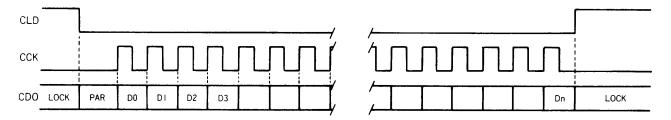

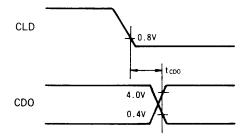

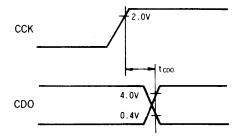

#### 7. Microprocessor interface CLD, CCK, CDO

Following information items are output from the microprocessor interface.

- Lock condition of PLL

- Parity check condition

- Head end 32 bits of channel status

- 32 bits local sample address of channel status (for professional use format only)

- Head end 32 bits of user data

(There is no specification to delimit the user data in the same way as the channel status data, the DIR2 delimits the user bits in blocks just as for the channel status bits and the first 32 bits of the user bits are output. This is not a general format; however, this is very useful when used with YM3437(DIT2), forming is done that way and the head end 32 bits are output.)

LOCK: PLL lock condition ('0'=Locked, '1'=Unlocked)

PAR : Parity error condition ('0'=No error, '1'=Parity error occurred)

D0 - Dn; Channel status and user data information

#### < Data Assignment >

|                      | D0 | D1 ~ D31                       | D32 ~ D63                 | D64 ~ D67                        | D68     | D69 ~ D100                |

|----------------------|----|--------------------------------|---------------------------|----------------------------------|---------|---------------------------|

| For Consumer use     | 0  | Channel status bits<br>1 to 31 | User data bits<br>0 to 31 |                                  |         |                           |

| For Professional use | 1  | Channel status bits<br>1 to 31 | Local sample address code | Reliability flag<br>lower 4 bits | CRC bit | User data bits<br>0 to 31 |

Note) The CRC bit becomes '1' only when the CRC check esulted in an error.

#### 8. Initial clear/test RSTN, TSTN, TST2

For the power on resetting, it is necessary that the RSTN terminal be 'L' for the XI 256 clock cycles. TSTN and TST2 terminals are for the LSI test and usually should be discornected.

#### ■ INPUT/OUTPUT FORMAT

DOODDING DOOD TO DOODDING DOOD  $oldsymbol{n}$ MSB 23 A H MSB R-CH LSB MSB 23 0 MCC(2) DOUT(1) DOUT(3) DOUT(4) SYNC PP × DOUT(2)

MCC(1), DOUT(2) MCC(2), DOUT(3)

1 H 1 H

JJHH

MCC(1), DOUT(1)

MCC(1), DOUT(4)

#### ■ ELECTRICAL CHARACTERISTICS

#### • ABSOLUTE MAXIMUM RATINGS

| Parameter             | Symbol | Rating                 | Unit |

|-----------------------|--------|------------------------|------|

| Power supply voltage  | VDD    | -0.3 ~ 7.0             | V    |

| Input voltage         | Vı     | $Vss-0.3 \sim Vdd+0.5$ | V    |

| Operation temperature | Тор    | 0 ~ +70                | °C   |

| Storage temperature   | Tstg   | $-50 \sim +125$        | °C   |

#### • RECOMMENDED OPERATION CONDITIONS

| Parameter             | Symbol | Min. | Typ. | Max. | Unit |

|-----------------------|--------|------|------|------|------|

| Power supply voltage  | VDD    | 4.75 | 5.00 | 5.25 | V    |

| Operation temperature | Top    | 0    | 25   | 70   | °C   |

#### • DC CHARACTERISTICS (Conditions; $Ta=0 \sim 70$ °C, $VDD=5.0 \pm 0.25V$ )

| Parameter                | Symbol | Condition        | Min. | Typ. | Max. | Unit |

|--------------------------|--------|------------------|------|------|------|------|

| Power supply current     | IDD    | VDD=5.0V         |      | 22   | 30   | mA   |

| Input voltage H level(1) | VIH1   | (Note 1)         | 2.0  |      |      | v    |

| Input voltage L level(1) | VIL1   | (Note 1)         |      |      | 0.8  | v    |

| Input voltage H level(2) | VIH2   | (Note 2)         | 3.6  |      |      | v    |

| Input voltage L level(2) | VIL2   | (Note 2)         |      | 1    | 1.0  | v    |

| Input leakage current    | ILK    |                  | -10  |      | 10   | μΑ   |

| Output voltage H level   | Voн    | $IOH = -50\mu A$ | 4.0  |      |      | v    |

| Output voltage L level   | Vol    | IoL=2.0mA        |      |      | 0.4  | v    |

| Input capacitance        | Cı     |                  |      |      | 10   | pF   |

| Output capacitance       | Co     |                  |      |      | 10   | pF   |

Note 1; Applicable to input terminals except XI

Note 2; Applicable to XI terminal

#### • AC CHARACTERISTICS (Conditions; $Ta=0 \sim 70^{\circ}C$ , $V_{DD}=5.0 \pm 0.25V$ )

| Parameter            | Symbol | Min.    | Typ. | Max. | Unit |

|----------------------|--------|---------|------|------|------|

| XI frequency         | fxı    | 7.37    |      | 13.5 | MHz  |

| Duty                 |        | 40      | 50   | 60   | G.   |

| XI Rise time         |        |         |      | 50   | ns   |

| Fall time            |        |         |      | 50   | ns   |

| DOUT output delay    | tDOUT  |         |      | 40   | ns   |

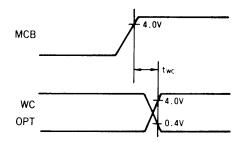

| WC, OPT output delay | twc    |         |      | 35   | ns   |

| DAUX setup time      | tauxs  | 70      |      |      | ns   |

| DAUX hold time       | tauxh  |         |      | 70   | ns   |

| CDO delay            | tcdo   |         |      | 130  | ns   |

| RSTN pulse width     |        | 256/fxi |      |      |      |

| CCK pulse width      |        | 16/fx1  |      |      |      |

#### ■ EXTERNAL DIMENSIONS

Note: The LSIs for surface mount need especial consideration on strage and soldering conditions. For detailed information, please contact your nearest agent of yamaha.

Note) Specifications of this product are subject to change for improvement without prior notice.

**YM3436D**

**MEMO**

#### IMPORTANT NOTICE

- 1. Yamaha reserves the right to make changes to its Products and to this document without notice. The information contained in this document has been carefully checked and is belived to be reliable. However, Yamaha assumes no responsibilities for inaccuracies and makes no commitment to update or to keep current the information contained in this document.

- 2. These Yamaha Products are designed only for commercial and normal industrial applications, and are not suitable for other uses, such as medical life support equipment nuclear facilities, critical care equipment or any other application the failure of which could lead to death, personal injury or environmental or property damage. Use of the Products in any such application is at the customer's sole risk and expense.

- 3. YAMAHA ASSUMES NO LIABILITY FOR INCIDENTAL, CONSEQUENTIAL OR SPE-CIAL DAMAGES OR INJURY THAT MAY RESULT FROM MISAPPLICATION OR IM-PROPER USE OR OPERATION OF THE PRODUCTS.

- 4. YAMAHA MAKES NO WARRANTY OR REPRESENTATION THAT THE PRODUCTS ARE SUBJECT TO INTELLECTUAL PROPERTY LICENSE FROM YAMAHA OR ANY THIRD PARTY, AND YAMAHA MAKES NO WARRANTY OR REPRESENTATION OF NON-INFRINGEMENT WITH RESPECT TO THE PRODUCTS. YAMAHA SPECIFI-CALLY EXCLUDES ANY LIABILITY TO THE CUSTOMER OR ANY THIRD PARTY ARISING FROM OR RELATED TO THE PRODUCTS' INFRINGEMENT OF ANY THIRD PARTY'S INTELLECTUAL PROPERTY RIGHTS, INCLUDING THE PATENT, COPYRIGHT, TRADEMARK OR TRADE SECRET RIGHTS OF ANY THIRD PARTY.

- 5. EXAMPLES OF USE DESCRIBED HEREIN ARE MERELY TO INDICATE THE CHARACTERISTICS AND PERFORMANCE OF YAMAHA PRODUCTS. YAMAHA ASSUMES NO RESPONSIBILITY FOR ANY INTELLECTUAL PROPERTY CLAIMS OR OTHER PROBLEMS THAT MAY RESULT FROM APPLICATIONS BASED ON THE EXAMPLES DESCRIBED HEREIN. YAMAHA MAKES NO WARRANTY WITH RESPECT TO THE PRODUCTS, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PAR-TICULAR USE AND TITLE.

# AGENCY -

#### YAMAHA CORPORATION

Address inquiries to:

Semiconductor Sales & Marketing Department

203. Matsunokijima, Toyooka-mura, ■ Head Office.

Iwata-gun, Shizuoka-ken, 438-0192 Tel. +81-539-62-4918 Fax. +81-539-62-5054

■ Tokyo Office 2-17-11, Takanawa, Minato-ku,

Tokyo, 108-8568

Tel. +81-3-5488-5431 Fax. +81-3-5488-5088

■ Osaka Office Namba Tsujimoto Nissei Bldg. 4F

1-13-17, Namba Naka, Naniwa-ku, Osaka City, Osaka, 556-0011

Tel. +81-6-6633-3690 Fax. +81-6-6633-3691

YAMAHA Systems Technology ■ U.S.A. Office

100 Century Center Court, San Jose,

CA 95112

Tel. +1-408-467-2300 Fax. +1-408-437-8791