# EVR3

# Electric Variable Resistance 3

#### ■Outline

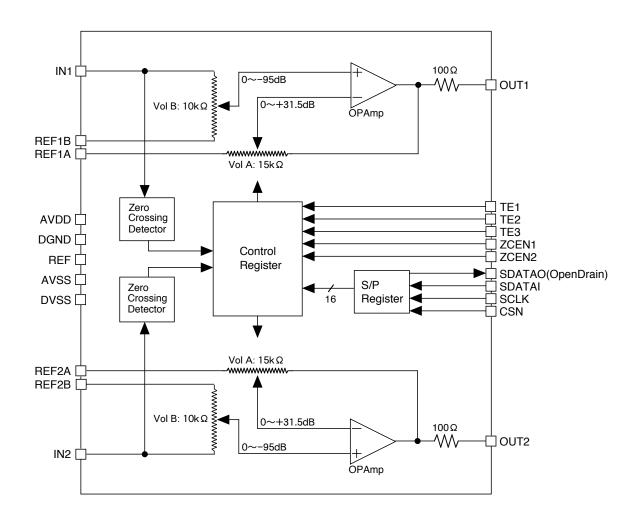

YAC526 (EVR3) is a 2ch high grade digital volume LSI for high-end audio systems.

Owing to its built-in high-quality sound operational amplifier, output with wide dynamic range and low distortion factor can be obtained.

YAC526 is able to control each channel through a serial data interface in 255 steps at 0.5dB per step, and daisy chain connection can constitute a multichannel system.

Owing to its zero-cross detection function, the device is able to suppress audible noise that may occur at a quick volume change.

#### ■ Features

- Built-in 2channel high sound quality operational amplifier.

- · Wide volume range.

- +31.5dB~ 95.0dB, MUTE (0.5dB/step, 255 steps)

- · Maximum input signal amplitude

- 4.2Vrms (±6V power supply)

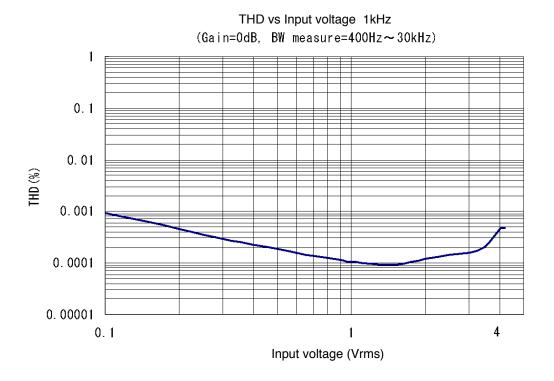

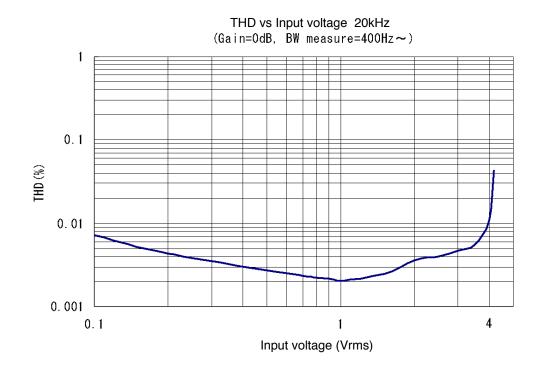

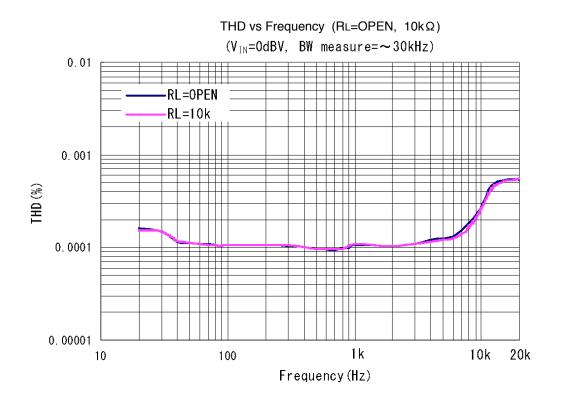

- Low distortion (THD)

- 0.0002% typ. (Input=1Vrms@1kHz, Gain=0dB)

- · Low residual noise

- 1.2 μ Vrms typ. (Gain=MUTE, IHF-A)

- · Power supply voltage

- $\pm 4.75 V \sim \pm 6.6 V$

- · Silicon gate CMOS process.

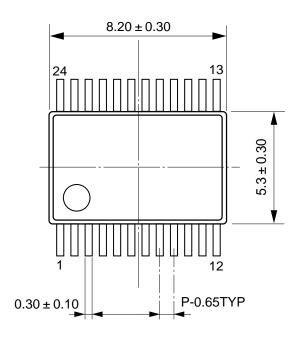

- · 24-pin plastic SSOP. The plating of pins is lead-free.(YAC526-EZ)

YAMAHA CORPORATION

YAC526 CATALOG CATALOG No.:LSI-4AC526A2 2003.10

2003.10

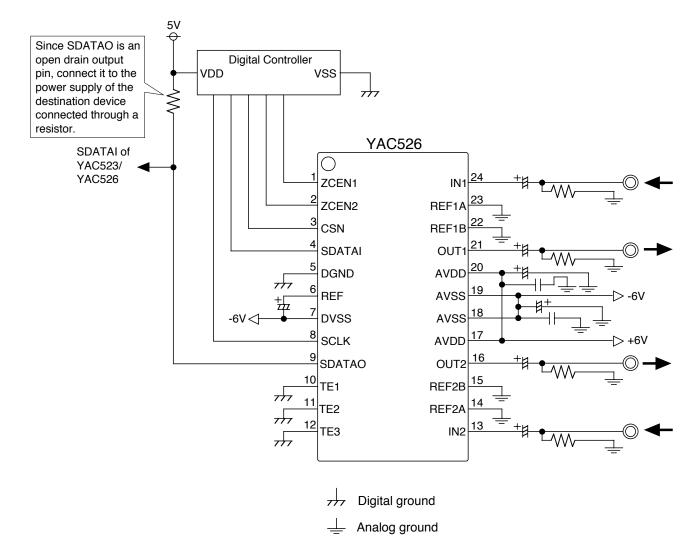

#### ■Terminal configration $\bigcirc$ ZCEN1 [ 1 24 IN1 ZCEN2 [ 2 23 REF1A 3 REF1B CSN [ 22 SDATAI [ OUT1 4 21 AVDD DGND [ 5 20 REF [ 6 19 **AVSS** 7 **AVSS** DVSS [ 18 AVDD SCLK [ 8 17 SDATAO [ 9 OUT2 16 TE1 REF2B 10 15 TE2 REF2A 11 14 TE3 [ 12 IN2 13 < 24 pin SSOP Top View >

### ■Terminal function

| No. | Name   | I/O | Function                                                                                                                                                                                                                                                     |

|-----|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | ZCEN1  | l   | Zero-cross control input 1. Select one from four types of zero-cross modes including non-zero-cross mode. When changing zero-cross modes during operation, set the system so that it changes at 1 second or more after the rise of CSN signal.               |

|     | ZCEN2  | I   | Zero-cross control input 2. Select one from four types of zero-cross modes including non-zero-cross mode. When changing zero-cross modes during operation, set the system so that it changes at 1 second or more after the rise of CSN signal.               |

| 3   | CSN    |     | Chip select input                                                                                                                                                                                                                                            |

| 4   | SDATAI | - 1 | Serial data input                                                                                                                                                                                                                                            |

| 5   |        | _   | Digital ground                                                                                                                                                                                                                                               |

| 6   | REF    | 0   | Reference voltage output for digital For attaining stabilization, connect this terminal to DVSS terminal through a capacitance of $10\mu\text{F}$ or higher (CREF). And please do not use this terminal output for the drive purpose of an external circuit. |

| 7   | DVSS   | 1   | Minus power supply for digital (-6.0V Typ.)                                                                                                                                                                                                                  |

| 8   | SCLK   |     | Serial clock input                                                                                                                                                                                                                                           |

| 9   | SDATAO | OD  | Serial data output                                                                                                                                                                                                                                           |

|     |        |     | Serial data are outputted from this terminal when CSN pin is "L" level. This terminal becomes                                                                                                                                                                |

|     |        |     | high-impedance state when CSN pin is "H". Since it is an open drain output pin, pull it up                                                                                                                                                                   |

|     |        |     | through a resistor to the power supply voltage (to be AVDD or less) of a device to be                                                                                                                                                                        |

|     |        |     | connected. Do not allow output current of 1.5mA or over.                                                                                                                                                                                                     |

| -   | TE1    | ı   | Test terminal (Pull-down) Non connection or connect to DGND terminal.                                                                                                                                                                                        |

| 11  | TE2    | ı   | Test terminal (Pull-down) Non connection or connect to DGND terminal.                                                                                                                                                                                        |

|     | TE3    | ı   | Test terminal (Pull-down) Non connection or connect to DGND terminal.                                                                                                                                                                                        |

|     | IN2    | Al  | ch2 analog input $\ $ The output impedance of input signal source is used less than $10k\Omega$ . When avoid the use of this terminal, connect to ground.                                                                                                    |

| 14  | REF2A  | ΑI  | ch2 analog reference voltage input A Connect to ground directly.                                                                                                                                                                                             |

| 15  | REF2B  | ΑI  | ch2 analog reference voltage input B Connect to ground directly.                                                                                                                                                                                             |

| 16  | OUT2   | АО  | ch2 analog output                                                                                                                                                                                                                                            |

| 17  | AVDD   | _   | Plus power supply for analog (+6.0V Typ.)                                                                                                                                                                                                                    |

| 18  | AVSS   | _   | Minus power supply for analog (-6.0V Typ.)                                                                                                                                                                                                                   |

| 19  | AVSS   | _   | Minus power supply for analog (-6.0V Typ.)                                                                                                                                                                                                                   |

| 20  | AVDD   | _   | Plus power supply for analog (+6.0V Typ.)                                                                                                                                                                                                                    |

| 21  | OUT1   | AO  | ch1 analog output                                                                                                                                                                                                                                            |

| 22  | REF1B  | ΑI  | ch1 analog reference voltage input B Connect to ground directly.                                                                                                                                                                                             |

| 23  | REF1A  | ΑI  | ch1 analog reference voltage input A Connect to ground directly.                                                                                                                                                                                             |

| 24  | IN1    | Al  | ch1 analog input $\ $ The output impedance of input signal source is used less than $10k\Omega$ . When avoid the use of this terminal, connect to ground.                                                                                                    |

Note A: analog terminal, OD: Open drain output terminal, "L" level means VIL, "H" level means VIH.

■Block diagram

### ■ Description of functions

#### Analog functions

#### · Maximum input voltage

The maximum amplitude of the input signal that is inputted to the analog input pin of YAC526 is 4.2Vrms when power supply voltage is ±6V.

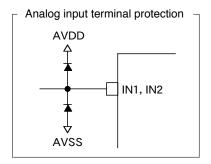

For a system to which a signal exceeding the power supply voltage (AVDD/AVSS) may be applied, use external diodes to suppress the signal to the maximum rating or less.

#### Maximum output voltage

The maximum output voltage(THD<1%) of the signal that is outputted from the analog output pin of YAC526 is 4.2Vrms when power supply voltage is  $\pm 6V$  and no load is connected. The output impedance is  $\pm 100 \,\Omega$  (typ.).

### Realization of low residual noise system

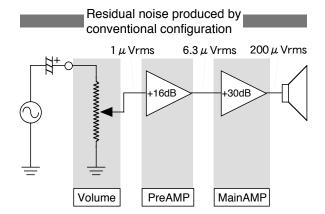

General audio amplifiers are designed to have input sensitivity of approximately 150mV, and have a gain of approximately 16dB at the preamplifier (PreAMP) section and approximately 30dB at the main amplifier section (MainAMP).

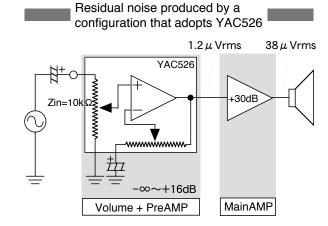

The residual noise of YAC526 (Gain=MUTE) is  $1.2 \mu$  Vrms (typ.) which is very small, and the device has positive side gain (max: 31.5dB). Therefore, by using YAC526 also as "PreAMP", systems with a very small residual noise and amplification of volume control noise can be configured.

For conventional configurations that need a "PreAMP", even if the residual noise of the volume control itself is zero, the noise that is produced at the "PreAMP" is amplified by the gain, the noise becomes very high when it is heard at the speakers.

When the input converted noise of "PreAMP" is 1  $\mu$  V, the conventional configuration produces noise of approximately 200  $\mu$  V at the speakers. For the configuration that uses YAC526, the noise is 38  $\mu$  V which is very small.

#### Digital functions

#### Serial data interface

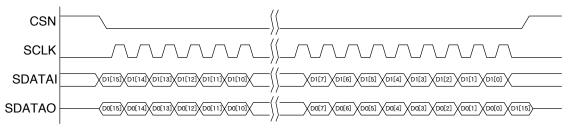

Writing of volume control data into YAC526 is performed through a serial interface. SDATAI is a serial data input pin, SCLK is a clock input pin, and CSN is a chip select pin for writing the value of volume. 16-bit serial data that is inputted from SDATAI (MSB first) is taken into YAC526 at the rising edge of SCLK when CSN terminal is at "L" level. The serial data is latched at the rising edge of CSN, and volume value of each channel is set into the register. The present volume value is outputted from SDATAO pin as serial data. With this data, the control by using daisy chain connection and verification of the present volume value can be performed easily. Note that the register value after turning the power supply on is ALL"0" (muted state) and the interface is enabled after a predetermined period (tpup) has elapsed. (Serial access is prohibited in tpup period.)

#### Assignment of volume control data

D[15: 8] : Channel1 Volume data D1[15:0] is volume data value to change. D[7: 0] : Channel2 Volume data D0[15:0] is present volume data value.

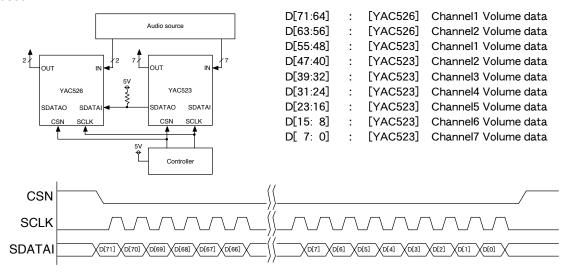

#### Daisy chain

YAC526 is extensible to a multichannel system with daisy chain connection.

For example, by connecting the device with YAC523 (7ch digital volume) through daisy chain, 8.1ch system can be attained. By connecting SDATAO pin of YAC526 (or YAC523) to SDATAI pin of YAC523 (or YAC526), YAC526 and YAC523 can be controlled simultaneously without need of a complex addressing. (It is also possible to connect multiple YAC526.)

The volume data is taken into S/P (serial / parallel) registers of each LSI by setting CSN pin to "L" for 8 clock period on all channels that are connected with daisy chain. And, by setting CSN pin to "H" after the elapse of 8 clock period on all channels, the data is written from S/P registers of all YAC526 (or YAC523) that are connected with daisy chain into the control registers simultaneously to change the volume value.

Example: Assignment of volume control data when a combination of YAC526 and YAC523 as described below is used.

#### · Volume setting

The relationship between input code and volume value is as shown in the following table. (As for an input code, the left serves as MSB.)

| Input code | Gain or attenuate(dB) |

|------------|-----------------------|

| 11111111   | MUTE                  |

| 11111110   | +31.5                 |

|            | •                     |

|            | •                     |

| 11011111   | +16.0                 |

|            | •                     |

|            | •                     |

| 10111111   | 0                     |

|            | •                     |

|            | •                     |

| 00000010   | -94.5                 |

| 0000001    | -95.0                 |

| 00000000   | MUTE                  |

The input codes ALL"0" and ALL"1" are set for mute.

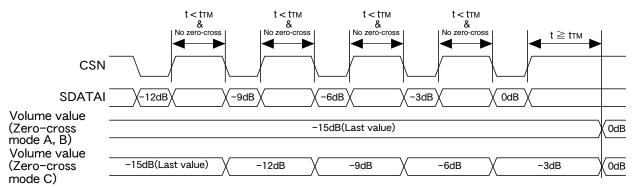

#### · Zero-cross mode

YAC526 incorporates the zero-cross detection function to suppress audible noise when the volume is changed quickly. A mode is selected from the following four modes by setting ZCEN1 and 2 pins.

| ZCEN[2:1] | Mode              | Operation                                                                                                                                                            |

|-----------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00        | Normal            | Zero-cross is not detected, and the volume value is changed immediately after the rising of CSN.                                                                     |

| 01        | Zero-cross mode A | Zero-cross is detected after the rising of CSN, or after tTM1 (20ms) passes, volume value is changed.                                                                |

| 10        | Zero-cross mode B | Zero-cross is detected after the rising of CSN, or after tTM2 (10ms) passes, volume value is changed.                                                                |

| 11        | Zero-cross mode C | When the next data is written within tTM1 (20ms) for zero-cross mode A, the changed is performed at the falling of CSN by using the volume value immediately before. |

Operation in each zero-cross mode when zero-cross is not detected

Be careful not to change the zero-cross mode during the operation of the device, or an erroneous operation may be caused. Perform change of zero-cross mode after the elapse of 1 second or more from the rising of CSN signal.

#### Power on reset

YAC526 builds in the power on reset function that resets the volume value when the power is turned on. Since a system that perform the reset by detecting the power supply voltage level, when turning on the power supply again, do it after the power supply voltage AVDD and AVSS has reduced sufficiently (to +1.0V/-1.0V or less). Moreover, although a volume register is reset at the time of a power supply injection, since shocking sound occurs in the case of power supply ON/OFF, please apply mute to the whole set.

#### ■ Electrical characteristics

#### 1. Absolute maximum rating

| Item                           | Symbol    | Min.      | Max.                                 | Unit          |

|--------------------------------|-----------|-----------|--------------------------------------|---------------|

| Power supply voltage           | AVDD-AVSS |           | 14.0                                 | V             |

| Analog input terminal voltage  | VINA      | AVss -0.6 | AVDD+0.6<br>and<br>VINA-AVSS < 14.0V | V             |

| Digital input terminal voltage | VIND      | AVss -0.3 | AVDD+0.3<br>and<br>VIND-AVSS < 14.0V | V             |

| Storage temperature            | Tstg      | -50       | 125                                  | ${\mathbb C}$ |

Note: Please use AVss and DVss with the same potential. DGND=0V

#### 2. Recommended operating conditions

| Item                                  | Symbol | Min.  | Тур.  | Max.  | Unit |

|---------------------------------------|--------|-------|-------|-------|------|

| Analog power supply voltage(Positive) | AVDD   | 4.75  | 6.00  | 6.60  | V    |

| Analog power supply voltage(Negative) | AVss   | -6.60 | -6.00 | -4.75 | V    |

| (AVss=DVss)                           | DVss   | -6.60 | -6.00 | -4.75 | V    |

| Operating ambient temperature         | Ta     | -40   |       | 85    | S    |

Note : Please use AVss and DVss with the same potential. DGND=0V

# 3. Analog characteristics (Ta=25°C, AVDD=+6.0V, AVSS=-6.0V, DVSS=-6.0V)

| Item                                                |    | Symbol | Min.  | Тур.   | Max.  | Unit   |

|-----------------------------------------------------|----|--------|-------|--------|-------|--------|

| Gain range                                          |    | Gain   | -95.0 |        | +31.5 | dB     |

| Step size                                           |    |        |       | 0.5    |       | dB     |

| Gain matching between channel (0~-40dB, 1kHz)       |    |        |       | ±0.1   |       | dB     |

| Gain matching between channel (@-80dB, 1kHz)        |    |        |       | ±0.2   |       | dB     |

| Step error (≧-80dB)                                 |    |        |       | ±0.1   |       | dB     |

| Input resistance                                    |    | Rı     |       | 10     |       | kΩ     |

| Output resistance                                   |    | Ro     |       | 100    |       | Ω      |

| Load resistance                                     |    | RL     | 5     |        |       | kΩ     |

| Input capacitance                                   |    | Cı     |       |        | 10    | pF     |

| Load capacitance                                    |    | CL     |       |        | 100   | рF     |

| Maximum input voltage (THD<1%, RL=∞)                |    | Vı     |       |        | 4.2   | Vrms   |

| Maximum output voltage (THD<1%, RL=∞)               |    | Vo     |       |        | 4.2   | Vrms   |

| Output noise voltage1 (In=GND, Vol=+16dB)           | *1 | Vn1    |       | 10.0   |       | μ Vrms |

| Output noise voltage2 (In=GND, Vol=0dB)             | *1 | Vn2    |       | 2.5    |       | μ Vrms |

| Catput Holos Voltagos (III—ai 12), Vol—Mato,        | *1 | Vn3    |       | 1.2    |       | μ Vrms |

| Total harmonic distortion (In=1Vrms, Vol=0dB, 1kHz) | *2 | THD1   |       | 0.0002 |       | %      |

|                                                     | *3 | THD2   |       | 0.0025 |       | %      |

| Inter channel isolation (Vol=0dB, 1kHz)             |    | Cs     |       | -130   |       | dB     |

Note: \*1: Input of other channels are analog ground, Band Width=IHF-A

\*2 : Input of other channels are analog ground, Band Width=400Hz~30kHz

\*3 : Input of other channels are analog ground, Band Width=400Hz~

#### 4. Power consumption

| Item                                           | Symbol | Min. | Тур. | Max. | Unit |

|------------------------------------------------|--------|------|------|------|------|

| Power consumption(AVDD=+6V, AVSS=-6V, CSN="H") | PD     |      | 150  |      | mW   |

#### 5. DC characteristics

| Item                     | Symbol | Condition | Min. | Тур. | Max.     | Unit |

|--------------------------|--------|-----------|------|------|----------|------|

| High level input voltage | VIH    |           | 2.2  |      | AVDD+0.3 | V    |

| Low level input voltage  | VIL    |           | -0.3 |      | 0.8      | V    |

| Low level output voltage | Vol    | Io= 1.5mA |      |      | 0.4      | V    |

| Input leakage current    | ILI    |           |      |      | 10       | μΑ   |

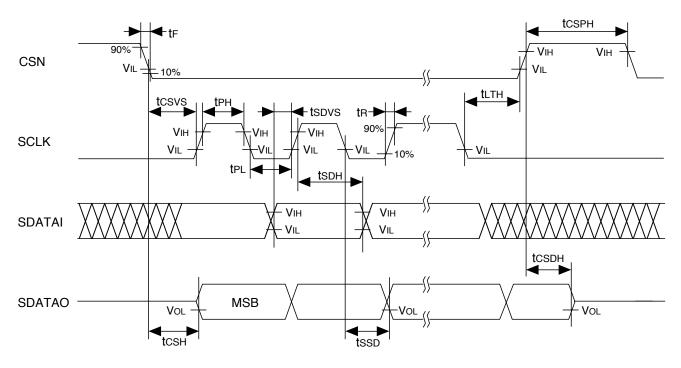

# 6. AC characteristics (CL=20pF)

| Item                                                | Symbol | Min. | Тур. | Max. | Unit |

|-----------------------------------------------------|--------|------|------|------|------|

| Serial clock frequency                              | SCLK   | 0    |      | 1.0  | MHz  |

| Serial clock pulse width high                       | tPH    | 500  |      |      | ns   |

| Serial clock pulse width Low                        | tPL    | 500  |      |      | ns   |

| SDATAI set up time                                  | tsdvs  | 200  |      |      | ns   |

| SDATAI hold time                                    | tsdh   | 200  |      |      | ns   |

| CSN pulse width High                                | tCSPH  | 1000 |      |      | ns   |

| CSN set up time                                     | tcsvs  | 500  |      |      | ns   |

| CSN hold time                                       | tLTH   | 200  |      |      | ns   |

| SDATAO data output set up time                      | tcsh   |      |      | 300  | ns   |

| SDATAO output delay time                            | tssd   |      |      | 300  | ns   |

| SDATAO output data hold time (data output stop)     | tCSDH  |      |      | 200  | ns   |

| CSN, SCLK rise time                                 | tR     |      |      | 100  | ns   |

| CSN, SCLK fall time                                 | tF     |      |      | 100  | ns   |

| Zero-cross time out (Zero-cross MODE=A, C)          | tTM1   |      | 20   |      | ms   |

| Zero-cross time out (Zero-cross MODE=B)             | tTM2   |      | 10   |      | ms   |

| Regulation time until the data writing from a power | tPUP   |      | 200  | 400  | ms   |

| supply injection (more than AVSS=90%) to LSI        |        |      |      |      |      |

| becomes effective. (CREF=10 $\mu$ F)                |        |      |      |      |      |

Fig 1 Serial port timing

# ■Example of system configuration

When there is a fear that voltage exceeding the maximum rating is applied to the analog input pins (IN1 and IN2) of YAC526, connect diodes between AVDD and AVSS as shown below to prevent application of voltage exceeding the maximum rating to the input pins.

Please make an analog domain and a digital domain into the ground side separated, respectively, and arrange YAC526 to an analog domain and the impedance to an AVSS pin should become small as much as possible. And please secure an area large enough, and a radiation noise should fully be stopped and an analog ground and a digital ground also make it.

Control signals, such as serial interface, should wire a digital ground side collectively. In order to prevent interference with a control signal and an analog signal, be careful for an analog signal and a digital signal not to cross or not to adjoin.

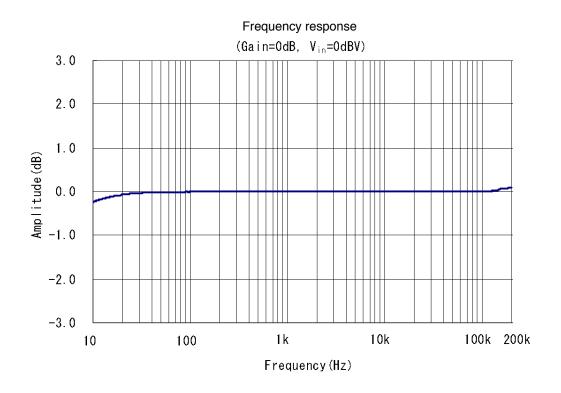

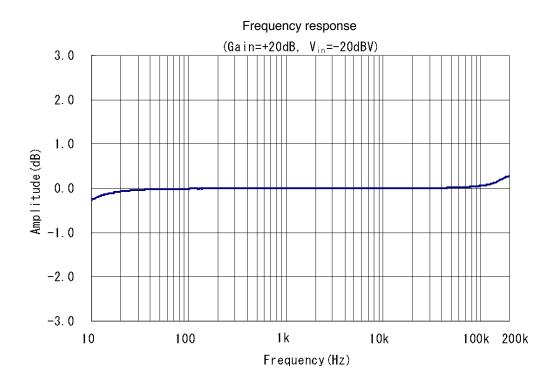

# ■Typical analog characteristic

As long as there is no description especially, it is Ta=+25 , AVDD=+6V, AVSS=-6V, DVSS=-6V, RL=10k , CL=100pF.

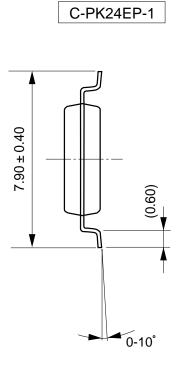

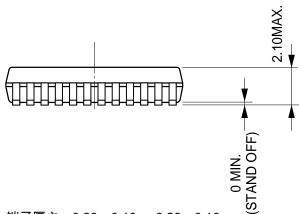

# ■ External dimensions of package

端子厚さ:0.20±0.10 or 0.22±0.10 (LEAD THICKNESS)

> カッコ内の寸法値は参考値とする。 モールド外形寸法はバリを含まない。 単位(UNIT):mm (millimeters)

The figure in the parenthesis ( ) should be used as a reference. Plastic body dimensions do not include burr of resin. UNIT: mm

注)表面実装LSIは保管条件及び、半田付けについての特別な配慮が必要です。 詳しくはヤマハ代理店までお問い合わせ下さい。

Note: The storage and soldering of LSIs for surface mounting need special consideration. For detailed information, please contact your local Yamaha agent.

#### IMPORTANT NOTICE

- 1. Yamaha reserves the right to make changes to its Products and to this document without notice. The information contained in this document has been carefully checked and is believed to be reliable. However, Yamaha assumes no responsibilities for inaccuracies and makes no commitment to update or to keep current the information contained in this document.

- 2. These Yamaha Products are designed only for commercial and normal industrial applications, and are not suitable for other uses, such as medical life support equipment, nuclear facilities, critical care equipment or any other application the failure of which could lead to death, personal injury or environmental or property damage. Use of the Products in any such application is at the customer's sole risk and expense.

- 3. YAMAHA ASSUMES NO LIABILITY FOR INCIDENTAL, CONSEQUENTIAL, OR SPECIAL DAMAGES OR INJURY THAT MAY RESULT FROM MISAPPLICATION OR IMPROPER USE OR OPERATION OF THE PRODUCTS.

- 4. YAMAHA MAKES NO WARRANTY OR REPRESENTATION THAT THE PRODUCTS ARE SUBJECT TO INTELLECTUAL PROPERTY LICENSE FROM YAMAHA OR ANY THIRD PARTY, AND YAMAHA MAKES NO WARRANTY OR REPRESENTATION OF NON-INFRANGIMENT WITH RESPECT TO THE PRODUCTS. YAMAHA SPECIALLY EXCLUDES ANY LIABILITY TO THE CUSTOMER OR ANY THIRD PARTY ARISING FROM OR RELATED TO THE PRODUCTS' INFRINGEMENT OF ANY THIRD PARTY'S INTELLECTUAL PROPERTY RIGHTS, INCLUDING THE PATENT, COPYRIGHT, TRADEMARK OR TRADE SECRET RIGHTS OF ANY THIRD PARTY.

- 5. EXAMPLES OF USE DESCRIBED HEREIN ARE MERELY TO INDICATE THE CHARACTERISTICS AND PERFORMANCE OF YAMAHA PRODUCTS. YAMAHA ASSUMES NO RESPONSIBILITY FOR ANY INTELLECTUAL PROPERTY CLAIMS OR OTHER PROBLEMS THAT MAY RESULT FROM APPLICATIONS BASED ON THE EXAMPLES DESCRIBED HEREIN. YAMAHA MAKES NO WARRANTY WITH RESPECT TO THE PRODUCTS, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR USE AND TITLE.

Note) The specifications of this product are subject to change without notice.

| ——— Agency ——— | ) |

|----------------|---|

|                |   |

|                |   |

|                |   |

|                |   |

|                |   |

|                |   |

# YAMAHA CORPORATION

# Semiconductor Sales & Marketing Department

- Head Office 203, Matsunokijima, Toyooka-mura, Iwata-gun, Shizuoka-ken, 438-0192, Japan Tel. +81-539-62-4918 Fax. +81-539-62-5054

- Tokyo Office 2-17-11, Takanawa, Minato-ku, Tokyo, 108-8568, Japan

- Tel. +81-3-5488-5431 Fax. +81-3-5488-5088

- Osaka Office 3-12-12, Minami Senba, Chuo-ku Osaka City, Osaka, 542-0081, Japan Tel. +81-6-6252-6221 Fax. +81-6-6252-6229