## **CH7028 TV Encoder**

#### **Features**

- TV encoder targets for handheld device and surveillance camera

- Supports multiple output formats such as analog TV (NTSC and PAL). Sync signals can be provided in separated or composite manner.

- Two on-chip 10-bit high speed DACs providing flexible output capabilities such as single or simultaneous CVBS and S-video outputs.

- 90/180/270 degree image rotation and vertical or horizontal flip.

- 16-Mbit SDRAM is used as a frame buffer for frame rate conversion.

- Flexible up and down scaling.

- Programmable 24-bit/18-bit/16-bit/15-bit/12-bit/8-bit digital input interface supports various RGB (RGB888, RGB666, RGB565 and etc), YCbCr (4:4:4 YCbCr, ITU656) and 2x or 3x multiplexed input. CPU interface is also supported.

- Supports flexible input resolution up to 800x800 and 1024x680.

- Pixel by pixel brightness, contrast, hue and saturation adjustment for each output is supported.

- Pixel by pixel horizontal position adjustment and line by line vertical position adjustment.

- TV/Monitor connection detection capability. DAC can be switched off based on detection result.

- Programmable power management.

- Flexible pixel clock frequency from graphics controller is supported. (2.3MHz –120MHz)

- Flexible input clock from crystal or oscillator is supported. (2.3MHz – 64MHz)

- Supports slave input clock mode only.

- Fully programmable through serial port.

- IO and SPC/SPD voltage supported is from 1.2V to 3.3V.

- Offered in a 64-pin LQFP package.

### **General Description**

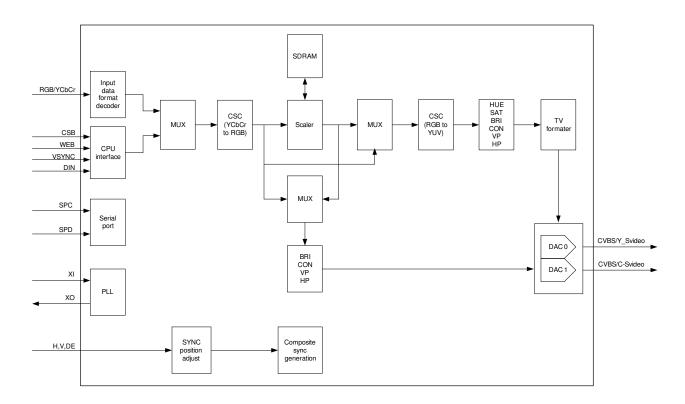

The CH7028 is a semiconductor device targeting for surveillance system and consumer product for handheld market. This device accepts digital video signals through its 24-bit input bus and generates NTSC, PAL video signal by its 10-bit DACs. In addition, CH7028 has an embedded 16-Mbit SDRAM to support the CPU interface.

CH7028 has incorporated an advanced technology that can perform real-time video rotations and frame rate conversions for incoming video stream. These complicated tasks are achieved by storing video data into the internal SDRAM and applying scaling process if required. CH7028 provides great flexibility for accepting different video data formats including RGB and YCbCr (e.g. RGB565, RGB 666, RGB 888, ITU 656).

Note: the above feature list is subject to change without notice. Please contact Chrontel for more information and current updates.

Figure 1: CH7028 block diagram

2 209-0000-092 Rev. 1.0, 03/21/2008

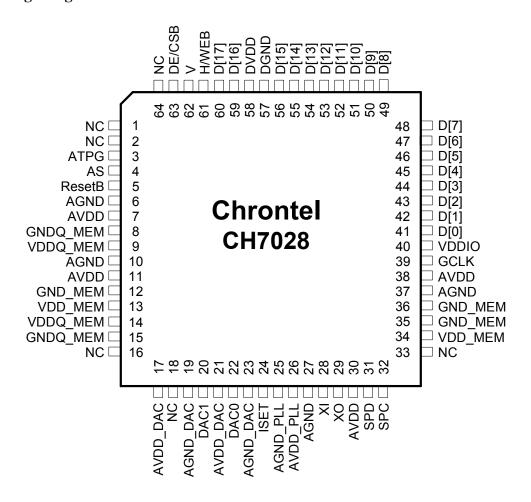

### 1.0 Pin-out

### 1.1 Package diagram

Figure 2: 64 pin LQFP package

### 1.2 Pin description

Table 1: Pin name descriptions (LQFP64 package)

| Pin #              | Type | Symbol  | Description                                                                                              |  |  |  |

|--------------------|------|---------|----------------------------------------------------------------------------------------------------------|--|--|--|

| 41 - 56<br>59 - 60 | In   | D[17:0] | Data[0] through Data[17] Inputs  These pins accept the 18 data inputs from a digital video port of a     |  |  |  |

|                    |      |         | graphics controller. The swing is defined by VDDIO.                                                      |  |  |  |

| 62                 | I/O  | V       | Vertical Sync Input / Output                                                                             |  |  |  |

|                    |      |         | When the SYO control bit is low, this pin accepts a vertical sync input                                  |  |  |  |

|                    |      |         | for use with the input data. The amplitude will be 0 to VDDIO.                                           |  |  |  |

|                    |      |         | When the SYO control bit is high, the device will output a vertical                                      |  |  |  |

|                    |      |         | sync pulse. The output is driven from the VDDIO supply.                                                  |  |  |  |

| 61                 | I/O  | H/WEB   | Horizontal Sync Input / Output                                                                           |  |  |  |

|                    |      |         | When the SYO control bit is low, this pin accepts a horizontal sync                                      |  |  |  |

|                    |      |         | input for use with the input data. The amplitude will be 0 to VDDIO.                                     |  |  |  |

|                    |      |         | When the SYO control bit is high, the device will output a horizontal                                    |  |  |  |

|                    |      |         | sync pulse. The output is driven from the VDDIO supply.                                                  |  |  |  |

|                    |      |         | It is also the WEB signal of CPU interface.                                                              |  |  |  |

| 63                 | In   | DE/CSB  | Data Input Indicator                                                                                     |  |  |  |

|                    |      |         | When the pin is high, the input data is active.                                                          |  |  |  |

|                    |      |         | When the pin is low, the input data is blanking.                                                         |  |  |  |

|                    |      |         | CSB signal input of CPU interface                                                                        |  |  |  |

|                    |      |         | The amplitude will be 0 to VDDIO.                                                                        |  |  |  |

| 4                  | In   | AS      | Chip address select                                                                                      |  |  |  |

|                    |      |         | 0: 76h                                                                                                   |  |  |  |

| 3                  | T    | ATPG    | 1: 75h                                                                                                   |  |  |  |

| 3                  | In   | AIPG    | ATPG Enable (Internally pull-down) This pin should be left open or pulled low with a 10k resistor in the |  |  |  |

|                    |      |         | application. This pin configures the pre-condition for scan chain and                                    |  |  |  |

|                    |      |         | boundary scan test when high. Otherwise it should be low. Voltage                                        |  |  |  |

|                    |      |         | level is 0 to 3.3V.                                                                                      |  |  |  |

| 5                  | In   | ResetB  | Reset * Input                                                                                            |  |  |  |

|                    |      |         | When this pin is low, the device is held in the power-on reset                                           |  |  |  |

|                    |      |         | condition. When this pin is high, reset is controlled through the serial                                 |  |  |  |

|                    |      |         | port.                                                                                                    |  |  |  |

| 31                 | I/O  | SPD     | Serial Port Data Input / Output                                                                          |  |  |  |

|                    |      |         | This pin functions as the bi-directional data pin of the serial port.                                    |  |  |  |

|                    |      |         | External pull-up resister is required.                                                                   |  |  |  |

| 32                 | In   | SPC     | Serial Port Clock Input                                                                                  |  |  |  |

|                    |      |         | This pin functions as the clock pin of the serial port. External pull-up                                 |  |  |  |

| 22                 | 0.4  | DAGO    | resister is required.                                                                                    |  |  |  |

| 22                 | Out  | DAC0    | CVBS or S-video output                                                                                   |  |  |  |

| 20                 | Out  | DAC1    | Full swing is up to 1.3v  CVBS or S-video output                                                         |  |  |  |

| 20                 | Out  | DACI    | Full swing is up to 1.3v                                                                                 |  |  |  |

| 24                 | In   | ISET    | Current Set Resistor Input                                                                               |  |  |  |

| 47                 | 111  | 1011    | This pin sets the DAC current. A 1.2k ohm, 1% tolerance resistor                                         |  |  |  |

|                    |      |         | should be connected between this pin and AGND_DAC using short                                            |  |  |  |

|                    |      |         | and wide traces.                                                                                         |  |  |  |

| 28                 | In   | XI      | Crystal Input / External Reference Input                                                                 |  |  |  |

|                    |      |         | For master mode and some situation of the slave mode, a parallel                                         |  |  |  |

|                    |      |         | resonance crystal (± 20 ppm) should be attached between this pin and                                     |  |  |  |

|                    |      |         | XO. However, an external 3.3V CMOS compatible clock can drive the                                        |  |  |  |

|                    |      |         | XI/FIN input.                                                                                            |  |  |  |

4 209-0000-092 Rev. 1.0, 03/21/2008

| Pin#       | Type  | Symbol   | Description                                                              |  |

|------------|-------|----------|--------------------------------------------------------------------------|--|

| 29         | Out   | XO       | Crystal Output                                                           |  |

|            |       |          | For master mode and some situation of the slave mode, a parallel         |  |

|            |       |          | resonance crystal (± 20 ppm) should be attached between this pin and     |  |

|            |       |          | XI / FIN. However, if an external CMOS clock is attached to XI/FIN,      |  |

|            |       |          | XO should be left open.                                                  |  |

| 39         | In    | GCLK     | External Clock Inputs                                                    |  |

|            |       |          | The input is the clock signal input to the device for use with the H, V, |  |

|            |       |          | DE and D[17:0] data.                                                     |  |

| 40         | Power | VDDIO    | IO supply voltage (1.2-3.3V).                                            |  |

| 58         | Power | DVDD     | Digital supply voltage (1.8V)                                            |  |

| 7,11,30,38 | Power | AVDD     | Analog supply voltage                                                    |  |

| 26         | Power | AVDD_PLL | PLL supply voltage                                                       |  |

| 17,21      | Power | AVDD_DAC | DAC power supply                                                         |  |

| 9,14       | Power | VDDQ_MEM | SDRAM output buffer supply voltage                                       |  |

| 13,34      | Power | VDD_MEM  | SDRAM device supply voltage                                              |  |

| 57         | Power | DGND     | Digital supply ground                                                    |  |

| 6,10,27,37 | Power | AGND     | Analog supply ground                                                     |  |

| 25         | Power | AGND_PLL | PLL supply ground                                                        |  |

| 19,23      | Power | AGND_DAC | DAC supply ground                                                        |  |

| 8,15       | Power | GNDQ_MEM | SDRAM output buffer supply ground                                        |  |

| 12,35,36   | Power | GND_MEM  | SDRAM device supply ground                                               |  |

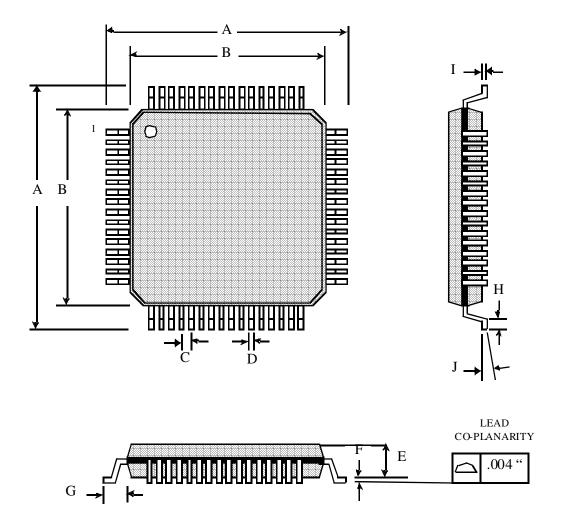

### 2.0 Package Dimensions

Figure 3: 64 Pin LQFP Package

### **Table of Dimensions**

| No. of Leads |         | SYMBOL |    |      |      |      |      |      |      |      |            |

|--------------|---------|--------|----|------|------|------|------|------|------|------|------------|

| 64 (10 X     | (10 mm) | A      | В  | С    | D    | E    | F    | G    | Н    | I    | J          |

| Milli-       | MIN     | 12     | 10 | 0.50 | 0.17 | 1.35 | 0.05 | 1.00 | 0.45 | 0.09 | <b>0</b> ° |

| meters       | MAX     | 12     | 10 | 0.50 | 0.27 | 1.45 | 0.15 | 1.00 | 0.75 | 0.20 | <b>7</b> ° |

### **Notes:**

- 1. Conforms to JEDEC standard JESD-30 MS-026D.

- 2. Dimension B: Top Package body size may be smaller than bottom package size by as much as 0.15 mm.

- 3. Dimension B does not include allowable mold protrusions up to 0.25 mm per side.

6 209-0000-092 Rev. 1.0, 03/21/2008

### **Disclaimer**

This document provides technical information for the user. Chrontel reserves the right to make changes at any time without notice to improve and supply the best possible product and is not responsible and does not assume any liability for misapplication or use outside the limits specified in this document. We provide no warranty for the use of our products and assume no liability for errors contained in this document. The customer should make sure that they have the most recent data sheet version. Customers should take appropriate action to ensure their use of the products does not infringe upon any patents. Chrontel, Inc. respects valid patent rights of third parties and does not infringe upon or assist others to infringe upon such rights.

Chrontel PRODUCTS ARE NOT AUTHORIZED FOR AND SHOULD NOT BE USED WITHIN LIFE SUPPORT SYSTEMS OR NUCLEAR FACILITY APPLICATIONS WITHOUT THE SPECIFIC WRITTEN CONSENT OF Chrontel. Life support systems are those intended to support or sustain life and whose failure to perform when used as directed can reasonably expect to result in personal injury or death.

| ORDERING INFORMATION |                                    |                    |                             |  |  |  |  |

|----------------------|------------------------------------|--------------------|-----------------------------|--|--|--|--|

| Part Number          | Package Type                       | Copy<br>Protection | Operating Temperature Range |  |  |  |  |

| CH7028B-TF           | 64LQFP, Lead-free                  | None               | Commercial : -20 to 70°C    |  |  |  |  |

| CH7028B-TF-TR        | 64LQFP, Lead-free,<br>Tape & Reel. | None               | Commercial : -20 to 70°C    |  |  |  |  |

# **Chrontel**

2210 O'Toole Avenue, Suite 100, San Jose, CA 95131-1326 Tel: (408) 383-9328

Fax: (408) 383-9338 www.chrontel.com E-mail: sales@chrontel.com

©2008 Chrontel, Inc. All Rights Reserved. Printed in the U.S.A.

209-0000-092 Rev. 1.0, 03/21/2008 7