### 10/100BASE 3-in-1 Local CPU Bus Fast Ethernet Controller with Embedded SRAM

#### **Features**

- Highly integrated with embedded 10/100Mbps MAC, PHY and Transceiver

- Embedded 8K \* 16 bit SRAM

- Compliant with IEEE 802.3/802.3u 100BASE-TX/FX specification

- NE2000 register level compatible instruction

- Single chip local CPU bus 10/100Mbps Fast Ethernet MAC Controller

- Support both 8 bit and 16 bit local CPU interfaces include MCS-51 series, 80186 series and MC68K series CPU

- Support both 10Mbps and 100Mbps data rate

- Support both full-duplex or half-duplex operation

- Provides an extra MII port for supporting other media. For example, Home LAN application

- Support EEPROM interface to store MAC address

- External and internal loop-back capability

Document No.: AX88796-23 / V2.3/ Sep. 12, 05

- Support Standard Print Port for printer server application

- Support upto 3/1 General Purpose In/Out pins

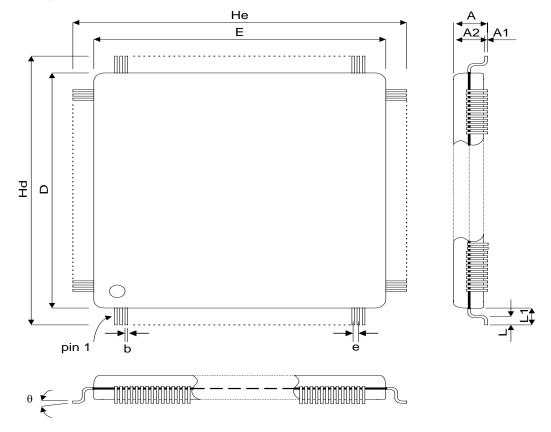

- 128-pin LQFP low profile package

- Low Power Consumption, typical under 100mA

- 0.25 Micron low power CMOS process. 25MHz Operation, Pure 3.3V operation with 5V I/O tolerance.

- Non leed free part number is AX88796 L

- RoHS compliant part number is AX88796 LF \*IEEE is a registered trademark of the Institute of Electrical and Electronic Engineers, Inc. \*All other trademarks and registered trademark are the property of their respective holders.

#### **Product description**

The AX88796 Fast Ethernet Controller is a high performance and highly integrated local CPU bus Ethernet Controller with embedded 10/100Mbps PHY/Transceiver and 8K\*16 bit SRAM. The AX88796 supports both 8 bit and 16 bit local CPU interfaces include MCS-51 series, 80186 series, MC68K series CPU and ISA bus. The AX88796 implements both 10Mbps and 100Mbps Ethernet function based on IEEE802.3 / IEEE802.3 u LAN standard. The AX88796 also provides an extra IEEE802.3u compliant media-independent interface (MII) to support other media applications. Using MII interface, Home LAN PHY type media can be supported.

As well as, the chip also provides optional Standard Print Port ( parallel port interface ), can be used for printer server device or treat as simple general I/O port. The chip also support upto 3/1 additional General Purpose In/Out pins

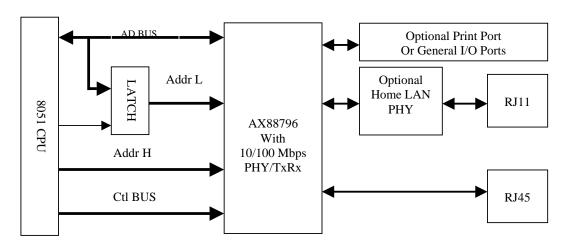

#### System Block Diagram

#### Always contact ASIX for possible updates before starting a design.

This data sheet contains new products information. ASIX ELECTRONICS reserves the rights to modify product specification without notice. No liability is assumed as a result of the use of this product. No rights under any patent accompany the sale of the product.

#### **ASIX ELECTRONICS CORPORATION**

First Released Date : July/31/2000 2F, NO.13, Industry East Rd. II, Science-based Industrial Park, Hsin-Chu City, Taiwan, R.O.C. TEL: 886-3-579-9500 FAX: 886-3-579-9558

### CONTENTS

| 1.0 INTRODUCTION                                                                                             | 5  |

|--------------------------------------------------------------------------------------------------------------|----|

| 1.1 General Description:                                                                                     |    |

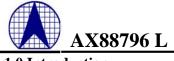

| 1.2 AX88796 Block Diagram:                                                                                   | 5  |

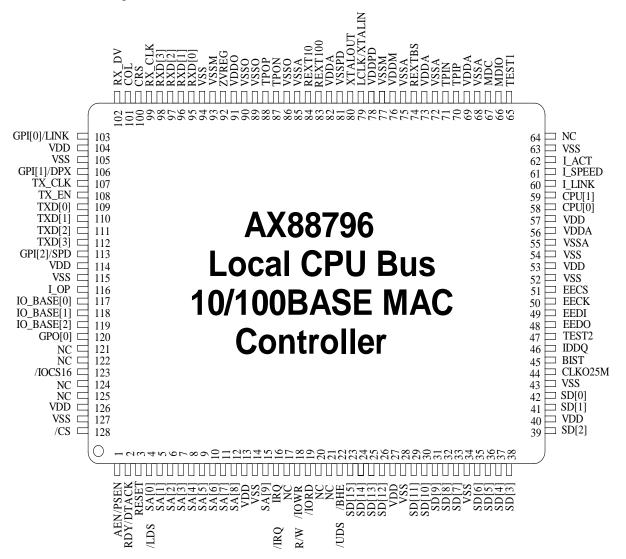

| 1.3A AX88796 Pin Connection Diagram                                                                          |    |

| 1.3B AX88796 PIN CONNECTION DIAGRAM WITH SPP PORT OPTION                                                     | 7  |

| 1.3.1 AX88796 Pin Connection Diagram for ISA Bus Mode                                                        | 8  |

| 1.3.2 AX88796 Pin Connection Diagram for 80x86 Mode                                                          |    |

| 1.3.3 AX88796 Pin Connection Diagram for MC68K Mode                                                          |    |

| 1.3.4 AX88796 Pin Connection Diagram for MCS-51 Mode                                                         | 11 |

| 2.0 SIGNAL DESCRIPTION                                                                                       |    |

| 2.1 LOCAL CPU BUS INTERFACE SIGNALS GROUP                                                                    | 12 |

| 2.2 10/100Mbps Twisted-Pair Interface pins group                                                             |    |

| 2.3 BUILT-IN PHY LED INDICATOR PINS GROUP                                                                    |    |

| 2.4 EEPROM Signals Group                                                                                     |    |

| 2.5 MII INTERFACE SIGNALS GROUP(OPTIONAL)                                                                    |    |

| 2.6 STANDARD PRINTER PORT (SPP) INTERFACE PINS GROUP (OPTIONAL)                                              |    |

| 2.7 GENERAL PURPOSE I/O PINS GROUP                                                                           |    |

| 2.8 MISCELLANEOUS PINS GROUP                                                                                 |    |

| 2.9 POWER ON CONFIGURATION SETUP SIGNALS CROSS REFERENCE TABLE                                               | 17 |

| 3.0 MEMORY AND I/O MAPPING                                                                                   |    |

| 3.1 EEPROM MEMORY MAPPING                                                                                    |    |

| 3.1 EEPROM MEMORY MAPPING                                                                                    |    |

| 3.3 SRAM MEMORY MAPPING                                                                                      |    |

|                                                                                                              |    |

| 4.0 BASIC OPERATION                                                                                          |    |

| 4.1 Receiver Filtering                                                                                       |    |

| 4.1.1 Unicast Address Match Filter                                                                           |    |

| 4.1.2 Multicast Address Match Filter                                                                         |    |

| 4.1.3 Broadcast Address Match Filter                                                                         |    |

| 4.1.4 Aggregate Address Filter with Receive Configuration Setup                                              |    |

| 4.2 BUFFER MANAGEMENT OPERATION                                                                              |    |

| 4.2.1 Packet Reception                                                                                       |    |

| 4.2.2 Packet Transmision                                                                                     |    |

| 4.2.3 Filling Packet to Transmit Buffer (Host fill data to memory)                                           |    |

| 4.2.4 Removing Packets from the Ring (Host read data from memory)<br>4.2.5 Other Useful Operations           |    |

|                                                                                                              |    |

| 5.0 REGISTERS OPERATION                                                                                      |    |

| 5.1 MAC Core Registers                                                                                       |    |

| 5.1.1 Command Register (CR) Offset 00H (Read/Write)                                                          |    |

| 5.1.2 Interrupt Status Register (ISR) Offset 07H (Read/Write)                                                |    |

| 5.1.3 Interrupt mask register (IMR) Offset 0FH (Write)                                                       |    |

| 5.1.4 Data Configuration Register (DCR) Offset 0EH (Write)                                                   |    |

| 5.1.5 Transmit Configuration Register (TCR) Offset 0DH (Write)                                               |    |

| 5.1.6 Transmit Status Register (TSR) Offset 04H (Read)                                                       |    |

| 5.1.7 Receive Configuration (RCR) Offset 0CH (Write)                                                         |    |

| 5.1.8 Receive Status Register (RSR) Offset 0CH (Read)<br>5.1.9 Inter-frame gap (IFG) Offset 16H (Read/Write) |    |

| 5.1.10 Inter-frame gap Segment 1(IFGS1) Offset 12H (Read/Write)                                              |    |

| 5.1.11 Inter-frame gap Segment 2(IFGS2) Offset 12H (Read/Write)                                              |    |

| 5.1.12 MII/EEPROM Management Register (MEMR) Offset 14H (Read/Write)                                         |    |

| 5.1.13 Test Register (TR) Offset 15H (Write)                                                                 |    |

| 5.1.14 Test Register (TR) Offset 15H (Read)                                                                  |    |

|                                                                                                              |    |

2

| AX88796 L 3-in-1 Local Bus Fast Ethernet Co                                                                      | ntroller |

|------------------------------------------------------------------------------------------------------------------|----------|

| 5.1.15 General Purpose Input Register (GPI) Offset 17H (Read)                                                    |          |

| 5.1.16 GPO and Control (GPOC) Offset 17H (Write)                                                                 | 38       |

| 5.1.17 SPP Data Port Register (SPP_DPR) Offset 18H (Read/Write)                                                  |          |

| 5.1.18 SPP Status Port Register (SPP_SPR) Offset 19H (Read)                                                      |          |

| 5.1.19 SPP Command Port Register (SPP_CPR) Offset 1AH (Read/Write)                                               |          |

| 5.2 THE EMBEDDED PHY REGISTERS                                                                                   |          |

| 5.2.1 MR0 Control Register Bit Descriptions                                                                      |          |

| 5.2.2 MR1 Status Register Bit Descriptions<br>5.2.3 MR2, MR3 Identification Registers (1 and 2) Bit Descriptions |          |

| 5.2.4 MR2, MR5 Identification Registers (1 and 2) Bit Descriptions                                               |          |

| 5.2.5 MR5 – Autonegotiation Link Partner Ability (Base Page) Register Bit Descriptions                           |          |

| 5.2.6 MR5 –Autonegotiation Link Partner(LP)Ability Register (Next Page)Bit Descriptions                          |          |

| 5.2.7 MR6 – Autonegotiation Expansion Register Bit Descriptions                                                  |          |

| 5.2.8 MR7 –Next Page Transmit Register Bit Descriptions                                                          |          |

| 5.2.9 MR16 – PCS Control Register Bit Descriptions                                                               | 45       |

| 5.2.10 MR17 –Autonegotiation Register A Bit Descriptions                                                         |          |

| 5.2.11 MR18 – Autonegotiation Register B Bit Descriptions                                                        |          |

| 5.2.12 MR20 – User Defined Register Bit Descriptions                                                             |          |

| 5.2.13 MR21 –RXER Counter Register Bit Descriptions                                                              |          |

| 5.2.14 MR28 – Device-Specific Register 1 (Status Register) Bit Descriptions                                      |          |

| 5.2.15 MR29 – Device-Specific Register 2 (100Mbps Control) Bit Descriptions                                      |          |

| 5.2.16 MR30 – Device-Specific Register 3 (10Mbps Control) Bit Descriptions                                       |          |

| 5.2.17 MR31 –Device-Specific Register 4 (Quick Status) Bit Descriptions                                          |          |

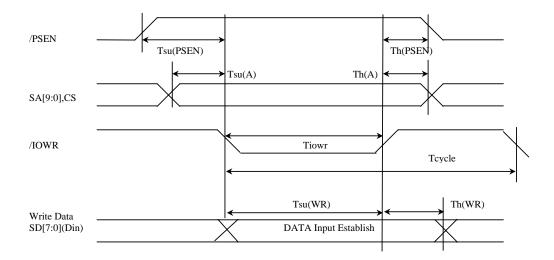

| 6.0 CPU I/O READ AND WRITE FUNCTIONS                                                                             |          |

| 6.1 ISA BUS TYPE ACCESS FUNCTIONS.                                                                               |          |

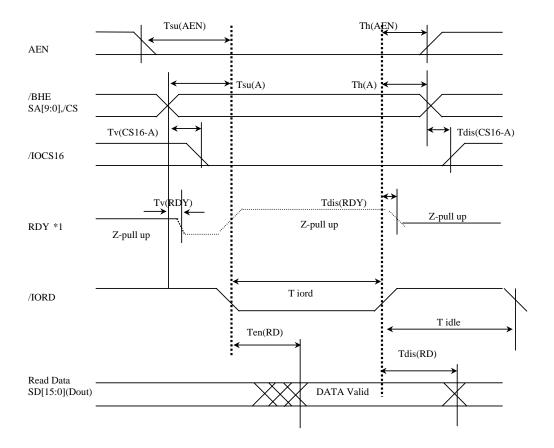

| 6.2 80186 CPU BUS TYPE ACCESS FUNCTIONS                                                                          |          |

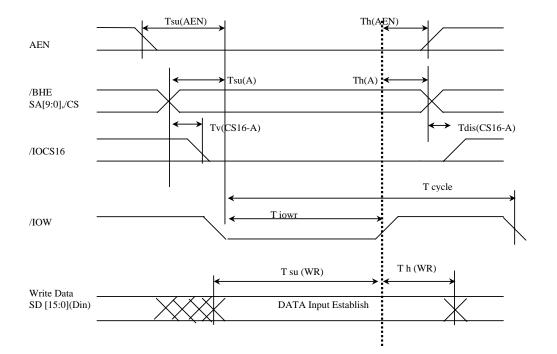

| 6.3 MC68K CPU BUS TYPE ACCESS FUNCTIONS.                                                                         |          |

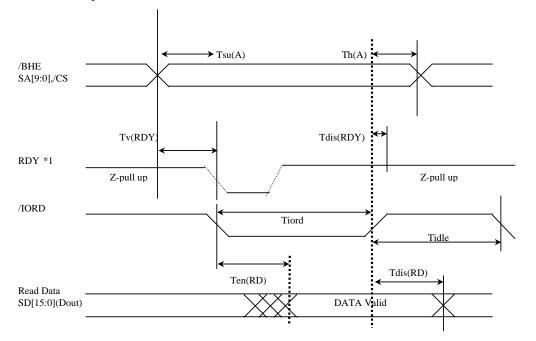

| 6.4 MCS-51 CPU BUS TYPE ACCESS FUNCTIONS.                                                                        |          |

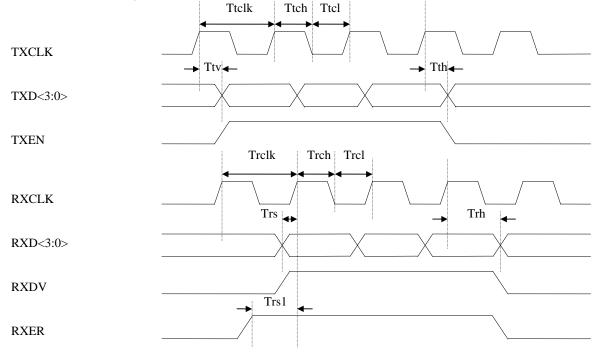

| 6.5 CPU ACCESS MII STATION MANAGEMENT FUNCTIONS                                                                  |          |

| 7.0 ELECTRICAL SPECIFICATION AND TIMINGS                                                                         |          |

| 7.1 Absolute Maximum Ratings                                                                                     |          |

| 7.2 GENERAL OPERATION CONDITIONS                                                                                 |          |

| 7.3 DC CHARACTERISTICS                                                                                           |          |

| 7.4 A.C. TIMING CHARACTERISTICS                                                                                  |          |

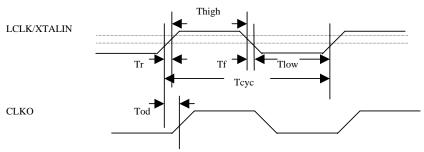

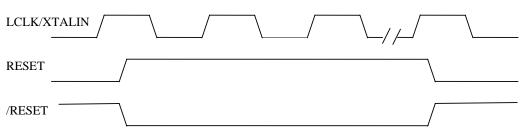

| 7.4.1 XTAL / CLOCK                                                                                               |          |

| 7.4.2 Reset Timing<br>7.4.3 ISA Bus Access Timing                                                                |          |

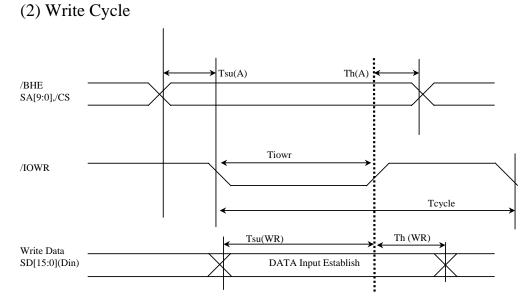

| 7.4.4 80186 Type I/O Access Timing                                                                               |          |

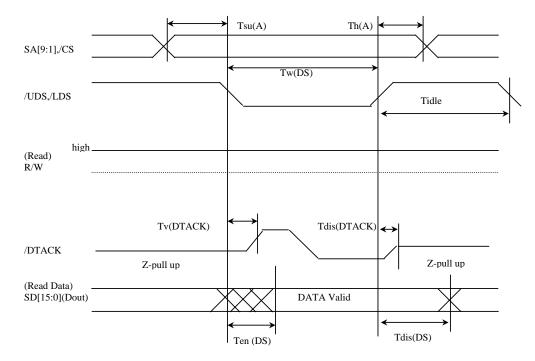

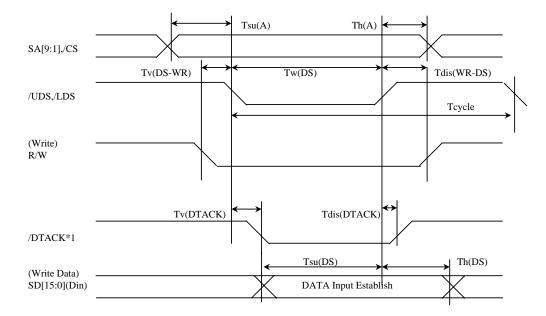

| 7.4.5 68K Type I/O Access Timing                                                                                 |          |

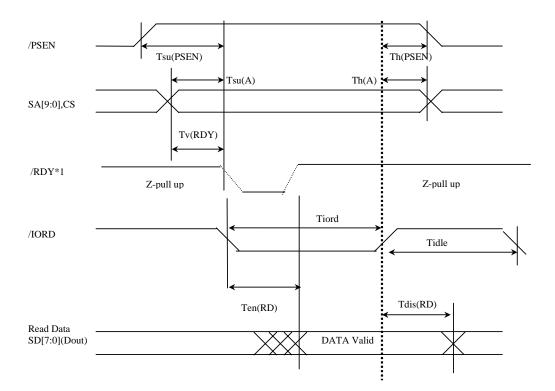

| 7.4.6 8051 Bus Access Timing                                                                                     |          |

| 7.4.7 MII Timing                                                                                                 |          |

| 8.0 PACKAGE INFORMATION                                                                                          |          |

| 9.0 ORDERING INFORMATION                                                                                         |          |

|                                                                                                                  |          |

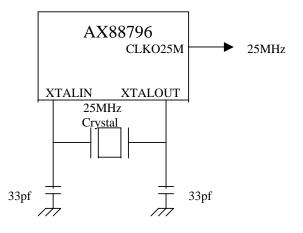

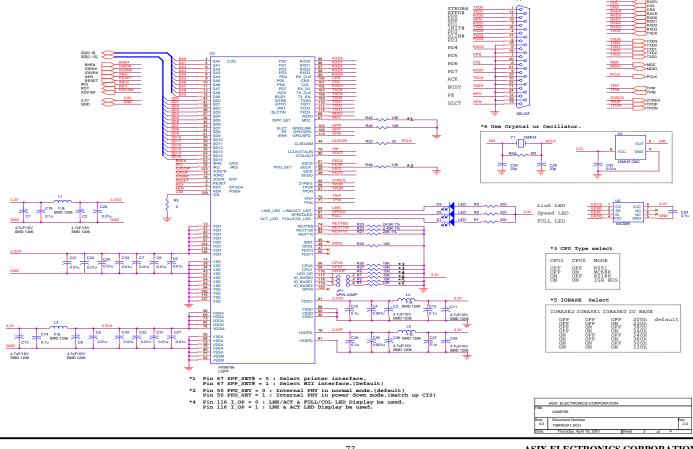

| APPENDIX A: APPLICATION NOTE 1                                                                                   |          |

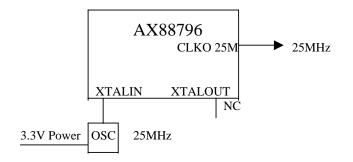

| A.1 Using Crystal 25MHz<br>A.2 Using Oscillator 25MHz                                                            |          |

| A.2 USING OSCILLATOR 25MHZ<br>APPENDIX B: POWER CONSUMPTION REFERENCE DATA                                       |          |

| ERRATA OF AX88796                                                                                                |          |

|                                                                                                                  |          |

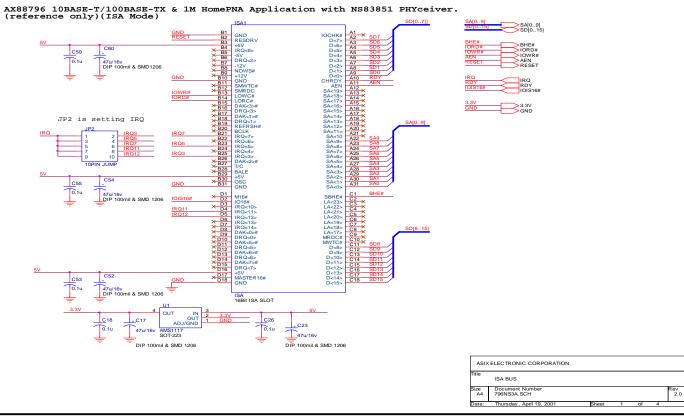

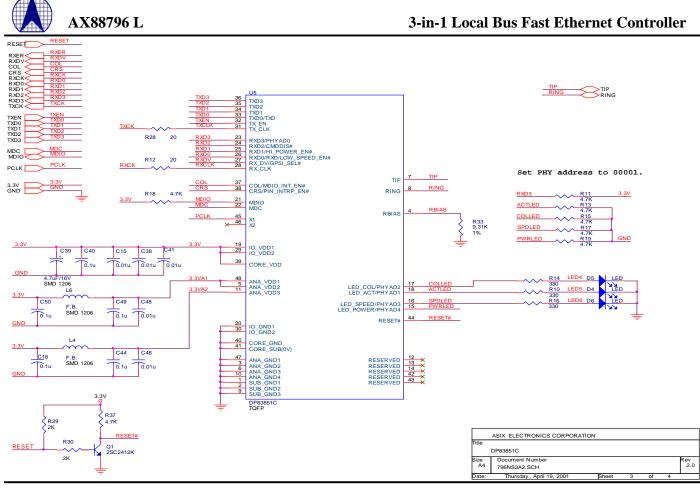

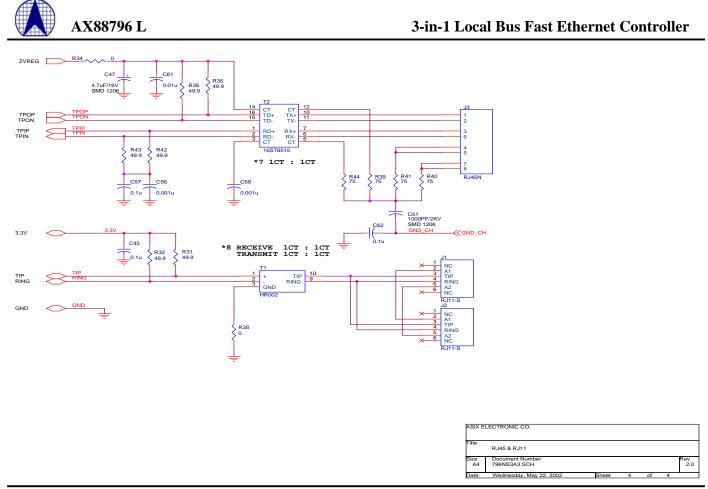

| DEMONSTRATION CIRCUIT (A): AX88796 WITH ISA BUS + HOMEPNA 1M8 PHY                                                |          |

| Date(M/D/Y)                                                                                                      | 77       |

### **FIGURES**

| Fig - 1 AX88796 Block Diagram                               | 5  |

|-------------------------------------------------------------|----|

| Fig - 2 AX88796 Pin Connection Diagram                      |    |

| FIG - 3 AX88796 PIN CONNECTION DIAGRAM WITH SPP PORT OPTION | 7  |

| FIG - 4 AX88796 PIN CONNECTION DIAGRAM FOR ISA BUS MODE     | 8  |

| FIG - 5 AX88796 PIN CONNECTION DIAGRAM FOR 80x86 MODE       | 9  |

| FIG - 6 AX88796 PIN CONNECTION DIAGRAM FOR MC68K MODE       | 10 |

| FIG - 7 AX88796 PIN CONNECTION DIAGRAM FOR MCS-51 MODE      | 11 |

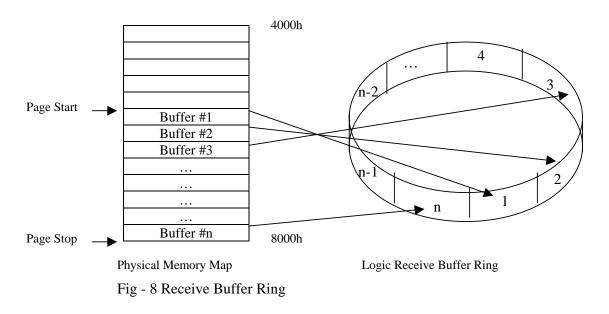

| FIG - 8 RECEIVE BUFFER RING                                 | 22 |

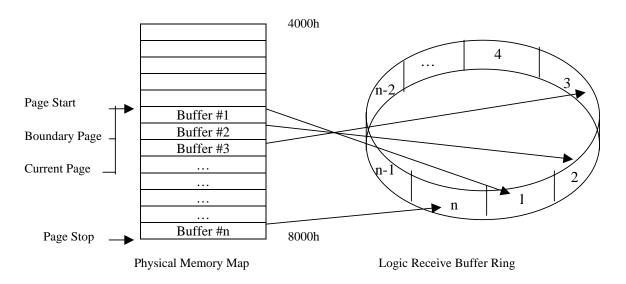

| FIG - 9 RECEIVE BUFFER RING AT INITIALIZATION               | 23 |

### **TABLES**

| TAB - 1 LOCAL CPU BUS INTERFACE SIGNALS GROUP         |    |

|-------------------------------------------------------|----|

| TAB - 2 10/100MBPS TWISTED-PAIR INTERFACES PINS GROUP |    |

| TAB - 3 BUILT-IN PHY LED INDICATOR PINS GROUP         | 13 |

| TAB - 4 EEPROM BUS INTERFACE SIGNALS GROUP            | 14 |

| TAB - 5 MII INTERFACE SIGNALS GROUP                   |    |

| TAB - 6 STANDARD PRINTER PORT INTERFACE PINS GROUP    | 15 |

| TAB - 7 GENERAL PURPOSES I/O PINS GROUP               |    |

| TAB - 8 MISCELLANEOUS PINS GROUP                      |    |

| TAB - 9 POWER ON CONFIGURATION SETUP TABLE            |    |

| TAB - 10 I/O ADDRESS MAPPING                          |    |

| TAB - 11 LOCAL MEMORY MAPPING                         |    |

| TAB - 12 PAGE 0 OF MAC CORE REGISTERS MAPPING         |    |

| TAB - 13 PAGE 1 OF MAC CORE REGISTERS MAPPING         |    |

| TAB - 14 THE EMBEDDED PHY REGISTERS                   |    |

| TAB - 15 MII MANAGEMENT FRAME FORMAT                  | 53 |

| TAB - 16 MII MANAGEMENT FRAMES- FIELD DESCRIPTION     | 53 |

**1.0 Introduction**

### **1.1 General Description:**

The AX88796 provides industrial standard NE2000 registers level compatible instruction set. Various drivers are easy acquired, maintenance and usage. No much additional effort to be paid. Software is easily port to various embedded systems with no pain and tears

The AX88796 Fast Ethernet Controller is a high performance and highly integrated local CPU bus Ethernet Controller with embedded 10/100Mbps PHY/Transceiver and 8K\*16 bit SRAM. The AX88796 supports both 8 bit and 16 bit local CPU interfaces include MCS-51 series, 80186 series, MC68K series CPU and ISA bus. The AX88796 implements both 10Mbps and 100Mbps Ethernet function based on IEEE802.3 / IEEE802.3u LAN standard. The AX88796 also provides an extra IEEE802.3u compliant media-independent interface (MII) to support other media applications. Using MII interface, Home LAN PHY type media can be supported.

As well as, the chip also provides optional Standard Print Port (parallel port interface), can be used for printer server device or treat as simple general I/O port. The chip also support upto 3/1 additional General Purpose In/Out pins

The main difference between AX88796 and AX88195 are : 1) Embedded packet buffer memory 2) Built-in 10/100Mbps PHY/Transceiver 3) Replace memory I/F with PHY/Transceiver I/F. 4) Canceling SAX address decoding. 5) Fix interrupt status can't always clean up problem of AX88195. 6) Add upto 3/1 general Purpose In/Out pins.

AX88796 use 128-pin LQFP low profile package, 25MHz operation, and single 3.3V operation with 5V I/O tolerance. The ultra low power consumption is an outstanding feature and enlarges the application field. It is suitable for some power consumption sensitive product like small size embedded products, PDA (Personal Digital Assistant) and Palm size computer ...etc.

### 1.2 AX88796 Block Diagram:

Fig - 1 AX88796 Block Diagram

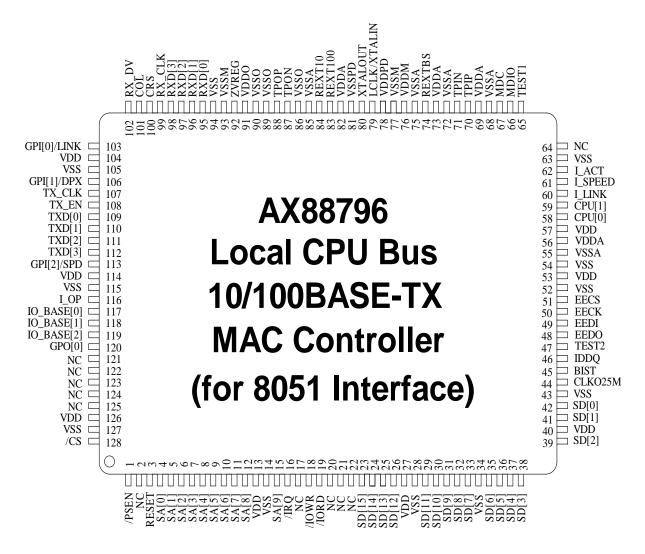

### 1.3a AX88796 Pin Connection Diagram

The AX88796 is housed in the 128-pin plastic light quad flat pack. Fig - 2 shows the AX88796 pin connection diagram.

Fig - 2 AX88796 Pin Connection Diagram

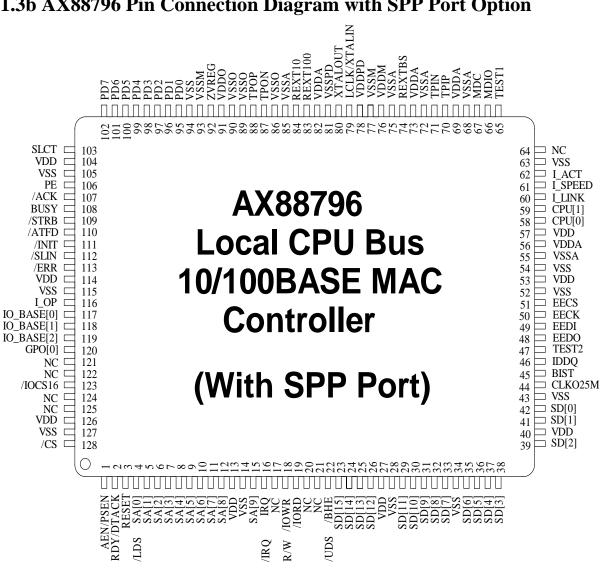

### 1.3b AX88796 Pin Connection Diagram with SPP Port Option

Fig - 3 AX88796 Pin Connection Diagram with SPP Port Option

7

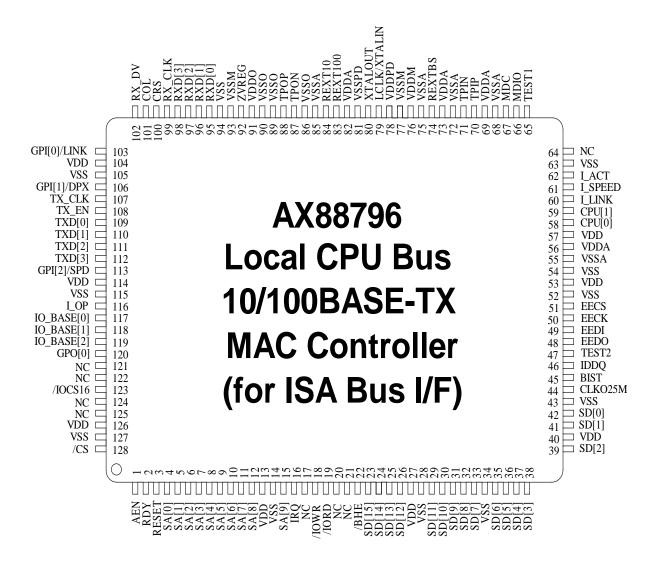

#### 1.3.1 AX88796 Pin Connection Diagram for ISA Bus Mode

Fig - 4 AX88796 Pin Connection Diagram for ISA Bus Mode

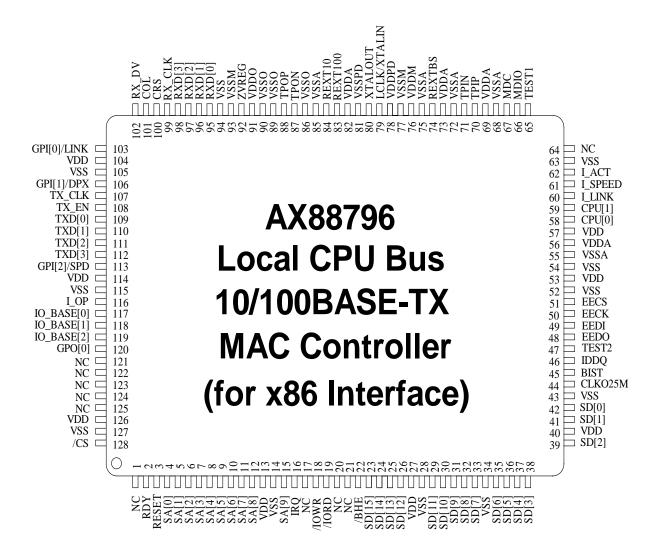

#### 1.3.2 AX88796 Pin Connection Diagram for 80x86 Mode

Fig - 5 AX88796 Pin Connection Diagram for 80x86 Mode

9

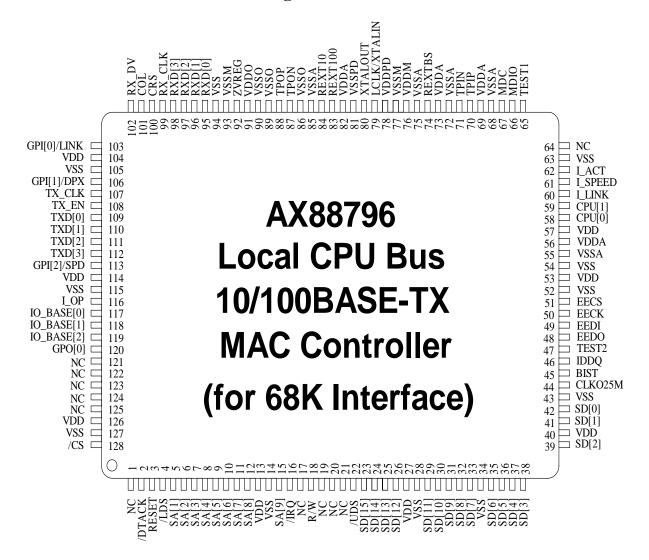

#### 1.3.3 AX88796 Pin Connection Diagram for MC68K Mode

Fig - 6 AX88796 Pin Connection Diagram for MC68K Mode

### 1.3.4 AX88796 Pin Connection Diagram for MCS-51 Mode

Fig - 7 AX88796 Pin Connection Diagram for MCS-51 Mode

#### **2.0 Signal Description**

The following terms describe the AX88796 pin-out: All pin names with the "/" suffix are asserted low. The following abbreviations are used in following Tables.

| Ι   | Input        | PU | Internal Pull Up(200K)  |

|-----|--------------|----|-------------------------|

| 0   | Output       | PD | Internal Pull Down(50K) |

| I/O | Input/Output | Р  | Power Pin               |

| TRI | TRI-state    |    |                         |

### 2.1 Local CPU Bus Interface Signals Group

| SIGNAL    | TYPE   | PIN NO.  | DESCRIPTION                                                              |

|-----------|--------|----------|--------------------------------------------------------------------------|

| SA[9:1],  | Ι      | 15,      | System Address : Signals SA[9:0] are address bus input lines, which      |

| SA[0]/LDS |        | 12 - 4   | lower I/O spaces on chip. SA[0] also means Lower Data Strobe             |

|           |        |          | (/LDS) active low signal in 68K application mode.                        |

| /BHE      | I/PU   | 22       | Bus High Enable or Upper Data Strobe : Bus High Enable is active         |

| or        |        |          | low signal in some 16-bit application mode, which enable high bus        |

| /UDS      |        |          | (SD[15:8]) active. The signal also name as Upper Data Strobe (/UDS)      |

|           |        |          | for 68K application mode.                                                |

| SD[15:0]  | I/O/PD | 23 - 26, | System Data Bus : Signals SD[15:0] constitute the bi-directional data    |

|           |        | 29 – 33, | bus.                                                                     |

|           |        | 35 – 39, |                                                                          |

|           |        | 41 - 42  |                                                                          |

| IREQ/IREQ | 0      | 16       | Interrupt Request : When ISA BUS or 80186 CPU mode is select.            |

|           |        |          | IREQ is asserted high to indicate the host system that the chip requires |

|           |        |          | host software service. When MC68K or MCS-51 CPU mode is select.          |

|           |        |          | /IREQ is asserted low to indicate the host system that the chip requires |

|           |        |          | host software service.                                                   |

| RDY/DTACK | TRI/PU | 2        | Ready : This signal is set low to insert wait states during Remote       |

|           |        |          | DMA transfer.                                                            |

|           |        |          | /Dtack : When Motorola CPU type is selected, the pin is active low       |

|           |        |          | inform CPU that data is accepted.                                        |

| /CS       | I/PU   | 128      | Chip Select                                                              |

|           |        |          | When the /CS signal is asserted, the chip is selected.                   |

| /IORD     | I/PU   | 19       | I/O Read :The host asserts /IORD to read data from AX88796 I/O           |

|           |        |          | space. When Motorola CPU type is select, the pin is useless.             |

| /IOWR     | I/PU   | 18       | I/O Write :The host asserts /IOWR to write data into AX88796 I/O         |

| or        |        |          | space. When Motorola CPU type is select, the pin is active high for      |

| R/W       |        |          | read operation at the same time.                                         |

| /IOCS16   | TRI/PU | 123      | I/O is 16 Bit Port : The /IOIS16 is asserted when the address at the     |

|           |        |          | range corresponds to an I/O address to which the chip responds, and      |

|           |        |          | the I/O port addressed is capable of 16-bit access.                      |

| AEN       | I/PD   | 1        | Address Enable : The signal is asserted when the address bus is          |

|           |        |          | available for DMA cycle. When negated (low), AX88796 an I/O slave        |

| or        |        |          | device may respond to addresses and I/O command.                         |

| /PSEN     |        |          | PSEN : This signal is active low for 8051 program access. For I/O        |

|           |        |          | device, AX88796, this signal is active high to access the chip. This     |

|           |        |          | signal is for 8051 bus application only.                                 |

Tab - 1 Local CPU bus interface signals group

### 2.2 10/100Mbps Twisted-Pair Interface pins group

| SIGNAL  | ТҮРЕ | PIN NO. | DESCRIPTION                                                                                                                                                                                              |

|---------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPI+    | I    | 70      | Received Data. Positive differential received 125M baud MLT3 or 10M baud Manchester data from magnetic.                                                                                                  |

| TPI-    | Ι    | 71      | Received Data. Negative differential received 125M baud MLT3 or 10M baud Manchester data from magnetic.                                                                                                  |

| TPO+    | 0    | 88      | Transmit Data. Positive differential transmit 125M baud MLT3 or 10M baud Manchester data to magnetic.                                                                                                    |

| ТРО-    | 0    | 87      | Transmit Data. Negative differential transmit 125M baud MLT3 or 10M baud Manchester data to magnetic.                                                                                                    |

| REXT10  | Ι    | 84      | Current Setting 10Mbits/s. An external resistor 20k ohm is placed from this signal to ground to set the 10Mbits/s TP driver transmit output level.                                                       |

| REXT100 | I    | 83      | Current Setting 100Mbits/s. An external resistor 2.49k ohm is placed from this signal to ground to set the 100Mbits/s TP driver transmit output level.                                                   |

| REXTBS  | Ι    | 74      | External Bias Resistor. Band Gap Reference for the Receive Channel.<br>Connect this signal to a 24.9k ohm +/- 1 percent resistor to ground. The<br>parasitic load capacitance should be less than 15 pF. |

Tab - 2 10/100Mbps Twisted-Pair Interfaces pins group

### 2.3 Built-in PHY LED indicator pins group

| SIGNAL     | TYPE | PIN NO. | DESCRIPTION                                                                   |

|------------|------|---------|-------------------------------------------------------------------------------|

| I_ACT      | 0    | 62      | Active Status : When I_OP is logic 1. If there is activity, transmit or       |

|            |      |         | receive, on the line occurred, the output will be driven low for 0.67 sec     |

| or         |      |         | and then driven high at least 0.67 sec.                                       |

| I_FULL/COL |      |         | Full-Duplex/Collision Status. When I_OP is logic 0. If this signal is         |

|            |      |         | low, it indicates full-duplex link established, and if it is high, then the   |

|            |      |         | link is in half-duplex mode. When in half-duplex and collision                |

|            |      |         | occurrence, the output will be driven low for 0.67 sec and driven high        |

|            |      |         | at least 0.67 sec. (Current sink capacity is 6mA)                             |

| I_SPEED    | 0    | 61      | Speed Status : If this signal is low, it indicates 100Mbps, and if it is      |

|            |      |         | high, then the speed is 10Mbps. (Current sink capacity is 6mA)                |

| I_LINK     | 0    | 60      | Link Status : When I_OP is logic 1. If this signal is low, it indicates       |

| Or         |      |         | link, and if it is high, then the link is fail.                               |

| I_LK/ACT   |      |         | Link Status/Active : When I_OP is logic 0. If this signal is low, it          |

|            |      |         | indicates link, and if it is high, then the link is fail. When in link status |

|            |      |         | and line activity occurrence, the output will be driven low for 0.67 sec      |

|            |      |         | and driven high at least 0.67 sec. (Current sink capacity is 6mA)             |

Tab - 3 Built-in PHY LED indicator pins group

# AX88796 L

**3-in-1 Local Bus Fast Ethernet Controller**

### **2.4 EEPROM Signals Group**

| SIGNAL | ТҮРЕ | PIN NO. | DESCRIPTION                                                   |

|--------|------|---------|---------------------------------------------------------------|

| EECS   | 0    | 51      | EEPROM Chip Select : EEPROM chip select signal.               |

| EECK   | O/PD | 50      | EEPROM Clock : Signal connected to EEPROM clock pin.          |

| EEDI   | 0    | 49      | EEPROM Data In : Signal connected to EEPROM data input pin.   |

| EEDO   | I/PU | 48      | EEPROM Data Out : Signal connected to EEPROM data output pin. |

Tab - 4 EEPROM bus interface signals group

### 2.5 MII interface signals group (Optional)

| SIGNAL   | TYPE   | PIN NO.    | DESCRIPTION                                                                                                    |

|----------|--------|------------|----------------------------------------------------------------------------------------------------------------|

| RXD[3:0] | I/PU   | 98 – 95    | Receive Data : RXD[3:0] is driven by the PHY synchronously with                                                |

|          |        |            | respect to RX_CLK.                                                                                             |

| CRS      | I/PD   | 100        | Carrier Sense : Asynchronous signal CRS is asserted by the PHY                                                 |

|          |        |            | when either the transmit or receive medium is non-idle.                                                        |

| RX_DV    | I/PD   | 102        | Receive Data Valid : RX_DV is driven by the PHY synchronously                                                  |

|          |        |            | with respect to RX_CLK. Asserted high when valid data is present on                                            |

|          |        |            | RXD [3:0].                                                                                                     |

| RX_ER    | (Omit) | No Support | Receive Error : RX_ER , is driven by PHY and synchronous to                                                    |

|          |        |            | RX_CLK, is asserted for one or more RX_CLK periods to indicate to                                              |

|          |        |            | the port that an error has detected.                                                                           |

| RX_CLK   | I/PU   | 99         | Receive Clock : RX_CLK is a continuous clock that provides the                                                 |

|          |        |            | timing reference for the transfer of the RX_DV,RXD[3:0] and                                                    |

|          |        |            | RX_ER signals from the PHY to the MII port of the repeater.                                                    |

| COL      | I/PD   | 101        | Collision : this signal is driven by PHY when collision is detected.                                           |

| TX_EN    | 0      | 108        | Transmit Enable : TX_EN is transition synchronously with respect to                                            |

|          |        |            | the rising edge of TX_CLK. TX_EN indicates that the port is                                                    |

|          | -      |            | presenting nibbles on TXD [3:0] for transmission.                                                              |

| TXD[3:0] | 0      | 112 – 109  | Transmit Data : TXD[3:0] is transition synchronously with respect to                                           |

|          |        |            | the rising edge of TX_CLK. For each TX_CLK period in which                                                     |

|          |        |            | TX_EN is asserted, TXD[3:0] are accepted for transmission by the                                               |

| TX_CLK   |        | 107        | PHY.                                                                                                           |

| IX_CLK   | I/PU   | 107        | Transmit Clock : TX_CLK is a continuous clock from PHY. It                                                     |

|          |        |            | provides the timing reference for the transfer of the TX_EN and TXD[3:0] signals from the MII port to the PHY. |

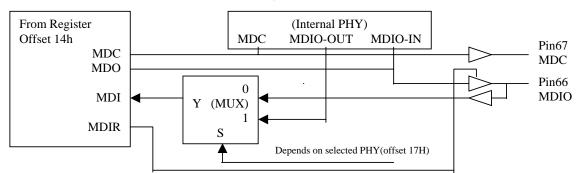

| MDC      | O/PU   | 67         | Station Management Data Clock : The timing reference for MDIO. All                                             |

| WIDC     | U/FU   | 07         | data transfers on MDIO are synchronized to the rising edge of this                                             |

|          |        |            | clock. The signal output reflects MDC register value. About MDC                                                |

|          |        |            | register, please refer to MII/EEPROM Management register bit 0.                                                |

|          |        |            | MDC clock frequency is a 2.5MHz maximum accourding to IEEE                                                     |

|          |        |            | 802.3u MII specification. Acturely, many PHYs are designed to                                                  |

|          |        |            | accept                                                                                                         |

|          |        |            | higher frequency than 2.5MHz.                                                                                  |

| MDIO     | I/O/PU | 66         | Station Management Data Input/Output :Serial data input/output                                                 |

|          |        |            | transfers from/to the PHYs. The transfer protocol has to meet the                                              |

|          |        |            | IEEE 802.3u MII specification. For more information, please refer to                                           |

|          |        |            | section 6.5 CPU Access MII Station Management functions.                                                       |

Tab - 5 MII interface signals group

### 2.6 Standard Printer Port (SPP) Interface pins group (Optional)

| SIGNAL  | TYPE   | PIN NO.   | DESCRIPTION                                                              |

|---------|--------|-----------|--------------------------------------------------------------------------|

| PD[7:5] | I/O/PD | 102 - 100 | Parallel Data : The bi-directional parallel data bus is used to transfer |

| PD[4:0] | I/O/PU | 99 - 95   | information between CPU and peripherals. Default serve as input,         |

|         |        |           | using /DOE bit of register offset x1Ah to set the direction.             |

| BUSY    | I/PU   | 108       | Busy : This is a status input from the printer, high indicating that the |

|         |        |           | printer is not ready to receive new data.                                |

| /ACK    | I/PU   | 107       | Acknowledge : A low active input from the printer indicating that it     |

|         |        |           | has received the data and is ready to accept new data.                   |

| PE      | I/PU   | 106       | Paper Empty : A status input from the printer, high indicating that the  |

|         |        |           | printer is out of paper.                                                 |

| SLCT    | I/PU   | 103       | Slect: This high active input from the printer indicating that it has    |

|         |        |           | power on.                                                                |

| /ERR    | I/PU   | 113       | Error : A low active input from the printer indicating that there is an  |

|         |        |           | error condition at the printer.                                          |

| /SLCTIN | 0      | 112       | Slect In: This active low output selects the printer.                    |

| /INIT   | 0      | 111       | Init: This signal is used to initiate the printer when low.              |

| /ATFD   | 0      | 110       | Auto Feed : This output goes low to cause the printer to automatically   |

|         |        |           | feed one line after each line is printed.                                |

| /STRB   | 0      | 109       | Strobe : A low active pulse on this output is used to strobe the print   |

|         |        |           | data into the printer.                                                   |

Tab - 6 Standard Printer Port Interface pins group

| Signal Name | Туре | Pin No. | Description                                                              |

|-------------|------|---------|--------------------------------------------------------------------------|

| GPI[2]/SPD  | I/PU | 113     | Read register offset 17h bit 6 value reflects this input value.          |

| GPI[1]/DPX  | I/PU | 106     | When MII port is selected. Read register offset 17h bit 5 value reflects |

|             |      |         | this input value.                                                        |

|             |      |         | When SPP port is selected. The pin is defined as PE.                     |

| GPI[0]/LINK | I/PU | 103     | When MII port is selected. Read register offset 17h bit 4 value reflects |

|             |      |         | this input value.                                                        |

|             |      |         | When SPP port is selected. The pin is defined as SLCT.                   |

| GPO[0]      | 0    | 120     | Default "1". The pin reflects write register offset 17h bit 0 inverted   |

|             |      |         | value.                                                                   |

### 2.7 General Purpose I/O pins group

Tab - 7 General Purposes I/O pins group

### 2.8 Miscellaneous pins group

| SIGNAL       | TYPE | PIN NO.         |               |            | D          | ESCRIPTION           |                           |

|--------------|------|-----------------|---------------|------------|------------|----------------------|---------------------------|

| LCLK/XTALIN  | Ι    | 79              | CMOS Loc      | cal Clock  | : A 251    | Mhz clock, +/- 10    | 0 PPM, 40%-60% duty       |

|              |      |                 | cycle. The    | signal no  | t suppor   | ts 5 Volts toleranc  | e.                        |

|              |      |                 |               |            |            |                      | , +/- 30 PPM can be       |

|              |      |                 |               |            |            | and XTALOUT.         |                           |

| XTALOUT      | 0    | 80              |               |            |            |                      | l, +/- 30 PPM can be      |

|              |      |                 |               |            |            |                      | a single-ended external   |

|              |      |                 | clock (LCL    | K) is con  | nnected    | to XTALIN, the ci    | rystal output pin should  |

|              |      |                 | be left float |            |            |                      |                           |

| CLKO25M      | 0    | 44              | 1             | out : This | clock is   | source from LCL      | K/XTALIN.                 |

| RESET        | I/PU | 3               | Reset :       |            |            |                      |                           |

|              |      |                 |               |            |            |                      | eset mode immediately.    |

|              |      |                 |               |            |            | AX88796 loads the    | e power on setting data.  |

| CPU[1:0]     | I/PU | 59, 58          | CPU type s    |            |            |                      |                           |

|              |      |                 | CPU[1]        | CPU[0]     |            | CPU TY               |                           |

|              |      |                 | 0             | 0          |            | ISA BUS              | 5                         |

|              |      |                 | 0             | 1          |            | 80186                |                           |

|              |      |                 | 1             | 0          |            | MC68K                |                           |

|              |      |                 | 1             | 1          | <u> </u>   | MCS-51               | (805X)                    |

| IO_BASE[2:1] | I/PU | 119, 118,       | I/O Base A    |            |            |                      |                           |

| IO_BASE[0]   | I/PD | 117             | _             | 2] IO_BA   |            | O_BASE[0]            | IO_BASE                   |

|              |      |                 | 0             |            | 0          | 0                    | 300h                      |

|              |      |                 | 0             |            | 0          | l                    | 320h                      |

|              |      |                 | 0             |            | l          | 0                    | 340h                      |

|              |      |                 | 0             |            | 1          | 1                    | 360h                      |

|              |      |                 | 1             |            | 0          | 0                    | 380h                      |

|              |      |                 | 1             |            | 0          | 1                    | 3A0h<br>200h(dafault)     |

|              |      |                 | 1             |            | 1          | 0                    | 200h(default)<br>220h     |

| I_OP         | I/PU | 116             | LED Indica    | ator Optic | on : Sele  | ction of LED displ   |                           |

| 1_01         | 210  | 110             |               |            |            |                      | LL/COL LED display        |

|              |      |                 |               | mode.      | , <u> </u> |                      |                           |

|              |      |                 | I OP = 1: I   | LINK, I    | SPEEL      | Dand I ACT LED       | display mode. (default)   |

| TEST[2:1]    | I/PD | 47, 65          | Test Pins :   |            |            | —                    | 1 2                       |

|              |      | ,               |               |            |            | mode setting purp    | ose only. Must be pull    |

|              |      |                 |               |            |            | when normal oper     |                           |

| IDDQ         | Ι    | 46              |               |            |            | l down at normal o   |                           |

| BIST         | I/PD | 45              |               |            |            |                      | p no connection when      |

|              |      |                 | normal ope    |            |            |                      |                           |

| ZVREG        | 0    | 92              | This sets th  | ne comm    | on mode    | e voltage for 10Ba   | ase-T and 100Base-TX      |

|              |      |                 | modes. It sl  | hould be   | connect    | ed to the center tap | o of the transmit side of |

|              |      |                 | the transfor  |            |            | _                    |                           |

| NC           | N/A  | 17, 20, 21,     | No Connec     | tion : for | manufa     | cturing test only.   |                           |

|              |      | 64, 122, 124,   |               |            |            |                      |                           |

|              |      | 125             |               |            |            |                      |                           |

| VDD          | Р    | 13, 27, 40,     | Power Supp    | ply:+3.3   | 3V DC.     |                      |                           |

|              |      | 53, 57, 104,    |               |            |            |                      |                           |

|              |      | 114, 126        |               |            |            |                      |                           |

| VSS          | Р    | 14, 28, 34,     |               | ply:+0V    | DC or      | Ground Power.        |                           |

|              |      | 43, 52, 54, 63, |               |            |            |                      |                           |

|              |      | 94, 105,115,    |               |            |            |                      |                           |

|              |      | 127             |               |            |            |                      |                           |

| VDDA         | Р    | 56, 69,         | Power Sup     | ply for A  | nalog Ci   | ircuit: +3.3V DC.    |                           |

|       |   | 73, 82      |                                                                       |

|-------|---|-------------|-----------------------------------------------------------------------|

| VSSA  | Р | 55, 68,     | Power Supply for Analog Circuit: +0V DC or Ground Power.              |

|       |   | 72, 75, 85, |                                                                       |

| VDDM  | Р | 76          | Powers the analog block around the transmit/receive area. This should |

|       |   |             | be connected to VDDA: +3.3V DC.                                       |

| VSSM  | Р | 77, 93      | Powers the analog block around the transmit/receive area. This should |

|       |   |             | be connected to VSSA: +0V DC or Ground Power.                         |

| VDDPD | Р | 78          | The Phase Detector (or PLL) power. This should be isolated with other |

|       |   |             | power: +3.3V DC.                                                      |

| VSSPD | Р | 81          | The Phase Detector (or PLL) power. This should be isolated with other |

|       |   |             | power: +0V DC or Ground.                                              |

| VDDO  | Р | 91          | Power Supply for Transceiver Output Driver: +3.3V DC.                 |

| VSSO  | Р | 86, 89, 90  | Power Supply for Transceiver Output Driver: +0V DC or Ground.         |

Tab - 8 Miscellaneous pins group

### 2.9 Power on configuration setup signals cross reference table

| Signal Name | Share with | Description                                              |

|-------------|------------|----------------------------------------------------------|

| /SPP_SET    | MDC        | Standard Printer Port Selection:                         |

|             |            | /SPP_SET = 0 : Standard Printer Port or GPIO is selected |

|             |            | /SPP_SET = 1 : MII port is selected (default)            |

Tab - 9 Power on Configuration Setup Table

#### **3.0 Memory and I/O Mapping**

There are three memories or I/O mapping used in AX88796.

- 1. EEPROM Memory Mapping

- 2. I/O Mapping

- 3. Local Memory Mapping

### **3.1 EEPROM Memory Mapping**

User can define by them and can access via I/O address offset 14H MII/EEPROM registers. The contants of EEPROM will not be loading to any registers automaticlly.

### **3.2 I/O Mapping**

| SYSTEM I/O OFFSET | FUNCTION          |

|-------------------|-------------------|

| 0000H             | MAC CORE REGISTER |

| 001FH             |                   |

Tab - 10 I/O Address Mapping

### **3.3 SRAM Memory Mapping**

| OFFSET | FUNCTION               |

|--------|------------------------|

| 0000H  | RESERVED               |

| 3FFFH  |                        |

| 4000H  | NE2000 COMPATABLE MODE |

| 7FFF   | 8K X 16 SRAM BUFFER    |

| 8000H  | RESERVED               |

| FFFFH  |                        |

Tab - 11 Local Memory Mapping

18

4.0 Basic Operation

### **4.1 Receiver Filtering**

The address filtering logic compares the Destination Address Field (first 6 bytes of the received packet) to the Physical address registers stored in the Address Register Array. If any one of the six bytes does not match the pre-programmed physical address, the Protocol Control Logic rejects the packet. This is for unicast address filtering. All multicast destination addresses are filtered using a hashing algorithm. (See following description.) If the multicast address indexes a bit that has been set in the filter bit array of the Multicast Address Register Array the packet is accepted, otherwise it is rejected by the Protocol Control Logic. Each destination address is also checked for all 1's which is the reserved broadcast address.

### 4.1.1 Unicast Address Match Filter

The physical address registers are used to compare the destination address of incoming packets for rejecting or accepting packets. Comparisons are performed on a byte wide basis. The bit assignment shown below relates the sequence in PAR0-PAR5 to the bit sequence of the received packet.

|      | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|------|------|------|------|------|------|------|------|------|

| PAR0 | DA7  | DA6  | DA5  | DA4  | DA3  | DA2  | DA1  | DA0  |

| PAR1 | DA15 | DA14 | DA13 | DA12 | DA11 | DA10 | DA9  | DA8  |

| PAR2 | DA23 | DA22 | DA21 | DA20 | DA19 | DA18 | DA17 | DA16 |

| PAR3 | DA31 | DA30 | DA29 | DA28 | DA27 | DA26 | DA25 | DA24 |

| PAR4 | DA39 | DA38 | DA37 | DA36 | DA35 | DA34 | DA33 | DA32 |

| PAR5 | DA47 | DA46 | DA45 | DA44 | DA43 | DA42 | DA41 | DA40 |

Note: The bit sequence of the received packet is DA0, DA1, ... DA7, DA8 ....

### 4.1.2 Multicast Address Match Filter

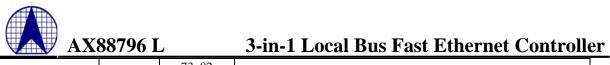

The Multicast Address Registers provide filtering of multicast addresses hashed by the CRC logic. All destination addresses are fed through the 32 bits CRC generation logic and as the last bit of the destination address enters the CRC, the 6 most significant bits of the CRC generator are latched. These 6 bits are then decoded by a 1 of 64 decode to index a unique filter bit (FB0-63) in the Multicast Address Registers. If the filter bit selected is set, the multicast packet is accepted. The system designer would use a program to determine which filter bits to set in the multicast registers. All multicast filter bits that correspond to Multicast Address Registers accepted by the node are then set to one. To accept all multicast packets all of the registers are set to all ones.

|      | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|------|------|------|------|------|------|------|------|------|

| MAR0 | FB7  | FB6  | FB5  | FB4  | FB3  | FB2  | FB1  | FB0  |

| MAR1 | FB15 | FB14 | FB13 | FB12 | FB11 | FB10 | FB9  | FB8  |

| MAR2 | FB23 | FB22 | FB21 | FB20 | FB19 | FB18 | FB17 | FB16 |

| MAR3 | FB31 | FB30 | FB29 | FB28 | FB27 | FB26 | FB25 | FB24 |

| MAR4 | FB39 | FB38 | FB37 | FB36 | FB35 | FB34 | FB33 | FB32 |

| MAR5 | FB47 | FB46 | FB45 | FB44 | FB43 | FB42 | FB41 | FB40 |

| MAR6 | FB55 | FB54 | FB53 | FB52 | FB51 | FB50 | FB49 | FB48 |

| MAR7 | FB63 | FB62 | FB61 | FB60 | FB59 | FB58 | FB57 | FB56 |

If address Y is found to hash to the value 32 (20H), then FB32 in MAR2 should be initialized to 1". This will cause the AX88796 to accept any multicast packet with the address Y.

Although the hashing algorithm does not guarantee perfect filtering of multicast address, it will perfectly filter up to 64 logical address filteres if these addresses are chosen to map into unique locations in the multicast filter.

Note: The first bit of received packet sequence is 1's stands by Multicast Address.

#### 4.1.3 Broadcast Address Match Filter

The Broadcast check logic compares the Destination Address Field (first 6 bytes of the received packet) to all 1's, that is the values are "FF FF in Hex format. If any bit of the six bytes does not equal to 1's, the Protocol Control Logic rejects the packet.

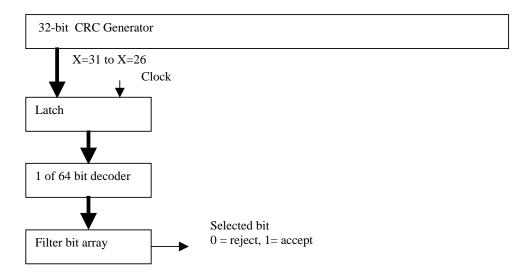

### 4.1.4 Aggregate Address Filter with Receive Configuration Setup

The final address filter decision depands on the destination address types, identified by the above 3 address match filters, and the setup of parameters of Receive Configuration Register.

| Signal | Value | Description                 |

|--------|-------|-----------------------------|

| Phy    | =1    | Unicast Address Match       |

|        | =0    | Unicast Address not Match   |

| Mul    | =1    | Multicast Address Match     |

|        | =0    | Multicast Address not Match |

| Bro    | =1    | Brocast Address Match       |

|        | =0    | Brocast Address not Match   |

| AGG    | =1    | Aggregate Address Match     |

|        | =0    | Aggregate Address not Match |

Definitions of address match filter result are as following:

The meaning of AB, AM and PRO signals, please refer to "Receive Configuration Register"

Aggregate Address Filter function will be:

Downloaded from Elcodis.com electronic components distributor

### 4.2 Buffer Management Operation

There are four buffer memory access types used in AX88796.

- 1. Packet Reception (Write data to memory from MAC)

- 2. Packet Transmision (Read data from memory to MAC)

- 3. Filling Packets to Transmit Buffer (Host fill data to memory)

- 4. Removing Packets from the Receive Buffer Ring (Host read data from memory)

The type 1 and 2 operations act as Local DMA. Type 1 does Local DMA write operation and type 2 does Local DMA read operation. The type 3 and 4 operations act as Remote DMA. Type 3 does Remote DMA write operation and type 4 does Remote DMA read operation.

### 4.2.1 Packet Reception

The Local DMA receive channel uses a Buffer Ring Structure comprised of a series of contiguous fixed length 256 byte (128 word) buffers for storage of received packets. The location of the Receive Buffer Ring is programmed in two registers, a Page Start and a Page Stop Register. Ethernet packets consist of minimum packet size (64 bytes) to maximum packet size (1522 bytes), the 256 byte buffer length provides a good compromise between short packets and longer packets to most efficiently use memory. In addition these buffers provide memory resources for storage of back-to-back packets in loaded networks. The assignment of buffers for storing packets is controlled by Buffer Management Logic in the AX88796. The Buffer Management Logic provides three basic functions: linking receive buffers for long packets, recovery of buffers when a packet is rejected, and recirculation of buffer pages that have been read by the host.

At initialization, a portion of the 16k byte (or 8k word) address space is reserved for the receiver buffer ring. Two eight bit registers, the Page Start Address Register (PSTART) and the Page Stop Address Register (PSTOP) define the physical boundaries of where the buffers reside. The AX88796 treats the list of buffers as a logical ring; whenever the DMA address reaches the Page Stop Address, the DMA is reset to the Page Start Address.

#### INITIALIZATION OF THE BUFFER RING

Two static registers and two working registers control the operation of the Buffer Ring. These are the Page Start Register, Page Stop Register (both described previously), the Current Page Register and the Boundary Pointer Register. The Current Page Register points to the first buffer used to store a packet and is used to restore the DMA for writing status to the Buffer Ring or for restoring the DMA address in the event of a Runt packet, a CRC, or Frame Alignment error. The Boundary Register points to the first packet in the Ring not yet read by the host. If the local DMA address ever reaches the Boundary, reception is aborted. The Boundary Pointer is also used to initialize the Remote DMA for removing a packet and is advanced when a packet is removed. A simple analogy to remember the function of these registers is that the Current Page Register acts as a Write Pointer and the Boundary Pointer acts as a Read Pointer.

Fig - 9 Receive Buffer Ring At Initialization

#### **BEGINNING OF RECEPTION**

When the first packet begins arriving the AX88796 and begins storing the packet at the location pointed to by the Current Page Register. An offset of 4 bytes is reserved in this first buffer to allow room for storing receive status corresponding to this packet.

#### LINKING RECEIVE BUFFER PAGES

If the length of the packet exhausts the first 256 bytes buffer, the DMA performs a forward link to the next buffer to store the remainder of the packet. For a maximal length packet the buffer logic will link six buffers to store the entire packet. Buffers cannot be skipped when linking, a packet will always be stored in contiguous buffers. Before the next buffer can be linked, the Buffer Management Logic performs two comparisons. The first comparison tests for equality between the DMA address of the next buffer and the contents of the Page Stop Register. If the buffer address equals the Page Stop Register, the buffer management logic will restore the DMA to the first buffer in the Receive Buffer Ring value programmed in the Page Start Address Register. The second comparison test for equality between the DMA address of the next buffer address and the contents of the Boundary Pointer Register. If the two values are equal the reception is aborted. The Boundary Pointer Register can be used to protect against overwriting any area in the receive buffer ring that has not yet been read. When linking buffers, buffer management will never cross this pointer, effectively avoiding any overwrites. If the buffer address does not match either the Boundary Pointer or Page Stop Address, the link to the next buffer is performed.

#### LINKING BUFFERS

Before the DMA can enter the next contiguous 256 bytes buffer, the address is checked for equality to PSTOP and to the Boundary Pointer. If neither are reached, the DMA is allowed to use the next buffer.

#### BUFFER RING OVERFLOW

If the Buffer Ring has been filled and the DMA reaches the Boundary Pointer Address, reception of the incoming packet will be aborted by the AX88796. Thus, the packets previously received and still contained in the Ring will not be destroyed. In a heavily loaded network environment the local DMA may be disabled, preventing the AX88796 from buffering packets from the network. To guarantee this will not happen, a software reset must be issued during all Receive Buffer Ring over flows (indicated by the OVW bit in the Interrupt Status Register). The following procedure is required to recover from a Receiver Buffer Ring Overflow. If this routine is not adhered to, the AX88796 may act in an unpredictable manner. It should also be noted that it is not permissible to service an overflow interrupt by continuing to empty packets from the receive buffer without implementing the prescribed overflow routine.

Note: It is necessary to define a variable in the driver, which will be called "Resend".

- 1. Read and store the value of the TXP bit in the AX88796's Command Register.

- 2. Issue the STOP command to the AX88796. This is accomplished be setting the STP bit in the AX88796's Command Register. Writing 21H to the Command Register will stop the AX88796.

- 3. Wait for at least 1.5 ms. Since the AX88796 will complete any transmission or reception that is in progress, it is necessary to time out for the maximum possible duration of an Ethernet transmission or reception. By waiting 1.5 ms this is achieved with some guard band added. Previously, it was recommended that the RST bit of the Interrupt Status Register be polled to insure that the pending transmission or reception is completed. This bit is not a reliable indicator and subsequently should be ignored.

- 4. Clear the AX88796's Remote Byte Count registers (RBCR0 and RBCR1).

- 5. Read the stored value of the TXP bit from step 1, above. If this value is a 0, set the ``Resend" variable to a 0 and jump to step 6. If this value is a 1, read the AX88796's Interrupt Status Register. If either the Packet Transmitted bit (PTX) or Transmit Error bit (TXE) is set to a 1, set the ``Resend" variable to a 0 and jump to step 6. If neither of these bits is set, place a 1 in the ``Resend" variable and jump to step 6. This step determines if there was a transmission in progress when the stop command was issued in step 2. If there was a transmission in progress when the stop command was issued in step 2. If there was a transmission in progress when the stop command was issued in step 2. If there was a transmission in progress when the stop command was issued in step 2. If there was a transmission in progress when the stop command was issued in step 2. If there was a transmission in progress when the stop command was issued in step 2. If there was a transmission in progress the AX88796's ISR is read to determine whether or not the packet was recognized by the AX88796. If neither the PTX nor TXE bit was set, then the packet will essentially be lost and retransmitted only after a time-out takes place in the upper level software. By determining that the packet was lost at the driver level, a transmit command can be reissued to the AX88796 once the overflow routine is completed (as in step 11). Also, it is possible for the AX88796 to defer indefinitely, when it is stopped on a busy network. Step 5 also alleviates this problem. Step 5 is essential and should not be omitted

from the overflow routine, in order for the AX88796 to operate correctly.

- 6. Place the AX88796 in mode 1 loopback. This can be accomplished by setting bits D2 and D1, of the Transmit Configuration Register to ``0,1".

- 7. Issue the START command to the AX88796. This can be accomplished by writing <u>22H</u> to the Command Register. This is necessary to activate the AX88796's Remote DMA channel.

- 8. Remove one or more packets from the receive bufferring.

- 9. Reset the overwrite warning (OVW, overflow) bit in the Interrupt Status Register.

- 10. Take the AX88796 out of loopback. This is done by writing the Transmit Configuration Register with the value it contains during normal operation. (Bits D2 and D1 should both be programmed to 0.)

- 11. If the ``Resend" variable is set to a 1, reset the ``Resend" variable and reissue the transmit command. This is done by writing a value of 26H to the Command Register. If the ``Resend" variable is 0, nothing needs to bedone.

#### END OF PACKET OPERATIONS

AX88796 L

At the end of the packet the AX88796 determines whether the received packet is to be accepted or rejected. It either branches to a routine to store the Buffer Header or to another routine that recovers the buffers used to store the packet.

#### SUCCESSFUL RECEPTION

If the packet is successfully received as shown, the DMA is restored to the first buffer used to store the packet (pointed to by the Current Page Register). The DMA then stores the Receive Status, a Pointer to where the next packet will be stored and the number of received bytes. Note that the remaining bytes in the last buffer are discarded and reception of the next packet begins on the next empty 256 byte buffer boundary. The Current Page Register is then initialized to the next available buffer in the Buffer Ring. (The location of the next buffer had been previously calculated and temporarily stored in an internal scratchpad register.)

#### BUFFER RECOVERY FOR REJECTED PACKETS

If the packet is a runt packet or contains CRC or Frame Alignment errors, it is rejected. The buffer management logic resets the DMA back to the first buffer page used to store the packet (pointed to by CPR), recovering all buffers that had been used to store the rejected packet. This operation will not be performed if the AX88796 is programmed to accept either runt packets or packets with CRC or Frame Alignment errors. The received CRC is always stored in buffer memory after the last byte of received data for the packet.

#### Error Recovery

If the packet is rejected as shown, the DMA is restored by the AX88796 by reprogramming the DMA starting address pointed to by the Current Page Register.

#### 4.2.2 Packet Transmision

The Local DMA Read is also used during transmission of a packet. Three registers control the DMA transfer during transmission, a Transmit Page Start Address Register (TPSR) and the Transmit Byte Count Registers (TBCR0,1). When the AX88796 receives a command to transmit the packet pointed to by these registers, buffer memory data will be moved into the FIFO as required during transmission. The AX88796 Controller will generate and append the preamble, synch and CRC fields.

TRANSMIT PACKET ASSEMBLY

The AX88796 requires a contiguous assembled packet with the format shown. The transmit byte count includes the Destination Address, Source Address, Length Field and Data. It does not include preamble and CRC. When transmitting data smaller than 46 bytes, the packet must be padded to a minimum size of 64 bytes. The programmer is responsible for adding and stripping pad bytes. The packets are placed in the buffer RAM by the system. System programs the AX88796 Core's Remote DMA to move the data from the data port to the RAM handshaking with system transfers loading the I/O data port.

The data transfer must be 16 bits (1 word) when in 16-bit mode, and 8 bits when the AX88796 Controller is set in 8-bit mode. The data width is selected by setting the WTS bit in the Data Configuration Register and setting the CPU[1:0] pins for ISA, 80186 or MC68K mode.

| Destination Address            | 6 Bytes  |  |

|--------------------------------|----------|--|

| Source Address                 | 6 Bytes  |  |

| Length / Type                  | 2 Bytes  |  |

| Data                           | 46 Bytes |  |

| (Pad if $< 46$ Bytes)          | Min.     |  |

| General Transmit Packet Format |          |  |

#### TRANSMISSION

Prior to transmission, the TPSR (Transmit Page Start Register) and TBCR0, TBCR1 (Transmit Byte Count Registers) must be initialized. To initiate transmission of the packet the TXP bit in the Command Register is set. The Transmit Status Register (TSR) is cleared and the AX88796 begins to prefetch transmit data from memory. If the Interpacket Gap (IPG) has timed out the AX88796 will begin transmission.

#### CONDITIONS REQUIRED TO BEGIN TRANSMISSION

In order to transmit a packet, the following three conditions must be met:

- 1. The Interpacket Gap Timer has timed out

- 2. At least one byte has entered the FIFO. (This indicates that the burst transfer has been started)

- 3. If a collision had been detected then before transmission the packet backoff time must have timed out.

#### COLLISION RECOVERY

During transmission, the Buffer Management logic monitors the transmit circuitry to determine if a collision has occurred. If a collision is detected, the Buffer Management logic will reset the FIFO and restore the Transmit DMA pointers for retransmission of the packet. The COL bit will be set in the TSR and the NCR (Number of Collisions Register) will be incremented. If 15 retransmissions each result in a collision the transmission will be aborted and the ABT bit in the TSR will be set.

#### Transmit Packet Assembly Format

The following diagrams describe the format for how packets must be assembled prior to transmission for different byte ordering schemes. The various formats are selected in the Data Configuration Register and setting the CPU[1:0] pins for ISA, 80186, MC68K or MCS-51 mode.

| D15 D8                | D7 D                  | 00 |

|-----------------------|-----------------------|----|

| Destination Address 1 | Destination Address 0 |    |

| Destination Address 3 | Destination Address 2 |    |

| Destination Address 5 | Destination Address 4 |    |

| Source Address 1 | Source Address 0 |

|------------------|------------------|

| Source Address 3 | Source Address 2 |

| Source Address 5 | Source Address 4 |

| Type / Length 1  | Type / Length 0  |

| Data 1           | Data 0           |

|                  |                  |

BOS = 0, WTS = 1 in Data Configuration Register. This format is used with ISA or 80186 Mode.

| D15 D8                | D7 D0                 |

|-----------------------|-----------------------|

| Destination Address 0 | Destination Address 1 |

| Destination Address 2 | Destination Address 3 |

| Destination Address 4 | Destination Address 5 |

| Source Address 0      | Source Address 1      |

| Source Address 2      | Source Address 3      |

| Source Address 4      | Source Address 5      |

| Type / Length 0       | Type / Length 1       |

| Data 0                | Data 1                |

|                       |                       |

BOS = 1, WTS = 1 in Data Configuration Register. This format is used with MC68K Mode.

| D7 |                             | D0 |

|----|-----------------------------|----|

|    | Destination Address 0 (DA0) |    |

|    | Destination Address 1 (DA1) |    |

|    | Destination Address 2 (DA2) |    |

|    | Destination Address 3 (DA3) |    |

|    | Destination Address 4 (DA4) |    |

|    | Destination Address 5 (DA5) |    |

|    | Source Address 0 (SA0)      |    |

|    | Source Address 1 (SA1)      |    |

|    | Source Address 2 (SA2)      |    |

|    | Source Address 3 (SA3)      |    |

|    | Source Address 4 (SA4)      |    |

|    | Source Address 5 (SA5)      |    |

|    | Type / Length 0             |    |

|    | Type / Length 1             |    |

|    | Data 0                      |    |

|    | Data 1                      |    |

|    |                             |    |

BOS = 0, WTS = 0 in Data Configuration Register. This format is used with ISA, 80186 or MCS-51 Mode.

Note: All examples above will result in a transmission of a packet in order of DA0 (Destination Address 0), DA1, DA2, DA3... in byte. Bits within each byte will be transmitted least significant bit first.

### 4.2.3 Filling Packet to Transmit Buffer (Host fill data to memory)

The Remote DMA channel is used to both assemble packets for transmission, and to remove received packets from the Receive Buffer Ring. It may also be used as a general purpose slave DMA channel for moving blocks

27

of data or commands between host memory and local buffer memory. There are two modes of operation, Remote Write and Remote Read Packet.

Two register pairs are used to control the Remote DMA, a Remote Start Address (RSAR0, RSAR1) and a Remote Byte Count (RBCR0, RBCR1) register pair. The Start Address Register pair points to the beginning of the block to be moved while the Byte Count Register pair is used to indicate the number of bytes to be transferred. Full handshake logic is provided to move data between local buffer memory (Embedded Memory) and a bidirectional I/O port.

#### REMOTE WRITE

A Remote Write transfer is used to move a block of data from the host into local buffer memory. The Remote DMA will read data from the I/O port and sequentially write it to local buffer memory beginning at the Remote Start Address. The DMA Address will be incremented and the Byte Counter will be decremented after each transfer. The DMA is terminated when the Remote Byte Count Register reaches a count of zero.

### 4.2.4 Removing Packets from the Ring (Host read data from memory)

REMOTE READ

A Remote Read transfer is used to move a block of data from local buffer memory to the host. The Remote DMA will sequentially read data from the local buffer memory, beginning at the Remote Start Address, and write data to the I/O port. The DMA Address will be incremented and the Byte Counter will be decremented after each transfer. The DMA is terminated when the Remote Byte Count Register reaches zero.

Packets are removed from the ring using the Remote DMA or an external device. When using the Remote DMA. The Boundary Pointer can also be moved manually by programming the Boundary Register. Care should be taken to keep the Boundary Pointer at least one buffer behind the Current Page Pointer. The following is a suggested method for maintaining the Receive Buffer Ring pointers.

- 1. At initialization, set up a software variable (next\_pkt) to indicate where the next packet will be read. At the beginning of each Remote Read DMA operation, the value of next\_pkt will be loaded into RSAR0 and RSAR1.

- 2. When initializing the AX88796 set: BNRY = PSTART CPR = PSTART + 1 Next\_pkt = PSTART + 1

- 3. After a packet is DMAed from the Receive Buffer Ring, the Next Page Pointer (second byte in AX88796 receive packet buffer header) is used to update BNRY and next\_pkt. Next\_pkt = Next Page Pointer

BNRY = Next Page Pointer - 1 If BNRY < PSTART then BNRY = PSTOP - 1

Note the size of the Receive Buffer Ring is reduced by one 256-byte buffer; this will not, however, impede the operation of the AX88796. The advantage of this scheme is that it easily differentiates between buffer full and buffer empty: it is full if BNRY = CPR; empty when BNRY = CPR-1.

#### STORAGE FORMAT FOR RECEIVED PACKETS

The following diagrams describe the format for how received packets are placed into memory by the local DMA channel. These modes are selected in the Data Configuration Register and setting the CPU[1:0] pins for ISA, 80186, MC68K or MCS-51 mode.

| D15              | D8    | D7 D0                 |

|------------------|-------|-----------------------|

| Next Packet Poi  | nter  | Receive Status        |

| Receive Byte Cor | unt 1 | Receive Byte Count 0  |

| Destination Addr | ess 1 | Destination Address 0 |

| Destination Addr | ess 3 | Destination Address 2 |

| Destination Addr | ess 5 | Destination Address 4 |

| Source Address   | s 1   | Source Address 0      |

| Source Address   | s 3   | Source Address 2      |

| Source Address   | s 5   | Source Address 4      |

| Type / Length    | 1     | Type / Length 0       |

| Data 1           |       | Data 0                |

|                  |       |                       |

BOS = 0, WTS = 1 in Data Configuration Register. This format is used with ISA or 80186 Mode.

| D15              | D8    | D7          | D0          |

|------------------|-------|-------------|-------------|

| Receive Statu    | S     | Next Pac    | ket Pointer |

| Receive Byte Co  | unt 0 | Receive B   | yte Count 1 |

| Destination Addr | ess 0 | Destination | n Address 1 |

| Destination Addr | ess 2 | Destination | n Address 3 |

| Destination Addr | ess 4 | Destination | n Address 5 |

| Source Address   | s 0   | Source A    | Address 1   |

| Source Address   | s 2   | Source A    | Address 3   |

| Source Address   | s 4   | Source A    | Address 5   |

| Type / Length    | 0     | Type / ]    | Length 1    |

| Data 0           |       | Da          | ta 1        |

|                  |       |             |             |

BOS = 1, WTS = 1 in Data Configuration Register. This format is used with MC68K Mode.

| D7 |                       | D0 |

|----|-----------------------|----|

|    | Receive Status        |    |

|    | Next Packet Pointer   |    |

|    | Receive Byte Count 0  |    |

|    | Receive Byte Count 1  |    |

|    | Destination Address 0 |    |

|    | Destination Address 1 |    |