# IA82527 Serial Communications Controller—CAN Protocol

# **Data Sheet**

Copyright © 2009 by Innovasic Semiconductor, Inc.

Published by Innovasic Semiconductor, Inc. 3737 Princeton Drive NE, Suite 130, Albuquerque, NM 87107

MILES™ is a trademark Innovasic Semiconductor, Inc. Intel® is a registered trademark of Intel Corporation

## **TABLE OF CONTENTS**

| 1. | Introduction                                                |    |  |

|----|-------------------------------------------------------------|----|--|

|    | 1.1 General Description                                     | 6  |  |

|    | 1.2 Features                                                |    |  |

| 2. | Packaging, Pin Descriptions, and Physical Dimensions        |    |  |

|    | 2.1 Packages and Pinouts                                    |    |  |

|    | 2.1.1 PLCC Package                                          |    |  |

|    | 2.1.2 PLCC Physical Dimensions                              | 11 |  |

|    | 2.1.3 PQFP Package                                          | 12 |  |

|    | 2.1.4 PQFP Physical Dimensions                              | 14 |  |

|    | 2.2 Pin/Signal Descriptions                                 |    |  |

| 3. | Maximum Ratings, Thermal Characteristics, and DC Parameters |    |  |

| 4. | Functional Description                                      |    |  |

|    | 4.1 Hardware Architecture                                   | 28 |  |

|    | 4.1.1 CAN Controller                                        | 29 |  |

|    | 4.1.2 Message RAM                                           | 29 |  |

|    | 4.1.3 I/O Ports                                             |    |  |

|    | 4.1.4 Programmable Clock Output                             |    |  |

|    | 4.2 Address Map                                             |    |  |

|    | 4.3 CAN Message Objects                                     |    |  |

| 5. |                                                             |    |  |

| 6. | Innovasic Part Number Cross-Reference.                      |    |  |

| 7. | Errata                                                      |    |  |

|    | 7.1 Summary                                                 |    |  |

|    | 7.2 Detail                                                  |    |  |

| 8. | Revision History                                            |    |  |

| 9. | For Further Information                                     |    |  |

## **LIST OF FIGURES**

| Figure 1. PLCC Package Diagram                                                  | 9  |

|---------------------------------------------------------------------------------|----|

| Figure 2. PLCC Physical Dimensions                                              |    |

| Figure 3. PQFP Package Diagram                                                  | 12 |

| Figure 4. PQFP Physical Dimensions                                              | 14 |

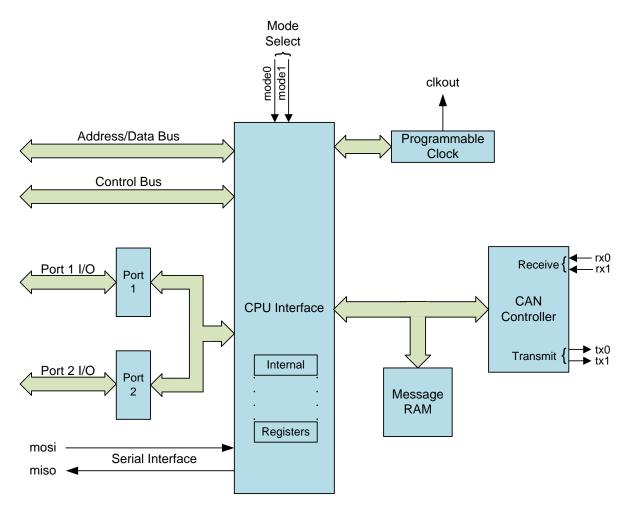

| Figure 5. Functional Block Diagram                                              | 28 |

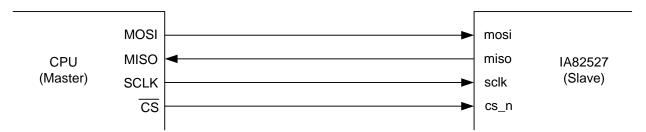

| Figure 6. mosi/miso Connection                                                  | 29 |

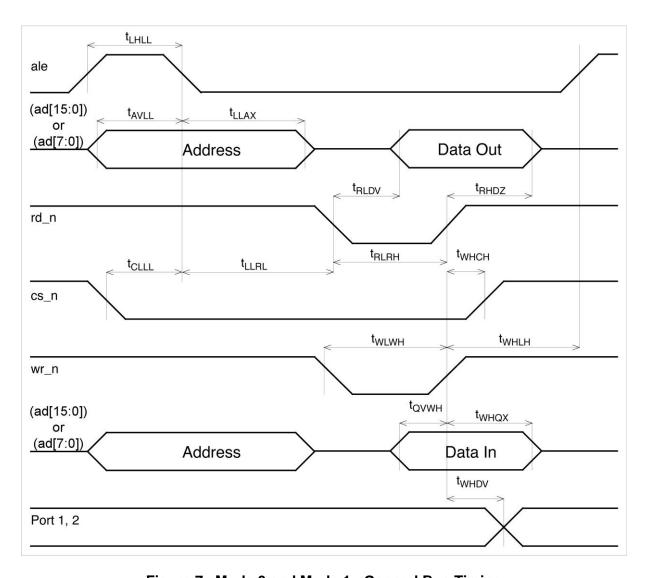

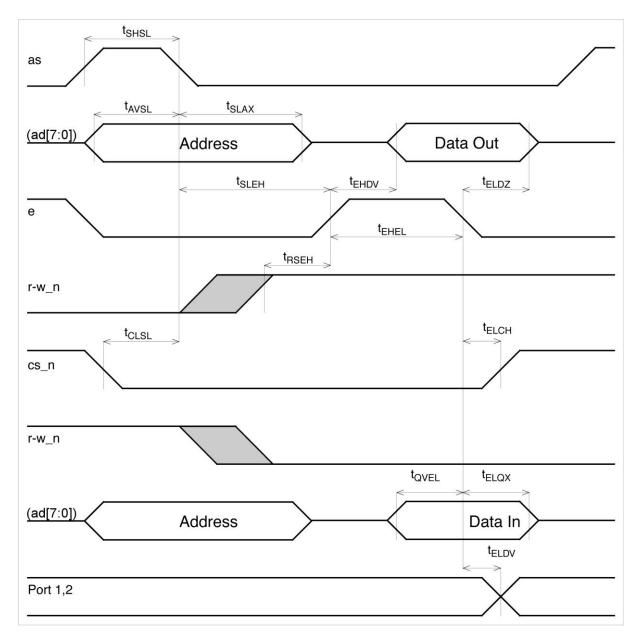

| Figure 7. Mode 0 and Mode 1: General Bus Timing                                 | 35 |

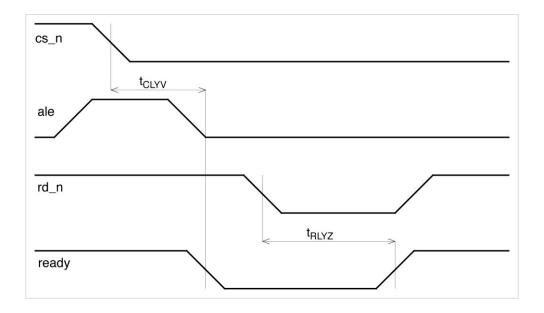

| Figure 8. Mode 0 and Mode 1: Ready Timing for Read Cycle                        | 36 |

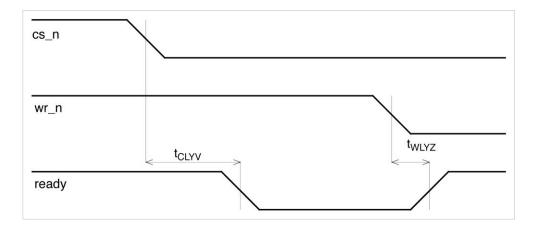

| Figure 9. Mode 0 and Mode 1: Ready Timing for Write Cycle with No Write Pending | 36 |

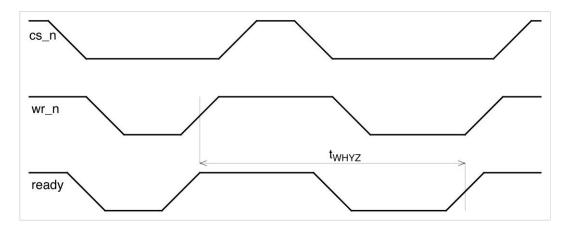

| Figure 10. Mode 0 and Mode 1: Ready Timing for Write Cycle with Write Active    | 37 |

| Figure 11. Mode 2: General Bus Timing                                           | 39 |

| Figure 12. Mode 3: Asynchronous Operation, Read Cycle                           | 41 |

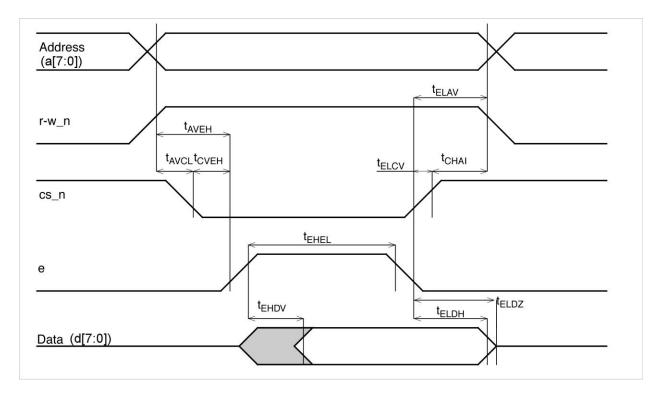

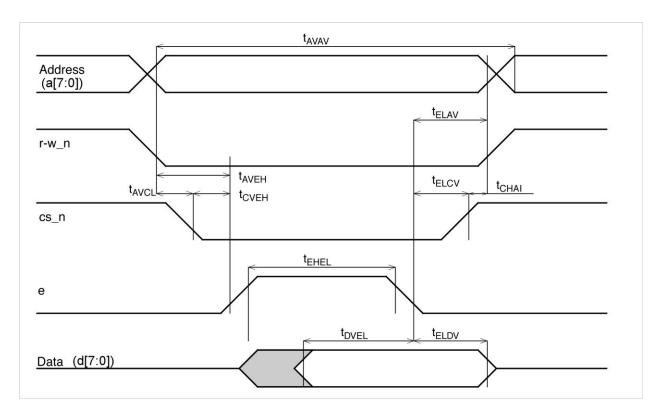

| Figure 13. Mode 3: Asynchronous Operation, Write Cycle                          | 42 |

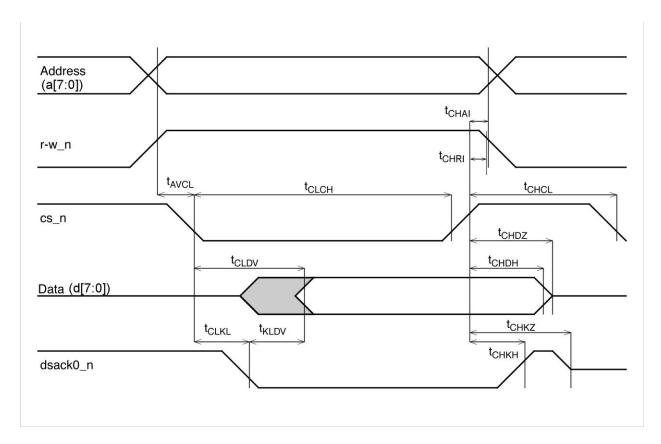

| Figure 14. Mode 3: Synchronous Operation, Read Cycle Timing                     | 44 |

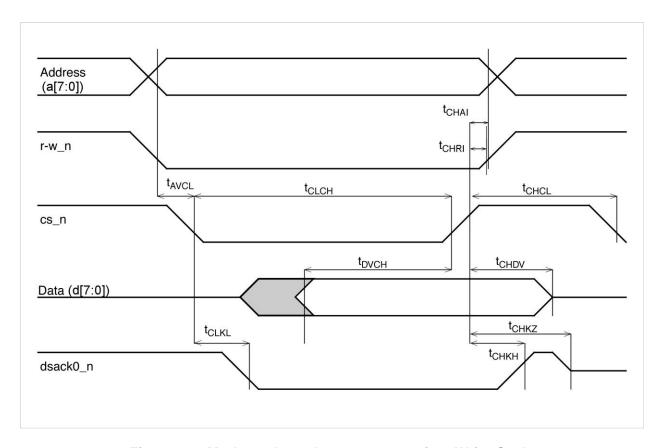

| Figure 15. Mode 3: Synchronous Operation, Write Cycle Timing                    | 45 |

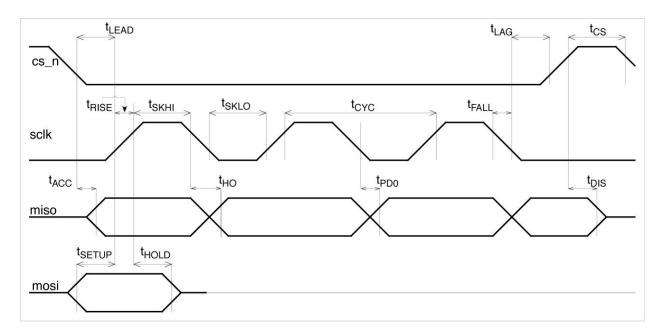

| Figure 16. Serial Interface Mode: icp = 0 and cp = 0                            | 47 |

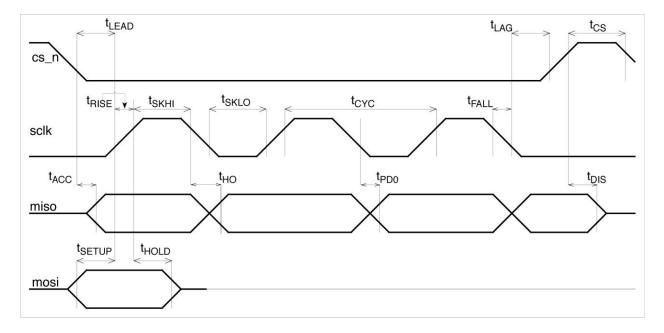

| Figure 17. Serial Interface Mode: icp = 1 and cp = 1                            | 47 |

## **LIST OF TABLES**

| Table 1. PLCC Pin List                                    | 10 |

|-----------------------------------------------------------|----|

| Table 2. PQFP Pin List                                    | 13 |

| Table 3. Pin/Signal Descriptions                          | 15 |

| Table 4. Absolute Maximum Ratings                         |    |

| Table 5. Thermal Characteristics                          |    |

| Table 6. DC Parameters                                    | 26 |

| Table 7. ISO Physical Layer DC Parameters                 | 27 |

| Table 8. Address Map                                      | 31 |

| Table 9. Message Object Structure                         | 32 |

| Table 10. Mode 0 and Mode 1: General Bus and Ready Timing | 34 |

| Table 11. Mode 2: General Bus Timing                      | 38 |

| Table 12. Mode 3: Asynchronous Operation Timing           | 40 |

| Table 13. Mode 3: Synchronous Operation Timing            | 43 |

| Table 14. Serial Interface Mode Timing                    | 46 |

| Table 15. Innovasic Part Number Cross-Reference           | 48 |

| Table 16. Revision History                                | 52 |

#### 1. Introduction

The Innovasic Semiconductor IA82527 Controller Area Network (CAN) Serial Communications Controller is a form, fit, and function replacement for the original Intel® 82527 Serial Communications Controller.

These devices are produced using Innovasic's Managed IC Lifetime Extension System (MILES<sup>TM</sup>). This cloning technology, which produces replacement ICs beyond simple emulations, ensures complete compatibility with the original device, including any "undocumented features." Additionally, MILES<sup>TM</sup> captures the clone design in such a way that production of the clone can continue even as silicon technology advances.

The IA82527 Serial Communications Controller replaces the obsolete Intel 82527 device, allowing users to retain existing board designs, software compilers/assemblers, and emulation tools, thereby avoiding expensive redesign efforts.

## 1.1 General Description

CAN protocol uses a multi-master CSMA/CR (Carrier Sense, Multiple Access with Collision Resolution) bus to transfer message objects between network nodes.

The IA82527 supports CAN Specification 2.0 Part A and B, standard and extended message frames, and has the capability to transmit, receive, and perform message filtering on standard and extended message frames.

The IA82527 can store 15 message objects of 8-byte data length. Each message object can be configured as either transmit or receive except for message object 15, which is receive-only. Message object 15 also provides a special acceptance mask designed to filter message identifiers that are received.

The IA82527 also provides a programmable acceptance mask that allows users to globally mask any identifier bits of the incoming message. This global mask can be used for both standard and extended message frames.

The IA82527 is manufactured in a reliable 5-volt process technology and is available in 44-lead PLCC or PQFP RoHs packages for the automotive temperature range (-40°C to 125°C).

### 1.2 Features

The primary features of the IA82527 are as follows:

- CAN Protocol Support

- Specification 2.0, Part A and Part B

- Standard ID Data and Remote Frames

- Extended ID Data and Remote Frames

IA211080504-02

- CAN Bus Interface

- Configurable Input Comparator

- Configurable Output Driver

- Programmable Bit Rate

- Global Mask, Programmable

- Standard Message Identifier

- Extended Message Identifier

- Message Objects

- 14 Transmit/Receive Buffers

- 1 Double Buffered Receive Buffer with Programmable Mask

- Flexible Status Interface

- CPU Interface Options

- 16-Bit Multiplexed Intel Architecture

- 8-Bit Multiplexed Intel Architecture

- 8-Bit Multiplexed Non-Intel Architecture

- 8-Bit Non-Multiplexed Non-Intel Architecture

- Serial (SPI)

- I/O Ports (2)

- 8-Bit

- Bidirectional

- Flexible Interrupt Structure

- Programmable Clock Output

A detailed description of the IA82527, including the features listed above, is provided in Chapter 4, Functional Description.

# 2. Packaging, Pin Descriptions, and Physical Dimensions

## 2.1 Packages and Pinouts

The Innovasic Semiconductor IA82527 CAN Serial Communications Controller is available in the following RoHs packages:

- 44-Pin Plastic Leaded Chip Carrier (PLCC), equivalent to original Intel PLCC package

- 44-Pin Plastic Quad Flat Pack (PQFP), equivalent to original Intel QFP package

## 2.1.1 PLCC Package

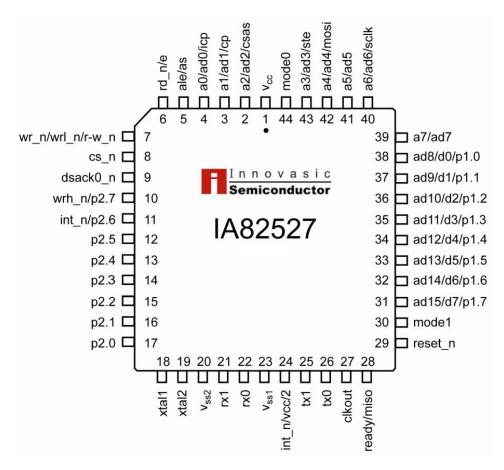

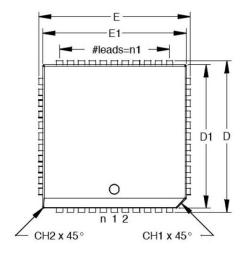

The pinout for the PLCC Package is as shown in Figure 1. The corresponding pinout is provided in Table 1.

Figure 1. PLCC Package Diagram

Table 1. PLCC Pin List

|     | T Comments of the comments of |  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 1   | V <sub>cc</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 2   | a2/ad2/csas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 3   | a1/ad1/cp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 4   | a0/ad0/icp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 5   | ale/as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 6   | rd_n/e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 7   | wr_n/wrl_n/r-w_n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 8   | cs_n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 9   | dsack0_n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 10  | wrh_n/p2.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 11  | int n/p2.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Pin | Name             |

|-----|------------------|

| 12  | p2.5             |

| 13  | p2.4             |

| 14  | p2.3             |

| 15  | p2.2             |

| 16  | p2.1             |

| 17  | p2.0             |

| 18  | xtal1            |

| 19  | xtal2            |

| 20  | V <sub>ss2</sub> |

| 21  | rx1              |

| 22  | rx0              |

| Pin | Name                     |  |

|-----|--------------------------|--|

| 23  | V <sub>ss1</sub>         |  |

| 24  | int_n/v <sub>cc</sub> /2 |  |

| 25  | tx1                      |  |

| 26  | tx0                      |  |

| 27  | clkout                   |  |

| 28  | ready/miso               |  |

| 29  | reset_n                  |  |

| 30  | mode1                    |  |

| 31  | ad15/d7/p1.7             |  |

| 32  | ad14/d6/p1.6             |  |

| 33  | ad13/d5/p1.5             |  |

| Pin | Name         |

|-----|--------------|

| 34  | ad12/d4/p1.4 |

| 35  | ad11/d3/p1.3 |

| 36  | ad10/d2/p1.2 |

| 37  | ad9/d1/p1.1  |

| 38  | ad8/d0/p1.0  |

| 39  | a7/ad7       |

| 40  | a6/ad6/sclk  |

| 41  | a5/ad5       |

| 42  | a4/ad4/mosi  |

| 43  | a3/ad3/ste   |

| 44  | mode0        |

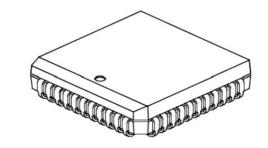

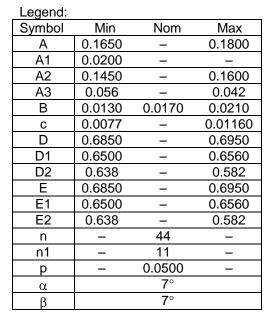

## 2.1.2 PLCC Physical Dimensions

The physical dimensions for the PLCC are as shown in Figure 2.

Note: Controlling dimension in inches.

Figure 2. PLCC Physical Dimensions

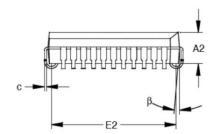

## 2.1.3 PQFP Package

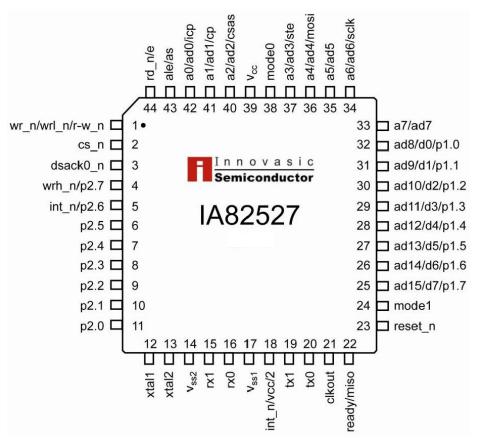

The pinout for the PQFP Package is as shown in Figure 3. The corresponding pinout is provided in Table 2.

Figure 3. PQFP Package Diagram

Table 2. PQFP Pin List

| Pin | Name             |  |  |

|-----|------------------|--|--|

| 1   | wr_n/wrl_n/r-w_n |  |  |

| 2   | cs_n             |  |  |

| 3   | dsack0_n         |  |  |

| 4   | wrh_n/p2.7       |  |  |

| 5   | int_n/p2.6       |  |  |

| 6   | p2.5             |  |  |

| 7   | p2.4             |  |  |

| 8   | p2.3             |  |  |

| 9   | p2.2             |  |  |

| 10  | p2.1             |  |  |

| 11  | p2.0             |  |  |

| Pin | Name                     |  |

|-----|--------------------------|--|

| 12  | xtal1                    |  |

| 13  | xtal2                    |  |

| 14  | V <sub>ss2</sub>         |  |

| 15  | rx1                      |  |

| 16  | rx0                      |  |

| 17  | V <sub>ss1</sub>         |  |

| 18  | int_n/v <sub>cc</sub> /2 |  |

| 19  | tx1                      |  |

| 20  | tx0                      |  |

| 21  | clkout                   |  |

| 22  | ready/miso               |  |

| Pin | Name         |  |

|-----|--------------|--|

| 23  | reset_n      |  |

| 24  | mode1        |  |

| 25  | ad15/d7/p1.7 |  |

| 26  | ad14/d6/p1.6 |  |

| 27  | ad13/d5/p1.5 |  |

| 28  | ad12/d4/p1.4 |  |

| 29  | ad11/d3/p1.3 |  |

| 30  | ad10/d2/p1.2 |  |

| 31  | ad9/d1/p1.1  |  |

| 32  | ad8/d0/p1.0  |  |

| 33  | a7/ad7       |  |

| Pin | Name            |

|-----|-----------------|

| 34  | a6/ad6/sclk     |

| 35  | a5/ad5          |

| 36  | a4/ad4/mosi     |

| 37  | a3/ad3/ste      |

| 38  | mode0           |

| 39  | V <sub>cc</sub> |

| 40  | a2/ad2/csas     |

| 41  | a1/ad1/cp       |

| 42  | a0/ad0/icp      |

| 43  | ale/as          |

| 44  | rd_n/e          |

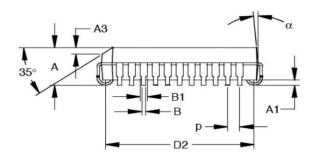

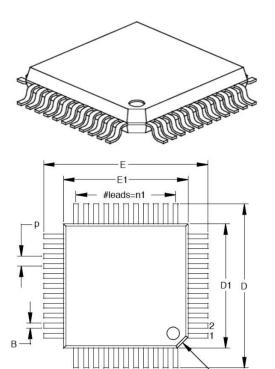

## 2.1.4 PQFP Physical Dimensions

The physical dimensions for the PQFP are as shown in Figure 4.

| Legend: |       |       |       |

|---------|-------|-------|-------|

| Symbol  | Min   | Nom   | Max   |

| n       | _     | 44    | _     |

| n1      | _     | 11    | _     |

| р       | _     | 0.031 | _     |

| Α       | _     | _     | 0.096 |

| A2      | _     | 0.079 | _     |

| A1      | _     | 0.010 | _     |

| L       | 0.019 | 0.025 | 0.031 |

| (F)     | _     | 0.047 | _     |

| Е       | 0.478 | 0.488 | 0.498 |

| D       | 0.478 | 0.488 | 0.498 |

| E1      | 0.390 | 0.394 | 0.398 |

| D1      | 0.390 | 0.394 | 0.398 |

| С       | 0.005 | 0.007 | 0.009 |

| В       | 0.011 | 0.014 | 0.017 |

| CH      | _     | 0.030 | _     |

| α       | 5°    | _     | 16°   |

| β       | 5°    | _     | 16°   |

| ф       | 0°    | _     | 10°   |

Note: Controlling dimension in inches.

**Figure 4. PQFP Physical Dimensions**

CH x 45°

## 2.2 Pin/Signal Descriptions

Descriptions of the pin and signal functions for the IA82527 Serial Communications Controller are provided in Table 3.

Several of the IA82527 pins have different functions depending on the operating mode of the device. Each of the different signals supported by a pin is listed and defined in Table 3, indexed alphabetically in the first column of the table. Additionally, the name of the pin associated with the signal as well as the pin numbers for both the PLCC and PQFP packages are provided in the "Pin" column. If the signal and pin names are the same, no entry is provided in the "Pin-Name" column.

Table 3. Pin/Signal Descriptions

|        | Pin          |      |      |                                                                                                        |

|--------|--------------|------|------|--------------------------------------------------------------------------------------------------------|

| Signal | Name         | PLCC | PQFP | Description                                                                                            |

| a0     | a0/ad0/icp   | 4    | 42   | address bits 7–0. Input. Mode 3. When the IA82527                                                      |

| a1     | a1/ad1/cp    | 3    | 41   | is configured to operate in the 8-bit non-multiplexed                                                  |

| a2     | a2/ad2/csas  | 2    | 40   | non-Intel architecture mode (Mode 3), these lines provide the 8-bit address bus input to the device.   |

| a3     | a3/ad3/ste   | 43   | 37   | , , , , , , , , , , , , , , , , , , , ,                                                                |

| a4     | a4/ad4/mosi  | 42   | 36   |                                                                                                        |

| a5     | a5/ad5       | 41   | 35   |                                                                                                        |

| a6     | a6/ad6/sclk  | 40   | 34   |                                                                                                        |

| a7     | a7/ad7       | 39   | 33   |                                                                                                        |

| ad0    | a0/ad0/icp   | 4    | 42   | address/data bits 15-0. Input/Output. Mode 1. When                                                     |

| ad1    | a1/ad1/cp    | 3    | 41   | the IA82527 is configured to operate in the 16-bit multiplexed Intel architecture mode (Mode 1), these |

| ad2    | a2/ad2/csas  | 2    | 40   | lines provide the 16-bit address bus (input) and the                                                   |

| ad3    | a3/ad3/ste   | 43   | 37   | 16-bit data bus (input/output) for the device.                                                         |

| ad4    | a4/ad4/mosi  | 42   | 36   |                                                                                                        |

| ad5    | a5/ad5       | 41   | 35   |                                                                                                        |

| ad6    | a6/ad6/sclk  | 40   | 34   |                                                                                                        |

| ad7    | a7/ad7       | 39   | 33   |                                                                                                        |

| ad8    | ad8/d0/p1.0  | 38   | 32   |                                                                                                        |

| ad9    | ad9/d1/p1.1  | 37   | 31   |                                                                                                        |

| ad10   | ad10/d2/p1.2 | 36   | 30   |                                                                                                        |

| ad11   | ad11/d3/p1.3 | 35   | 29   |                                                                                                        |

| ad12   | ad12/d4/p1.4 | 34   | 28   |                                                                                                        |

| ad13   | ad13/d5/p1.5 | 33   | 27   |                                                                                                        |

| ad14   | ad14/d6/p1.6 | 32   | 26   |                                                                                                        |

| ad15   | ad15/d7/p1.7 | 31   | 25   |                                                                                                        |

Table 3. Pin/Signal Descriptions (Continued)

|        | Pi          | n    |      |                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|-------------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal | Name        | PLCC | PQFP | Description                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ale    | ale/as      | 5    | 43   | address latch enable. Input. Active High. Mode 0 and Mode 1. When the IA82527 is configured to operate in either the 8-bit multiplexed Intel architecture mode (Mode 0) or the 16-bit multiplexed Intel architecture mode (Mode 1), this signal latches the address into the device during the address phase of the bus cycle.                                                                                                |

| as     | ale/as      | 5    | 43   | address strobe. Input. Active High. Mode 2. When the IA82527 is configured to operate in the 8-bit multiplexed non-Intel architecture mode (Mode 2), this signal latches the address into the device during the address phase of the bus cycle.  If the IA82527 is configured to operate in Mode 3 (8-bit non-multiplexed non-Intel architecture), this pin must be tied high.                                                |

| clkout | clkout      | 27   | 21   | clock out. Output (push-pull). This output provides a programmable clock frequency. The frequency is set via the Clockout Register (1FH) and can range from the frequency of the xtal (crystal) input to xtal/n, where n can be an integer value from 2 through 15. This output allows the IA82527 to clock other devices such as the host CPU.                                                                               |

| ср     | a1/ad1/cp   | 3    | 41   | clock phase. Input. Serial Interface Mode. When this input is a logic 0, data is sampled on the rising edge of sclk. When this input is a logic 1, data is sampled on the falling edge of sclk.                                                                                                                                                                                                                               |

| cs_n   | cs_n        | 8    | 2    | chip select. Input. Active Low (Modes 0–3); Selectable Active Level (Serial Interface Mode). When the IA82527 is configured to operate in one of the parallel interface modes (Modes 0–3) or the Serial Interface Mode, this input, during its active state, selects the device allowing CPU access.  For Serial Interface Mode operation, the active state is selectable (i.e., either high or low) via the IA8257 csas pin. |

| csas   | a2/ad2/csas | 2    | 40   | chip select active state. Input. Serial Interface Mode. When this input is a logic 0, the cs_n input is configured to function active low. When this input is a logic 1, the cs_n input is configured to function active high.                                                                                                                                                                                                |

Table 3. Pin/Signal Descriptions (Continued)

|          | Pir          | า    |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|--------------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal   | Name         | PLCC | PQFP | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| d0       | ad8/d0/p1.0  | 38   | 32   | data bits 7–0. Input/Output. Mode 3. When the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| d1       | ad9/d1/p1.1  | 37   | 31   | IA82527 is configured to operate in the 8-bit non-multiplexed non-Intel architecture mode (Mode 3),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| d2       | ad10/d2/p1.2 | 36   | 30   | these lines provide the 8-bit data bus to the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| d3       | ad11/d3/p1.3 | 35   | 29   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| d4       | ad12/d4/p1.4 | 34   | 28   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| d5       | ad13/d5/p1.5 | 33   | 27   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| d6       | ad14/d6/p1.6 | 32   | 26   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| d7       | ad15/d7/p1.7 | 31   | 25   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| dsack0_n | dsack0_n     | 9    | 3    | data and size acknowledge 0. Output. Active Low (open drain with active pull-up). Mode 3 (asynchronous operation). When the IA82527 is configured to operate in the 8-bit non-multiplexed non-Intel architecture mode (Mode 3), this signal functions as follows: when the CPU reads from the IA82527, dsack0_n active low indicates that the data is valid; when the CPU writes to the IA82527, dsack0_n active low indicates that the data has been received.  Note: The active pull-up circuitry drives dsack0_n high for 10ns to raise it to a 3.0V voltage level. After that, an external pull up is required to pull dsack0_n the remainder of the way to Vss. |

| е        | rd_n/e       | 6    | 44   | enable. Input. Active High. Mode 3 (synchronous). When the IA82527 is configured to operate in the 8-bit non-multiplexed non-Intel architecture mode (Mode 3), this signal functions as follows: when the CPU reads from or writes to the IA82527, e active high indicates that the address is valid.                                                                                                                                                                                                                                                                                                                                                                |

| icp      | a0/ad0/icp   | 4    | 42   | idle clock polarity. Input. Serial Interface Mode. When this input is a logic 0, the polarity for the idle state of sclk is low. When this input is a logic 1, the polarity for the idle state of sclk is high.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Table 3. Pin/Signal Descriptions (Continued)

|        | Pir                       | າ    |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------|---------------------------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal | Name                      | PLCC | PQFP | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| int_n  | int_n/ V <sub>CC</sub> /2 | 24   | 18   | interrupt. Output (open collector). Active Low. On the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|        | int_n/p2.6                | 11   | 5    | <ul> <li>IA82527, two pins can provide the interrupt (int_n) output; however, depending on the setting of the MUX bit in the CPU Interface Register (02H), only one of the pins will serve as the source of int_n as follows:</li> <li>PLCC Package:  <ul> <li>When the MUX bit of the CPU Interface Register is 0, pin 24 functions as the int_n output and pin 11 functions as p2.6.</li> <li>When the MUX bit of the CPU Interface Register is 1, pin 11 functions as the int_n output and pin 24 functions as V<sub>cc</sub>/2.</li> </ul> </li> <li>PQFP Package:  <ul> <li>When the MUX bit of the CPU Interface Register is 0, pin 18 functions as the int_n output and pin 5 functions as p2.6.</li> <li>When the MUX bit of the CPU Interface Register is 1, pin 5 functions as the int_n output and pin 18 functions as V<sub>cc</sub>/2.</li> </ul> </li> </ul> |

| miso   | ready/miso                | 28   | 22   | master in slave out. Output (open drain). Serial Interface Mode. When the IA82527 is configured to operate with a serial interface, miso is the serial data output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Table 3. Pin/Signal Descriptions (Continued)

| Signal |                |      |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|----------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.9    | Name           | PLCC | PQFP  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| mode0  | mode0          | 44   | 38    | modeN (N = 1 or 0). Input. The logic levels at the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| mode1  | mode0<br>mode1 | 30   | 38 24 | modeN (N = 1 or 0). Input. The logic levels at the mode0 and mode1 inputs determine the operating mode (i.e., interface type) of the IA82527 as follows:  mode1 mode0 Interface Type  0 0 8-bit multiplexed Intel 0 1 16-bit multiplexed Intel 1 0 8-bit multiplexed non-Intel 1 1 8-bit Non-multiplexed non-Intel 1 1 8-bit Non-multiplexed non-Intel 1 1 8-bit Non-multiplexed non-Intel  The mode1 and mode0 inputs are also used to establish the Serial Interface Mode as follows: when the IA82527 is reset, if  mode1 = 0 mode0 = 0 rd_n = 0 mr_n = 0 the Serial Interface Mode will be selected.  The mode1 and mode0 pins are internally connected to weak pull-downs. These pins will be pulled low |

|        |                |      |       | during reset if unconnected. Following reset, these pins will float.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| mosi   | a4/ad4/mosi    | 42   | 36    | pins will float.  master out slave in. Input. Serial Interface Mode. When the IA82527 is configured to operate with a serial interface, mosi is the serial data input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Table 3. Pin/Signal Descriptions (Continued)

|        | Pir          | 1    |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|--------------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal | Name         | PLCC | PQFP | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| p1.0   | ad8/d0/p1.0  | 38   | 32   | port 1, bit N (N = 7–0). Input/Output (general-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| p1.1   | ad9/d1/p1.1  | 37   | 31   | purpose). Mode 0, Mode 2, and Serial Interface Mode. Port 1 bits <b>p1.7–p1.0</b> can be individually programmed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| p1.2   | ad10/d2/p1.2 | 36   | 30   | as inputs or outputs. Programming is accomplished by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| p1.3   | ad11/d3/p1.3 | 35   | 29   | writing to the P1CONF Register (9FH). The 8 bits of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| p1.4   | ad12/d4/p1.4 | 34   | 28   | the P1CONF Register, P1CONF7–P1CONF0, correspond directly to pins <b>p1.7–p1.0</b> . Writing a 0 to a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| p1.5   | ad13/d5/p1.5 | 33   | 27   | bit in the P1CONF Register causes the corresponding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| p1.6   | ad14/d6/p1.6 | 32   | 26   | pin to be configured as a high-impedance input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |