# CONTENTS

| 1. INT | RODUCTION                                                   | MCU11E9 - | 1  |

|--------|-------------------------------------------------------------|-----------|----|

| 1.1    | FEATURES                                                    | MCU11E9 - | 1  |

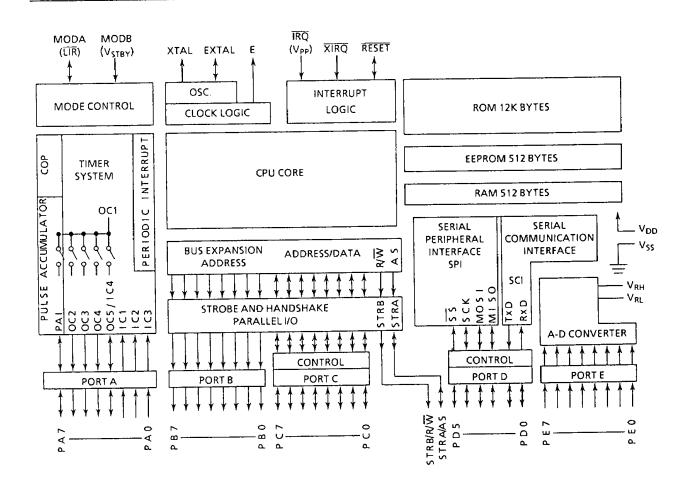

| 1.2    | GENERAL DESCRIPTION                                         | MCU11E9 - | 2  |

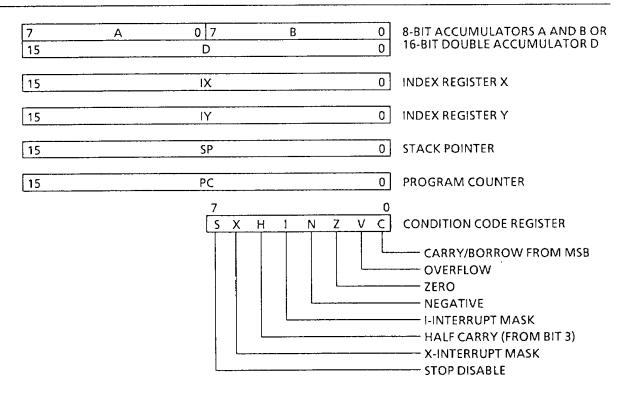

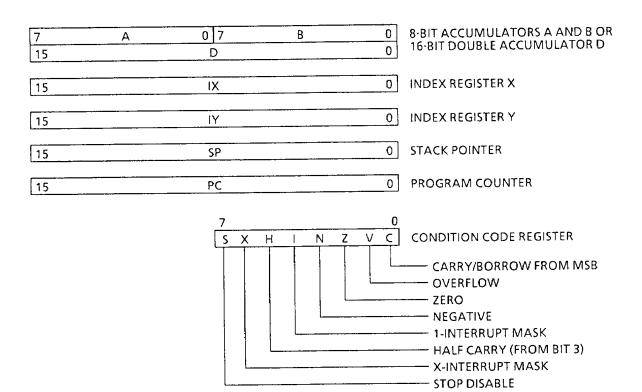

| 1.3    | PROGRAMMER'S MODEL                                          | MCU11E9 - | 2  |

| 1.4    | SUMMARY OF TMP68HC11 FAMILY                                 | MCU11E9 - | 4  |

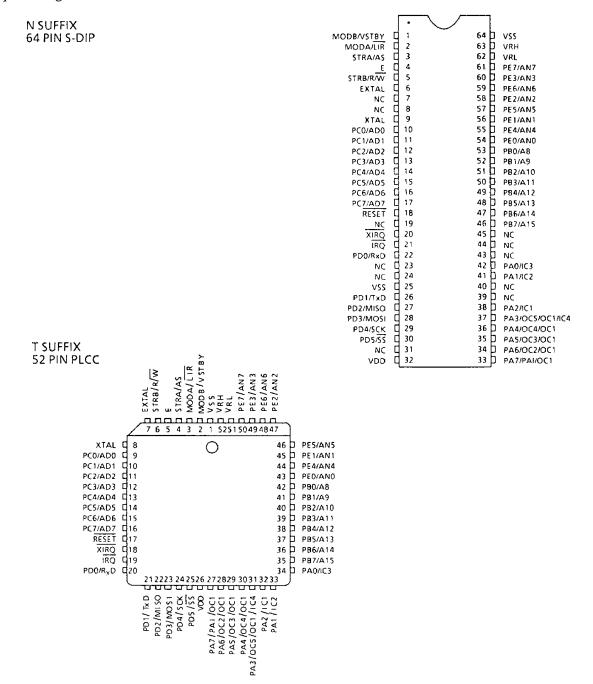

| 2. SIG | NAL DESCRIPTIONS AND OPERATING MODES                        | MCU11E9 - | 6  |

| 2.1    | SIGNAL PIN DESCRIPTIONS                                     | MCU11E9 - | 6  |

| 2.1.1  | Input Power ( $V_{ m DD}$ ) and Ground ( $V_{ m SS}$ )      | MCU11E9 - | 6  |

| 2.1.2  | Reset (RESET)                                               | MCU11E9 - | 6  |

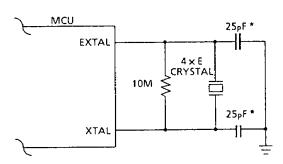

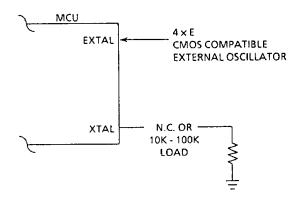

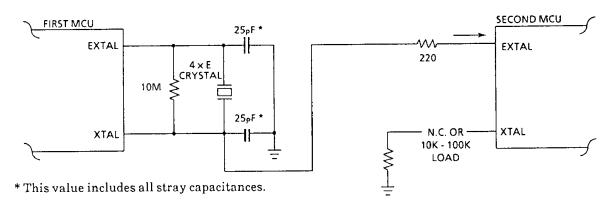

| 2.1.3  | Crystal Driver and External Clock Input (XTAL, EXTAL)       | MCU11E9 - | 6  |

| 2.1.4  | E Clock Output (E)                                          | MCU11E9 - | 8  |

| 2.1.5  | Interrupt Request ( $\overline{	ext{IRQ}}$ )                | MCU11E9 - | 8  |

| 2.1.6  | Non-Maskable Interrupt (XIRQ)                               | MCU11E9 - | 8  |

| 2.1.7  | Mode A/Load Instruction Register and Mode B/Standby Voltage |           |    |

|        | (MODA/ <del>LIR</del> , MODB/V <sub>STBY</sub> )            | MCU11E9 - | 8  |

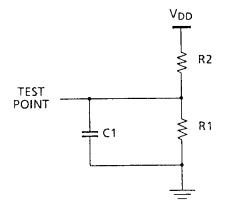

| 2.1.8  | A/D Converter Reference Voltages ( $V_{RL}, V_{RH}$ )       | MCU11E9 - | 9  |

| 2.1.9  | Strobe B and Read/Write (STRB/R/ $\overline{W}$ )           | MCU11E9 - | 9  |

| 2.1.1  | 0 Strobe A and Address Strobe (STRA/AS)                     | MCU11E9 - | 9  |

| 2.1.1  | 1 Port Signals                                              | MCU11E9 - | 9  |

| 2.1    | .11.1 Port A                                                | MCU11E9 - | 10 |

| 2.1    | .11.2 Port B                                                | MCU11E9 - | 11 |

| 2.1    | .11.3 Port C                                                | MCU11E9 - | 12 |

| 2.1    | .11.4 Port D                                                | MCU11E9 - | 12 |

| 2.1    | .11.5 Port E                                                | MCU11E9 - | 12 |

| 2.2    | OPERATING MODES                                             | MCU11E9 - | 12 |

| 2.2.1  | Single-Chip Operating Mode                                  | MCU11E9 - | 13 |

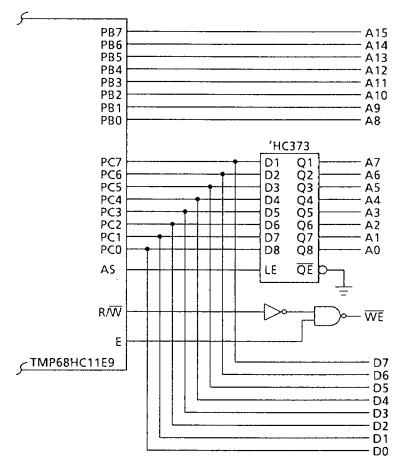

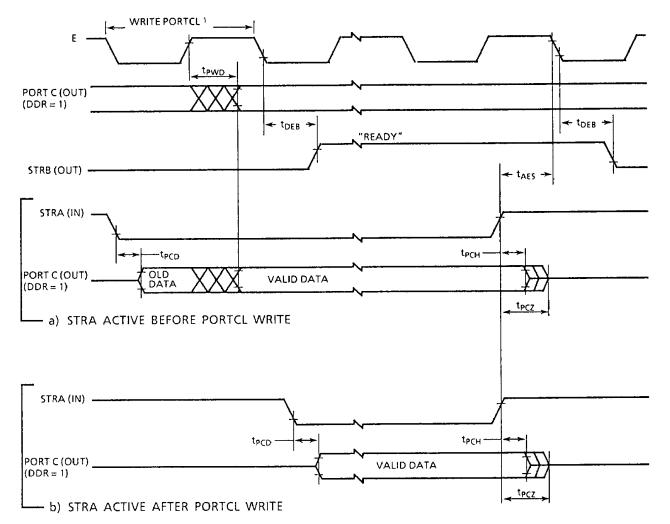

| 2.2.2  | Expanded Multiplexed Operating Mode                         | MCU11E9 - | 13 |

| 2.2.3  | Special Bootstrap Operating Mode                            | MCU11E9 - | 13 |

| 2.2.4  | Additional Boot Loader Program Options                      | MCU11E9 - | 16 |

| 2.2.5  | Special Test Operating Mode                                 | MCU11E9 - | 17 |

| 3. ON  | -CHIP MEMORIES                                              | MCU11E9 - | 18 |

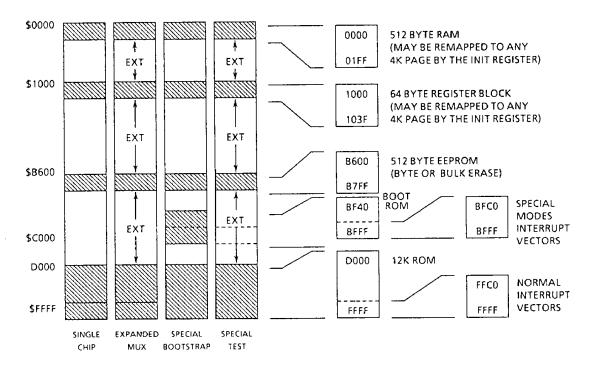

| 3.1    | MEMORY MAPS                                         | MCU11E9 - | 18 |

|--------|-----------------------------------------------------|-----------|----|

| 3.2    | RAM AND I/O MAPPING REGISTER (INIT)                 | MCU11E9 - | 21 |

| 3.3    | ROM                                                 | MCU11E9 - | 22 |

| 3.4    | RAM                                                 | MCU11E9 - | 23 |

| 3.5    | EEPROM                                              | MCU11E9 - | 23 |

| 3.5.1  | EEPROM Programming Control Register (PPROG)         | MCU11E9 - | 23 |

| 3.5.2  | EEPROM Block Protect Register (BPROT)               | MCU11E9 - | 25 |

| 3.5.3  | Programming/Erasing Internal EEPROM                 | MCU11E9 - | 25 |

| 3.5    | .3.1 Read                                           | MCU11E9 - | 26 |

| 3.5    | .3.2 Programming                                    | MCU11E9 - | 26 |

| 3.5    | .3.3 Bulk Erase                                     | MCU11E9 - | 26 |

| 3.5    | .3.4 Row Erase                                      | MCU11E9 - | 27 |

| 3.5    | .3.5 Byte Erase                                     | MCU11E9 - | 27 |

| 3.5.4  | System Configuration Register (CONFIG)              | MCU11E9 - | 28 |

| 3.5    | .4.1 Programming and Erasure of the CONFIG Register | MCU11E9 - | 29 |

| 3.5    | .4.2 Operation of the Configuration Mechanism       | MCU11E9 - | 30 |

|        |                                                     |           |    |

| 4. PA  | RALLEL I/O                                          | MCU11E9 - | 31 |

| 4.1    | GENERAL PURPOSE I/O (PORTS C AND D)                 | MCU11E9 - | 31 |

| 4.2    | FIXED DIRECTION I/O (PORTS A, B, AND E)             | MCU11E9 - | 31 |

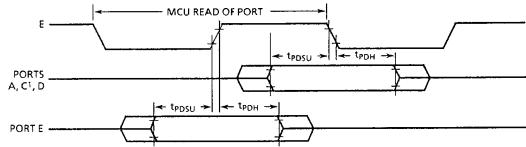

| 4.3    | SIMPLE STROBED I/O                                  | MCU11E9 - | 31 |

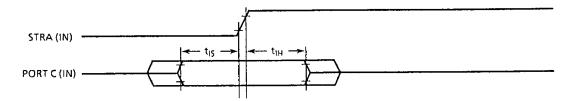

| 4.3.1  | Strobed Input Port C                                | MCU11E9 - | 32 |

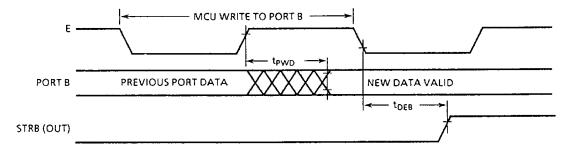

| 4.3.2  | Strobed Output Port B                               | MCU11E9 - | 32 |

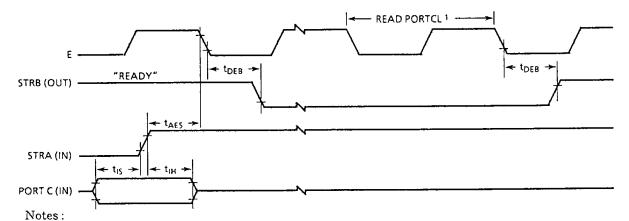

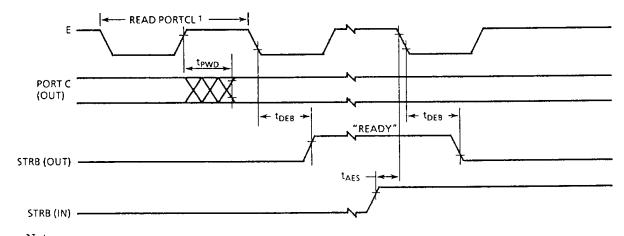

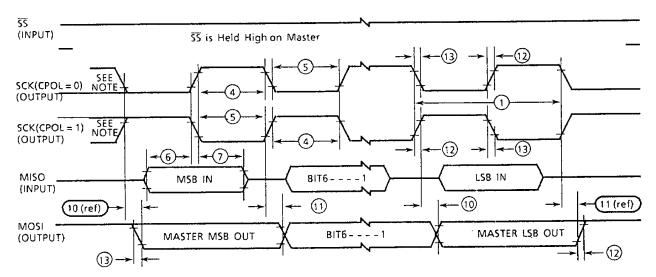

| 4.4    | FULL HANDSHAKE I/O                                  | MCU11E9 - | 32 |

| 4.4.1  |                                                     |           |    |

| 4.4.2  | •                                                   |           |    |

| 4.5    | PARALLEL I/O CONTROL REGISTER (PIOC)                | MCU11E9 - | 34 |

|        |                                                     |           |    |

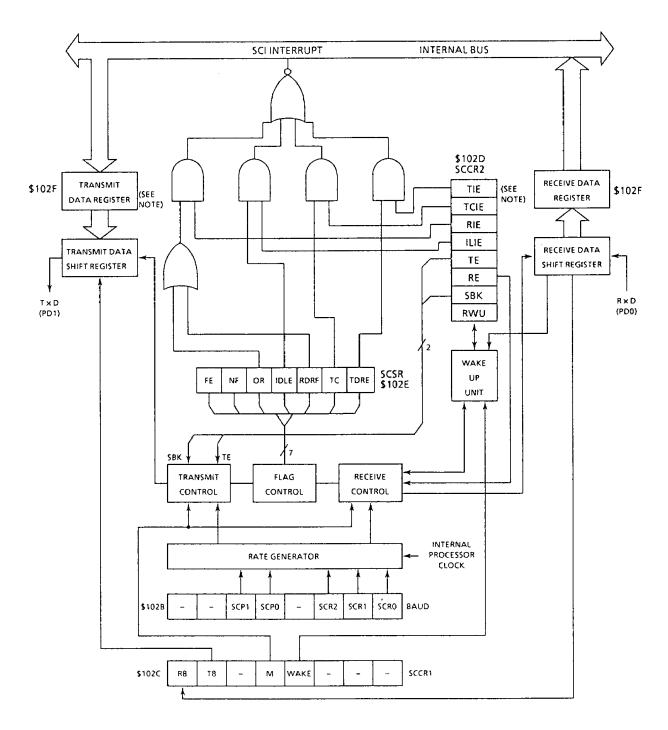

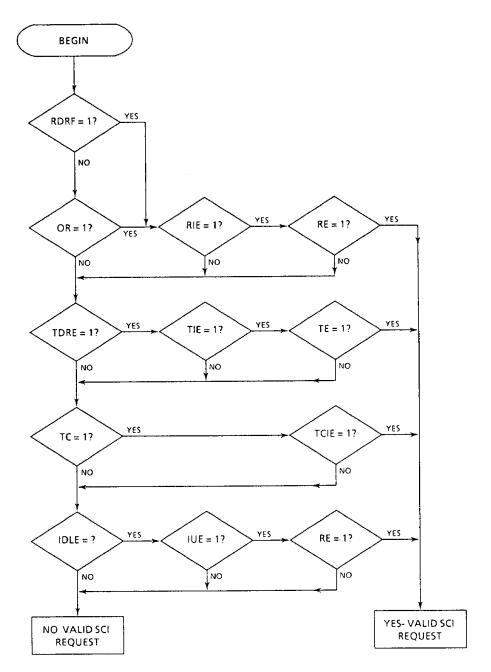

| 5. SEI | RIAL COMMUNICATIONS INTERFACE (SCI)                 |           |    |

| 5.1    | OVERVIEW AND FEATURES                               |           |    |

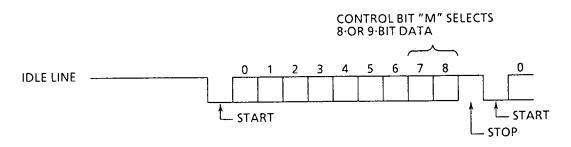

| 5.2    | DATA FORMAT                                         |           | 39 |

| 5.3    | WAKE-UP FEATURE                                     |           | 39 |

| 5.4    | RECEIVE DATA (RxD)                                  |           |    |

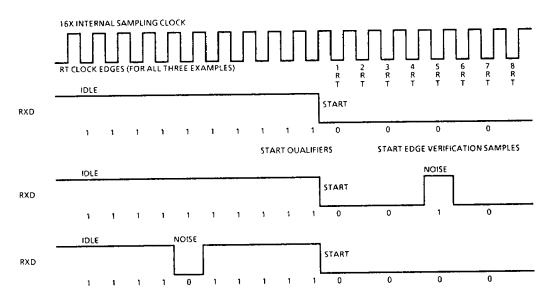

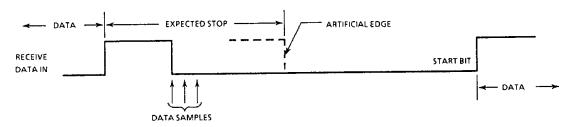

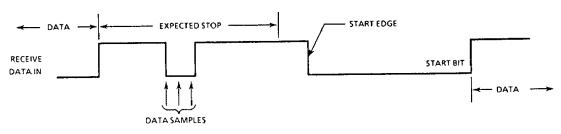

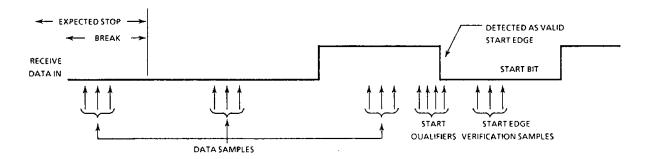

| 5.5    | START BIT DETECTION                                 |           |    |

| 5.6    | TRANSMIT DATA (TxD)                                 |           |    |

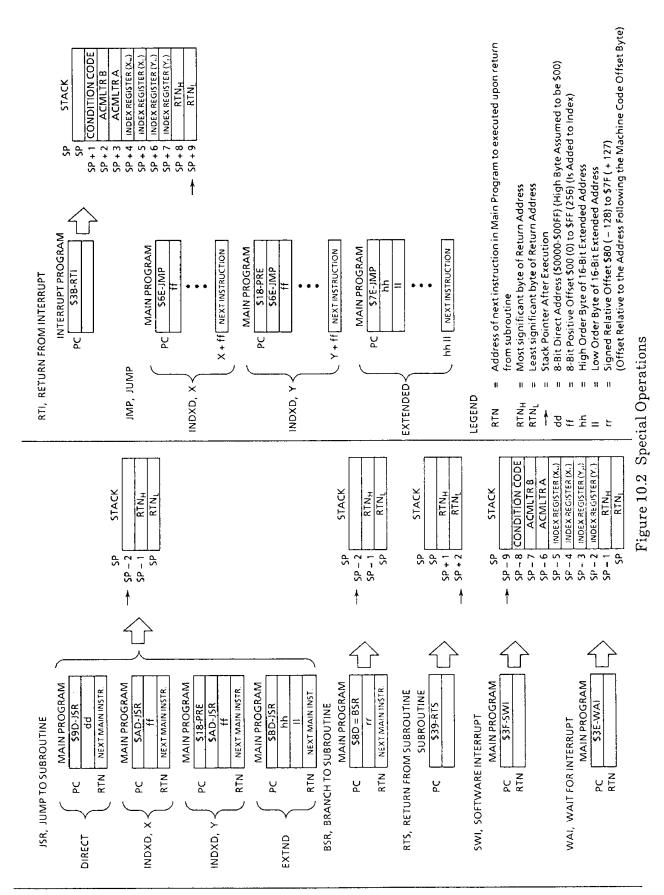

| 5.7    | FUNCTIONAL DESCRIPTION                              | MCU11E9 - | 42 |

CONTENTS

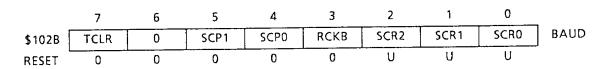

| 5.8    | SCI REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MCU11E9 - | 43 |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----|

| 5.8.1  | (0.07.7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MCU11E9 - | 43 |

| 5.8.2  | 1 T (10 C C C C C C C C C C C C C C C C C C C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MCU11E9 - | 45 |

| 5.8.3  | a de la composição de l | MCU11E9 - | 45 |

| 5.8.4  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MCU11E9 - | 47 |

| 5.8.5  | <del></del> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MCU11E9-  | 48 |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |    |

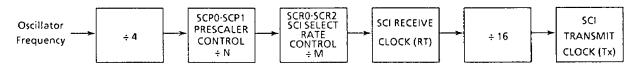

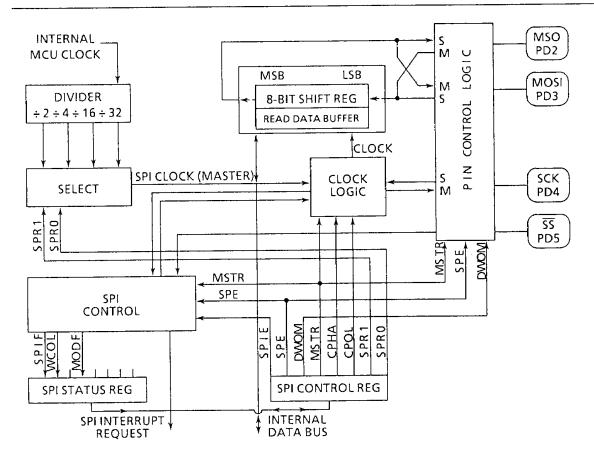

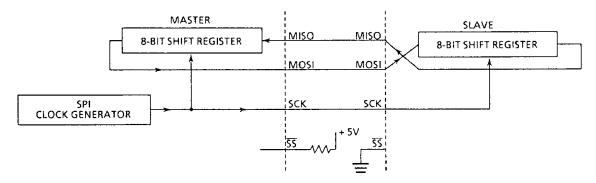

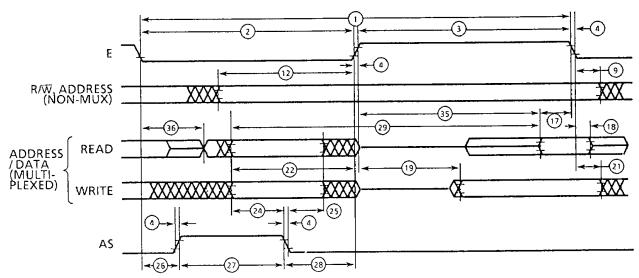

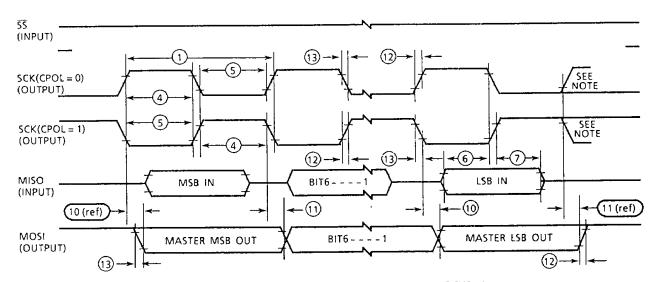

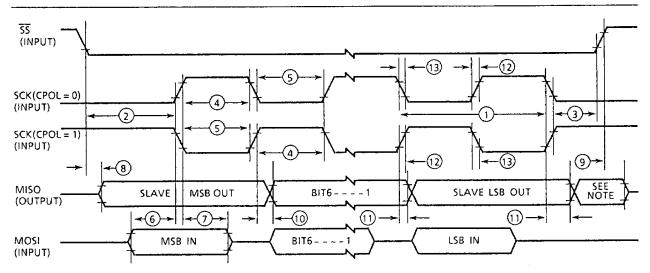

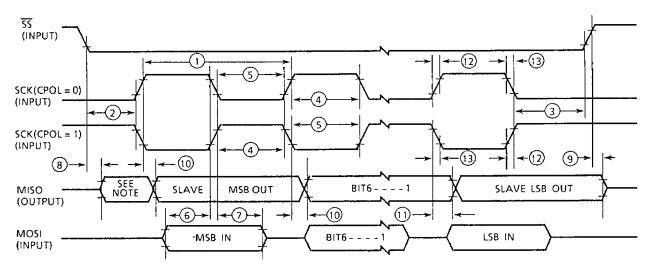

| 6. SEF | RIAL PERIPHERAL INTERFACE (SPI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MCU11E9 - | 52 |

| 6.1    | OVERVIEW AND FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MCU11E9 - | 52 |

| 6.2    | SPI SIGNAL DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | MCU11E9 - | 52 |

| 6.2.1  | Master In Slave Out (MISO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MCU11E9 - | 52 |

| 6.2.2  | Master Out Slave In (MOSI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MCU11E9 - | 53 |

| 6.2.3  | Serial Clock (SCK)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | MCU11E9 - | 53 |

| 6.2.4  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MCU11E9 - | 53 |

| 6.3    | FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MCU11E9 - | 54 |

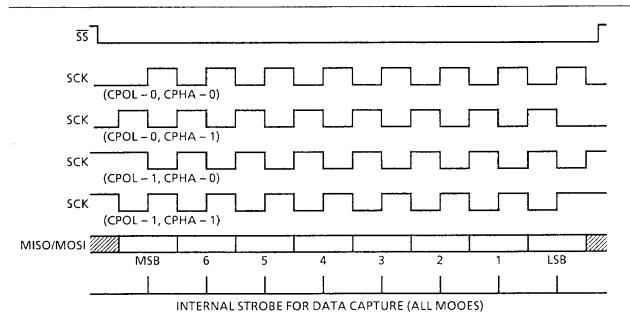

| 6.4    | SPI REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MCU11E9 - | 56 |

| 6.4.1  | Serial Peripheral Control Register (SPCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | MCU11E9 - | 56 |

| 6.4.2  | Serial Peripheral Status Register (SPSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MCU11E9 - | 57 |

| 6.4.3  | Serial Peripheral Data I/O Register (SPDR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MCU11E9 - | 58 |

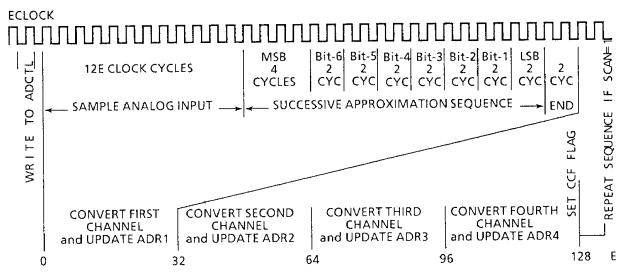

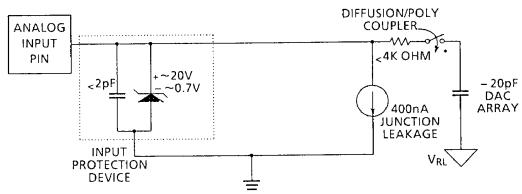

| 7 AN   | ALOG-TO-DIGITAL CONVERTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | MCU11E9 - | 60 |

| 7.1    | CONVERSION PROCESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           | 60 |

| 7.2    | CHANNEL ASSIGNMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | MCU11E9 - | 60 |

| 7.3    | SINGLE-CHANNEL OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MCU11E9 - | 60 |

| 7.4    | MULTIPLE-CHANNEL OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           | 61 |

| 7.5    | OPERATION IN STOP AND WAIT MODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           | 62 |

| 7.6    | A/D CONTROL/STATUS REGISTER (ADCTL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |    |

| 7.7    | A/D RESULT REGISTERS 1, 2, 3, AND 4 (ADR1, ADR2,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |    |

| •••    | ADR3, AND ADR4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MCU11E9 - | 64 |

| 7.8    | A/D POWER UP AND CLOCK SELECT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           | 64 |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |    |

| 8. PR  | OGRAMMABLE TIMER, REAL TIME INTERRUPT,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |    |

| AN     | D PULSE ACCUMULATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | MCU11E9 - | 65 |

| 8.1    | PROGRAMMABLE TIMER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | MCU11E9 - | 65 |

| 8.1.   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           | 65 |

| 8.1.   | 2 Input Capture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MCU11E9 - | 65 |

| 8.1.2.1  | Input Capture 4                          | MCU11E9 - | 66 |

|----------|------------------------------------------|-----------|----|

| 8.1.3    | Output Compare                           | MCU11E9 - | 66 |

| 8.1.4    | Output Compare 1 I/O Pin Control         | MCU11E9 - | 67 |

| 8.1.5    | Timer Compare Force Register (CFORC)     | MCU11E9-  | 67 |

| 8.1.6    | Output Compare 1 Mask Register (OC1M)    | MCU11E9 - | 68 |

| 8.1.7    | Output Compare 1 Data Register (OC1D)    | MCU11E9 - | 68 |

| 8.1.8    | Timer Control Register 1 (TCTL1)         | MCU11E9 - | 69 |

| 8.1.9    | Timer Control Register 2 (TCTL2)         | MCU11E9 - | 69 |