PCS LOW NOISE AMPLIFIER/MIXER

**RF9986**

Typical Applications

- CDMA/TDMA/DCS1900 PCS Systems

- PHS 1500/WLAN 2400 Systems

- General Purpose Down Converter

### Micro-Cell PCS Base Stations

• Portable Battery-Powered Equipment

### **Product Description**

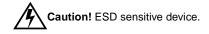

The RF9986 is a monolithic integrated receiver front-end for PCS, PHS, and WLAN applications. The IC contains all of the required components to implement the RF functions of the receiver front-end except for the passive filtering and LO generation. It contains an LNA (low-noise amplifiers), a double-balanced Gilbert cell mixer, a balanced IF output, an LO isolation buffer amplifier, and an LO output buffer amplifier for providing the buffered LO signal as an output. The IC is designed to operate from a single 3.6V power supply.

#### Optimum Technology Matching® Applied GaAs HBT Si BJT GaAs MESFET Si Bi-CMOS SiGe HBT Si CMOS NC 1 24 NC VCC1 2 23 GND9 VCC2 3 22 VCC4 GND1 4 21 GND8 LNA IN 5 20 LNA OUT 19 GND7 GND2 6 GND3 7 18 MIX RF IN NC 8 17 GND6 16 IF-GND4 9 VCC3 10 15 IF+

LO BUFF EN 11 LO IN 12 H

Functional Block Diagram

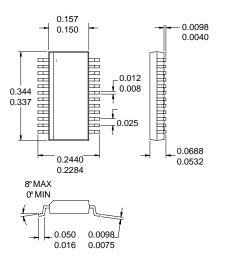

Package Style: SSOP-24

#### Features

- Complete Receiver Front-End

- Extremely High Dynamic Range

- Single 3.6V Power Supply

- External LNA IP3 Adjustment

- 1500MHz to 2500MHz Operation

#### Ordering Information

RF9986PCS Low Noise Amplifier/MixerRF9986 PCBAFully Assembled Evaluation Board

RF Micro Devices, Inc.

Tel (336) 664 1233

7628 Thorndike Road

Fax (336) 664 0454

Greensboro, NC 27409, USA

http://www.rfmd.com

#### **Absolute Maximum Ratings**

| Parameter                     | Rating      | Unit            |

|-------------------------------|-------------|-----------------|

| Supply Voltage                | -0.5 to 7.0 | V <sub>DC</sub> |

| Input LO and RF Levels        | +6          | dBm             |

| Ambient Operating Temperature | -40 to +85  | °C              |

| Storage Temperature           | -40 to +150 | °C              |

RF Micro Devices believes the furnished information is correct and accurate at the time of this printing. However, RF Micro Devices reserves the right to make changes to its products without notice. RF Micro Devices does not assume responsibility for the use of the described product(s).

| Devenuetor                              |       | Specificatio | n    | 11   | Condition                                                                                                                                                                                            |  |

|-----------------------------------------|-------|--------------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                               | Min.  | Тур.         | Max. | Unit |                                                                                                                                                                                                      |  |

| Overall                                 |       |              |      |      | T=25°C, V <sub>CC</sub> =3.6V, RF=1959MHz,                                                                                                                                                           |  |

|                                         | 4500  |              | 0500 |      | LO=1749MHz @ -2dBm                                                                                                                                                                                   |  |

| RF Frequency Range                      | 1500  |              | 2500 | MHz  |                                                                                                                                                                                                      |  |

| LO Frequency Range                      | 1200  |              | 2500 | MHz  |                                                                                                                                                                                                      |  |

| IF Frequency Range Cascaded Performance |       | DC to 500    |      | MHz  | 1kΩ balanced load, 2.5dB Image Filter Loss.                                                                                                                                                          |  |

|                                         | 22    | 05           |      |      | TK22 balanced load, 2.50B image Filter Loss.                                                                                                                                                         |  |

| Cascade Conversion Gain                 | 22    | 25           |      | dB   |                                                                                                                                                                                                      |  |

| Cascade Input IP3                       | -15.0 | -10.0        |      | dBm  | Cipela Cidahand                                                                                                                                                                                      |  |

| Cascade Noise Figure                    |       | 2.5          |      | dB   | Single Sideband<br>The LNA section may be left unused. Power                                                                                                                                         |  |

| First Section (LNA)                     |       |              |      |      | is not connected to pin 1. The performance<br>is then as specified for the Second Section<br>(Mixer).                                                                                                |  |

| Noise Figure                            |       | 1.4          |      | dB   |                                                                                                                                                                                                      |  |

| Input VSWR                              |       | <2:1         |      |      | Input is internally matched for optimum noise figure from a $50\Omega$ source.                                                                                                                       |  |

| Input IP3                               |       | +5.5         |      | dBm  | IP3 may be increased 10dB by connecting<br>pin 22 to $V_{CC}$ through the matching inductor.<br>The LNA's current then increases by 10mA.<br>Other in-between IP3 vs. I <sub>CC</sub> trade-offs may |  |

| Gain                                    |       | 12           |      | dB   | be made. See pin description for pin 20.                                                                                                                                                             |  |

| Reverse Isolation                       |       | 23           |      | dB   |                                                                                                                                                                                                      |  |

| Output VSWR                             |       | <1.5:1       |      | üD   |                                                                                                                                                                                                      |  |

| Second Section (Mixer)                  |       |              |      |      | With $1 k\Omega$ balanced load.                                                                                                                                                                      |  |

| Noise Figure                            |       | 5.5          |      | dB   | Single Sideband                                                                                                                                                                                      |  |

| Input VSWR                              |       | 1.5:1        |      | -    | 3                                                                                                                                                                                                    |  |

| Input IP3                               |       | -0.5         |      | dBm  |                                                                                                                                                                                                      |  |

| Conversion Gain                         |       | 15.5         |      | dB   |                                                                                                                                                                                                      |  |

| Output Impedance                        |       | 1            |      | kΩ   | Balanced                                                                                                                                                                                             |  |

| LO Input                                |       |              |      |      |                                                                                                                                                                                                      |  |

| LO Input Range                          |       | -5 to +3     |      | dBm  |                                                                                                                                                                                                      |  |

| LO Output Level                         |       | -4           | +1   | dBm  | Buffer On, -2dBm input                                                                                                                                                                               |  |

|                                         |       | -25          | -20  | dBm  | Buffer Off, -2dBm input                                                                                                                                                                              |  |

| LO to RF (Mix In) Rejection             |       | 30           |      | dB   |                                                                                                                                                                                                      |  |

| LO to IF1, IF2 Rejection                |       | 20           |      | dB   |                                                                                                                                                                                                      |  |

| LO Input VSWR                           |       | <2:1         |      |      | Single ended                                                                                                                                                                                         |  |

| Power Supply                            |       |              |      |      |                                                                                                                                                                                                      |  |

| Voltage                                 | 2.7   | 3.6±5%       | 5.0  | V    |                                                                                                                                                                                                      |  |

| Current Consumption                     |       | 5            |      | mA   | LNA only                                                                                                                                                                                             |  |

|                                         |       | 52           |      | mA   | LNA + Mixer, LO Buffer On                                                                                                                                                                            |  |

|                                         |       | 48           |      | mA   | LNA + Mixer, LO Buffer Off                                                                                                                                                                           |  |

| Pin | Function       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Interface Schematic |

|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 1   | NC             | No connection. This pin may be grounded (recommended) or left open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     |

| 2   | VCC1           | Supply voltage for the mixer and RF buffer amplifier. External RF bypassing is required. The trace length between the pin and the bypass capacitor should be minimized. The ground side of the bypass capacitor should connect immediately to ground plane.                                                                                                                                                                                                                                                                                                                       |                     |

| 3   | VCC2           | Supply voltage for the LNA. External RF bypassing is required. The trace length between the pin and the bypass capacitor should be mini-<br>mized. The ground side of the bypass capacitor should connect imme-<br>diately to ground plane.                                                                                                                                                                                                                                                                                                                                       |                     |

| 4   | GND1           | Ground connection for the LNA. For best performance, keep traces physically short and connect immediately to ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |

| 5   | LNA IN         | RF Input pin for the LNA. This pin is internally DC-blocked and internally matched for minimum noise figure (NOT for minimum VSWR), given a $50\Omega$ source impedance.                                                                                                                                                                                                                                                                                                                                                                                                          |                     |

| 6   | GND2           | Same as pin 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     |

| 7   | GND3           | Ground connection for the RF buffer amplifier. For best performance, keep traces physically short and connect immediately to ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |

| 8   | NC             | No connection. This pin may be grounded (recommended) or left open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     |

| 9   | GND4           | Same as pin 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     |

| 10  | VCC3           | Supply voltage for both LO buffer amplifiers. External RF bypassing is required. The trace length between the pin and the bypass capacitor should be minimized. The ground side of the bypass capacitor should connect immediately to ground plane.                                                                                                                                                                                                                                                                                                                               |                     |

| 11  | LO BUFF<br>EN  | Enable pin for the LO output buffer amplifier. This is a digitally controlled input. A logic "high" ( $\geq$ 3.1V) turns the buffer amplifier on, and the current consumption increases by 3mA (with -2dBm LO input). A logic "low" ( $\leq$ 0.5V) turns the buffer amplifier off.                                                                                                                                                                                                                                                                                                | LO<br>BUFF O<br>EN  |

| 12  | LO IN          | Mixer LO input pin. This pin is internally DC-blocked and matched to $50\Omega$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |

| 13  | LO BUFF<br>OUT | Optional buffered LO output. This pin is internally DC-blocked and matched to $50\Omega$ . The buffer amplifier is switched on or off by the voltage level at pin 11.                                                                                                                                                                                                                                                                                                                                                                                                             |                     |

| 14  | GND5           | Ground connection for both LO buffer amplifiers. For best performance, keep traces physically short and connect immediately to ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                      |                     |

| 15  | IF+            | Open-collector IF output pin. This is a balanced output. The output impedance is set by an internal $1000\Omega$ resistor to pin 16. Thus the differential IF output impedance is $1000\Omega$ . The resistor sets the operating impedance, but an external choke or matching inductor to $V_{CC}$ must be supplied in order to bias this output. This inductor is typically incorporated in the matching network between the output and IF filter. Because this pin is biased to $V_{CC}$ , a DC blocking capacitor must be used if the IF filter input has a DC path to ground. |                     |

| 16  | IF-            | Same as pin 15, except complementary output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | See pin 15.         |

| 17  | GND6           | Ground connection for the mixer. For best performance, keep traces physically short and connect immediately to ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                     |

| 18  | MIX RF IN      | Mixer RF Input Pin. This pin is internally DC-blocked and matched to 50 $\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                     |

| 19  | GND7           | Same as pin 17.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |

| Pin | Function | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Interface Schematic |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 20  | LNA OUT  | LNA output pin. This is an open-collector output. This pin is typically connected to pin 22 through a bias/matching inductor. This inductor, in conjunction with a series blocking/matching capacitor, forms a matching network to the 50 $\Omega$ image filter and provides bias (see Application Schematic). The LNA's IP3 may be increased 10dB by connecting pin 20 to V <sub>CC</sub> through the inductor. The LNA's current then increases by 10mA. Other in-between IP3 vs. I <sub>CC</sub> trade-offs may be made by connecting resistance values between V <sub>CC</sub> and the matching inductor. The two reference points for consideration are with 150 $\Omega$ used, which is what connection to pin 22 achieves, the Input IP3 is +15.5 dBm and the LNA I <sub>CC</sub> is 5mA. Using no resistance, the Input IP3 is +15.5 dBm and the LNA I <sub>CC</sub> is 15 mA. Desired operating points in between these values may be interpolated, roughly. |                     |

| 21  | GND8     | Same as pin 17.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                     |

| 22  | VCC4     | Output supply voltage for the LNA output (pin 20). This pin is typically connected to pin 20 through a bias/matching inductor (see application schematic). External RF bypassing is required. The trace length between the pin and the bypass capacitor should be minimized. The ground side of the bypass capacitor should connect immediately to ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | See pin 2.          |

| 23  | GND9     | Same as pin 17.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                     |

| 24  | NC       | No connection. This pin may be grounded (recommended) or left open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |

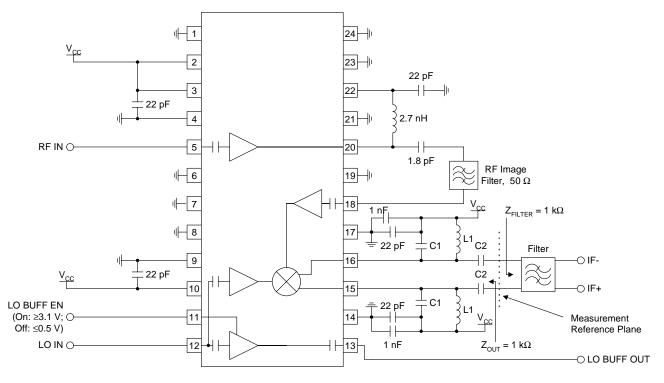

### **Application Schematic**

L1 and C2 serve dual purposes. L1 serves as an output bias choke, and C2 serves as a series DC block. In addition, the values of L1 and C2 may be chosen to form an impedance matching network if the IF filter's input impedance is not 1000  $\Omega$ . Otherwise, the values of L1 and C1 are chosen to form a parallel-resonant tank circut at the IF when the IF filter's input impedance is 1000  $\Omega$ .

- C11 is selected to fine tune L4 for IF output match at 210 MHz.

R3 is not normally populated. For applications requiring additional LNA IP3, see the datasheet for

- recommended resistance values. 3. C2 and C3 are not normally populated. If C2 and C3 are populated, the LNA and mixer can be tested independently; in this case, C1 and C5 should be removed.

8

**RF9986**

<BUFFER ENABLE

цł

P1-3 ()-3

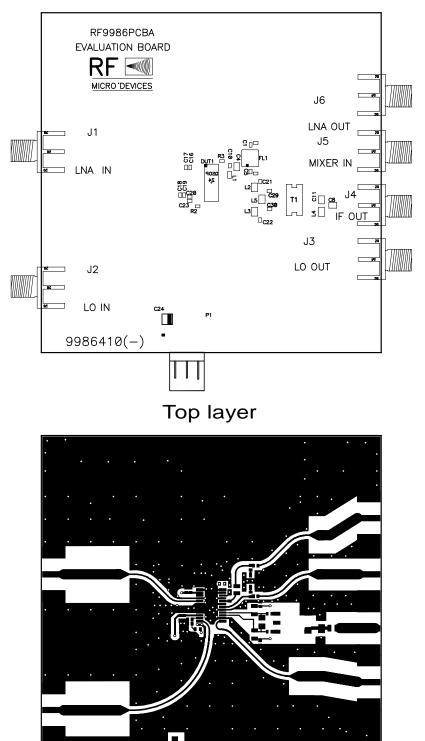

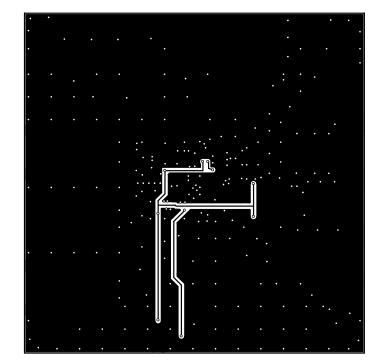

### Evaluation Board Layout 3" x 3" Assembly

FRONT-ENDS

8

## **Bottom Layer**

Internal Ground

Rev B1 010717