# Preliminary

Notice: This is not a final specification. Some parametric limits are subject to change.

# M6MGB/T331S4BKT

33,554,432-BIT (2,097,152 - WORD BY 16-BIT/4,194,304-WORD BY 8-BIT) CMOS 3.3V-ONLY FLASH MEMORY &

4,194,304-BIT (262,144-WORD BY 16-BIT/524,288-WORD BY 8-BIT) CMOS SRAM Stacked - μ MCP (micro Multi Chip Package)

### Description

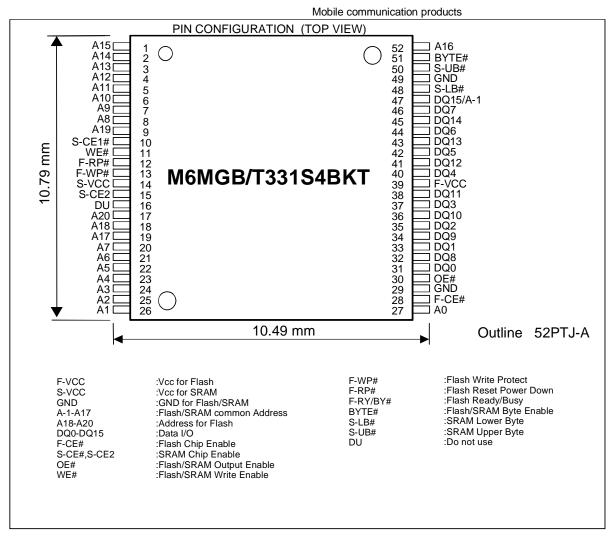

The M6MGB/T331S4BKT is a Stacked micro Multi Chip Package (S-  $\mu$ MCP) that contents 32M-bit Flash memory and 4M-bit Static RAM in a 52-pin TSOP for lead free use.

32M-bit Flash memory is a 4,194,304 bytes / 2,097,152 words, 3.3V-only, and high performance non-volatile memory fabricated by CMOS technology for the peripheral circuit and DINOR (Divided bit-line NOR) architecture for the memory cell.

4M-bit SRAM is a 524,288 bytes / 262,144 words asynchronous SRAM fabricated by silicon-gate CMOS technology.

M6MGB/T331S4BKT is suitable for the application of the mobile-communication-system to reduce both the mount space and weight.

M6MGB/T331S4BKT provides for Software Lock Release function. Usually, all memory blocks are locked and can not be programmed or erased, when F-WP# is low. Using Software Lock Release function, program or erase operation can be executed.

### Features

| Access Time    | Flash   | 70ns (Max.)                |  |  |  |

|----------------|---------|----------------------------|--|--|--|

|                | SRAM    | 70ns (Max.)                |  |  |  |

| Supply Voltage |         | VCC=2.7 ~ 3.0V             |  |  |  |

| Ambient Tempe  | erature | Ta=-40 ~ 85 °C             |  |  |  |

| Package        |         | 52pin TSOP(Type-II),       |  |  |  |

|                |         | Lead pitch 0.4mm           |  |  |  |

|                |         | Outer-lead finishing:Sn-Cu |  |  |  |

### Application

1

**Preliminary** Notice: This is not a final specification. **Renesas LSIs**

Some parametric limits are subject to change.

# M6MGB/T331S4BKT

33,554,432-BIT (2,097,152 - WO

33,554,432-BIT (2,097,152 - WORD BY 16-BIT/4,194,304-WORD BY 8-BIT) CMOS 3.3V-ONLY FLASH MEMORY & 4,194,304-BIT (262,144-WORD BY 16-BIT/524,288-WORD BY 8-BIT) CMOS SRAM Stacked - μ MCP (micro Multi Chip Package)

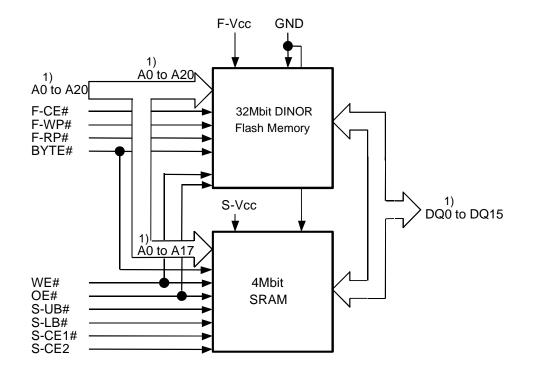

## **MCP Block Diagram**

Note 1): In case of x8 organization, A-1 is added, and only Lower Byte data(DQ0 to DQ7) are assigned to I/O and Upper Byte data(DQ8 to DQ15) are High-Z.

Note 2): In the flash memory part there are "VCC"s which mean "F-VCC".

In the SRAM part there are "UB#" and "LB#" which mean "S-UB#" and "S-UB#", respectively.

Note 3): "DU(Don't Use)" pin must be OPEN ,otherwise be inputted within 0V ~ Vcc.

### Capacitance

| Symbol | Parameter             |                                                                              | Conditions                         | Limits |      |      | Unit |

|--------|-----------------------|------------------------------------------------------------------------------|------------------------------------|--------|------|------|------|

| Cymbol |                       |                                                                              |                                    | Min.   | Тур. | Max. | Onic |

| CIN    | Input capacitance     | A20-A0, OE#, WE#, F-CE#, F-WP#, F-RP#,<br>S-CE1#, S-CE2, BYTE#, S-LB#, S-UB# | Ta=25°C,<br>f=1MHz,<br>Vin=Vout=0V |        |      | 18   | pF   |

| СОИТ   | Output<br>Capacitance | DQ15-DQ0                                                                     |                                    |        |      | 22   | pF   |

**Renesas LSIs**

# M6MGB/T331S4BKT

33,554,432-BIT (2,097,152 - WORD BY 16-BIT/4,194,304-WORD BY 8-BIT) CMOS 3.3V-ONLY FLASH MEMORY & 4,194,304-BIT (262,144-WORD BY 16-BIT/524,288-WORD BY 8-BIT) CMOS SRAM Stacked - μ MCP (micro Multi Chip Package)

# RenesasTechnologyCorp.

Nippon Bldg.,6-2,Otemachi 2-chome,Chiyoda-ku,Tokyo,100-0004 Japan

# Keep safety first in your circuit designs! • Reepsa Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to material or ingervention against ary malfunction or mishap. • Notes regarding these materials • Notes regarding these materials are intended as a reference to assist our customers in the selection of the Renessas Technology Corporation product best suited to the customer's application; they do not convey any license under any intellectual property rights, can any other rights, becinging to Renessas Technology Corporation or a third party. • Anisomatic contained in these materials. • Anisomatic contained in these materials, including product data, diagrams, charts, programs, and agortithms represents infomation on products at the time of publication of these materials, and are subject to change by Renessas Technology Corporation motion uncode due to poduit improvements or other reasons. It is therefore recommended that customers contact Renessas Technology Corporation on saturbrized Renessas Technology Corporation product distributor for the latest product information on totasing a product listed herein. • The information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sup a technology Corporation motion uncodes or toporation product listed hereins. • The information adjust the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a tubal system before making a final decision on the applicability of the information contrained in these materials, including produc