# HD61202 (Dot Matrix Liquid Crystal Graphic Display Column Driver)

# Description

HD61202 is a column (segment) driver for dot matrix liquid crystal graphic display systems. It stores the display data transferred from a 8-bit micro controller in the internal display RAM and generates dot matrix liquid crystal driving signals.

Each bit data of display RAM corresponds to the on/off state of a dot of a liquid crystal display to provide more flexible than character display.

As it is internally equipped with 64 output drivers for display, it is available for liquid crystal graphic display with many dots.

The HD61202, which is produced in the CMOS process, can complete portable battery drive equipment in combination with a CMOS microcontroller, utilizing the liquid crystal display's low power dissipation.

Moreover it can facilitate dot matrix liquid crystal graphic display system configuration in combination with the row (common) driver HD61203.

#### **Features**

- Dot matrix liquid crystal graphic display column driver incorporating display RAM

- RAM data direct display by internal display RAM

- RAM bit data 1: On RAM bit data 1: Off

- Internal display RAM address counter preset, increment

- Display RAM capacity: 512 bytes (4096 bits)

- 8-bit parallel interface

- Internal liquid crystal display driver circuit: 64

- Display duty cycle:

Drives liquid crystal panels with 1/32-1/64 duty cycle multiplexing

- Wide range of instruction function: Display Data Read/Write, Display On/Off, Set Address, Set Display Start Line, Read Status

- Lower power dissipation: during display 2 mW max

- Power supply:  $V_{CC}$ : 5 V ± 10%

- Liquid crystal display driving voltage: 8 V to 17.0 V

- CMOS process

# **Ordering Information**

| Type No.    | Package                          |

|-------------|----------------------------------|

| HD61202     | 100-pin plastic QFP(FP-100)      |

| HD61202TFIA | 100-pin thin plastic QFP(TFP-60) |

| HD61202D    | Chip                             |

HITACHI

580

4496204 0046376 DTT **=**

# **Absolute Maximum Ratings**

| Item                  | Symbol                               | Value                                          | Unit | Note |

|-----------------------|--------------------------------------|------------------------------------------------|------|------|

| Supply voltage        | V <sub>cc</sub>                      | -0.3 to +7.0                                   | V    | 2    |

|                       | V <sub>EE1</sub><br>V <sub>EE2</sub> | V <sub>CC</sub> -19.0 to V <sub>CC</sub> + 0.3 | V    | 3    |

| Terminal voltage (1)  | V <sub>T1</sub>                      | V <sub>EE</sub> - 0.3 to V <sub>CC</sub> + 0.3 |      | 4    |

| Terminla voltage (2)  | V <sub>T2</sub>                      | -0.3 to V <sub>CC</sub> + 0.3                  | v    | 2.5  |

| Operating temperature | Topr                                 | -20 to +75                                     | °C   |      |

| Storage temperature   | Tstg                                 | -55 to +125                                    | °C   |      |

- Notes: 1. LSIs may be destroyed if they are used beyond the absolute maximum ratings. In ordinary operation, it is desirable to use them within the recommended operation conditions.

- Using them beyond these conditions may cause malfunction and poor reliability.

- 2. All voltage values are referenced to GND = 0 V.

- Apply the same supply voltage to V<sub>EE1</sub> and V<sub>EE2</sub>.

- 4. Applies to V1L, V2L, V3L, V4L, V1R, V2R, V3R, and V4R.

- V<sub>CC</sub> ≥ V1L = V1R ≥ V3L = V3R ≥ V4L = V4R ≥ V2L = V2R ≥ V<sub>EE</sub>

- 5. Applies to M, FRM, CL, RST, ADC, \$1, \$2, \overline{CS1}, \overline{CS2}, CS3, E, R/W, D/I, and DB0-DB7.

HITACHI

4496204 0046377 T36

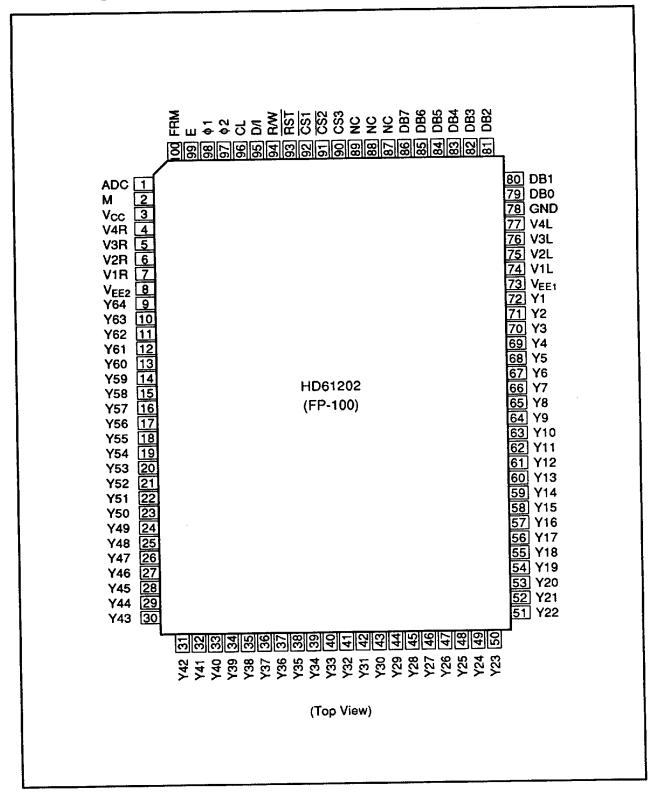

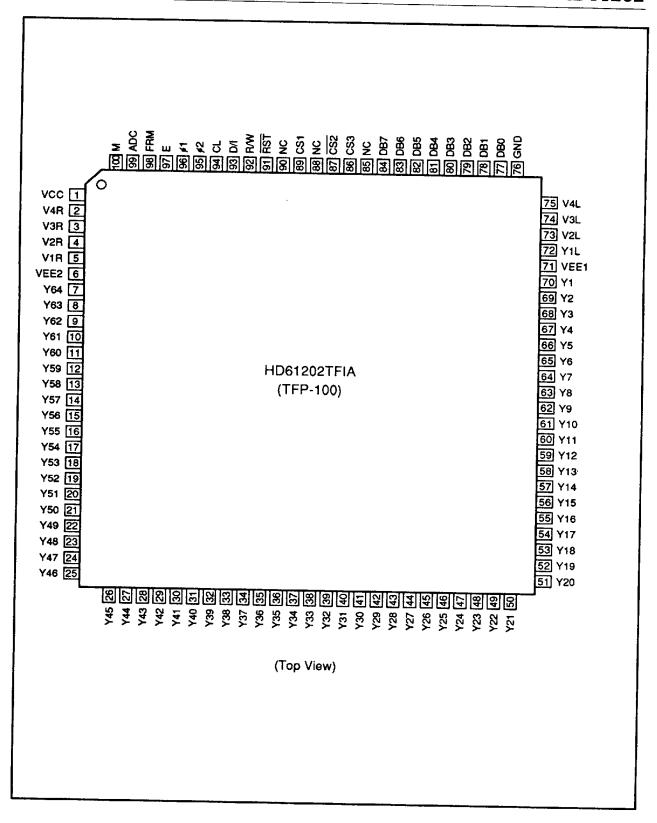

#### Pin Arrangement

HITACHI

**4496204 0046378 972**

#### **HITACHI**

583

**4**496204 0046379 809 **5**

# **Electrical Characteristics** (GND = 0 V, $V_{CC}$ = 4.5 to 5.5 V, $V_{CC} - V_{EE}$ = 8 to 17.0 V, Ta = -20 to +75°C)

|                                       |                     |                       | Limit |                       |      |                                                                     |        |

|---------------------------------------|---------------------|-----------------------|-------|-----------------------|------|---------------------------------------------------------------------|--------|

| Item                                  | Symbol              | Min                   | Тур   | Max                   | Unit | Test Condition                                                      | Note   |

| Input high voltage                    | V <sub>IHC</sub>    | 0.7 × V <sub>CC</sub> | _     | V <sub>CC</sub>       | ٧    |                                                                     | 1      |

| , -                                   | V <sub>IHT</sub>    | 2.0                   | _     | Vcc                   | ٧    |                                                                     | 2      |

| Input low voltage                     | V <sub>ILC</sub>    | 0                     |       | 0.3 × V <sub>CC</sub> | ٧    |                                                                     | 1      |

| ,                                     | V <sub>ILT</sub>    | 0                     | _     | 0.8                   | ٧    |                                                                     | 2      |

| Output high voltage                   | V <sub>OH</sub>     | 2.4                   |       |                       | ٧    | l <sub>OH</sub> = -205 μA                                           | 3      |

| Output low voltage                    | Vol                 | _                     |       | 0.4                   | ٧    | I <sub>OL</sub> = 1.6 mA                                            | 3      |

| Input leakage current                 | I <sub>IL</sub>     | -1.0                  |       | +1.0                  | μΑ   | Vin = GND-V <sub>CC</sub>                                           | 4      |

| Three-state (off) input current       | ITSL                | -5.0                  | _     | +5.0                  | μА   | $Vin = GND-V_{CC}$                                                  | 5      |

| Liquid crystal supply leakage current | I <sub>LSL</sub>    | -2.0                  |       | +2.0                  | μА   | Vin = V <sub>EE</sub> -V <sub>CC</sub>                              | 6      |

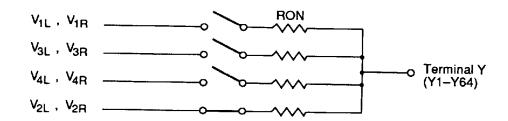

| Driver on resistance                  | R <sub>ON</sub>     | -                     |       | 7.5                   | kΩ   | $V_{CC} - V_{EE} = 15 \text{ V}$<br>$\pm I_{LOAD} = 0.1 \text{ mA}$ | 8      |

| Dissipation current                   | I <sub>CC</sub> (1) |                       |       | 100                   | μΑ   | During display                                                      | 7      |

|                                       | I <sub>CC</sub> (2) |                       |       | 500                   | μА   | During access<br>access cycle = 1 MHz                               | 7<br>z |

- Notes: 1. Applies to M, FRM, CL, RST, \$1, and \$2.

- Applies to CS1, CS2, CS3, E, R/W, D/I, and DB0-DB7. 2.

- Applies to DB0-DB7.

- 4. Applies to terminals except for DB0-DB7.

- 5. Applies to DB0-DB7 at high impedance.

- 6. Applies to V1L-V4L and V1R-V4R.

- Specified when liquid crystal display is in 1/64 duty cycle mode.

Operation frequency

f<sub>CLK</sub> = 250 kHz (\phi1 and \phi2 frequency)

Frame frequency

f<sub>M</sub> = 70 Hz (FRM frequency)

Specified in the state of

Output terminal: not loaded Input level:  $V_{H} = V_{CC}(V)$

$VI_L = GND(V)$

Measured at V<sub>CC</sub> terminal

8. Resistance between terminal Y and terminal V (one of V1L, V1R, V2L, V2R, V3L, V3R, V4L, and V4R) when load current flows through one of the terminals Y1 to Y64. This value is specified under the following condition:

HITACHI

584

4496204 0046380 520

$$\begin{aligned} & V_{CC} - V_{EE} = 15.5 \text{ V} \\ V_{1L} &= V_{1R}, \ V_{3L} = V_{3R} = V_{CC} - 2/7 \ (V_{CC} - V_{EE}) \\ V_{2L} &= V_{2R}, \ V_{4L} = V_{4R} = V_{CC} + 2/7 \ (V_{CC} - V_{EE}) \end{aligned}$$

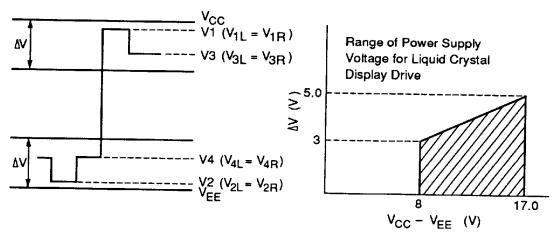

The following is a description of the range of power supply voltage for liquid crystal display drive. Apply positive voltage to V1L = V1R and V3L = V3R and negative voltage to V2L = V2R and V4L = V4R within the  $\Delta V$  range. This range allows stable impedance on driver output (RON). Notice that  $\Delta V$  depends on power supply voltage  $V_{CC} - V_{EE}$ .

Correlation between Driver Output Waveform and Power Supply Voltages for Liquid Crystal Display Drive

Correlation between Power Supply Voltage V<sub>CC</sub>- V<sub>EE</sub> and ΔV

HITACHI

4496204 0046381 467 📟

# Terminal Configuration

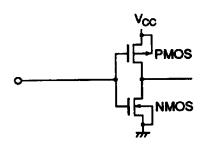

#### Input Terminal

Applicable terminals:

M, FRM, CL, RST, \$1, \$2, \overline{CS1}, \overline{CS2}, \overline{CS3}, E, R/W, D/I, ADC

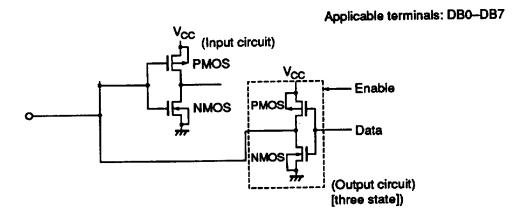

#### Input/Output Terminal

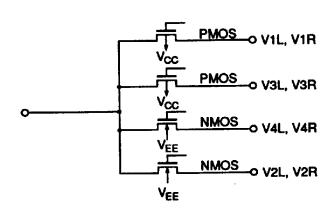

#### **Output Terminal**

Applicable Terminals: Y1-Y64

HITACHI

💻 4496204 0046382 3T3 💳

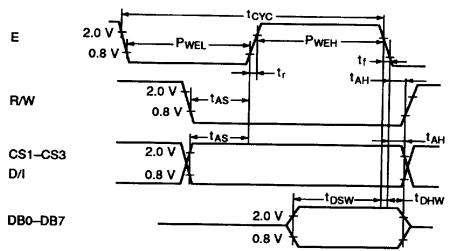

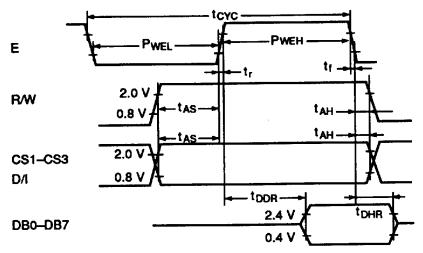

# Interface AC Characteristics

MPU Interface

(GND = 0 V,  $V_{CC}$  = 4.5 to 5.5 V, Ta = -20 to +75°C)

| Item                   | Symbol           | Min  | Тур         | Max         | Unit | Note |

|------------------------|------------------|------|-------------|-------------|------|------|

| E cycle time           | tcyc             | 1000 |             |             | ns   | 1, 2 |

| E high level width     | P <sub>WEH</sub> | 450  | _           | _           | ns   | 1, 2 |

| E low level width      | P <sub>WEL</sub> | 450  | _           |             | ns   | 1, 2 |

| E rise time            | tr               |      | _           | 25          | ns   | 1, 2 |

| E fall time            | tf               |      | <del></del> | 25          | ns   | 1, 2 |

| Address setup time     | t <sub>AS</sub>  | 140  | _           |             | ns   | 1, 2 |

| Address hold time      | taH              | 10   | _           | <del></del> | ns   | 1, 2 |

| Data setup time        | t <sub>DSW</sub> | 200  |             |             | ns   | 1    |

| Data delay time        | t <sub>DDR</sub> |      | _           | 320         | ns   | 2, 3 |

| Data hold time (Write) | tDHW             | 10   |             |             | ns   | 1    |

| Data hold time (Read)  | t <sub>DHR</sub> | 20   | _           |             | ns   | 2    |

#### Notes: 1.

Figure 1 CPU Write Timing

**HITACHI**

■ 1496204 0046383 23T **■**

#### Notes: 2.

Figure 2 CPU Read Timing

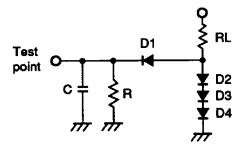

#### 3. DB0-DB7: load circuit

RL = 2.4 k  $\Omega$ R = 11 k  $\Omega$ C = 130 pF (including jig capacitance) Diodes D1–D4 are all 1S2074  $\bigoplus$ .

HITACHI

588

u496204 0046384 176 **=**

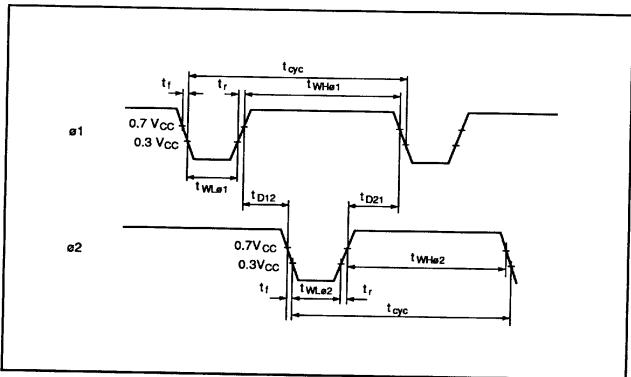

# Clock Timing (GND = 0 V, $V_{CC}$ = 4.5 to 5.5 V, Ta = -20 to +75°C)

|                          |                   |      | Limit |     |      |                |

|--------------------------|-------------------|------|-------|-----|------|----------------|

| Item                     | Symbol            | Min  | Тур   | Max | Unit | Test Condition |

| ♦1, ♦2 cycle time        | tcyc              | 2.5  |       | 20  | μs   | Fig. 3         |

| ♦1 low level width       | tWL+1             | 625  |       | _   | ns   | Fig. 3         |

| ♦2 low level width       | twL+2             | 625  |       |     | ns   | Fig. 3         |

| ♦1 high level width      | tw+++             | 1875 |       |     | ns   | Fig. 3         |

| ♦2 high level width      | t <sub>WH+2</sub> | 1875 |       |     | ns   | Fig. 3         |

| ♦1—♦2 phase difference   | t <sub>D12</sub>  | 625  |       |     | ns   | Fig. 3         |

| +2+1 phase difference    | t <sub>D21</sub>  | 625  |       |     | ns   | Fig. 3         |

| ♦1, <b>♦</b> 2 rise time | tr                |      |       | 150 | ns   | Fig. 3         |

| ♦1, ♦2 fall time         | tf                |      |       | 150 | ns   | Fig. 3         |

Figure 3 External Clock Waveform

HITACHI

4496204 0046385 002 1

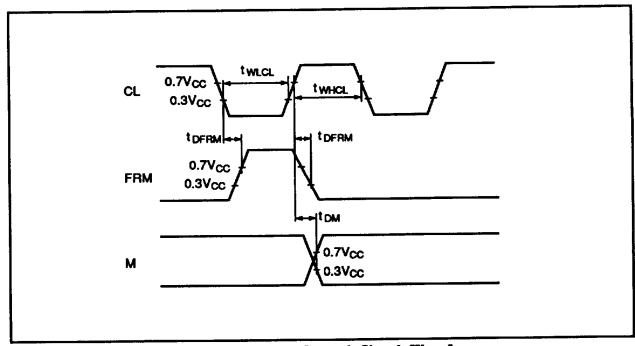

Display Control Timing (GND = 0V,  $V_{CC}$  = 4.5 to 5.5 V, Ta = -20 to +75 °C)

|                     |                   |     | Limit |     |      |                |

|---------------------|-------------------|-----|-------|-----|------|----------------|

| Item                | Symbol            | Min | Тур   | Max | Unit | Test Condition |

| FRM delay time      | <sup>†</sup> DFRM | -2  | -     | +2  | με   | Fig. 4         |

| M delay time        | † <sub>DM</sub>   | -2  |       | +2  | με   | Fig. 4         |

| CL low level width  | twlcl             | 35  | _     |     | ħs   | Fig. 4         |

| CL high level width | twict.            | 35  | _     | -   | με   | Fig. 4         |

Figure 4 Display Control Signal Waveform

HITACHI

**3** 4496204 0046386 T49

591

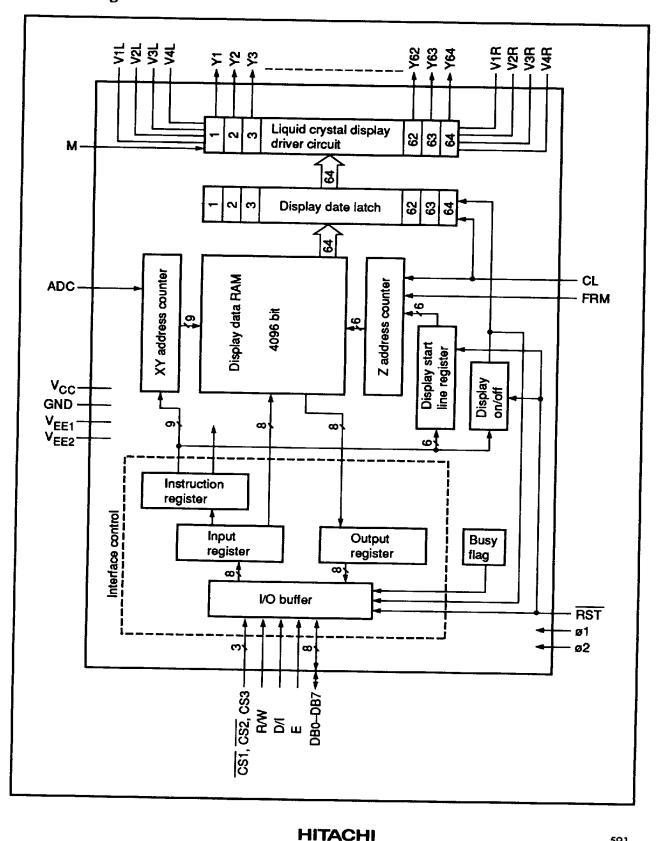

# **Block Diagram**

4496204 0046387 985 |

This Material Copyrighted By Its Respective Manufacturer

# **Terminal Functions**

| Terminai<br>Name     | Number of<br>Terminals | 1/0 | Connected to | Functions                                     |                     |                                                                      |                                         |

|----------------------|------------------------|-----|--------------|-----------------------------------------------|---------------------|----------------------------------------------------------------------|-----------------------------------------|

| V <sub>CC</sub>      | 2                      |     | Power        | Power supply for                              | internal            | logic.                                                               |                                         |

| GND                  |                        |     | supply       | Recommended v                                 | oltage is           | •                                                                    |                                         |

|                      |                        |     |              | GND = 0 V<br>V <sub>CC</sub> = 5 V ±10        | 1%                  |                                                                      |                                         |

| V <sub>EE1</sub>     | 2                      |     | Power        | Power supply for                              | r liquid cr         | ystal display drive                                                  | circuit.                                |

| V <sub>EE2</sub>     |                        |     | supply       | V. Connect the s                              | ame pow             | oply voltage is $V_{CC}$ er supply to $V_{EE1}$ ed each other in the | and V <sub>EE2</sub> . V <sub>EE1</sub> |

| V1L, V1R             | 8                      |     | Power        | Power supply for                              | r liquid cr         | ystal display drive                                                  | •                                       |

| V2L, V2R<br>V3L, V3R |                        |     | supply       | Apply the voltage within the limit of         |                     | ed depending on li<br>lugh V <sub>CC</sub> .                         | quid crystals                           |

| V4L, V4R             |                        |     |              |                                               |                     | : Selection level<br>: Non-selection le                              | vel                                     |

|                      |                        |     |              | Power supplies of V3L & V3R, V4L              | connected<br>& V4R) | d with V1L and V1I should have the sa                                | R (V2L & V2R,<br>me voltages.           |

| CS1                  | 3                      | ı   | MPU          | Chip selection.                               | _                   |                                                                      |                                         |

| CS2<br>CS3           |                        |     |              | Data can be inputolities following conditions |                     | ut when the termin                                                   | als are in the                          |

|                      |                        |     |              | Terminal Name                                 | CS                  | 51 CS2                                                               | CS3                                     |

|                      |                        |     |              | Condition                                     | L                   | L                                                                    | Н                                       |

| E                    | 1                      | 1   | MPU          | Enable.                                       |                     |                                                                      |                                         |

|                      |                        |     |              | At write(R/W                                  | = Low):             | Data of DB0 to D<br>the fall of E.                                   | B7 is latched at                        |

|                      |                        |     |              | At read(R/W                                   | = High):            | Data appears at E is at high level                                   |                                         |

| RW                   | 1                      | Ι   | MPU          | Read/write.                                   |                     |                                                                      |                                         |

|                      |                        |     |              | R/W = High:                                   | read by             | opears at DB0 to D<br>the CPU.<br>E = high, CS1, CS2                 |                                         |

|                      |                        |     |              | R/W = Low:                                    | DB0 to              | DB7 can accept a S2 = low and CS3                                    | t fall of E when<br>= high.             |

| D/I                  | 1                      | ı   | MPU          | Data/instruction                              | ١.                  |                                                                      |                                         |

|                      |                        |     |              | D/I = High:                                   | Indicate<br>display | es that the data of<br>data.                                         | DB0 to DB7 is                           |

|                      |                        |     |              | D/i = Low:                                    |                     | es that the data of control data.                                    | DB0 to DB7 is                           |

HITACHI

592

444P5O4 OO4P388 8JJ 🚃

# Terminal Functions (cont)

| Terminal<br>Name | Number of<br>Terminals |     | Connected<br>to      | d<br>Functions                                                                                                                             |

|------------------|------------------------|-----|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

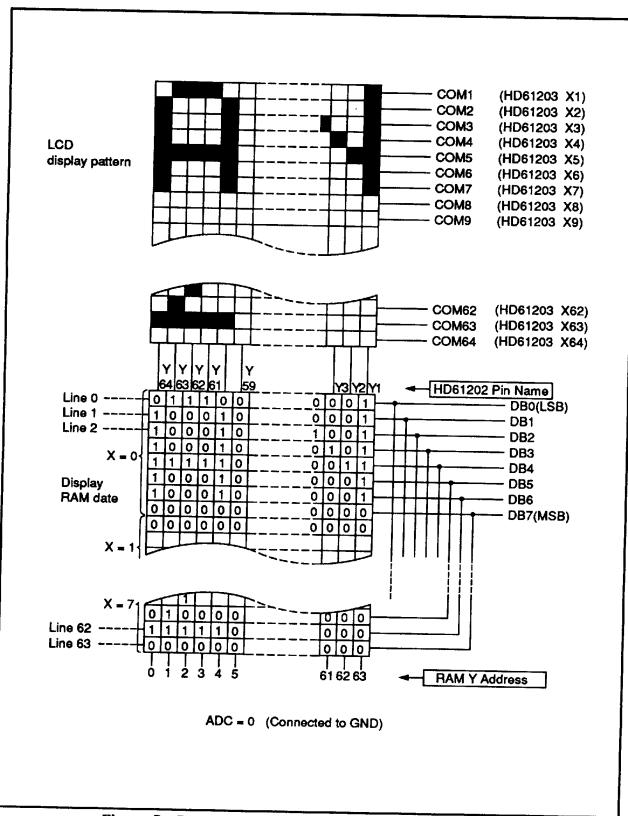

| ADC              | 1                      | I   | V <sub>CC</sub> /GND | Address control signal to determine the relation between Y address of display RAM and terminals from which the data is output.             |

|                  |                        |     |                      | ADC = High: Y1: \$0, Y64: \$63<br>ADC = Low: Y64: \$0, Y1: \$63                                                                            |

| DB1-DB7          | 8                      | 1/0 | MPU                  | Data bus, three-state I/O common terminal.                                                                                                 |

| M                | 1                      | ı   | HD61203              | Switch signal to convert liquid crystal drive waveform into AC.                                                                            |

| FRM              | 1                      | 1   | HD61203              | Display synchronous signal (frame signal).                                                                                                 |

|                  |                        |     |                      | Presets the 6-bit display line counter and synchronizes the common signal with the frame timing when the FRM signal becomes high.          |

| CL               | 1                      | l   | HD61203              | Synchronous signal to latch display data. The rising CL signal increments the display output address counter and latches the display data. |

| <b>♦1, ♦2</b>    | 2                      | 1   | HD61203              | 2-phase clock signal for internal operation.                                                                                               |

|                  |                        |     |                      | The \$1 and \$2 clocks are used to preform operations (I/O of display data and execution of instructions) other than display.              |

| Y1-Y64           | 64                     | 0   | Liquid               | Liquid crystal display column (segment) drive output.                                                                                      |

|                  |                        |     | crystal<br>display   | These pins outputs light on level when 1 is in the display RAM, and light off level when 0 is it.                                          |

|                  |                        |     |                      | Relation among output level, M, and display data (D) is as follows:                                                                        |

|                  |                        |     |                      | M 1 0                                                                                                                                      |

|                  |                        |     |                      | D 1 0 1 0                                                                                                                                  |

|                  |                        |     |                      | Output V1 V3 V2 V4                                                                                                                         |

| RST              | 1                      | ı   | CPU or external CR   | The following registers can be initialized by setting the RST signal to low level.                                                         |

|                  |                        |     |                      | <ol> <li>On/off register 0 set (display off)</li> </ol>                                                                                    |

|                  |                        |     |                      | <ol> <li>Display start line register line 0 set (displays from line 0)</li> </ol>                                                          |

| ·                |                        |     |                      | After releasing reset, this condition can be changed only by instruction.                                                                  |

| NC               | 3                      |     | Open                 | Unused terminals. Don't connect any lines to these terminals.                                                                              |

Note: 1 corresponds to high level in positive logic.

**HITACHI**

593

**4496204 0046389 758**

#### **Function of Each Block**

#### Interface Control

#### 1. I/O buffer

Data is transferred through 8 data bus lines (DB0-DB7).

MSB (Most significant bit) DB7: LSB (Least significant bit) DB0:

Data can neither be input nor output unless CS1 to CS3 are in the active mode. Therefore, when CS1 to CS3 are not in active mode it is useless to switch the signals of input terminals except RST and ADC; that is namely, the internal state is maintained and no instruction excutes. Besides, pay attention to RST and ADC which operate irrespectively of  $\overline{CS1}$  to CS3.

#### Register

Both input register and output register are provided to interface to an MPU whose speed is different from that of internal operation. The selection of these registers depend on the combination of R/W and D/I signals (table 1).

#### a. Input register

The input register is used to store data temporarily before writing it into display data RAM.

The data from MPU is written into the input register, then into display data RAM automatically by internal operation. When CSI to CS3 are in the active mode and D/I and R/W select the input register as shown in table 1, data is latched at the fall of the E signal.

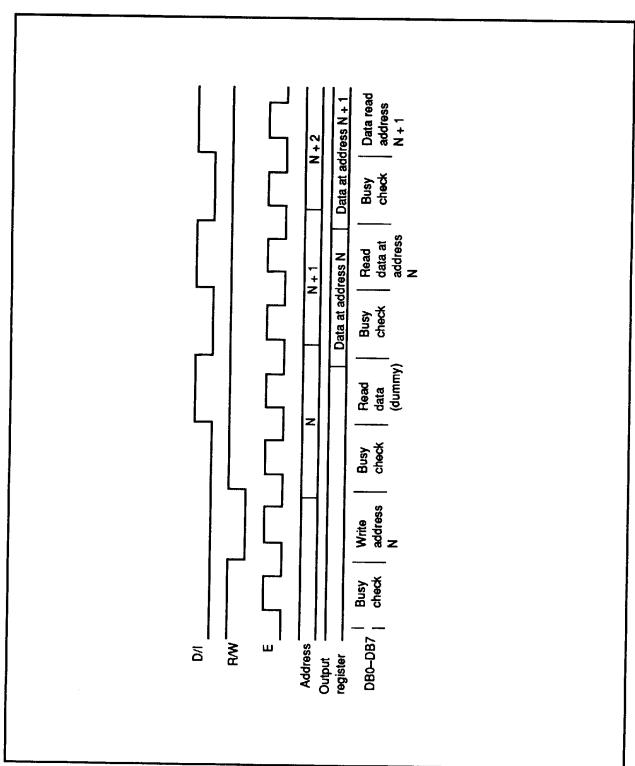

#### b. Output register

The output register is used to store data temporarily that is read from display data RAM. To read out the data from output register, CSI to CS3 should be in the active mode and both D/I and R/W should be 1. With the read display data instruction, data stored in the output register is output while E is high level. Then, at the fall of E, the display data at the indicated address is latched into the output register and the address is increased by 1.

The contents in the output register are rewritten by the read display data instruction, but are held by address set instruction, etc.

Therefore, the data of the specified address cannot be output with the read display data instruction right after the address is set, but can be output at the second read of data. That is to say, one dummy read is necessary. Figure 5 shows the CPU read timing.

Table 1 Register Selection

| D/I | R/W | Operation                                                                                    |

|-----|-----|----------------------------------------------------------------------------------------------|

| 1   | 1   | Reads data out of output register as internal operation (display data RAM → output register) |

| 1   | 0   | Writes data into input register as internal operation (input register → display data RAM)    |

| 0   | 1   | Busy check. Read of status data.                                                             |

| 0   | 0   | Instruction                                                                                  |

HITACHI

594

4496204 0046390 477 🚥

Figure 5 CPU Read Timing

HITACHI

595

**III** 4496204 004639**% 30**6 **III**

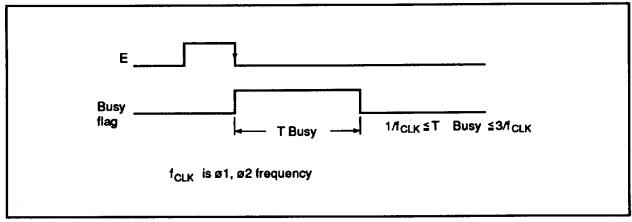

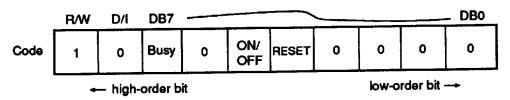

#### **Busy Flag**

Busy flag = 1 indicates that HD61202 is operating and no instructions except status read instruction can be accepted. The value of the busy flag is read

out on DB7 by the status read instruction. Make sure that the busy flag is reset (0) before issuing instructions.

Figure 6 Busy Flag

#### Display On/Off Flip/Flop

The display on/off flip/flop selects one of two states, on state and off state of segments Y1 to Y64. In on state, the display data corresponding to that in RAM is output to the segments. On the other hand, the display data at all segments disappear in off state independent of the data in RAM. It is controlled by display on/off instruction. RST signal = 0 sets the segments in off state. The status of the flip/flop is output to DB5 by status read instruction. Display on/off instruction does not influence data in RAM. To control display data latch by this flip/flop, CL signal (display synchronous signal) should be input correctly.

#### Display Start Line Register

The display start line register specifies the line in RAM which corresponds to the top line of LCD panel, when displaying contents in display data RAM on the LCD panel. It is used for scrolling of the screen.

6-bit display start line information is written into this register by the display start line set instruction. When high level of the FRM signal starts the display, the information in this register is transferred to the Z address counter, which controls the display address, presetting the Z address counter.

#### X. Y Address Counter

A 9-bit counter which designates addresses of the internal display data RAM. X address counter (upper 3 bits) and Y address counter (lower 6 bits) should be set to each address by the respective instructions.

#### 1. X address counter

Ordinary register with no count functions. An address is set by instruction.

#### 2. Y address counter

An address is set by instruction and is increased by 1 automatically by R/W operations of display data. The Y address counter loops the values of 0 to 63 to count.

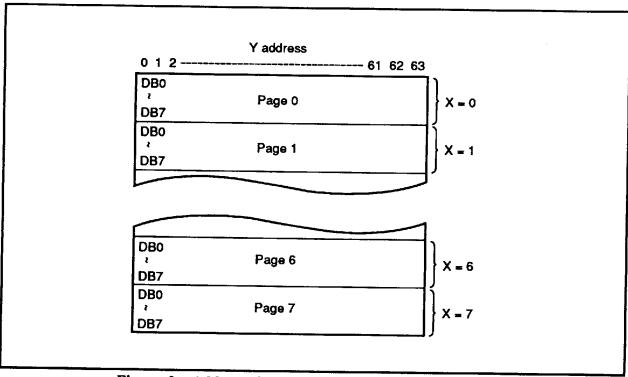

#### Display Data RAM

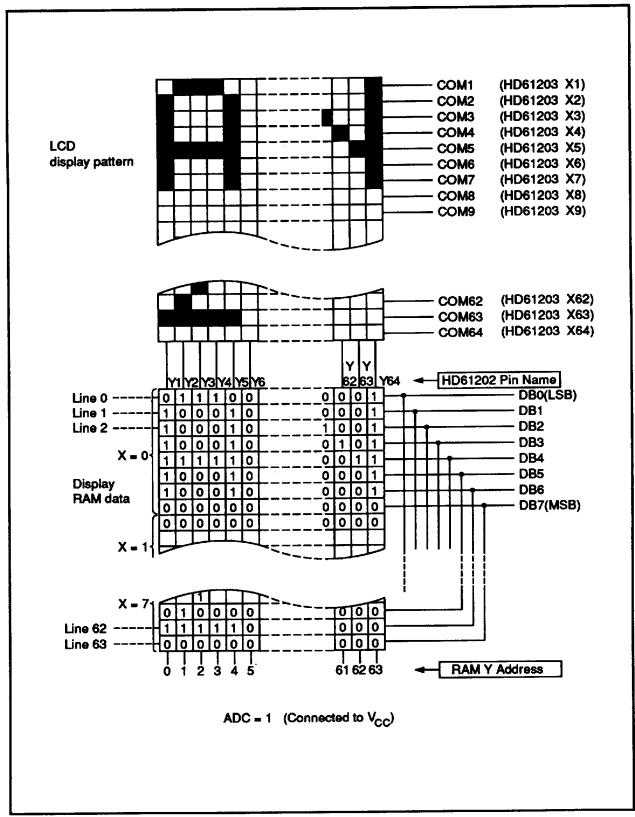

Stores dot data for display. 1-bit data of this RAM corresponds to light on (data = 1) and light off (data = 0) of 1 dot in the display panel. The correspondence between Y addresses of RAM and segment pins can be reversed by ADC signal.

HITACHI

596

4496204 0046392 242

As the ADC signal controls the Y address counter, reversing of the signal during the operation causes malfunction and destruction of the contents of register and data of RAM. Therefore, never fail to connect ADC pin to  $V_{CC}$  or GND when using.

Figure 7 shows the relations between Y address of RAM and segment pins in the cases of ADC = 1 and ADC = 0 (display start line = 0, 1/64 duty cycle).

# HITACHI

| 4496204 0046393 **1**89 **|||**

Figure 7 Relation between RAM Data and Display

HITACHI

4496204 0046394 015

Figure 7 Relation between RAM Data and Display (cont)

HITACHI

599

₩ 4496204 DO46395 T51 **W**

#### Z Address Counter

The Z address counter generates addresses for outputting the display data synchronized with the common signal. This counter consists of 6 bits and counts up at the fall of the CL signal. At the high level of FRM, the contents of the display start line register is preset at the Z counter.

#### Display Data Latch

The display data latch stores the display data temporarily that is output from display data RAM to the liquid crystal driving circuit. Data is latched at the rise of the CL signal. The display on/off instruction controls the data in this latch and does not influence data in display data RAM.

#### Liquid Crystal Display Driver Circuit

The combination of latched display data and M signal causes one of the 4 liquid crystal driver levels, V1, V2, V3, and V4 to be output.

#### Reset

The system can be initialized by setting RST terminal at low level when turning power on.

- 1. Display off

- 2. Set display start line register line 0.

While  $\overline{RST}$  is low level, no instruction except status read can be accepted. Therefore, execute other instructions after making sure that DB4 = 0 (clear RESET) and DB7 = 0 (Ready) by status read instruction. The conditions of power supply at initial power up are shown in table 1.

Table 1 Power Supply Initial Conditions

| ltem       | Symbol           | Min | Тур | Max | Unit |

|------------|------------------|-----|-----|-----|------|

| Reset time | t <sub>RST</sub> | 1.0 | _   |     | μs   |

| Rise time  | t <sub>r</sub>   |     | _   | 200 | ns   |

Do not fail to set the system again because RESET during operation may destroy the data in all the registers except on/off register and in RAM.

V<sub>CC</sub> 4.5 V t<sub>RST</sub> 0.7 V<sub>CC</sub> RST 0.3 V<sub>CC</sub>

HITACHI

600

4496204 0046396 998 |

# **Display Control Instructions**

#### Outline

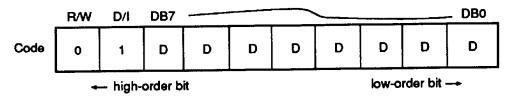

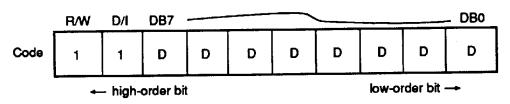

Table 2 shows the instructions. Read/write (R/W) signal, data/instruction (D/I) signal, and data bus signals (DB0 to DB7) are also called instructions because the internal operation depends on the signals from the MPU.

These explanations are detailed in the following pages. Generally, there are following three kinds of instructions:

- 1. Instruction to set addresses in the internal RAM

- 2. Instruction to transfer data from/to the internal RAM

- 3. Other instructions

In general use, the second type of instruction is used most frequently. Since Y address of the internal RAM is increased by 1 automatically after writing (reading) data, the program can be shortened. During the execution of an instruction, the system cannot accept instructions other than status read instruction. Send instructions from MPU after making sure that the busy flag is 0, which is proof that an instruction is not being excuted.

| 4496204 0046397 824 **|||**

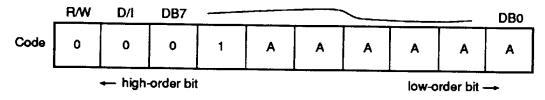

Table 2 Instructions

|                      |    |    |       |            | Code   |                           |          |            |       |     |                                                                                                                                |

|----------------------|----|----|-------|------------|--------|---------------------------|----------|------------|-------|-----|--------------------------------------------------------------------------------------------------------------------------------|

| Instructions         | χ. | 70 | 087   | 980        | DBS    | DB4                       | DB3      | DB2        | DB1   | DB0 | DB0 Functions                                                                                                                  |

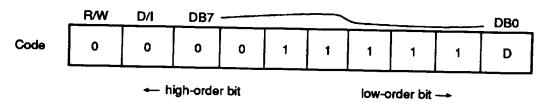

| Display on/off       | 0  | 0  | 0     | 0          |        | -                         | -        | -          | -     | 1/0 | Controls display on/off. RAM data and internal status are not affected. 1: on, 0: off.                                         |

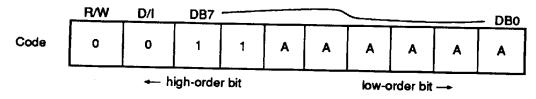

| Display start line   | 0  | 0  | -     | -          | Displ  | Display start line (0-63) | line (0  | <u> </u>   |       |     | Specifies the RAM line displayed at the top of the screen.                                                                     |

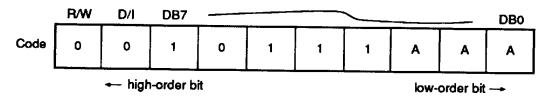

| Set page (X address) | 0  | 0  | -     | 0          | _      | _                         | _        | Page (0-7) | (0-7) |     | Sets the page (X address) of RAM at the page (X address) register.                                                             |

| Set address          | 0  | 0  | 0     | -          | Y ado  | Y address (0-63)          | <u>g</u> |            |       |     | Sets the Y address in the Y address counter.                                                                                   |

| Status read          | -  | 0  | Busy  | 0          | 8      | Reset 0                   | 0.2      | 0          | 0     | 0   | Reads the status.                                                                                                              |

|                      |    |    | •     |            | P<br>H |                           |          |            |       |     | RESET 1: Reset<br>0: Normal                                                                                                    |

|                      |    |    |       |            |        |                           |          |            |       |     | ONOFF 1: Display off 0: Display on                                                                                             |

|                      |    |    |       |            |        |                           |          |            |       |     | Busy 1: Internal operation 0: Ready                                                                                            |

| Write display data   | 0  | -  | Write | Write data |        |                           |          |            |       |     | Writes data DB0 (LSB) Has access to the to DB7 (MSB) on the address of the display data bus into display RAM specified in AAM. |

| Read display data    | -  | -  | Reac  | Read data  |        |                           |          |            |       |     | Reads data DB0 (LSB) access, Y address is to DB7 (MSB) from the display RAM to the data bus.                                   |

lote: 1. Busy time varies with the frequency (fCLK) of  $\phi$ 1, and  $\phi$ 2. (1fCLK  $\leq$  TBUSY  $\leq$  3fCLK)

HITACHI

602

**=** 4496204 0046398 760 **==**

#### Detailed Explanation

#### Display on/off

The display data appears when D is 1 and disappears when D is 0. Though the data is not on the screen with D=0, it remains in the display data RAM. Therefore, you can make it appear by changing D=0 into D=1.

# Display start line

Z address AAAAA (binary) of the display data RAM is set in the display start line register and displayed at the top of the screen. Figure 8 shows examples of display (1/64 duty cycle) when the start line = 0-3. When the display duty cycle is 1/64 or more (ex. 1/32, 1/24 etc.), the data of total line number of LCD screen, from the line specified by display start line instruction, is displayed.

HITACHI

4496204 0046399 6T7 **==**

Figure 8 Relation Between Start Line and Display

604 HITACHI

**--** 4496204 0046400 149 **--**

#### Set page (X address)

X address AAA (binary) of the display data RAM is set in the X address register. After that, writing or reading to or from MPU is executed in this specified page until the next page is set. See figure 9.

#### Set Y address

Y address AAAAA (binary) of the display data RAM is set in the Y address counter. After that, Y address counter is increased by 1 every time the data is written or read to or from MPU.

Figure 9 Address Configuration of Display Data RAM

HITACHI

605

■ 4496204 DO46401 O85 **■**■

#### Status Read

Busy:

When Busy is 1, the LSI is executing internal operations. No instructions are accepted while

Busy is 1, so you should make sure that Busy is 0 before writing the next instruction.

ON/OFF:

Shows the liquid crystal display conditions: on condition or off condition.

When ON/OFF is 1, the display is in off condition. When ON/OFF is 0, the display is in on condition.

RESET:

RESET = 1 shows that the system is being initialized. In this condition, no instructions

except status read can be accepted.

RESET = 0 shows that initializing has finished and the system is in the usual operation

condition.

#### Write Display Data

Writes 8-bit data DDDDDDDD (binary) into the display data RAM. Then Y address is increased by 1 automatically.

# Read Display Data

Reads out 8-bit data DDDDDDDD (binary) from the display data RAM. Then Y address is increased by 1 automatically.

One dummy read is necessary right after the address setting. For details, refer to the explanation of output register in "FUNCTION OF EACH BLOCK".

HITACHI

606

4496204 0046402 Tll **=**

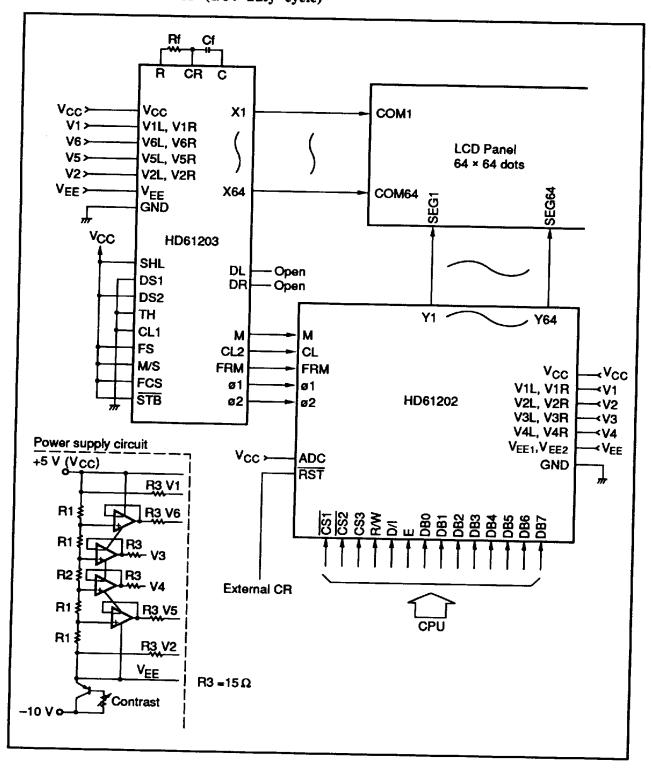

Use of HD61202

Interface with HD61203 (1/64 duty cycle)

HITACHI 607

■ 4496204 0046403 958 ■

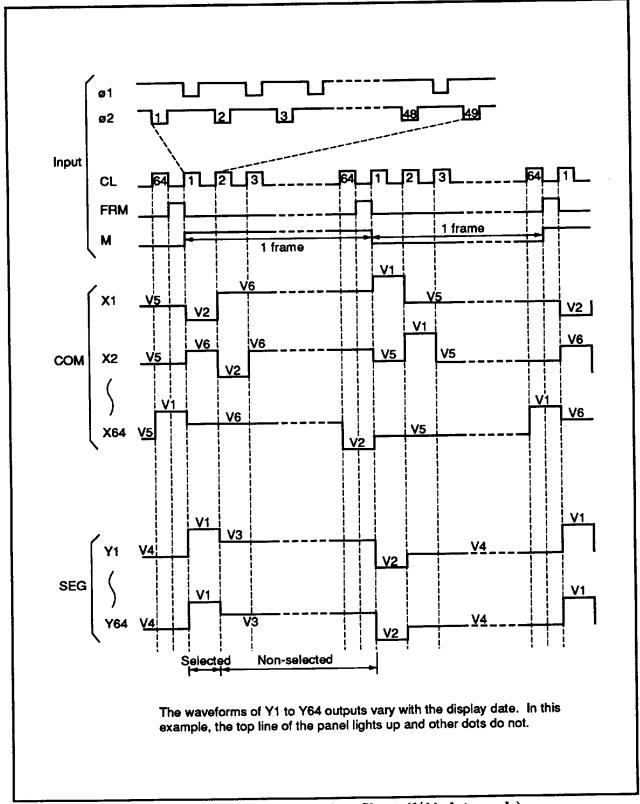

Figure 10 LCD Driver Timing Chart (1/64 duty cycle)

608 **HITACHI**■ 4496204 0046404 894 ■

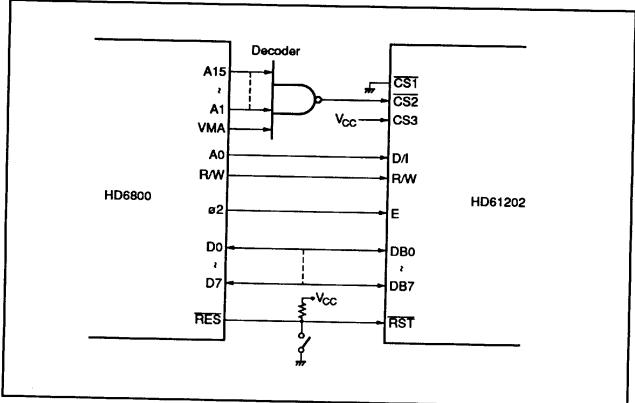

# Interface with CPU

# 1. Example of connection with HD6800

Figure 11 Example of Connection with HD6800 Series

In this decoder, addresses of HD61202 in the address area of HD6800 are:

Read/write of the display data

\$FFFF

write of display instruction

\$FFFE

Read out of status

\$FFFE

Therefore, you can control HD61202 by reading/writing the data at these addresses.

HITACHI

609

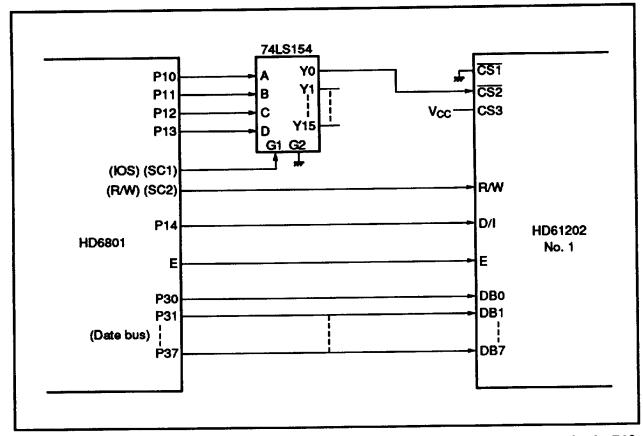

# 2. Example of connection with HD6801

- Set HD6801 to mode 5. P10 to P14 are used as the output port and P30 to P37 as the data bus.

- 74LS154 4-to-16 decoder generates chip select signal to make specified HD61202 active after decoding 4 bits of P10 to P13.

- Therefore, after enabling the operation by P10 to P13 and specifying D/I signal by P14, read/write from/to the external memory area (\$0100 to \$01FE) to control HD61202. In this case, IOS signal is output from SC1 and R/W signal from SC2.

- For details of HD6800 and HD6801, refer to their manuals.

HITACHI

610

4496204 0046406 667 📟

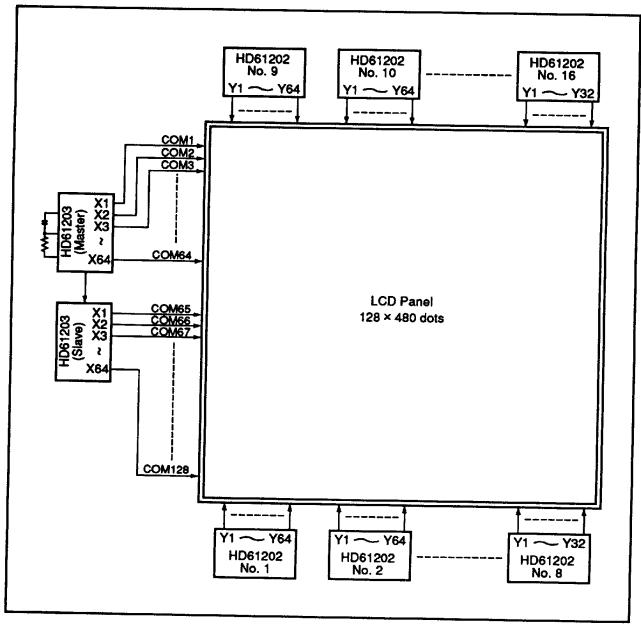

# Example of Application

Note: In this example, two HD61203s output the equivalent waveforms. So, stand-alone operation is possible. In this case, connect COM1 and COM65 to X1, COM2 and COM66 to X2, ..., and COM64 and COM128 to X64. However, for the large screen display, it is better to drive in 2 rows as in this example to guarantee the display quality.

HITACHI

环 4496204 0046407 5T3 🚥