# SONY

# CXD3220R

# IEEE1394 Link/Transaction Layer Controller LSI for SBP-2

#### Description

The CXD3220R is a Link/Transaction Layer LSI conforming to the IEEE1394 serial bus standard.

It is mainly used when connecting the IEEE1394 digital I/F to a storage device such as a hard disk, DVD-ROM, CD-ROM or tape streamer.

Data transfer conforms to the SBP-2 protocol.

This LSI utilizes Apple Computer's Fire Wire technology.

#### Features

- Conforms to IEEE1394 serial bus standard

- Conforms to SBP-2 (serial bus protocol-2)

- Compatible with bidirectional data transfer of computer peripherals

- Compatible with 1394 transfer rate at 100/200Mbps

- Dedicated Asynchronous data transfer

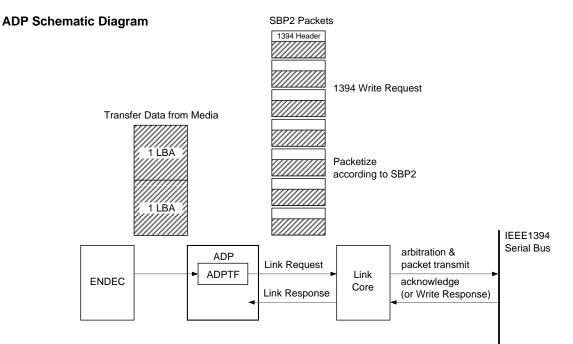

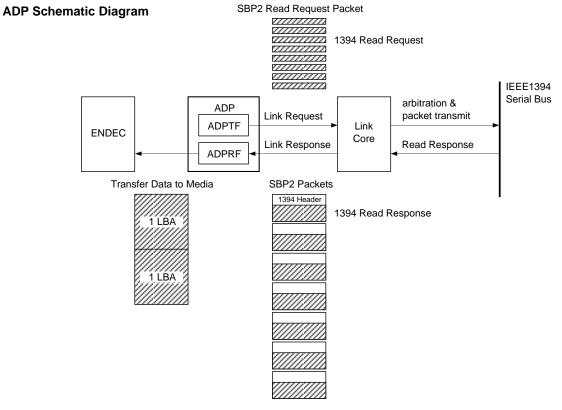

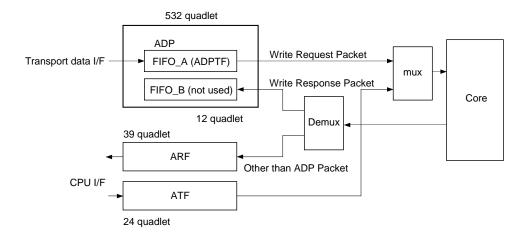

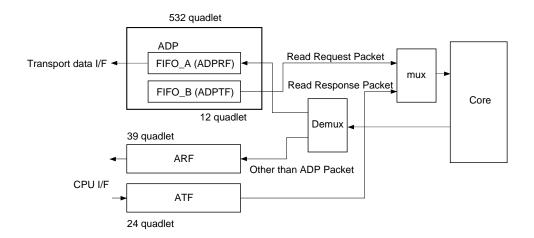

- High-speed data transfer through the use of an ADP (automatic data pipe) circuit

- Cycle master function

- Direct connection to 1394 Phy chip

- Large capacity FIFO

| Data transfer FIFO         | 532 quadlets |

|----------------------------|--------------|

| Asynchronous Transmit FIFO | 24 quadlets  |

| Asynchronous Receive FIFO  | 39 quadlets  |

#### Applications

Digital interface for computer peripheral

#### Structure

Silicon gate CMOS IC

#### Absolute Maximum Ratings (Ta = 25°C)

|                                    |       | <b>U</b> (                                         |    |

|------------------------------------|-------|----------------------------------------------------|----|

| <ul> <li>Supply voltage</li> </ul> | Vdd   | Vss – 0.5 to +4.6                                  | V  |

| <ul> <li>Input voltage</li> </ul>  | Vı    | Vss - 0.5 to Vpp + 0.5                             | V  |

| <ul> <li>Output voltage</li> </ul> | Vo    | $\ensuremath{Vss}-0.5$ to $\ensuremath{Vdd}$ + 0.5 | V  |

| Operating temperating              | ature |                                                    |    |

|                                    | Тор   | r –20 to +75                                       | °C |

| Storage temperatu                  | ire   |                                                    |    |

|                                    | Tstg  | g -55 to +150                                      | °C |

|                                    |       |                                                    |    |

| Recommended Op                     | erati | ng Conditions                                      |    |

|                                    | 1/    | 2.0 to 2.6                                         | v  |

| <ul> <li>Supply voltage</li> </ul> | Vdd    | 3.0 to 3.6 | V  |

|------------------------------------|--------|------------|----|

| • Operating tempe                  | rature |            |    |

|                                    | Topr   | -20 to +75 | °C |

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

# Contents

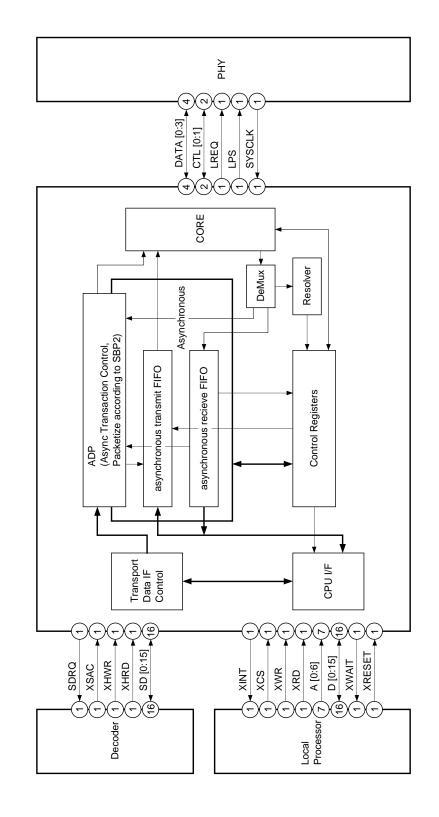

| 1. | Block Diagram                                  | . 3 |

|----|------------------------------------------------|-----|

| 2. | Pin Configuration                              | . 4 |

| 3. | Pin Description                                | . 5 |

| 4. | Electrical Characteristics                     | . 8 |

|    | 4-1. DC Characteristics                        | . 8 |

|    | 4-2. AC Characteristics                        | . 8 |

|    | 4-3. Input/Output Capacitance                  | . 8 |

|    | 4-4. Timing Definition                         | . 9 |

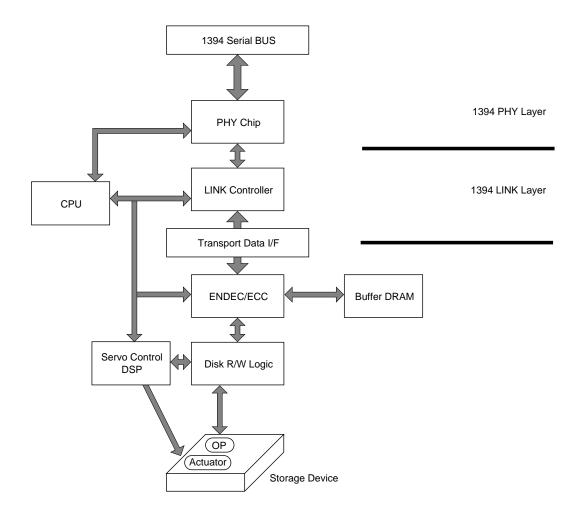

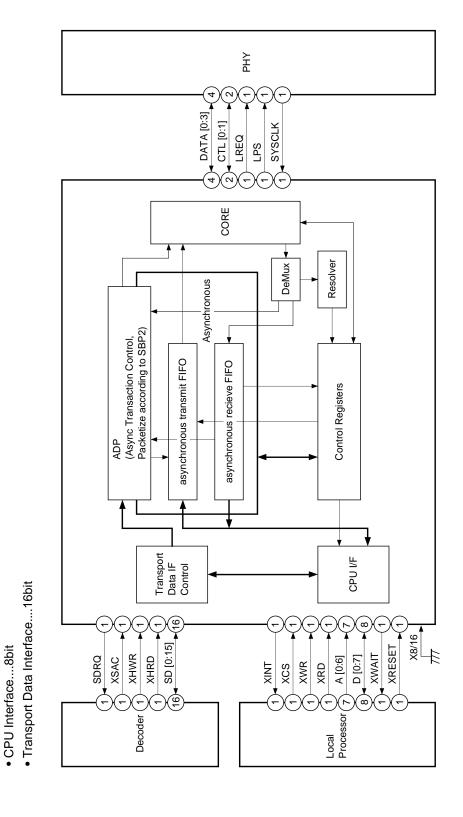

| 5. | System Configuration Example                   | 10  |

|    | 5-1. System Block Diagram                      | 10  |

|    | 5-2. System Connection Diagram                 | 11  |

| 6. | Asynchronous Communication                     | 12  |

|    | 6-1. CPU I/F                                   | 12  |

|    | 6-2. CFR                                       | 15  |

|    | 6-3. Asynchronous Packet Transmission          | 25  |

|    | 6-4. Asynchronous Packet Reception             | 28  |

|    | 6-5. CXD3220R Data Format                      | 33  |

|    | 6-6. Self-ID Packet Reception Error Processing |     |

| 7. | ADP (Asynchronous Data Pipe)                   |     |

|    | 7-1. Built-in FIFO                             | 44  |

|    | 7-2. Transport Data I/F                        | 44  |

|    | 7-3. ADP                                       | 47  |

|    | 7-4. ADP Structure and Functions               | 49  |

|    | 7-5. ADP Setting                               | 51  |

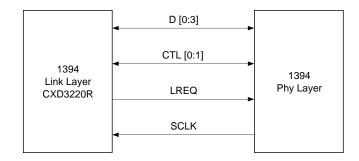

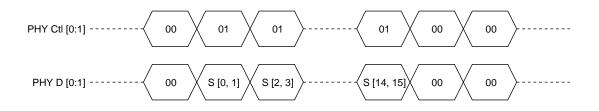

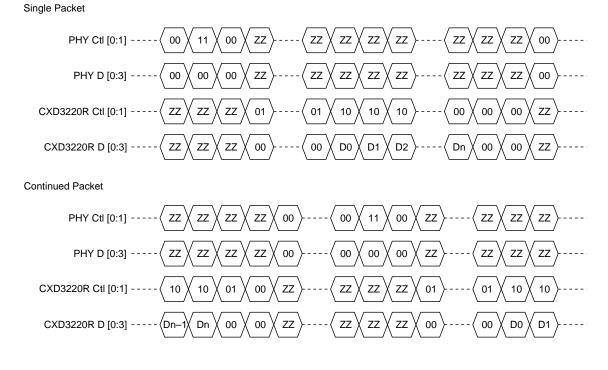

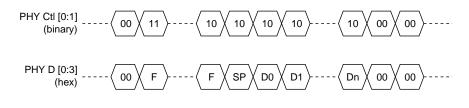

| 8. | Link-Phy Communication                         | 58  |

|    | 8-1. Link-Phy Interface Specifications         |     |

|    | 8-2. Communication                             | 58  |

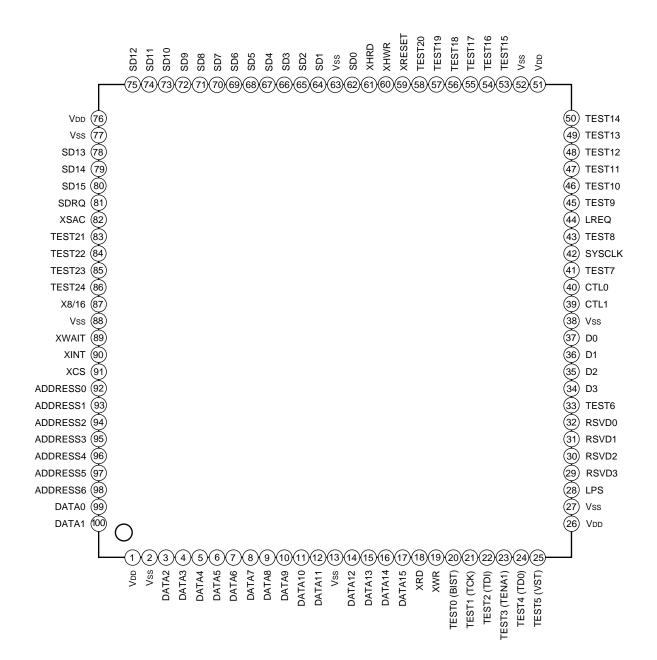

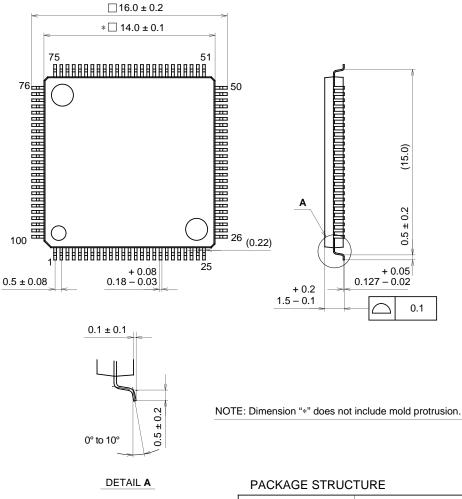

#### 2. Pin Configuration

# 3. Pin Description

| Pin<br>No. | Symbol | I/O | Description                                                           |

|------------|--------|-----|-----------------------------------------------------------------------|

| 1          | Vdd    | —   | Power Supply                                                          |

| 2          | Vss    | _   | GND                                                                   |

| 3          | DATA2  | I/O | CPU I/F I/O data bit 2                                                |

| 4          | DATA3  | I/O | CPU I/F I/O data bit 3                                                |

| 5          | DATA4  | I/O | CPU I/F I/O data bit 4                                                |

| 6          | DATA5  | I/O | CPU I/F I/O data bit 5                                                |

| 7          | DATA6  | I/O | CPU I/F I/O data bit 6                                                |

| 8          | DATA7  | I/O | CPU I/F I/O data bit 7                                                |

| 9          | DATA8  | I/O | CPU I/F I/O data bit 8                                                |

| 10         | DATA9  | I/O | CPU I/F I/O data bit 9                                                |

| 11         | DATA10 | I/O | CPU I/F I/O data bit 10                                               |

| 12         | DATA11 | I/O | CPU I/F I/O data bit 11                                               |

| 13         | Vss    |     | GND                                                                   |

| 14         | DATA12 | I/O | CPU I/F I/O data bit 12                                               |

| 15         | DATA13 | I/O | CPU I/F I/O data bit 13                                               |

| 16         | DATA14 | I/O | CPU I/F I/O data bit 14                                               |

| 17         | DATA15 | I/O | CPU I/F I/O data bit 15                                               |

| 18         | XRD    | I   | CPU I/F read signal<br>0: read                                        |

| 19         | XWR    | I   | CPU I/F write signal<br>0: write                                      |

| 20         | TEST0  | —   | Test pin <sup>*1</sup>                                                |

| 21         | TEST1  | —   | Test pin <sup>*1</sup>                                                |

| 22         | TEST2  | —   | Test pin <sup>*1</sup>                                                |

| 23         | TEST3  | —   | Test pin <sup>*1</sup>                                                |

| 24         | TEST4  | _   | Test pin <sup>*1</sup>                                                |

| 25         | TEST5  | —   | Test pin 2*2                                                          |

| 26         | Vdd    | _   | Power supply                                                          |

| 27         | Vss    | _   | GND                                                                   |

| 28         | LPS    | 0   | Phy I/F Link power status signal (High level when XRESET input = low) |

| 29         | RSVD3  | _   | Reserved*3                                                            |

| 30         | RSVD2  | _   | Reserved*3                                                            |

| 31         | RSVD1  | _   | Reserved*3                                                            |

| 32         | RSVD0  | _   | Reserved*3                                                            |

| 33         | TEST6  |     | Test pin*1                                                            |

$^{\rm *1}\,$  The test pins should be used open.

$^{\ast 2}$  Connect the test pin 2 to GND.

\*3 RSVD0 to 3 should be used open.

| Pin<br>No. | Symbol | I/O | Description                                                             |

|------------|--------|-----|-------------------------------------------------------------------------|

| 34         | D3     | I/O | Phy I/F data bus bit 3                                                  |

| 35         | D2     | I/O | Phy I/F data bus bit 2                                                  |

| 36         | D1     | I/O | Phy I/F data bus bit 1                                                  |

| 37         | D0     | I/O | Phy I/F data bus bit 0                                                  |

| 38         | Vss    | _   | GND                                                                     |

| 39         | CTL1   | I/O | Phy I/F control bus bit 1                                               |

| 40         | CTL0   | I/O | Phy I/F control bus bit 0                                               |

| 41         | TEST7  | _   | Test pin*1                                                              |

| 42         | SYSCLK | I   | Phy I/F system clock (49.195MHz)                                        |

| 43         | TEST8  | _   | Test pin <sup>*1</sup>                                                  |

| 44         | LREQ   | 0   | Phy I/F request signal                                                  |

| 45         | TEST9  | _   | Test pin <sup>*1</sup>                                                  |

| 46         | TEST10 | _   | Test pin*1                                                              |

| 47         | TEST11 | _   | Test pin*1                                                              |

| 48         | TEST12 | _   | Test pin*1                                                              |

| 49         | TEST13 | _   | Test pin <sup>*1</sup>                                                  |

| 50         | TEST14 | _   | Test pin*1                                                              |

| 51         | Vdd    | _   | Power supply                                                            |

| 52         | Vss    | _   | GND                                                                     |

| 53         | TEST15 | _   | Test pin*1                                                              |

| 54         | TEST16 | —   | Test pin*1                                                              |

| 55         | TEST17 | _   | Test pin*1                                                              |

| 56         | TEST18 | _   | Test pin <sup>*1</sup>                                                  |

| 57         | TEST19 | —   | Test pin <sup>*1</sup>                                                  |

| 58         | TEST20 | -   | Test pin <sup>*1</sup>                                                  |

| 59         | XRESET | I   | Master reset signal<br>0: Active; 1: Non-active                         |

| 60         | XHWR   | I   | Transport data I/F data write enable signal<br>0: Non-active; 1: Active |

| 61         | XHRD   | I   | Transport data I/F data read enable signal<br>0: Non-active; 1: Active  |

| 62         | SD0    | I/O | Transport data I/F data bus bit 0                                       |

| 63         | Vss    | -   | GND                                                                     |

| 64         | SD1    | I/O | Transport data I/F data bus bit 1                                       |

| 65         | SD2    | I/O | Transport data I/F data bus bit 2                                       |

| 66         | SD3    | I/O | Transport data I/F data bus bit 3                                       |

| 67         | SD4    | I/O | Transport data I/F data bus bit 4                                       |

$^{\ast 1}\,$  The test pins should be used open.

| Pin<br>No. | Symbol   | I/O | Description                                                             |

|------------|----------|-----|-------------------------------------------------------------------------|

| 68         | SD5      | I/O | Transport data I/F data bus bit 5                                       |

| 69         | SD6      | I/O | Transport data I/F data bus bit 6                                       |

| 70         | SD7      | I/O | Transport data I/F data bus bit 7                                       |

| 71         | SD8      | I/O | Transport data I/F data bus bit 8                                       |

| 72         | SD9      | I/O | Transport data I/F data bus bit 9                                       |

| 73         | SD10     | I/O | Transport data I/F data bus bit 10                                      |

| 74         | SD11     | I/O | Transport data I/F data bus bit 11                                      |

| 75         | SD12     | I/O | Transport data I/F data bus bit 12                                      |

| 76         | Vdd      |     | Power supply                                                            |

| 77         | Vss      |     | GND                                                                     |

| 78         | SD13     | I/O | Transport data I/F data bus bit 13                                      |

| 79         | SD14     | I/O | Transport data I/F data bus bit 14                                      |

| 80         | SD15     | I/O | Transport data I/F data bus bit 15                                      |

| 81         | SDRQ     | 0   | Transport data I/F data request signal                                  |

| 82         | XSAC     | I   | Transport data I/F acknowledge signal                                   |

| 83         | TEST21   | _   | Test pin*1                                                              |

| 84         | TEST22   | _   | Test pin*1                                                              |

| 85         | TEST23   |     | Test pin*1                                                              |

| 86         | TEST24   |     | Test pin*1                                                              |

| 87         | X8/16    | I   | CPU I/F I/O data bus select signal<br>0: 8 bits; 1:16 bits              |

| 88         | Vss      | _   | GND                                                                     |

| 89         | XWAIT    | 0   | CPU I/F wait signal active when XCS = 0,<br>high impedance when XCS = 1 |

| 90         | XINT     | 0   | CPU I/F interrupt signal<br>0: Active; 1: Non-active                    |

| 91         | XCS      | I   | CPU I/F chip select signal<br>0: Active; 1: Non-active                  |

| 92         | ADDRESS0 | I   | CPU I/F address bus bit 0                                               |

| 93         | ADDRESS1 | I   | CPU I/F address bus bit 1                                               |

| 94         | ADDRESS2 | I   | CPU I/F address bus bit 2                                               |

| 95         | ADDRESS3 | I   | CPU I/F address bus bit 3                                               |

| 96         | ADDRESS4 | I   | CPU I/F address bus bit 4                                               |

| 97         | ADDRESS5 | I   | CPU I/F address bus bit 5                                               |

| 98         | ADDRESS6 | I   | CPU I/F address bus bit 6                                               |

| 99         | DATA0    | I/O | CPU I/F I/O data bit 0                                                  |

| 100        | DATA1    | I/O | CPU I/F I/O data bit 1                                                  |

\*1 The test pins should be used open.

# 4. Electrical Characteristics

# 4-1. DC Characteristics

(Ta = 25°C, V ss = 0V)

| Item                   | Symbol | Conditions                                           | 3          | Min.      | Тур. | Max.   | Unit |

|------------------------|--------|------------------------------------------------------|------------|-----------|------|--------|------|

|                        | Vін    | All input pins                                       |            | 0.7Vdd    |      |        | V    |

| Input voltage          | VIL    | All input pins                                       |            |           |      | 0.2Vdd | V    |

|                        | Vон    | Output pins excluding                                | Іон = -4mA | Vdd - 0.4 |      |        | V    |

| Output voltage         | Vol    | D [3:0], CTL [1:0], LREQ                             | lo∟ = 4mA  |           |      | 0.4    | V    |

| Output voltage         | Vон    |                                                      | Іон = –8mA | Vdd - 0.4 |      |        | V    |

|                        | Vol    | D [3:0], CTL [1:0], LREQ                             | lo∟ = 8mA  |           |      | 0.4    | V    |

|                        | lı1    | SD [15:0], D [3:0], CTL [1:                          | 0]         | -40       |      | 40     | μA   |

| Input leak current     | lı2    | Normal input pins                                    |            | -10       |      | 10     | μA   |

|                        | ΠL     | XHRD, XHWR, XRD, XRESET, XSAC,<br>XWR                |            | -240      | -100 | -40    | μA   |

| Output leak<br>current | loz    | XWAIT (for high impedance state)<br>VIN = Vss or VDD |            | -40       |      | 40     | μA   |

| Power supply           | lcc1   | For ADP operation V                                  | dd = 3.3V  |           | 90   | 120    | mA   |

| Power supply           | lcc2   | For ADP not operation V                              | dd = 3.3V  |           | 50   | 70     | mA   |

# 4-2. AC Characteristics

$(V_{DD} = 3.0 \text{ to } 3.6 \text{V})$

| Item         | Applicable pins                      | Symbol | Reference clock                                                                  | Conditions                             | Min. | Тур. | Max. | Unit |  |

|--------------|--------------------------------------|--------|----------------------------------------------------------------------------------|----------------------------------------|------|------|------|------|--|

| Input setup  |                                      | Tsu1   |                                                                                  | ······································ |      |      |      |      |  |

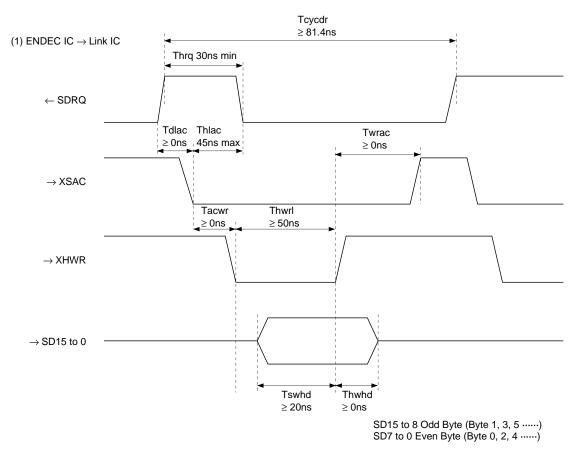

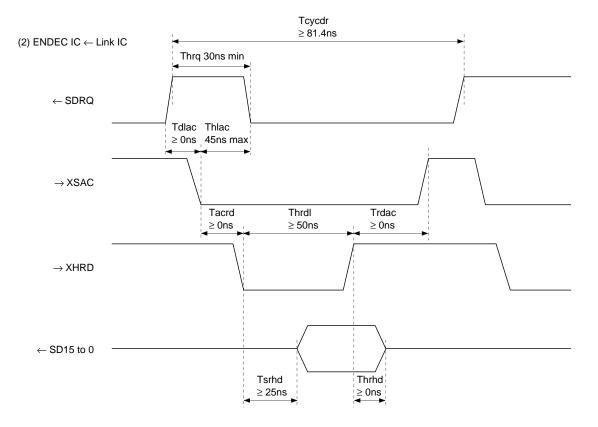

| Input hold   | SD [15:0], SDRQ, XSAC,<br>XHRD, XHWR | Th1    | Refer to 7-2. Transport data I/F write timing and Transport data I/F read timing |                                        |      |      |      |      |  |

| Output delay | ,                                    | Td1    |                                                                                  |                                        |      |      |      |      |  |

| Input setup  | D [3:0], CTL [1:0]                   | Tsu2   |                                                                                  |                                        | 5    |      |      | ns   |  |

| Input hold   |                                      | Th2    | SYSCLK                                                                           | CL = 10pF                              | 2    |      |      | ns   |  |

| Output delay | D [3:0], CTL [1:0], LREQ             | Td2    |                                                                                  |                                        | 2    |      | 15   | ns   |  |

| Input setup  | ADDRESS [6:0], DATA [15:0],          | Tsu3   |                                                                                  |                                        |      |      |      | -    |  |

| Input hold   | XCS, XWR, XRD                        | Th3    | Refer to 6-1. ATF/CFR write timing and ATF/CFF<br>read timing                    |                                        |      |      |      | -K   |  |

| Output delay | DATA [15:0], XWAIT                   | Td3    | <b>3</b>                                                                         |                                        |      |      |      |      |  |

# 4-3. Input/Output Capacitance

| Item               | Symbol | Conditions                    | Min. | Тур. | Max. | Unit |

|--------------------|--------|-------------------------------|------|------|------|------|

| Input capacitance  | CIN    | All input pins                |      |      | 9    | pF   |

| Output capacitance | Соит   | All input pins                |      |      | 11   | pF   |

| I/O capacitance    | CI/O   | D [3:0], CTL [1:0], SD [15:0] |      |      | 11   | pF   |

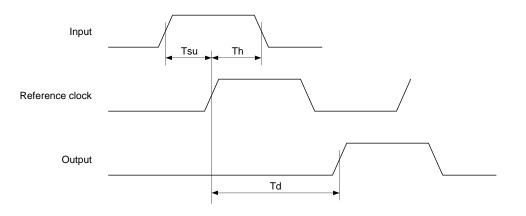

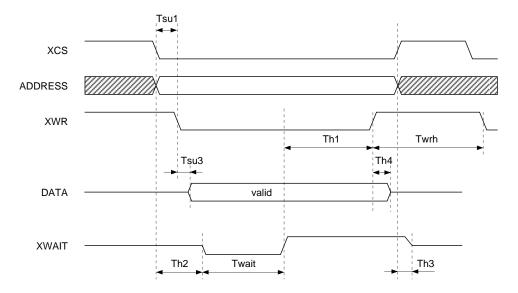

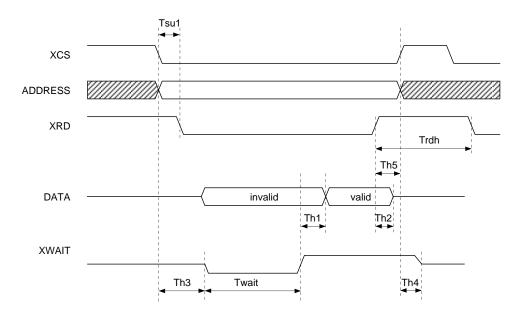

# 4-4. Timing Definition

# 5. System Configuration Example

#### 5-1. System Block Diagram

5-2. System Connection Diagram

# 6. Asynchronous Communication

### 6-1. CPU I/F

The CPU I/F controls data communication between the external CPU and the CXD3220R ATF/ARF/CFR<sup>\*1</sup>, respectively.

Communications between the CPU and CXD3220R include:

- 1) CPU writes data to ATF  $\rightarrow$  Asynchronous packet transmit

- 2) CPU reads data in ARF  $\rightarrow$  Asynchronous packet receive

- 3) CPU writes data to CFR  $\rightarrow$  mode, header data setting

- 4) CPU reads data in CFR  $\rightarrow$  internal status, header data read

- 5) CXD3220R informs CPU of an interrupt event with an interrupt signal

The CXD3220R supports 16-bit and 8-bit CPU I/F.

The ATF/ARF/CFR built in the CXD3220R have a 32-bit structure, so all bits can not be accessed with one access. The target address must be accessed two consecutive times for 16 bits and four consecutive times for 8 bits.

The roles played by the signals communicated between the CXD3220R and the external CPU are given bellow.

| Data [15:0]   | in/out | Data for writing to or reading from specified address                        |

|---------------|--------|------------------------------------------------------------------------------|

| ADDRESS [6:0] | in     | Address for writing or reading data                                          |

|               |        | Data destination (CFR or FIFO) and data breakpoint (Write or Confirm) are    |

|               |        | discriminated according to the address                                       |

| XCS           | in     | Access enable from host bus (low active)                                     |

| XWR           | in     | Data write enable signal (low: write)                                        |

| XRD           | in     | Data read enable signal (low: read)                                          |

| XWAIT         | out    | Indicates access (read or write) completed to specified address (low active) |

| XINT          | out    | Interrupt signal. Indicates some kind of interrupt when low                  |

|               |        | Type of interrupt and mask specified by CFR                                  |

| X8/16         | in     | CPU I/F data bus switching                                                   |

|               |        | High: 16 bits; low: 8 bits                                                   |

\*1 ATF (Asynchronous Transmit FIFO), ARF (Asynchronous Receive FIFO), CFR (Configuration Register) In the CXD3220R, the ATF has the capacity of 24 quadlets and the ARF has the capacity of 39 quadlets.

#### Writing Timing to ATF/CFR

Tsu1 5nsec min, Tsu3 13nsec max, Th1 5nsec min, Twrh 60nsec min Twait 100nsec max, Th2 8nsec max, Th3 14nsec max, Th4 5nsec min

#### Read Timing from ARF/CFR

Tsu1 5nsec min, Th1 3nsec max, Trdh 60nsec min Twait 270nsec max, Th2 16nsec max, Th3 8nsec max, Th4 14nsec max, Th5 5nsec min

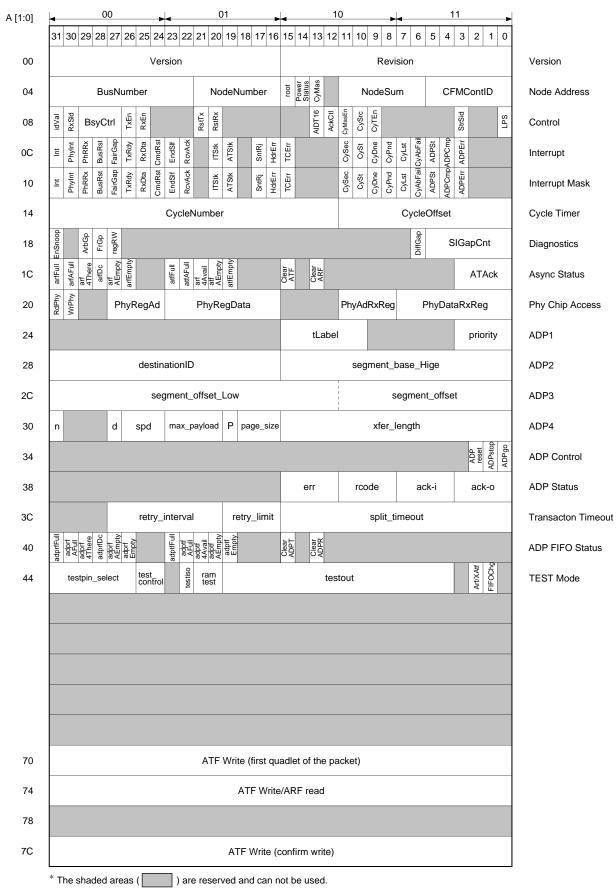

# Configuration Register (CFR) Address Map

#### 6-2. CFR (Configuration Register)

This is a memory space to store the status information, operation mode and packet header information in the chip. Read/write with the external CPU can be performed via the CPU I/F. The address map and register contents are shown below.

#### **Register Description**

#### 1) Version/Revision Register

These registers have the CXD3220R version/revision written in them. The register address is 00h; they are read only, and the default value is 3220\_0000h.

| Bit      | Name     | Function                 |

|----------|----------|--------------------------|

| 31 to 16 | Version  | CXD3220R version number  |

| 15 to 0  | Revision | CXD3220R revision number |

#### 2) Node Address Register

These registers are used to monitor root/cycle master status and the total number of nodes connected, and so on.

The register address is 04h and the initial value is FFFF\_0000h.

Only the bus number is for read/write, and the other registers are normally for read only, but the Diagnostic register can be read/write by setting regRW to "1".

| Bit      | Name         | Function                                                                                                                                                                                                                                                                                                               |

|----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 to 22 | Bus Number   | Bus number of connected bus                                                                                                                                                                                                                                                                                            |

| 21 to 16 | Node Number  | Node number of this link                                                                                                                                                                                                                                                                                               |

| 15       | root         | Root/not root for this link<br>1: root; 0: not root                                                                                                                                                                                                                                                                    |

| 14       | Power Status | Cable power status for this mode<br>1: CPS on; 0: CPS off                                                                                                                                                                                                                                                              |

| 13       | CyMas        | Whether or not this link is cycle master<br>1: cycle master; 0: not                                                                                                                                                                                                                                                    |

| 11 to 6  | NodeSum      | Total number of connected nodes. The value becomes "0" when an error occurs in the Self ID phase. This value is fixed when the Interrupt register EndSlf bit becomes "1" from "0".                                                                                                                                     |

| 5 to 0   | CFMcontID    | The Phy-ID value of the contender is loaded.<br>However, when the CXD3220R node has an ability to become the contender<br>and this LSI has the Phy-ID value larger than the loaded value, the CXD3220R<br>itself is the contender. This value is fixed when the Interrupt register EndSIf<br>bit becomes "1" from "0". |

# 3) Control Register

These registers perform settings for the CXD3220R basic operations. The register address is 08h; they are for read/write, and the initial value is C600\_2A01h.

| Bit      | Name    | Function                                                                                                                                                                                                         |

|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31       | idVal   | Receives packet from the address set in the Node Address register and packet at bus number "3FFh" node number "3Fh" when "1". Receives packet at bus number "3FFh" node number "3Fh" only when "0".              |

| 30       | RxSld   | Validates reception of Self ID packet when "1". Non-valid when "0".<br>(Fixed at "1" in the CXD3220R)                                                                                                            |

| 29 to 27 | BsyCtrl | Controls Busy status of input packet<br>000 = Returns Busy according to normal Busy/retry protocol when necessary.<br>(Fixed at "000" in the CXD3220R)                                                           |

| 26       | TxEn    | Transmitter does not transmit Arbitration and packet when "0".                                                                                                                                                   |

| 25       | RxEn    | Receiver does not receive packet when "0".                                                                                                                                                                       |

| 21       | RstTx   | Sync resets transmitter when "1".<br>This bit is cleared automatically. (Do not use for normal operation.)                                                                                                       |

| 20       | RstRx   | Sync resets receiver when "1".<br>This bit is cleared automatically. (Do not use for normal operation.)                                                                                                          |

| 13       | AIDT16  | Selects SD bus width. 8 bits when "0" and 16 bits when "1".                                                                                                                                                      |

| 12       | AckCtl  | Controls the Ack code that is sent back when a packet is received for which<br>Tcode = 0, 1 (write request quadlet/block).<br>0: Ack code = 1 (complete), 1: Ack code = 2 (pending)                              |

| 11       | CyMasEn | The Cycle Master function operates if the CXD3220R becomes Root when "1".                                                                                                                                        |

| 10       | CySrc   | Incrementation of the cycle number and reset of Cycle Offset are performed with Cycle In when "1". Incrementation is performed with Cycle Offset when "0". (This is always set to "0" internally for this link.) |

| 9        | CyTEn   | Validates Cycle Offset increment when "1".<br>(This is always set to "1" internally for this link.)                                                                                                              |

| 3        | StrSid  | Takes received Self ID packet in at the ARF when "1".<br>Does not take received Self ID packet in to the ARF when "0".                                                                                           |

| 0        | LPS     | The LPS pin is high when "1".<br>The LPS pin is low when "0".                                                                                                                                                    |

#### 4) Interrupt and Interrupt-Mask Registers

These registers combine the Interrupt register, which informs the CPU I/F of changes in the CXD3220R status, and the Interrupt-Mask register, which masks the Interrupt register.

The address of the Interrupt register is 0Ch, and when the regRW bit is "0", bits other than Int bit and ADPErr bit are cleared by writing "1". When the regRW bit is "1" all bits are for read/write.

The address of the Interrupt-Mask register is 10h and it is for read/write. When "1" is written to the corresponding bit, the interrupt becomes valid; when "0" is written, it becomes invalid.

The initial value for both registers is 0000\_0000h. The Interrupt OR corresponding to the bit where "1" is written in the Interrupt-Mask register becomes the INT bit, resulting in the XINT output signal.

And the XINT output signal becomes valid when "1" is written to the Interrupt-Mask register INT bit; when "0" is written, invalid.

| Bit | Name     | Function                                                                                                                                                                                                                                                                   |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31  | Int      | All interrupt OR results and their interrupt mask bits.                                                                                                                                                                                                                    |

| 30  | PhyInt   | Phy Interrupt was received from Phy chip.                                                                                                                                                                                                                                  |

| 29  | PhyRegRx | Data was received from Phy to Phy register.                                                                                                                                                                                                                                |

| 28  | BusRst   | Bus Reset was received from Phy.                                                                                                                                                                                                                                           |

| 27  | FairGap  | Fair Gap received from Phy.                                                                                                                                                                                                                                                |

| 26  | TxRdy    | Transmitter is able to transmit. "0" when a packet is transmitted; "1" when an Ack code is fixed.                                                                                                                                                                          |

| 25  | RxDta    | Receiver has received a correct packet. A packet is not loaded in the ARF when the Self-ID packet is received if the Control register Strsid is set to "0" and when the Response packet is received at the ADP circuit for ADP operation. However, RxDta Interrupt is set. |

| 24  | CmdRst   | Receiver has received a packet addressed to CSR RESET_START register.                                                                                                                                                                                                      |

| 23  | EndSlf   | Indicates that Self ID phase has completed.                                                                                                                                                                                                                                |

| 22  | RcvAck   | Ack code was received.                                                                                                                                                                                                                                                     |

| 20  | ITStk    | Transmitter detected wrong data in Isochronous FIFO during Isochronous transmit. (Always set to "0" in this IC)                                                                                                                                                            |

| 19  | ATStk    | Transmitter detected wrong data in Asynchronous FIFO during Asynchronous transmit.                                                                                                                                                                                         |

| 17  | SntRj    | Receiver transmitted Busy Ack for a packet transmitted to this node because received FIFO is full.                                                                                                                                                                         |

| 16  | HdrErr   | Receiver detected Header CRC error in the packet transmitted to this note.                                                                                                                                                                                                 |

| 15  | TCErr    | Transmitter detected wrong tCode data in transmitted FIFO.                                                                                                                                                                                                                 |

| 11  | CySec    | Cycle Timer register Cycle Number upper 7 bits were incremented.<br>(This is generated almost every second when Cycle Timer is valid.)                                                                                                                                     |

| 10  | CycSt    | Transmitter/Receiver transmitted/received Cycle Start packet.                                                                                                                                                                                                              |

| 9   | CycDne   | After transmit or receive of Cycle Start packet, Fair Gap was detected on the bus. This means that the Isochronous cycle is complete.                                                                                                                                      |

| 8   | CycPnd   | Cycle Timer register Cycle Offset is "0". Stays as is until Isochronous cycle is complete.                                                                                                                                                                                 |

| 7   | CycLst   | When not Cycle Master, Cycle Timer completed two cycles without receiving Cycle Start packet.                                                                                                                                                                              |

| 6   | CyAbFail | Failure of Cycle Start packet transmission Arbitration.                                                                                                                                                                                                                    |

| Bit | Name   | Function                                                                                                                                                    |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | ADPSt  | The ADP has started.                                                                                                                                        |

| 4   | ADPCmp | The ADP has completed.                                                                                                                                      |

| 3   | ADPErr | An error has occurred during ADP processing. In order to clear ADPErr bit, write "1" to this bit after "1" is written to ADP Control register ADPreset bit. |

# 5) Cycle Timer Registers

These registers are composed of the 24.576MHz clock cycle Cycle Offset and the 125µs in its host, and the Cycle Number that counts one second. The value of all nodes are regulated by the Cycle Master node. The register address is 14h; it is for read/write, and the initial value is 0000\_0000h.

| Bit      | Name        | Function                                                                                                                                                                                         |

|----------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 to 12 | CycleNumber | The upper 7 bits count seconds (1Hz) and the lower 13 bits count the Isochronous cycle ( $8kHz = 125\mu s$ ). The values are controlled by Control register Cycle Master and Cycle Timer Enable. |

| 11 to 0  | CycleOffset | Counts the system clock (24.576MHz). The Cycle Number is incremented when this counter completes one cycle. The value is controlled by Control register Cycle Master and Cycle Timer Enable.     |

# 6) Diagnostic Register

This register controls or monitors the CXD3220R status.

The register address is 18h and the initial value is 0000\_0000h.

Only the EnSp bit and regRW bit are for read/write; other bits are for read/write when the regRW bit is "1" and for read only when it is "0".

| Bit    | Name     | Function                                                                                                                                               |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31     | EnSnoop  | Receives all packets on the bus regardless of receiver address and format when "1". Invalid when "0".                                                  |

| 30     | BsyF     | Ack to be sent back next is "Ack_BusyB" when "1".<br>Ack to be sent back next is "Ack_BusyA" when "0".                                                 |

| 29     | ArbGp    | Bus is in idle state due to Arbitration Reset Gap.                                                                                                     |

| 28     | FrGp     | Bus is in idle state due to Fair Gap.                                                                                                                  |

| 27     | regRW    | Almost all registers are for read/write when "1".                                                                                                      |

| 6      | DiffGap  | "1" when there is dispersion in Gap count values in received Self ID. This value is fixed when the Interrupt register EndSlf bit becomes "1" from "0". |

| 5 to 0 | SIGapCnt | The value is entered when all Gap count values in received Self ID are the same. "00h" when bus reset is generated.                                    |

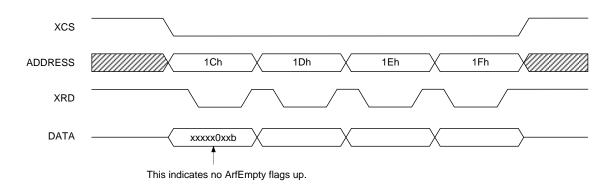

# 7) Asynchronous Transmit and Received FIFO Status Registers

These registers can monitor and control the ATF/ARF statuses.

The register address is 1ch and the initial value is 0428\_0000h.

Only the Clear ATF bit and Clear ARF bit are for read/write; other bits are for read/write when the regRW bit is "1" and read only when it is "0".

| Bit    | Name      | Function                                                                                                                                                |

|--------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31     | ARFFull   | The ARF is full when "1" and receive is not possible.                                                                                                   |

| 30     | ARFAFull  | The ARF can receive only one more quadlet when "1".                                                                                                     |

| 29     | ARF4Th    | The ATF can write more than four quadlets of data when "1".                                                                                             |

| 28     | ARFDc     | This is the control bit for reading a packet from ARF, and is "1" only for the first and last quadlets of the packet.                                   |

| 27     | ARFAEmpty | Only one more quadlet of data is written in the ARF when "1".                                                                                           |

| 26     | ARFEmpty  | The ARF is empty when "1" and there is no data to be read.                                                                                              |

| 23     | ATFFull   | The ATF is full when "1" and write is not possible.                                                                                                     |

| 22     | ATFAFull  | Only one more quadlet can be written in the ATF when "1".                                                                                               |

| 21     | ATF4Avail | More than four quadlets of data can be written in the ATF when "1".                                                                                     |

| 20     | ATFAEmpty | The ATF has only one more quadlet of data not transmitted when "1".                                                                                     |

| 19     | ATFEmpty  | The ATF is empty when "1" and there is no data for transmit.                                                                                            |

| 15     | ClearATF  | Sync reset of ATF when "1" (Self Clear).                                                                                                                |

| 13     | ClearARF  | Sync reset of ARF when "1" (Self Clear).                                                                                                                |

| 3 to 0 | ATAck     | Value of received Ack code. This is fixed when the TxRdy bit becomes "1" from "0" and the fixed value is maintained till the next Act code is received. |

#### 8) Phy Chip Access Registers

These registers are used for read/write of the contents of the Phy chip Phy register connected to the CXD3220R.

The register address is 20h and the initial value is 0000\_0000h.

| Bit      | Name         | Function                                                                            |

|----------|--------------|-------------------------------------------------------------------------------------|

| 31       | RdPhy        | The CXD3220R requests read to the address set in PhyRgAd via the Phy I/F when "1".  |

| 30       | WrPhy        | The CXD3220R requests write to the address set in PhyRgAd via the Phy I/F when "1". |

| 27 to 24 | PhyRegAd     | Sets the read/write address of the connected Phy chip Phy register.                 |

| 23 to 16 | PhyRegData   | Value of data for write to address specified by PhyRegAd.                           |

| 11 to 8  | PhyAdRxReg   | Value of the read Phy register address during read.                                 |

| 7 to 0   | PhyDataRxReg | Value of the read Phy register data during read.                                    |

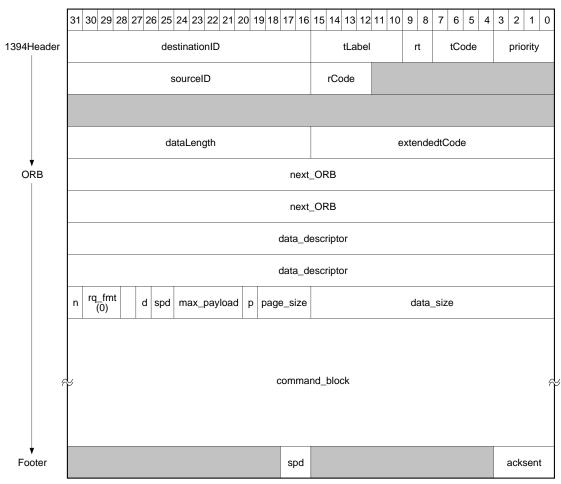

#### 9) ADP1 Registers

These registers are used to set the ADP.

The register address is 24h and the initial value is 0000\_0000h.

| Bit      | Name     | Function                                                                                                                                                                          |

|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 to 10 | tLabel   | Indicates the Transaction Label and is used in a pair with the response packet to that request packet. (Do not use the tLabel set with ADP for packets transmitted from the ATF.) |

| 3 to 0   | priority | Indicates the priority level of the packet.<br>In the case of a value other than "0", the transmitter uses priority Arbitration<br>for this packet.                               |

#### 10) ADP2 Registers

These registers are used for setting of the ADP.

The register address is 28h and the initial value is 0000\_0000h.

| Bit      | Name                  | Function                                                                                                                                                                         |

|----------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 to 16 | destinationID         | The bus number of the destination of the packet is represented with 10 bits, while the node number is represented with 6 bits.                                                   |

| 15 to 0  | segment_base<br>_High | For a continuous area (segment_base_High, segment_base_Low and, depending on the case, segment_offset), this indicates the address of the address space of the destination node. |

#### 11) ADP3 Registers

These registers are used for setting of the ADP.

The register address is 2Ch and the initial value is 0000\_0000h.

All 32 bits are at segment\_base\_Low when in Mode0 or 1.

In Mode2, the lower bit (page\_size + 8) is at segment\_offset, while the upper bit is at segment\_base\_Low.

Mode0 and Mode1

| ſ | Bit     | Name                 | Function                                                                                                                                                                                                                  |

|---|---------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 31 to 0 | segment_base<br>_Low | For a continuous area (segment_base_High, segment_base_Low), this indicates the address of the address space of the destination node. This address must be in word units when the Control register AIDT16 = "1" in Mode1. |

Mode2

| Bit          | Name                 | Function                                                                                                                                                                                                                          |

|--------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 to b      | segment_base<br>_Low | For 3 continuous areas (segment_base_High, segment_base_Low, segment_offset), this indicates the address of the address space of the destination node. This address must be in word units when the Control register AIDT16 = "1". |

| (b – 1) to 0 | segment_offset       | In the case of Mode2 that supports transfer by page_table, this indicates the lower bit of the first address of the element. It also sets the segment_offset value of ORB.                                                        |

$b = (page_size + 8)$

#### 12) ADP4 Registers

These registers are used for setting of the ADP.

The register address is 30h and the initial value is 0000\_0000h.

| Bit      | Name          | Function                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31       | notify (n)    | This is the notify bit of the ORB format. This has not effect on this IC. Please use it as memory.                                                                                                                                                                                                                                                                                                                                                    |

| 27       | direction (d) | This is used to determine the direction of ADP transfer.<br>0: Reception of data from the initiator to this link.<br>1: Transmission of data from this link to the initiator.<br>This is used to set the direction value of the ORB. (Since ADP transmission<br>and reception is switched with this bit, only perform writing to this register<br>after the series of Transactions with the ADP have been completed and the<br>ADP is not operating.) |

| 26 to 24 | spd           | This is the transfer rate of the 1394 serial bus.<br>0: S100<br>1: S200<br>2 to 7: Reserved (Do not set to these values.)<br>This bit is used to set the spd value of the ORB.                                                                                                                                                                                                                                                                        |

| 23 to 20 | max_payload   | This indicates the maximum data_length with 2 <sup>^</sup> (max_payload + 2).<br>It is used to set the max_payload value of the ORB. A value of 8 is set when<br>a value larger than 8 is set with the CXD3220R.                                                                                                                                                                                                                                      |

| 19       | р             | This is the page_table_present bit.<br>This is set to "1" when using the page_table, and set to "0" when not using.<br>The device enters Mode2 when "1".<br>This is used to set the p value of the ORB.                                                                                                                                                                                                                                               |

| 18 to 16 | page_size     | This bit represents the data_length of one page.<br>page_length is represented with 2 <sup>^</sup> (page_size + 8).<br>It is used to set the page_size value of the ORB.                                                                                                                                                                                                                                                                              |

| 15 to 0  | xfer_length   | This represents the data buffer length in Mode0 or 1, and is used to set the data_size value of the ORB. In Mode2, it represents the segment length, and is used to set the Segment_Length value of the Page Table. (Do not start the ADP when xfer_length = $0$ .)                                                                                                                                                                                   |

#### 13) ADP Control Registers

These registers are used for controlling the ADP. The register address is 34h and the initial value is 0000\_0000h.

| Bit | Name     | Function                                                                                                                                                                                                                              |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | ADPreset | Returns the ADP to the initial state. Clears the ADP status register.                                                                                                                                                                 |

| 1   | ADPstop  | This bit is set to "1" when stopping the ADP.<br>The ADP is then stopped after it has normally completed the Transaction of<br>the packet currently loaded in the ADPTF or an error has occurred, after<br>which this bit is cleared. |

| 0   | ADPgo    | This bit is set to "1" when starting the ADP.<br>The ADP is then stopped after it has normally completed or an error has<br>occurred, after which this bit is cleared.                                                                |

#### 14) ADP Status Registers

These registers are used for reading the ADP Status value. The register address is 38h and the initial value is 0000\_0000h. This register is for read only.

| Bit      | Name  | Function                                                                                                                                                                                           |

|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 to 12 | err   | This indicates the error code (see below) of the ADP.<br>The Interrupt ADPErr bit rises when an error has occurred.                                                                                |

| 11 to 8  | rcode | This indicates the response code of a response packet that has returned to the ADP from the initiator. "1111" is written in the case of a Write Transaction that has become a unified Transaction. |

| 7 to 4   | ack-i | Writes the Ack code for the request packet.                                                                                                                                                        |

| 3 to 0   | ack-o | Writes the Ack code transmitted by the ADP for the response packet.                                                                                                                                |

These registers are cleared when a ADPgo bit has been set. After a ADPgo bit has been set and the ADP has started, the following occurs in the case any type of error occurs in the request packet or response packet.

1) Generation of a request packet is stopped.

2) The rcode and Ack are latched, and stored in the ADP Status register.

3) An interrupt is generated.

This register is cleared when ADPreset = 1.

# <List of Error Codes>

| err value     | meaning                                                              |

|---------------|----------------------------------------------------------------------|

| 0 (all clear) | no error                                                             |

| 1             | error ack code received (for request packet)                         |

| 2             | error ack code sent (for response packet)                            |

| 3             | split transaction time-out                                           |

| 4             | busy_timeout                                                         |

| 5             | bus reset occurred                                                   |

| 6             | bad rcode received                                                   |

| 7             | receive response packet<br>from a node other than the specified node |

| 8             | bad tCode received<br>(bad tCode is 2 [d = 0], $6/7$ [d = 1])        |

(When two or more error codes occur at the same time, the code with the lower code value is displayed.)

#### **15) Transaction Timeout Registers**

In the case the Ack code of ack\_busy has returned after the ADP has sent a request packet, there is a function for retransmitting the subject request packet.

These registers are used to set the limit value of the timeout required until a response packet is sent back after a request packet has been transmitted during Split Transaction, as well as the upper limit of the number of times retry is performed when an Ack code has returned as ack\_busy. The register address is 3Ch, and the Initial value is 800 (dec).

| Bit      | Name           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27 to 20 | retry_interval | This designates the retry interval. The packet is retransmitted after waiting for $125\mu s \times (retry\_interval)$ . When set to "0", transmission is performed immediately without waiting for the interval.                                                                                                                                                                                                                                                                                                                                                                                   |

| 19 to 16 | retry_limit    | The retry_limit bit controls retry when a single-phase retry protocol is in use.<br>When this bit is set to "0", packet transfer that was busy is not retried. When<br>set to a value other than "0", packet transfer is retried for the maximum<br>number of retries (retry_limit) until any Ack code returns other than a busy<br>acknowledgement. When a packet is unable to be transferred as a result of<br>being busy after the maximum number of retries, the ADP stops the<br>processing of that packet. A busy_timeout error is indicated in the err field of<br>the ADP Status register. |

| 15 to 0  | split_timeout  | When Split Transactions are being performed, the ADP stops processing when the amount of time for a response packet sent in response to a request packet to return exceeds (split_timeout $\times$ 125) µs. A split transaction_timeout error is displayed in the err field of the ADP Status register.                                                                                                                                                                                                                                                                                            |

#### 16) ADP FIFO Status Registers

These registers make it possible to monitor and control ADP status.

The register address is 40h and the initial value is 0428\_0000h.

Reading and writing are only possible for the Clear ADPTF bit and Clear ADPRF bit. Reading and writing of other bits is possible only when the regRW bit is set to "1". These bits are for read only when it is set to "0".

| Bit | Name        | Function                                                                                                                       |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------|

| 31  | ADPRFFull   | Indicates that the ADPRF is full and reception is not possible when "1".                                                       |

| 30  | ADPRFAFull  | Indicates that the ADPRF is able to receive only one more quadlet when "1".                                                    |

| 29  | ADPRF4Th    | Indicates that four or more quadlets of data have been written into the ADPRF when "1".                                        |

| 28  | ADPRFDc     | This is a control bit for reading packets from the ADPRF. This bit is "1" only during the first and last quadlets of a packet. |

| 27  | ADPRFAEmpty | Indicates that only one quadlet of data has been written into the ADPRF when "1".                                              |

| 26  | ADPRFEmpty  | Indicates that the ADPRF is empty and there is no data that can be read when "1".                                              |

| 23  | ADPTFFull   | Indicates that the ADPTF is full and that writing is not possible when "1".                                                    |

| 22  | ADPTFAFull  | Indicates that only one more quadlet can be written into the ADPTF when "1".                                                   |

| 21  | ADPTF4Avail | Indicates that only four more quadlets can be written into the ADPTF when "1".                                                 |

| 20  | ADPTFAEmpty | Indicates that there is only one quadlet of data that has not been transmitted in the ADPTF when "1".                          |

| 19  | ADPTFEmpty  | Indicates that the ADPTF is empty and there is no data that can be transmitted when "1".                                       |

| 15  | ClearADPTF  | Sync resets the ADPTF when "1" (Self Clear).                                                                                   |

| 13  | ClearADPRF  | Sync resets the ADPRF when "1" (Self Clear).                                                                                   |

#### 17) TEST Mode Registers

These registers are used to control the test mode of the CXD3220R. They are normally set to 0000\_0000h.

The register address is 44h and the initial value is 0000\_0000h. Do not write in this register.

#### 18) ATFWrite (first quadlet of the packet) Registers

The first quadlet of the transmitted Asynchronous packet is written in these registers.

The register address is 70h and the initial value is 0000\_0000h.

| Bit     | Name                                         | Function                                                         |

|---------|----------------------------------------------|------------------------------------------------------------------|

| 31 to 0 | ATFWrite<br>(first quadlet of<br>the packet) | Writes the first quadlet of the transmitted Asynchronous packet. |

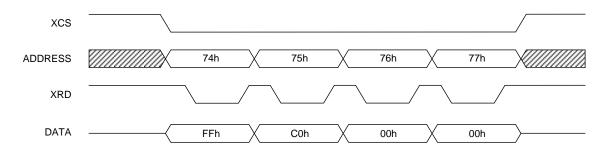

#### 19) ATFWrite/ARFRead Registers

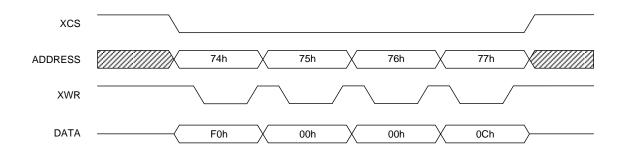

The second through the next to the last quadlets of the transmitted Asynchronous packet are written in these registers. Also, the Asynchronous packet read from the ARF during receive is written one quadlet at a time. The register address is 74h and the initial value is 0000\_0000h.

| Bit     | Name                 | Function                                                                                                                                                                                                            |

|---------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 to 0 | ATFWrite<br>/ARFRead | <ul><li>Transmit: Writes the second through the next to the last quadlets of the transmitted Asynchronous packet.</li><li>Receive: Reads one quadlet at a time for the Asynchronous packet read from ARF.</li></ul> |

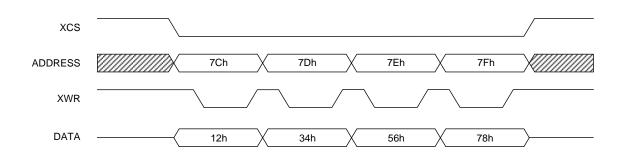

# 20) ATFWrite (confirm write) Registers

The last quadlet of the transmitted Asynchronous packet is written in these registers. The register address is 7Ch and the initial value is 0000\_0000h.

| Bit     | Name                        | Function                                                        |

|---------|-----------------------------|-----------------------------------------------------------------|

| 31 to 0 | ATFWrite<br>(confirm write) | Writes the last quadlet of the transmitted Asynchronous packet. |

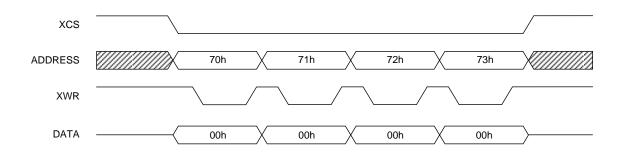

#### 6-3. Asynchronous Packet Transmission

Packet data is written from the external CPU to the ATF inside the CXD3220R in order to transmit an Asynchronous packet. At this time the first quadlet of the packet only is written in the CFR ATFWrite (first quadlet of the packet) register (70h). The second through the next to the last quadlets are written in the CFR ATFWrite/ARFRead registers (74h). Then the last quadlet is written in the CFR ATFWrite (confirm write) register (7Ch) and the packet is stored in the ATF.

However, if the ATF is full, write will not actually be performed even when write is executed. Once the bus is enabled, transmit takes place automatically.

The procedure for transmitting a Quadlet Write request packet is given here as an example. (for 8-bit data interface)

#### (1) Confirming that the ATF is not full

The CFR Async Status register (1Ch to 1Fh) is read to confirm that the 23th bit (AtfFull bit) is low. If it is high it means that there are some unsent packets stored and it waits until they are transmitted.

The number of quadlets that can be stored in the ATF can be found from the value of the Async Status register bits [23:19]. The following six states can be found, so a judgment must be made as to whether write is possible from the number of quadlets in the packet being sent from the external CPU.

AtfFull = High: Can't Write AtfAFull = High: Only one quadlet All bits low: 2 to 3 quadlets Atf4Avail = High: 4 to 22 quadlets Atf4Avail = High, AtfAEmpty = High: 4 to 23 quadlets Atf4Avail = High, AtfEmpty = High: 4 to 24 quadlets

#### (2) First quadlet of the transmitted packet Write

Let the first quadlet of the Quadlet Write request packet be "00000000h".

This is written in the CFR ATFWrite (first quadlet of the packet) register.

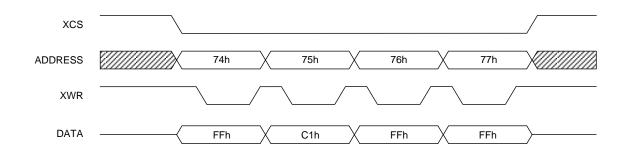

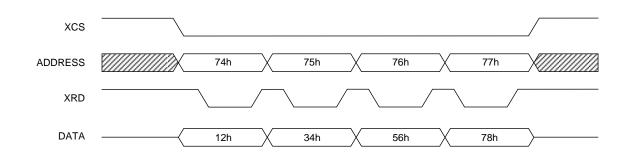

# (3) Second quadlet of the transmitted packet Write

Let the second quadlet of the Quadlet Write request packet be "FFC1FFFFh". This is written in the CFR ATFWrite/ARFRead register.

#### (4) Third quadlet of the transmitted packet Write

Let the third quadlet of the Quadlet Write request packet be "F000000Ch". This is written in the CFR ATFWrite/ARFRead register.

#### (5) Last quadlet of the transmitted packet Write

Let the last quadlet of the Quadlet Write request packet be "12345678h". This is written in the CFR ATFWrite (confirm write) register.

The Quadlet Write request packet is stored in the ATF as shown above. When the bus is enabled, the CXD3220R transmits automatically. If transmit does not take place, the CFR interrupt register (0Ch to 0Fh) must be read to confirm if the ATStk bit or TCErr bit is high. If these bits are high, the packet stored in the ATF may not be correct.

- ATStk = High: If the first quadlet of the packet was not written in the CFR ATFWrite (first quadlet of the packet) register but was written in the ATFWrite/ARFRead register or the ATFWrite (confirm write) register.

- TCErr = High: A value that is not a Transaction code able to be transmitted by Asynchronous packet is written in the tCode field of the first quadlet of the packet.The Transaction codes that can be transmitted as Asynchronous packets are any of (0, 1, 2, 4, 5, 6, 7, 9, B, Eh).

For either of ATStk or TCErr above, the next packet for write will not be transmitted even if it is correct. At this time "1" must be written in the CFR Async Status register ClearATF bit in order to clear the ATF. Transmit is then enabled when a correct packet is written.

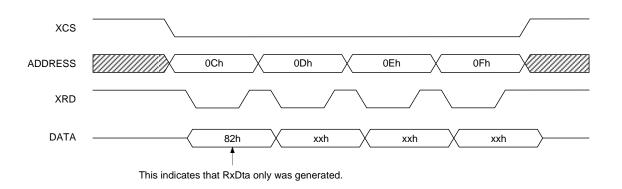

#### 6-4. Asynchronous Packet Reception

Basically, if there is room to write the packet in FIFO and the destination\_ID matches, then Asynchronous packets are received. Receive is completed when the packet data is read from the ARF inside the CXD3220R by the external CPU.

The CXD3220R raises an RxDta flag when a packet is received. (Normally, if the RxDta bit of the CFR Interrupt Mask register (10h to 13h) is set to "1", XINT goes low when a packet is received and this can be detected.) Next, the CFR Async Status register (1C to 1Fh) ArfEmpty bit should be low. This indicates that a correct packet was received.

After this, one quadlet at a time can be read by reading the CFR ATFWrite/ARFRead registers (74h to 77h). Packet receive is completed by repeating this until the ArfEmpty bit goes high.

However, if the ARF status is empty, read will not be done even if it is executed. In this case, the data read by the CPU will be the previously read value.

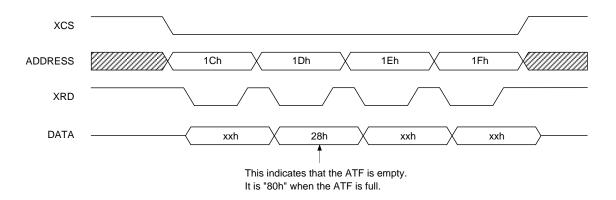

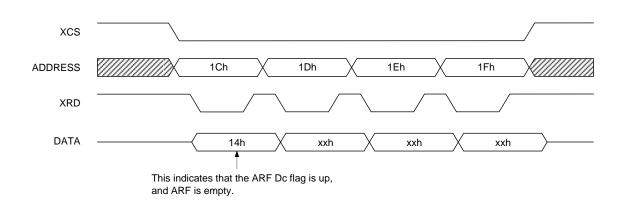

The procedure for receiving a Quadlet Write request packet is given here as an example. (for 8-bit data interface)

#### (1) Confirming that the packet was received

The CFR Interrupt register (0Ch) is read to confirm that the 25th bit (RxDta bit) is high.

When only desiring to know information about the register of the lower 2 bits A [1:0] = 00 of the address, only the address of A [1:0] = 00 may be read. In the case of reading register information for A [1:0] = 01, 10, 11 read the addresses in order starting from the address of A [1:0] = 00.

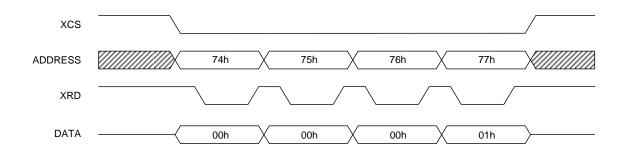

#### (2) Confirming that the received packet was stored correctly in FIFO

The CFR Async Status register (1C to 1Fh) is read to confirm that the 26th bit (ArfEmpty bit) is low.

If this bit is high it means that reception may be in progress (all quadlets have not arrived). In this state, do not read the ARF read register (74 to 77h). Wait some time and again read the Async Status register to confirm the ArfEmpty bit.

In the above example, ArfEmpty is low. Data read is possible because the ArfEmpty bit is low.

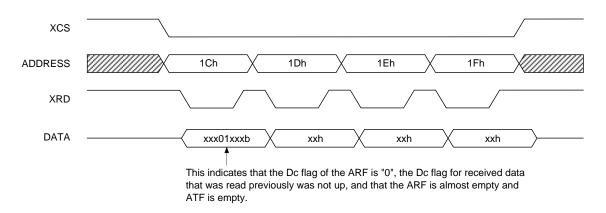

# (3) First quadlet of the received packet Read

The CFR ATFWrite/ARFRead register is read.

The data read is "FFC00000h".

At this time, the ArfDc bit is high (from (2) above), so this quadlet is the first quadlet.

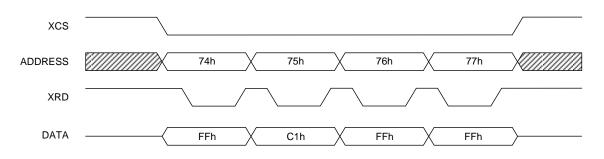

#### (4) Second quadlet of the received packet Read

The CFR ATFWrite/ARFRead register is read.

The data read is "FFC1FFFh".

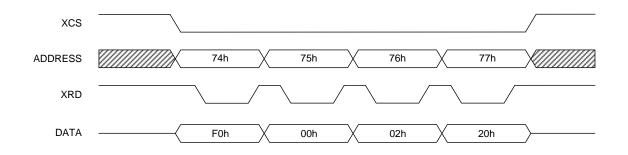

#### (5) Third quadlet of the received packet Read

The CFR ATFWrite/ARFRead register is read.

The data read is "F0000220h".

#### (6) Fourth quadlet of the received packet Read

The CFR ATFWrite/ARFRead register is read.

The data read is "12345678h".

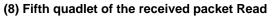

#### (7) Checking for remaining packets still in FIFO

Four quadlets were read in preceding items (1) to (6). They were read continuously because Arf4There was high.

If Arf4There was low, Async Status must be read after one quadlet is read, to find out if ArfEmpty is high. Even if Arf4There is high, as in this case, after the fourth quadlet read must be done while checking ArfEmpty and ArfDc in the same way.

In the above example the Arf4There bit is low, so a maximum of three more quadlets can be predicted, but the ArfAEmpty bit is high, so there is only one more quadlet in FIFO.

The CFR ATFWrite/ARFRead register is read.

The data read is "00000001h".

The lower 4 bits of this quadlet are the ackSent field, and this indicates "01h" transmitted as this packet's Ack\_code. This is always written even if the packet is one which does not have Ack\_code transmitted, such as a broadcast packet.

If this value is "04h", the ARF may have become full during receive and quadlets may be missing.