## MK5027 SS7 SIGNALLING LINK CONTROLLER

- CMOS

- FULLY COMPATIBLE WITH BOTH 8 OR 16 BIT SYSTEMS

- SYSTEM CLOCK RATE TO 10MHz. DATA RATE UP TO 2.5Mbps FOR SS7 PROTOCOL PROCESSING,7Mbps FOR TRANSPARENT HDLC MODE

- COMPLETE LEVEL 2 IMPLEMENTATION

- COMPATIBLE WITH 1988 CCITT, AT&T, ANSI, AND BELLCORE SIGNALLING SYS-TEM NUMBER 7 LINK LEVEL PROTOCOLS

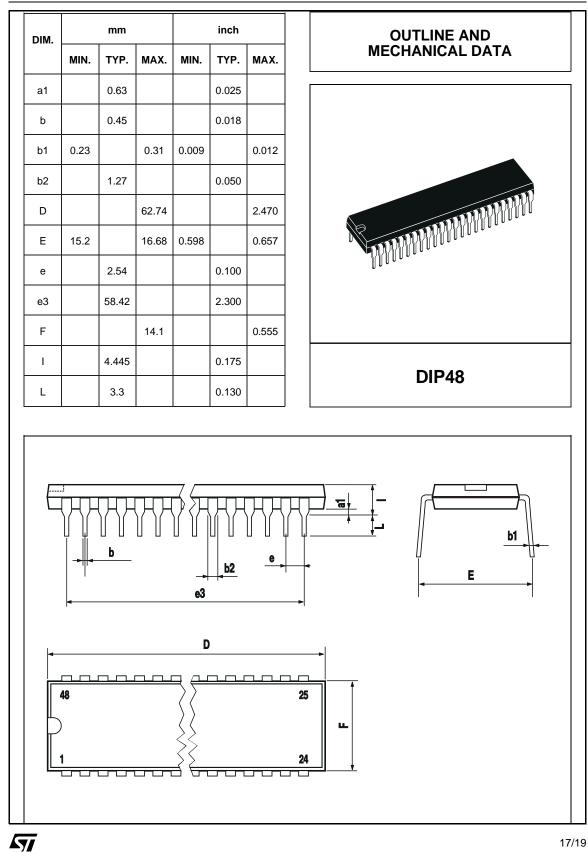

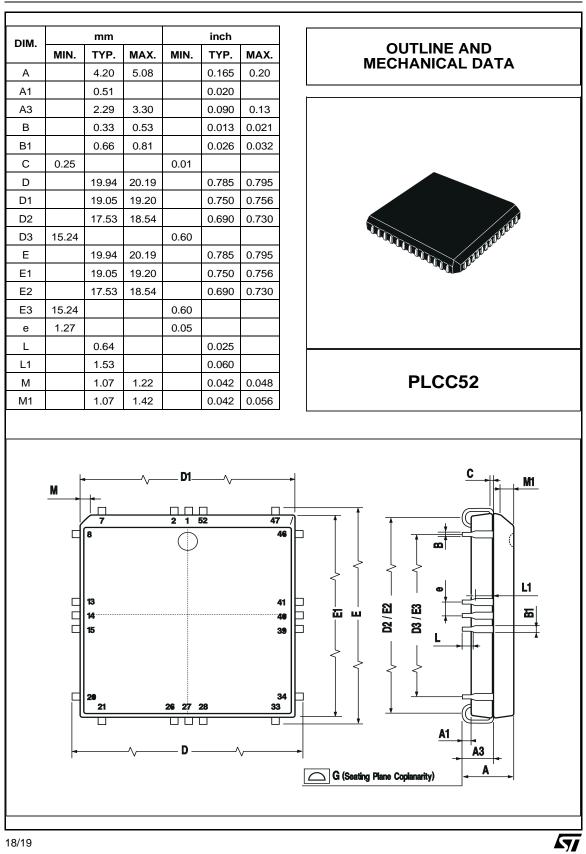

- 52 PIN PLCC AND 48-PIN DIP PIN-FOR-PIN COMPATIBLE WITH THE SGS-THOMSON X.25 CHIP (MK5025) AND NEARLY PIN-FOR-PIN COMPATIBLE WITH THE SGS-THOM-SON VLANCE CHIP (MK5032)

- BUFFER MANAGEMENT INCLUDES:

- Initialization Block

- Separate Receive and Transmit Rings

- Variable Descriptor Ring and Window Sizes.

- ON CHIP DMA CONTROL WITH PROGRAM-MABLE BURST LENGTH

- SELECTABLE BEC OR PCR RETRANSMIS-SION METHODS, INCLUDING FORCED RE-TRANSMISSION FOR PCR

- HANDLES ALL 7 SS7 TIMERS

- HANDLES ALL SS7 FRAME FORMATTING:

Zero bit insert and delete

- FCS generation and detection

- Frame delimiting with flags

- PROGRAMMABLE MINIMUM SIGNAL UNIT SPACING (number of flags between SU's)

- HANDLES ALL SEQUENCING AND LINK CONTROL

- SELECTABLE FCS OF 16 OR 32 BITS.

- TESTING FACILITIES:

- Internal Loopback

- Silent Loopback

- Optional Internal Data Clock Generation

Self Test

- ALL INPUTS AND OUTPUTS ARE TTL COM-PATIBLE

- PROGRAMMABLE FOR FULL OR HALF DU-PLEX OPERATION

#### DESCRIPTION

The SGS-THOMSON Signalling System #7 Signalling Link Controller (MK5027) is a VLSI semi-

September 2003

conductor device which provides a complete link control function conforming to the 1988 CCITT version of SS7. This includes frame formatting, transparency (so called "bit-stufling"), error recovery by two types of retransmission, error monitoring, sequence number control, link status control, and FISU generation. One of the outstanding features of the MK5027 is its buffer management which includes on-chip DMA. This feature allows users to handlq multiple packets of receive and transmit data at a time. (A conventional data linkcontrol chip plus a separate DMA chip would handle data for only a single block at a time.) The MK5027 may be used with any of several popular 16 and 8 bit microprocessors, such as 68000, 6800, Z8000, Z80, LSI-11, 8086, 8088, 8080, etc.

#### Figure 1: Pin Connection.

| VSS-GND           | 1  | 48 | VCC (+5V) |

|-------------------|----|----|-----------|

| DAL07             | 2  | 47 | DAL08     |

| DAL06             | 3  | 46 | DAL09     |

| DAL05             | 4  | 45 | DAL10     |

| DAL04             | 5  | 44 | DAL11     |

| DAL03             | 6  | 43 | DAL12     |

| DAL02             | 7  | 42 | DAL13     |

| DAL01             | 8  | 41 | DAL14     |

| DAL00             | 9  | 40 | DAL15     |

| READ              | 10 | 39 | A16       |

| INTR              | 11 | 38 | A17       |

| DALI              | 12 | 37 | A18       |

| DALO              | 13 | 36 | A19       |

| DAS               | 14 | 35 | A20       |

| BMO, BYTE, BUSREL | 15 | 34 | A21       |

| BMI, BUSAKO       | 16 | 33 | A22       |

| HOLD, BUSRQ       | 17 | 32 | A23       |

| ALE, AS           | 18 | 31 | RD        |

| HLDA              | 19 | 30 | DSR, CTS  |

| cs 🗆              | 20 | 29 | TD        |

| ADR               | 21 | 28 | SYSCLK    |

| READY             | 22 | 27 | RCLK      |

| RESET             | 23 | 26 | DTR, RTS  |

| VSS-GND           | 24 | 25 | TCLK      |

|                   | I  |    |           |

# Table 1: Pin Description.LEGEND:

| I Input only | 0 | Output only |

|--------------|---|-------------|

|--------------|---|-------------|

| 10 | Input/Output | 3S | 3-State |

|----|--------------|----|---------|

|----|--------------|----|---------|

OD Open Drain (no internal pull-up)

| Signal Name           | Pin(s)       | Туре  | Descriplion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------|--------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DAL<15:00>            | 2-9<br>40-47 | IO/3S | The time multiplexed Data Address bus. During the address portion of a memory transfer, DALe15:00 contains the lower 16 bits of the memory address.<br>During the data portion of a memory transfer, DAL<15:00> contains the read or write data, depending on the type of transfer.                                                                                                                                                                                                                                                                                                                                                      |

| READ                  | 10           | IO/3S | READ indicates the type of operation that the bus controller is performing<br>during a bus transaction. READ is driven by the MK5027 only while it is<br>the BUS MASTER. READ is valid during the entire bus transaction and is<br>tristated at all other times.<br>MK5027 as a Bus Slave:<br>READ = HIGH - Data is placed on the DAL lines by the chip.<br>READ = LOW - Data is taken off the DAL lines by the chip.<br>MK5027 as a Bus Master:<br>READ = HIGH - Data is taken off the DAL lines by the chip.<br>READ = LOW - Data is placed on the DAL lines by the chip.<br>READ = LOW - Data is placed on the DAL lines by the chip. |

| INTR                  | 11           | O/OD  | INTERRUPT is an attention interrupt line that indicates that one or more of the following CSR0 status flags is set: MISS, MERR, RINT, TINT or PINT. INTERRUPT is enabled by CSR0<0.9>, INEA = 1.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DALI                  | 12           | O/3S  | DAL IN is an external bus transceiver control line. DALI is driven by the MK5027 only while it is the BUS MASTER. DALI is asserted by the MK5027 when   ads from the DAL lines during the data portion of a READ transfer. DALI is not asserted during a WRITE transfer.                                                                                                                                                                                                                                                                                                                                                                 |

| DALO                  | 13           | O/3S  | DAL OUT is an external bus transceiver control line. DALO is driven by the MK5027 only while it is the BUS MASTER. DALO is asserted by the MK5027 when it drives the DAL lines during the address portion of a READ transfer or for the duration of a WRITE transfer.                                                                                                                                                                                                                                                                                                                                                                    |

| DAS                   | 14           | IO/3S | DATA STROBE defines the data portio,n of a transaction. By definition, data is stable and valid at the low to high transition of DAS. This signal is driven by the MK5027 while it is the BUS MASTER. During the BUS SLAVE operation, this pin is used as an input. At all other times the signal is tristated.                                                                                                                                                                                                                                                                                                                          |

| BMO<br>BYTE<br>BUSREL | 15           | IO/3S | I/O pins 15 and 16 are programmable through CSR4. If bit 06 of CSR4 is set to a one, pin 15 becomes input BUSREL and is used by the host to signal the MK5027 to terminate a DMA burst after the current bus transfer has completed. If bit 06 is clear the pin 15 is an output and behaves as described below for pin 16.                                                                                                                                                                                                                                                                                                               |

Note: Pin out shown is for 48 pin dip.

Table 1: Pin Description (continued)

| Signal Name   | Pin(s) | Туре  | Descriplion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|--------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BM1<br>BUSAKO | 16     | O/3S  | Pins 15 and 16 are programmable though bit 00 of CSR4 (BCON).      If CSR4<00> BCON = 0,      I/O PIN 15 = BMO (O/3S)      BYTE MASK<1:0> indicates the byte(s) on the DAL to be read or written during this bus transaction. MK5027 drives these lines only as a Bus Master. MK5027 ignores the BM lines when it is a Bus Slave.      Byte selection is done as outlined in the following table.      BM1    BM0      TYPE OF TRANSFER      LOW    ENTIRE WORD      LOW    HIGH      UPPER BYTE (DAL<15:08>)      HIGH    LOW ENTIRE WORD      LOW    HIGH      UPPER BYTE (DAL<15:08>)      HIGH    HOW      If CSR4<00>BCON = 1,      I/O PIN 15 = BYTE (O/3S)      I/O PIN 16 = BUSAKO (O)      Byte selection is done using the BYTE line and DAL<00> latched during the address portion of the bus transaction. MK5027 drives BYTE only a Bus Master and ignores it when a Bus Slave. Byte selection is done as outlined in the following table.      BYTE    DAL<00>    TYPE OF TRANSFER      LOW    LOW    ENTIRE WORD      LOW    HIGH    ILLEGAL CONDITION      HIGH    LOW    ENTIRE WORD      LOW    HIGH    ILLEGAL CONDITION      HIGH    UPPER BYTE    BUSAKO |

| HOLD<br>BUSRQ | 17     | IO/OD | bit operation.<br>Pins 17 is configured through bit 0 of CSR4.<br>If CSR4<00> BCON = 0,<br>I/O PIN 17 = HOLD<br>HOLD request is asserted by MK5027 when it requires a DMA cycle, if<br>HLDA is inactive, regardless of the previous state of the HOLD pin.<br>HOLD is held low for the entire ensuing bus transaction.<br>If CSR4<00> BCON = 1,<br>I/O PIN 17 = BUSRQ<br>BUSRQ is asserted by MK5027 when it requires a DMA cycle if the prior<br>state of the BUSRQ pin was high and HLDA is inactive. BUSRQ is held<br>low for the entire ensuing bus transaction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ALE<br>AS     | 18     | O/3S  | The active level of ADDRESS STROBE is programmable through CSR4.<br>The address portion of a bus transfer occurs while this signal is at its<br>asserted level. This signal is driven by MK5027 while it is the BUS<br>MASTER. At all other times, the signal is tristated.<br>If CSR4<01> ACON = 0,<br>I/O PIN 18 = ALE<br>ADDRESS LATCH ENABLE is used to demultiplex the DAL lines and define<br>the address portion of the transfer and remains low during the data portion.<br>If CSR4<01> ACON = 1,<br>I/O PIN 18 = $\overline{AS}$<br>As $\overline{AS}$ , the signal pulses low during the address portion of the bus<br>transfer. The low to high transition of $\overline{AS}$ can be used by a slave device to<br>strobe the address into a register.<br>$\overline{AS}$ is effectively the inversion of ALE.                                                                                                                                                                                                                                                                                                                                                     |

| HLDA          | 19     | I     | HOLD AKNOWLEDGE is the response to HOLD. When HLDA is low in response to MK5027's assertion of HOLD, the MK5027 is the Bus Master. HLDA should be desasserted ONLY after HOLD has been released by the MK5027.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Table 1: | Pin Des | cription | (continued) |

|----------|---------|----------|-------------|

|----------|---------|----------|-------------|

| Signal Name | Pin(s) | Туре  | Descriplion                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|--------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS          | 20     | I     | CHIP SELECT indicates, when low, that the MK5027 is the slave device for the data transfer.CS must be valid througout the enture transaction.                                                                                                                                                                                                                                                                                                                  |

| ADR         | 21     | I     | ADDRESS selects the Register Address Port or the Register Data Port. It<br>must be valid throughout the data portion of the transfer and is only used<br>by the chip when CS is low.<br>ADR PORT<br>LOW REGISTER DATA PORT                                                                                                                                                                                                                                     |

|             |        |       | HIGH REGISTER ADDRESS PORT                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| READY       | 22     | IO/OD | When the MK5027 is a Bus Master, READY is an asynchronous acknowledgement from the bus memory that memory will accept data in a WRITE cycle or that memory has put data on the DAL lines in a READ cycle.<br>As a bus Slave, the MK5027 asserts READY when it has put data on the DAL lines during a READ cycle or is about to take data from the DAL lines during WRITE cycle. READY is a response to DAS and it will be released after DAS or CS is negated. |

| RESET       | 23     | I     | RESET is the Bus signal that will cause MK5027 to cease operation, clear its internal logic and enter an idle state with the Power Off bit of CSR0 set.                                                                                                                                                                                                                                                                                                        |

| TCLK        | 25     | I     | TRANSMIT CLOCK. A 1x clock input for transmitter timing. TD changes on the falling edge of $\overline{\text{TCLK}}$ . The frequency of $\overline{\text{TCLK}}$ may not be greater than the frequency of SYSCLK.                                                                                                                                                                                                                                               |

| DTR<br>RTS  | 26     | IO    | DATA TERMINAL READY, REQUEST TO SEND. Modem control pin. Pin 26 is configurable through CSR5. This pin can be programmed to behave as output RTS or as programmable IO pin DTR. If configured as RTS, the MK5027 will assert this pin if it has data to send and throughout the transmission of a signal unit.                                                                                                                                                 |

| RCLK        | 27     | I     | RECEIVE CLOCK. A 1x clock input for receiver timing. RD is sampled on the rising edge of RCLK. The frequency of RCLK may not be greater than the frequency of SYSCLK.                                                                                                                                                                                                                                                                                          |

| SYSCLK      | 28     | I     | SYSTEM CLOCK. System clock used for internal timing of the MK5027.<br>SYSCLK should be a square wave, of frequency up to 10MHz.                                                                                                                                                                                                                                                                                                                                |

| TD          | 29     | 0     | TRANSMIT DATA. Transmit serial data output.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DSR<br>CTS  | 30     | IO    | DATA SET READY, CLEAR TO SEND. Modem Control Pin. Pin 30 is configurable through CSR5. This pin can be programmed to behave as input CTS or as programmable IO pin DSR. If configured as CTS, the MK5027 will transmit all ones while CTS is high.                                                                                                                                                                                                             |

| RD          | 31     | I     | RECEIVE DATA. Received serial data input.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A<23:16>    | 32-39  | O/3S  | Address bits <23:16> used in conjunction with DAL <15:00> to produce a 24 bit address. MK5027 drives these lines only as a Bus Master. A23-A20 may be driven continuously as described in the CSR4<7> BAEN bit.                                                                                                                                                                                                                                                |

| VSS-GND     | 1, 24  |       | Ground Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VCC         | 48     |       | Power Supply Pin<br>+5.0 VDC ± 5%                                                                                                                                                                                                                                                                                                                                                                                                                              |

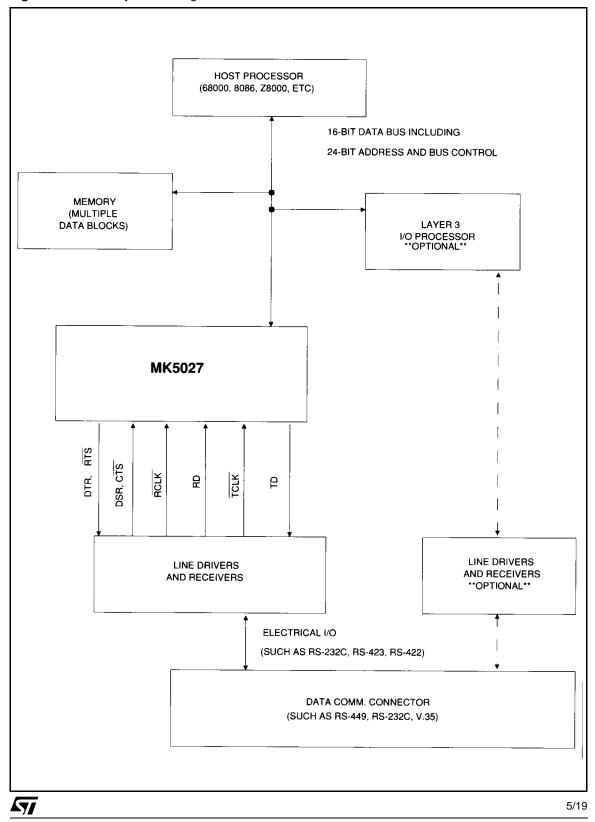

Figure 2: Possible System Configuration for the MK5027.

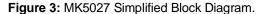

#### **OPERATIONAL DECRIPTION**

The SGS-THOMSON Signalling System #7 Signalling Link Controller (MK5027) device is a VLSI product intended for data communication applications requiring SS7 link level control. The MK5027 will perform all frame formatting, such as: frame delimiting with flags, FCS generation and detection. It will also perform all error recovery and link control. The MK5027 also includes a buffer management mechanism that allow the user to transmit and/or receive multiple MSU's. Contained in the buffer management is an on-chip dual chan-

6/19

nel DMA: one channel for receive and one channel for transmit. The MK5027 handles error recovery and link status signalling.

The MK5027 is intended to be used with any popular 16 or 8 bit microprocessor. Possible system configuration for the MK5027 is shown in Figure 2. The MK5027 will move multiple blocks of receive and transmit data directly into and out of memory through the host's bus. An I/O acceleration processor in Figure 2 is recommended, but not required.

All signal pins on the MK5027 are TTL compatible. This has the advantage of making the MK5027 in- dependent of the physical interface. As shown in Figure 2. line drivers and receivers are used for electrical- connection to the physical layer.

#### SERIAL INTERFACE

The MK5027 provides two separate serial channels: one for received data and one for transmitted data. These serial channels are completely separate and may be run at different clock frequencies The receiver is responsible for recognizing frame boundries. removal of inserted zeroes (for transparency) and checking the incoming FCS. Signal units with in correct FCS values are discarded. The receiver also parallelizes the incoming data which is placed into the receive data buffers within the receive descriptor ring The transmitter is responsible for framing and serializing the data frames placed in the transmit descriptor ring. The transmitter calculates the FCS of the outgoing data and appends it to the data The transmitter generates flag sequences for inter-signal unit fill, at least two flags are transmitted between adjacent signal units. The FCS calculations for both directions of serial data optionally follow either the 16 bit CRC CCITT or the 32-bit CRC 32 algorithms FCS generation and checking can also be optionally disabled if necessary.

#### MICROPROCESSOR INTERFACE

The MK5027 contains a dual channel DMA on chip to handle data transfers to and from the host mem- ory. All access to the initialization block and descriptor rings is handled in this way The address bus is 24 bits wide and does not use any segmentation or paging methods. Data transfers can optionally be 8 and 16 bit operations. this allows easy interfacing with both 8 and 16 bit processors DMA transfers can be up to 1. 8 or an unlimited number of words per transfer under program control During bus slave operation the MK5027 allows access to its 6 control/status registers which are used to monitor and control the chip. These registers are used to control link procedures, configure interface options, control and monitor interrupt status. and more. Bus slave mode also allows both 8 and 16 bit accesses.

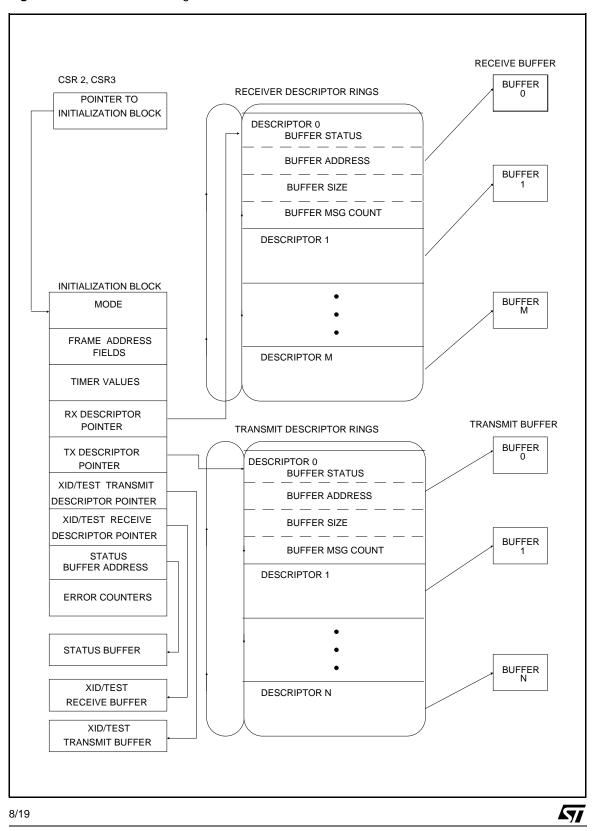

#### **BUFFER MANAGEMENT**

The basic organization of the buffer management is a circular queue of tasks in memory called descriptor rings. There are separate rings to describe the transmit and receive operations. Up to 128 buffers may be queued-up on a descriptor ring awaiting execution by the MK5027 The descriptor ring has a segment assigned to each buffer. Each segment holds a pointer for the starting address of the buffer. and holds a value for the length of the buffer in bytes.

Each segment also contains two control bits called OWNA and OWNB, which denote whether the MK5027. the HOST. or the I/O ACCELERA-TION PROCESSOR (if present) "owns" the buffer. For transmit. when the MK5027 owns the buffer. the MK5027 is allowed and commanded to transmit the buffer. When the MK5027 does not own the buffer, it will not transmit that buffer. For receive. when the MK5027 owns a buffer. it may place received data into that buffer. Conversely. when the MK5027 does not own a receive buffer, it will not place received data in that buffer.

The MK5027 buffer management mechanism will handly signal units which are longer than the length of an individual buffer. This is done by a chaining method which utilizes multiple buffers. The MK5027 tests the next segment in the descriptor ring in a "look ahead" manner. If the packet is too long for one buffer, the next bufferwill be used after filling the first buffer: that is, "chained". The MK5027 will then "look ahead" to the next buffer, and chain that buffer if necessary, and so on The operational parameters for the buffer management are defined by the user in the initialization block The parameters defined include the basic mode of operation. the number of entries for the transmitter and receiver descriptor rings. etc.

Figure 4: MK5027 Buffer Management.

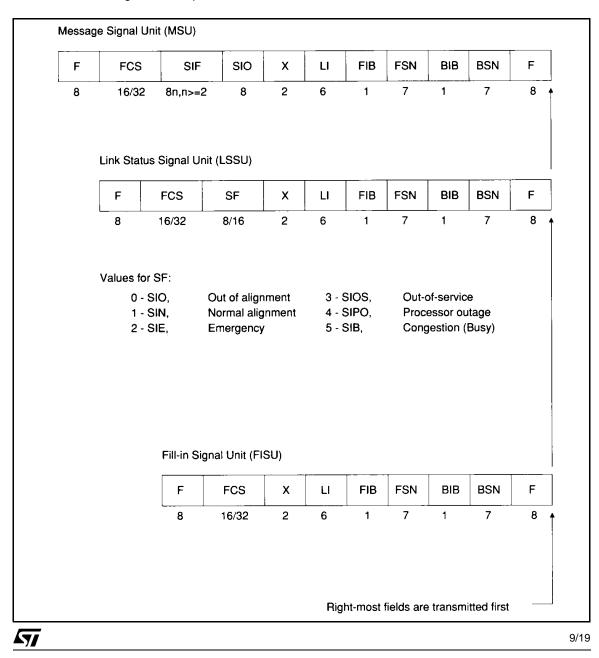

#### SIGNALLING UNIT REPERTOIRE

The signal unit repertoire of the MK5027 is shown in Table 1. This set conforms to the 1988 CCITT specification for level 2 of Signalling System #7. The definitions for the symbols for the frame types are:

| Name | Definition                   |

|------|------------------------------|

| F    | Flag Sequence                |

| FSN  | Forward Sequence Number      |

| BSN  | Backward Sequences Number    |

| FIB  | Forward Indicator Bit        |

| BIB  | Backward Indicator Bit       |

| LI   | Lenght Indicator             |

| Х    | Programmed As Zeroes         |

| SIO  | Signalling Information Octet |

| SIF  | Service Information Field    |

| SF   | Satus Field                  |

| FCS  | Frame Check Sequence         |

Table 1: MK5027 Signal Unit Repertoire.

## MK5027 ELECTRICAL SPECIFICATIONS ABSOLUTE MAXIMUM RATINGS

| Temperature under Bias                    | –25°C to +100°C    |

|-------------------------------------------|--------------------|

| Storage Temperature                       | –65℃ to +150℃      |

| Voltage on Any Pin with Respect to Ground | -0.5V to VCC +0.5V |

| Power Dissipation                         | 0.50W              |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the above device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affectdevice reliability.

#### DC CHARACTERISTICS

TA=0 °C to 70 °C, V<sub>CC</sub> = +5V  $\pm$ 5 percent unless otherwise specified.

| Symbol          | Parameter               | Min. | Тур. | Max.                 | Units |

|-----------------|-------------------------|------|------|----------------------|-------|

| VIL             |                         | -0.5 |      | +0.8                 | V     |

| VIH             |                         | +2.0 |      | V <sub>CC</sub> +0.5 | V     |

| Vol             | @ IOL = 3.2 mA          |      |      | +0.5                 | V     |

| V <sub>OH</sub> | @ IOH= -0.4 mA          | +2.4 |      |                      | V     |

| ١ <sub>١L</sub> | @ VIN = 0.4 to $V_{CC}$ |      |      | +10                  | mA    |

| Icc             | @ TSCT = 100 ns         |      | 50   |                      | μA    |

#### CAPACITANCE

f = 1MHz

| Symbol           | Parameter                  | Min. | Тур. | Max. | Units |

|------------------|----------------------------|------|------|------|-------|

| CIN              | Capacitance on Input pins  |      |      | 10   | pF    |

| C <sub>OUT</sub> | Capacitance on Output Pins |      |      | 10   | pF    |

| CIO              | Capacitance on I/O pins    |      |      | 20   | pF    |

#### AC TIMING SPECIFICATIONS

$T_A = 0$  °C to 70 °C,  $V_{CC} = +5V \pm 5$  percent, unless otherwise specified.

| No | Signal | Symbol           | Parameter                                                | Test<br>Condition | Min. | Тур. | Max.  | Units |

|----|--------|------------------|----------------------------------------------------------|-------------------|------|------|-------|-------|

| 1  | SYSCLK | T <sub>SCT</sub> | SYSCLK period                                            |                   | 100  |      | 20000 | ns    |

| 2  | SYSCLK | T <sub>SCL</sub> | SYSCLK low time                                          |                   | 45   |      |       | ns    |

| 3  | SYSCLK | T <sub>SCH</sub> | SYSCLK high time                                         |                   | 45   |      |       | ns    |

| 4  | SYSCLK | T <sub>SCR</sub> | Rise time of SYSCLK                                      |                   | 0    |      | 8     | ns    |

| 5  | SYSCLK | T <sub>SCF</sub> | Fall time of SYSCLK                                      |                   | 0    |      | 8     | ns    |

| 6  | TCLK   | T <sub>TCT</sub> | TCLK period                                              |                   | 140  |      |       | ns    |

| 7  | TCLK   | T <sub>TCL</sub> | TCLK low time                                            |                   | 63   |      |       | ns    |

| 8  | TCLK   | T <sub>TCH</sub> | TCLK high time                                           |                   | 63   |      |       | ns    |

| 9  | TCLK   | T <sub>TCR</sub> | Rise time of TCLK                                        | CL = 50 pF        | 0    |      | 8     | ns    |

| 10 | TCLK   | T <sub>TCF</sub> | Fall time of TCLK                                        |                   | 0    |      | 8     | ns    |

| 11 | TD     | T <sub>TDP</sub> | TD data propagation delay after the falling edge of TCLK | CL = 50 pF        |      |      | 40    | ns    |

| 12 | TD     | T <sub>TDH</sub> | TD data hold time after the falling edge of TCLK         |                   | 5    |      |       | ns    |

AC TIMING SPECIFICATIONS (Continued)  $T_A$  = 0 °C to 70 °C,  $V_{CC}$  = +5V  $\pm 5$  percent, unless otherwise specified.

| No | Signal | Symbol            | Parameter                                                                    | Test<br>Conditions | Min. | Тур. | Max. | Units |

|----|--------|-------------------|------------------------------------------------------------------------------|--------------------|------|------|------|-------|

| 13 | RCLK   | T <sub>RCT</sub>  | RCLK period                                                                  |                    | 140  |      |      | ns    |

| 14 | RCLK   | T <sub>RCH</sub>  | RCLK high time                                                               |                    | 63   |      |      | ns    |

| 15 | RCLK   | T <sub>RCL</sub>  | RCLK low time                                                                |                    | 63   |      |      | ns    |

| 16 | RCLK   | T <sub>RCR</sub>  | Rise time of RCLK                                                            |                    | 0    |      | 8    | ns    |

| 17 | RCLK   | T <sub>RCF</sub>  | Fall time of RCLK                                                            |                    | 0    |      | 8    | ns    |

| 18 | RD     | T <sub>RDR</sub>  | RD data rise time                                                            |                    | 0    |      | 8    | ns    |

| 19 | RD     | T <sub>RDF</sub>  | RD data fall time                                                            |                    | 0    |      | 8    | ns    |

| 20 | RD     | T <sub>RDH</sub>  | RD hold time after rising edge of RCLK                                       |                    | 5    |      |      | ns    |

| 21 | RD     | T <sub>RDS</sub>  | RD setup time prior to rising edge of RCLK                                   |                    | 30   |      |      | ns    |

| 22 | A/DAL  | T <sub>DOFF</sub> | Bus Master driver disable after rising edge of HOLD                          |                    | 0    |      | 50   | ns    |

| 23 | A/DAL  | T <sub>DON</sub>  | Bus Master driver enable after falling edge of HLDA                          | TSCT = 100ns       | 0    |      | 200  | ns    |

| 24 | HLDA   | T <sub>HHA</sub>  | Delay to fallin <u>g edge of HLDA</u> from falling edge of HOLD (Bus Master) |                    | 0    |      |      | ns    |

| 25 | RESET  | T <sub>RW</sub>   | RESET pulse width                                                            |                    | 30   |      |      | ns    |

| 26 | A/DAL  | TCYCLE            | Read/write, address/data Cycle Time                                          | TSCT = 100ns       | 600  |      |      | ns    |

| 27 | А      | T <sub>XAS</sub>  | Address setup time to falling edge<br>of ALE                                 |                    | 100  |      |      | ns    |

| 28 | А      | T <sub>XAH</sub>  | Address hold time after the rising edge of DAS                               |                    | 50   |      |      | ns    |

| 29 | DAL    | T <sub>AS</sub>   | Address setup time to falling edge<br>of ALE                                 |                    | 75   |      |      | ns    |

| 30 | DAL    | T <sub>AH</sub>   | Address hold time after the falling edge of ALE                              |                    | 20   |      |      | ns    |

| 31 | DAL    | T <sub>RDAS</sub> | Data setup time to the falling edge of DAS (Bus Master read)                 |                    | 55   |      |      | ns    |

| 32 | DAL    | T <sub>RDAH</sub> | Da <u>ta ho</u> ld time after the rising edge of DAS (bus master read)       |                    | 0    |      |      | ns    |

| 33 | DAL    | T <sub>DDAS</sub> | Data setup time to the falling edge of DAS (bus master write)                |                    | 0    |      |      | ns    |

| 34 | DAL    | T <sub>WDS</sub>  | Data setup time to the rising edge of DAS (bus master write)                 |                    | 250  |      |      | ns    |

| 35 | DAL    | T <sub>WDH</sub>  | Data hold time to the rising edge of DAS (bus slave write)                   |                    | 35   |      |      | ns    |

| 36 | DAL    | T <sub>SRDH</sub> | Data hold time after the rising edge of DAS (bus slave read)                 | TSCT = 100ns       | 0    |      | 35   | ns    |

| 37 | DAL    | T <sub>SWDH</sub> | Data hold time after the rising edge of DAS (bus slave write)                |                    | 0    |      |      | ns    |

| 38 | DAL    | T <sub>SWDS</sub> | Data setup time to the falling edge of DAS (bus slave write)                 |                    | 0    |      |      | ns    |

| 39 | ALE    | T <sub>ALEW</sub> | ALE width high                                                               |                    | 110  |      |      | ns    |

| 40 | ALE    | T <sub>DSW</sub>  | Delay from rising edge od DAS to the rising edge of ALE                      |                    | 70   |      |      | ns    |

| 41 | DAS    | T <sub>DSW</sub>  | DAS width low                                                                |                    | 200  |      |      | ns    |

11/19

AC TIMING SPECIFICATIONS (Continued)  $T_A$  = 0 °C to 70 °C,  $V_{CC}$  = +5V  $\pm 5$  percent, unless otherwise specified.

| No | Signal | Symbol            | Parameter                                                                                                        | Test<br>Conditions                        | Min. | Тур. | Max. | Units |

|----|--------|-------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------|------|------|-------|

| 42 | DAS    | T <sub>ADAS</sub> | Delay from the falling edge of ALE to the falling edge of DAS                                                    |                                           | 80   |      |      | ns    |

| 43 | DAS    | T <sub>RIDF</sub> | Delay from the rising edge of DALO<br>to the falling edge of DAS (bus<br>master read)                            |                                           | 35   |      |      | ns    |

| 44 | DAS    | T <sub>RDYS</sub> | Delay from the falling edge of READY to the falling edge of DAS                                                  | $T_{ARYD} = 300$ ns<br>$T_{SCT} = 100$ ns | 120  |      | 200  | ns    |

| 45 | DALI   | T <sub>ROIF</sub> | Delay from the rising edge of DALO<br>to the falling edge of DALI (bus<br>master read)                           |                                           | 70   |      |      | ns    |

| 46 | DALI   | T <sub>RIS</sub>  | DALI setup time to the rising edge of DAS (bus master read)                                                      |                                           | 150  |      |      | ns    |

| 47 | DALI   | T <sub>RIH</sub>  | DALI hold time after the rising edge of DAS (bus master read)                                                    |                                           | 0    |      |      | ns    |

| 48 | DALI   | T <sub>RIOF</sub> | Delay from the rising edge of DALI<br>to the falling edge of DALO (bus<br>master read)                           |                                           | 70   |      |      | ns    |

| 49 | DALO   | T <sub>OS</sub>   | DALO setup time to the falling edge of ALE (bus master read)                                                     |                                           | 110  |      |      | ns    |

| 50 | DALO   | T <sub>ROH</sub>  | DALO hold time after the falling edge of ALE (bus master read)                                                   |                                           | 35   |      |      | ns    |

| 51 | DALO   | T <sub>WDSI</sub> | Delay from the rising edge of DAS to the rising edge of DALO (bus master write)                                  |                                           | 50   |      |      | ns    |

| 52 | CS     | T <sub>CSH</sub>  | <u>CS</u> hold time after the rising edge of DAS (bus slave)                                                     |                                           | 0    |      |      | ns    |

| 53 | CS     | T <sub>CSS</sub>  | <u>CS</u> setup time to the falling edge of<br>DAS (bus slave)                                                   |                                           | 0    |      |      | ns    |

| 54 | ADR    | T <sub>SAH</sub>  | ADR hold time after the rising edge of DAS (bus slave)                                                           |                                           | 0    |      |      | ns    |

| 55 | ADR    | T <sub>SAS</sub>  | ADR setup time to the falling edge of DAS (bus slave)                                                            |                                           | 0    |      |      | ns    |

| 56 | READY  | T <sub>ARYD</sub> | Delay from the falling edge of ALE to<br>the falling edge of READY to Insure<br>a Minimum Bus Cycle Time (600ns) | T <sub>SCT</sub> = 100ns                  |      |      | 150  | ns    |

| 57 | READY  | T <sub>SRDS</sub> | Data setup time to the falling edge of READY (bus slave read)                                                    |                                           | 75   |      |      | ns    |

| 58 | READY  | T <sub>RDYH</sub> | READY hold time after the rising edge of DAS (bus master)                                                        |                                           | 0    |      |      | ns    |

| 59 | READY  | T <sub>SRYH</sub> | READY hold time after the rising edge of DAS (bus slave)                                                         | $T_{SCT} = 100 ns$                        | 0    |      | 35   | ns    |

| 60 | READY  | T <sub>RSH</sub>  | READ hold time after rhe rising edge of DAS (bus slave)                                                          |                                           | 0    |      |      | ns    |

| 61 | READ   | T <sub>SRS</sub>  | READ setup time after rhe rising edge of DAS (bus slave)                                                         |                                           | 0    |      |      | ns    |

| 62 | READY  | T <sub>RDYD</sub> | Delay from falling edge of DAS to falling edge of READY (bus slave)                                              | T <sub>SCT</sub> = 100ns                  |      | 200  |      | ns    |

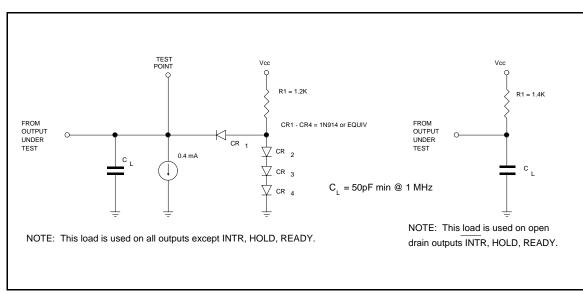

Figure 5A: TTL Output Load Diagram.

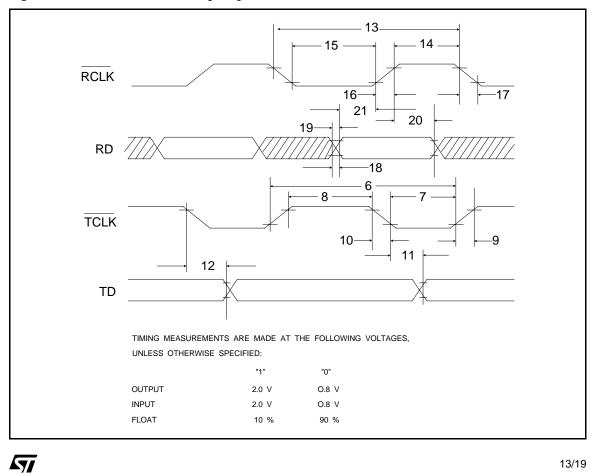

Figure 6: MK5027 Serial Link Timing Diagram

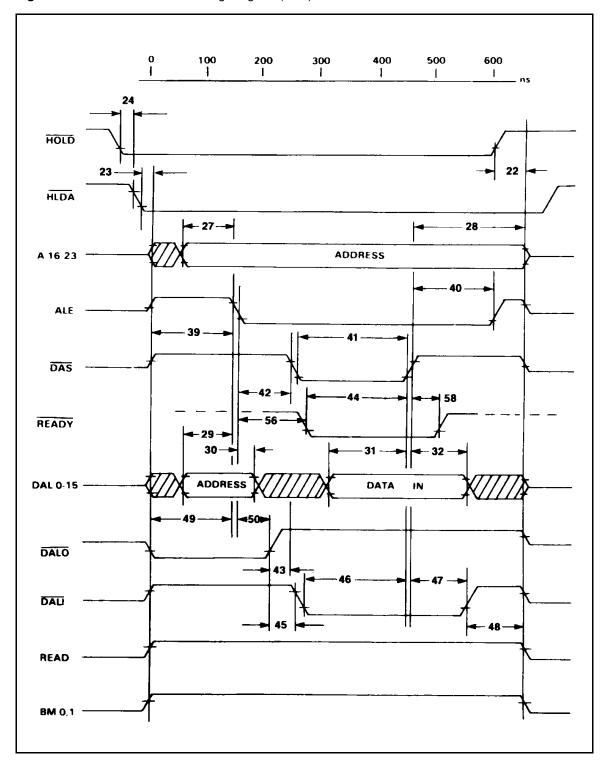

Figure 7: MK5027 Bus Master Timing Diagram (read).

Note: The Bus Master cycle time will increase from a minimum of 600ns in 100ns steps until the slave device return READY.

57

14/19

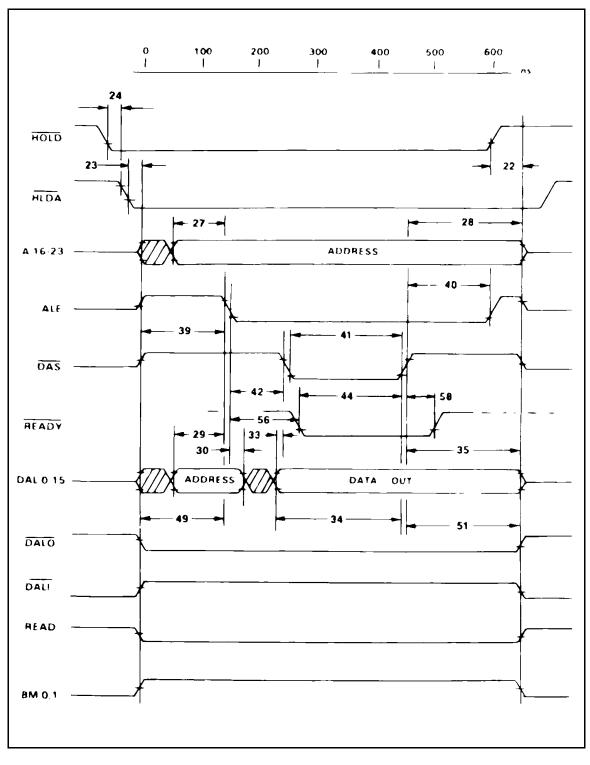

Figure 8: MK5027 Bus Master Timing Diagram (write).

Note: The Bus Master cycle time will increase from a minimum of 600ns in 100ns steps until the slave device return READY.

| 57 |

|----|

|----|

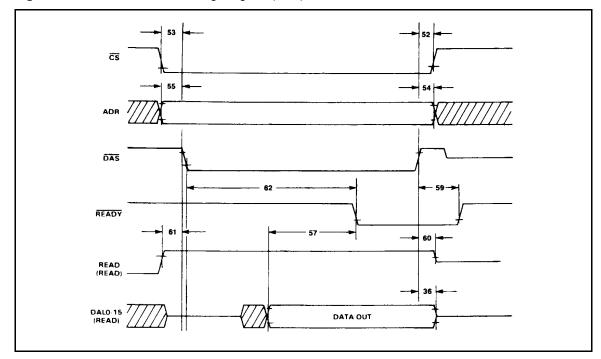

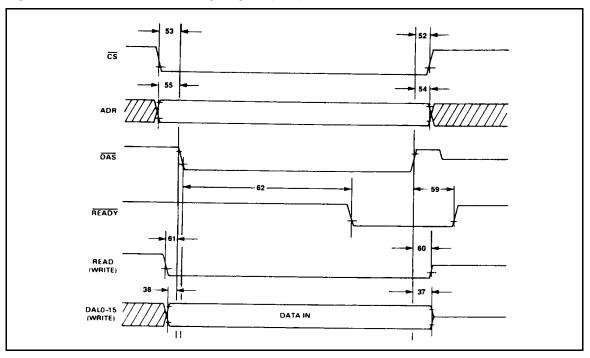

Figure 9: MK5027 Bus Slave Timing Diagram (read)

Figure 10: MK5027 Bus Slave Timing Diagram (write)

16/19

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners

© 2003 STMicroelectronics - All rights reserved

STMicroelectronics GROUP OF COMPANIES

Australia – Belgium - Brazil - Canada - China – Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States www.st.com