(240-Channel Common Driver with Internal LCD Timing Circuit)

# HITACHI

Preliminary

## Description

The HD66523 is a common driver for liquid crystal dot-matrix graphic display system. This device incorporates a 240 liquid crystal driver and an oscillator, and generates timing signals (line scanning signals and frame synchronizing signals) required for the liquid crystal display. It features a new LCD driving technique for better quality of display and low power dissipation. Combined with the HD66522, a 160-channel column driver with an internal RAM, the HD66523 is optimal for use in displays for portable information tools.

#### Features

- LCD timing generator: 1/200, 1/240 duty cycle timing are generated internally.

- Number of LCD drivers: 240

- Power supply voltage: 2.4V to 3.6V

- High voltage LCD drive circuit: ±20V

- LCD driving technique: Multi-line addressing for low power consumption.

- Programmable vertical retrace period: zero to 192 lines

- Low power consumption

- Internal display off function

- On-chip oscillator combined with external resistor and capacitor.

- Package: TCP

# **Pin Description**

| Classi-<br>fication | Symbol             | Pin Name             | I/O             | Number<br>of pins | Functions                                                                                                                                                                                                                                                                                                                                         |

|---------------------|--------------------|----------------------|-----------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power<br>supply     | V <sub>cc</sub>    | V <sub>cc</sub>      | Power supply    | 2                 | V <sub>cc</sub> –GND: logic power supply                                                                                                                                                                                                                                                                                                          |

|                     | GND                | GND                  | Power supply    | 2                 | -                                                                                                                                                                                                                                                                                                                                                 |

|                     | VLCD1,<br>VLCD2    | VLCD                 | Power supply    | 2                 | Power supply for LCD driving circuit                                                                                                                                                                                                                                                                                                              |

|                     | $V_{ee1}, V_{ee2}$ | $V_{ee}$             | Power<br>supply | 2                 | _                                                                                                                                                                                                                                                                                                                                                 |

|                     | VRH1, VRH2         | VRH                  | _               | 2                 | LCD drive level power supply                                                                                                                                                                                                                                                                                                                      |

|                     | VM1, VM2           | VM                   | _               | 2                 | _                                                                                                                                                                                                                                                                                                                                                 |

|                     | VRL1, VRL2         | VRL                  | _               | 2                 | _                                                                                                                                                                                                                                                                                                                                                 |

| Control signals     | M/S                | Master/<br>Slave     | I               | 1                 | Select master or slave mode.                                                                                                                                                                                                                                                                                                                      |

|                     | DUTY               | Duty                 | I               | 1                 | Selects the display duty cycle.<br>Low level: 1/200 display duty ratio<br>High level: 1/240 display duty ratio                                                                                                                                                                                                                                    |

|                     | BP4 to BP0         | Blanking<br>period   | I               | 5                 | Set vertical retrace period                                                                                                                                                                                                                                                                                                                       |

|                     | DOC                | Display off control  | I/O             | 1                 | Control the display-off function.                                                                                                                                                                                                                                                                                                                 |

|                     | DISPOFF            | Display off          | I               | 1                 | Turn off the LCD.<br>During display off, all LCD driver output VM<br>level                                                                                                                                                                                                                                                                        |

|                     | SHL                | Shift left           | I               | 1                 | Pin SHL switches the shift direction of the scanning direction.                                                                                                                                                                                                                                                                                   |

|                     | RESET              | Reset                | 1               | 1                 | Reset the LSI internally.                                                                                                                                                                                                                                                                                                                         |

|                     | CR, C, R           | Oscillator           |                 | 3                 | Oscillator with external resistor and<br>capacitor                                                                                                                                                                                                                                                                                                |

|                     | TEST1, TEST0       | Test                 | I               | 2                 | Test pins, must be connected to GND.                                                                                                                                                                                                                                                                                                              |

| LCD<br>timing       | CL1                | Clock 1              | I/O             | 1                 | The bidirectional shift register shifts data at<br>the falling edge of CL1.<br>During master mode, this pin outputs a data<br>transfer clock with a two times larger cycle<br>than the internal oscillator (or the cycle of<br>the external clock) with a duty of 50%.<br>During slave mode, this pin inputs the<br>external data transfer clock. |

|                     | FLM                | First line<br>marker | I/O             | 1                 | During master mode, pin FLM outputs the<br>first line marker signal.<br>During slave mode, this pin inputs the<br>external data first line marker signal.                                                                                                                                                                                         |

|                     | FX1, FX0           | Scanning function    | I/O             | 2                 | Output scanning function signals during master mode. Input scanning function signals during slave mode.                                                                                                                                                                                                                                           |

|                     | BLANK              | Blank                | 0               | 1                 | This pin shows vertical retrace period.                                                                                                                                                                                                                                                                                                           |

| LCD drive<br>output | X1 to X240         | X1 to X240           | 0               | 240               | Select one from among three levels, VRH, VM and VRL.                                                                                                                                                                                                                                                                                              |

## Table 1M/S Signal Status

| M/S | Mode   | LCD Timing Generator      | Status of CL1, FLM and $\overline{\text{DOC}}$ |

|-----|--------|---------------------------|------------------------------------------------|

| Н   | Master | 1/200 or 1/240 duty cycle | Output                                         |

| L   | Slave  | Stops                     | Input                                          |

## Table 2Retrace period

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                               | BP4 | BP3 | BP2 | BP1 | BP0 | Horizontal Retrace Period<br>Number of lines |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|----------------------------------------------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                               | 0   | 0   | 0   | 0   | 0   | 0                                            |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                               | D   | 0   | 0   | 0   | 1   | 6                                            |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                               | 0   | 0   | 0   | 1   | 0   | 12                                           |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                               | 0   | 0   | 0   | 1   | 1   | 18                                           |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                               | 0   | 0   | 1   | 0   | 0   | 24                                           |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                               | 0   | 0   | 1   | 0   | 1   | 30                                           |

| 10004810015410106010116611007211017811108411190000960001020011020011440111260111381001150101116210111621101174111011101174                                                                                                                                          | D   | 0   | 1   | 1   | 0   | 36                                           |

| 10015410106010116611007211017811108411119000009600011020010108001114401011260111138100115010111621011162110117411011741101180                                                                                                                                       | 0   | 0   | 1   | 1   | 1   | 42                                           |

| 10106010116611007211017811108411119000009600011020011114001111401011200101132011115010111621011162110117411011741110180                                                                                                                                             | D   | 1   | 0   | 0   | 0   | 48                                           |

| 1011661100721101781110841111900000960001102001010800111140101120010113201111381001150101162110117411011741110180                                                                                                                                                    | C   | 1   | 0   | 0   | 1   | 54                                           |

| 110072110178111084111190000096000110200101080011114001112001011200111138100115010111621011162110117411101                                                                                                                                                           | D   | 1   | 0   | 1   | 0   | 60                                           |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                               | 0   | 1   | 0   | 1   | 1   | 66                                           |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                               | 0   | 1   | 1   | 0   | 0   | 72                                           |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                               | 0   | 1   | 1   | 0   | 1   | 78                                           |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                               | 0   | 1   | 1   | 1   | 0   | 84                                           |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                               | 0   | 1   | 1   | 1   | 1   | 90                                           |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                               | 1   | 0   | 0   | 0   | 0   | 96                                           |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                               | 1   | 0   | 0   | 0   | 1   | 102                                          |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                               | 1   | 0   | 0   | 1   | 0   | 108                                          |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                               | 1   | 0   | 0   | 1   | 1   | 114                                          |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                               | 1   | 0   | 1   | 0   | 0   | 120                                          |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                               | 1   | 0   | 1   | 0   | 1   | 126                                          |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                               | 1   | 0   | 1   | 1   | 0   | 132                                          |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                               | 1   | 0   | 1   | 1   | 1   | 138                                          |

| 1         0         1         0         156           1         0         1         1         162           1         1         0         0         168           1         1         0         1         174           1         1         1         0         180 | 1   | 1   | 0   | 0   | 0   | 145                                          |

| 1         0         1         1         162           1         1         0         0         168           1         1         0         1         174           1         1         1         0         180                                                       | 1   | 1   | 0   | 0   | 1   | 150                                          |

| 1         1         0         0         168           1         1         0         1         174           1         1         1         0         180                                                                                                             | 1   | 1   | 0   | 1   | 0   | 156                                          |

| 1         1         0         1         174           1         1         1         0         180                                                                                                                                                                   | 1   | 1   | 0   | 1   | 1   | 162                                          |

| 1 1 1 0 180                                                                                                                                                                                                                                                         | 1   | 1   | 1   | 0   | 0   | 168                                          |

|                                                                                                                                                                                                                                                                     | 1   | 1   | 1   | 0   | 1   | 174                                          |

| 1 1 1 1 186                                                                                                                                                                                                                                                         | 1   | 1   | 1   | 1   | 0   | 180                                          |

|                                                                                                                                                                                                                                                                     | 1   | 1   | 1   | 1   | 1   | 186                                          |

| Table 5 | Shift Direction |                       |  |

|---------|-----------------|-----------------------|--|

| SHL     | DUTY            | Shift Direction       |  |

| Н       | Н               | $X240 \rightarrow X1$ |  |

|         | L               | $X200 \rightarrow X1$ |  |

| L       | Н               | $X1 \rightarrow X240$ |  |

|         | L               | $X1 \rightarrow X200$ |  |

#### Table 3Shift Direction

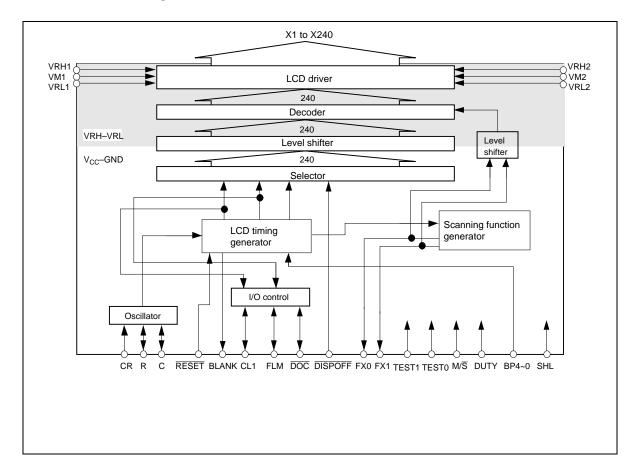

#### **Internal Block Diagram**

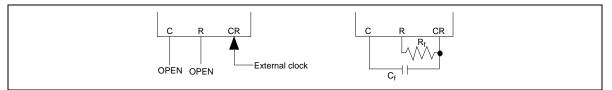

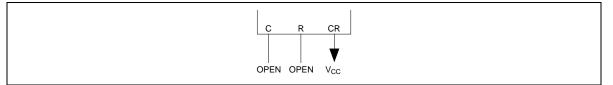

- 1. CR Oscillator: The CR oscillator generates the HD66523 operation clock. During master mode, since the operation clock is needed, connect oscillation resistor  $R_r$  with oscillation capacitor  $C_r$ . When the external clock is used. Input external clock to pin CR and open pins C and R (Figure 1). When using the HD66523 during slave mode, the operation clock will not be needed; therefore, connect pin CR to  $V_{cc}$  and open pins C and R (Figure 2).

- 2. Liquid Crystal Timing Generator: The liquid crystal timing generator creates various signals for the LCD. During master mode ( $M/\overline{S} = V_{cc}$ ), the generator operates the HD66523's internal circuitry as a common internal driver using the generated LCD signals. In addition, signals CL1, FLM and  $\overline{DOC}$  created by this generator can synchronously display data on a liquid crystal display by inputting them into the RAM-provided segment driver HD66522 used together with HD66523. During slave mode ( $M/\overline{S} = GND$ ), this generator stops; the slave HD66523 operates based on signals CL1,  $\overline{DOC}$  and FLM generated by the master HD66523.

Figure 1 Oscillator Connection in Master Mode

Figure 2 Oscillator Connection in Slave Mode

- **3.** Scanning Function Generator: During master mode, this circuit generates the scanning function signals. During slave mode, this circuit stops working and FX1 and FX0 must be supplied from master HD66523.

- 4. Selector: The selector generates signals which select two lines of LCD driver.

- 5. Decoder: Outputs data according to scanning function signals and data.

- 6. LCD driver: Outputs one of three levels according to outputs from decoder.

#### **Internal Function Description**

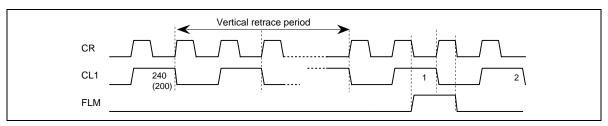

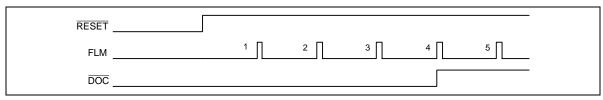

1. Generation of Signals CL1 and FLM: Signal CL1 shifts the scanning signal of the common driver. It is a 50% duty-ratio clock that changes level synchronously with the rising edge of oscillator clock CR.

FLM is a clock signal that goes high once every frame. One frame consists of display lines, 240 lines if DUTY is high and 200 lines if DUTY is low, and vertical retrace period which is set with BP4 to BP0.

2. Auto Display-off Control: This functions prevents incorrect display after reset release. The display is turned off four frames following after reset release. In addition, the display off control signal shown in Figure 4 is output by pin DOC. This pin is connected to pin DISPOFF of the HD66522.

Figure 3 Generation of Signals CL1 and FLM

Figure 4 Automatic Display-off Control Function

#### **Application Examples**

#### **Outline of HD66523 System Configuration**

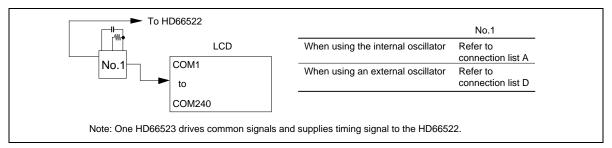

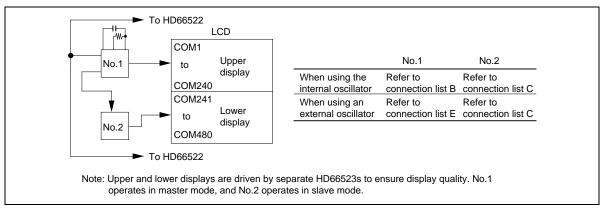

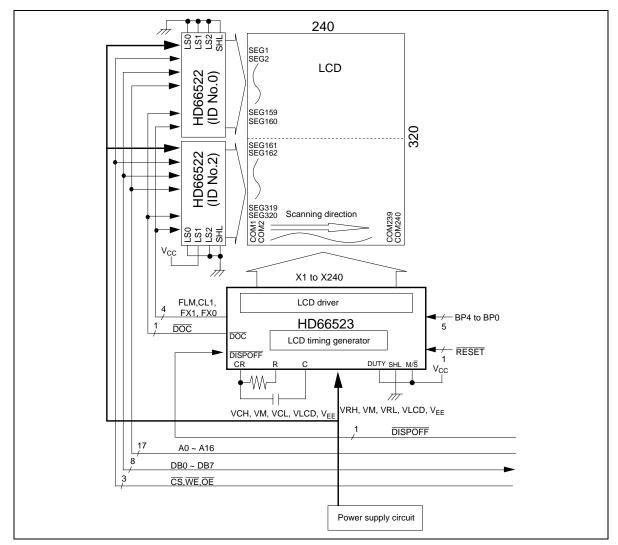

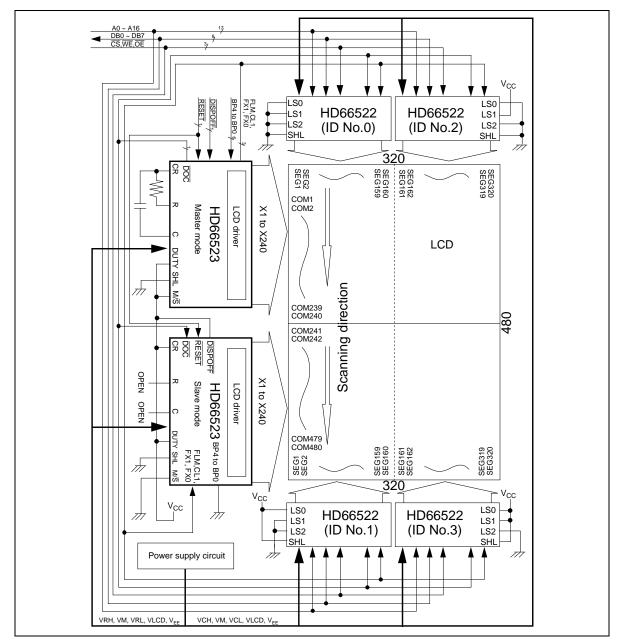

The HD66523 system configuration is outlined in Figure 5 and 6. Refer to the connection list (Table 4) for connection details.

- When a signal HD66523 is used to configure a small display (Figure 5)

- When two HD66523s are used to configure a large display (Figure 6)

Figure 5 System Configuration When Using a Single HD66523

Figure 6 System Configuration When Using a Two HD66523

#### Table 4 HD66523 Connection List

|                       | 0 -                                              | 0 -                                              | 480<br>241                                       | 0 +                                              | 0   <del>-</del>                                 |                                                                                                                                                      |

|-----------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                     | COM24                                            | COM24                                            | o COM                                            | COM24                                            | COM24                                            |                                                                                                                                                      |

| SHL X1 to X240        | COM1 to COM240<br>COM240 to COM1                 | COM1 to COM240<br>COM240 to COM1                 | COM241 to COM480<br>COM480 to COM241             | COM1 to COM240<br>COM240 to COM1                 | COM1 to COM240<br>COM240 to COM1                 |                                                                                                                                                      |

| Ļ                     |                                                  |                                                  |                                                  |                                                  |                                                  |                                                                                                                                                      |

| ę                     | 4 FX0                                            | FXO                                              | 4 FX0                                            | I FX0                                            | 4 FX0<br>2,                                      |                                                                                                                                                      |

| FX1 and FX0           | To FX1 and FX0 H<br>of HD66522                   | To FX1 and FX0<br>of HD66522,<br>HD66523         | To FX1 and FX0<br>of HD66523                     | To FX1 and FX0 H<br>of HD66522                   | To FX1 and FX0 H<br>of HD66522,<br>HD66523 L     |                                                                                                                                                      |

|                       |                                                  | tho ∞                                            |                                                  |                                                  |                                                  |                                                                                                                                                      |

| DOC                   | To DISPOFF<br>of HD66522                         | To DISPOFF<br>of HD66522<br>To DOC<br>of HD66523 | From FLM From DOC<br>of HD66523 of HD66523       | To DISPOFF<br>of HD66522                         | To DISPOFF<br>of HD66522<br>To DOC of<br>HD66523 |                                                                                                                                                      |

| ELM                   | To FLM of<br>HD66522                             | To FLM of<br>HD66522,<br>HD66523                 |                                                  | To FLM of<br>HD66522                             | To FLM of<br>HD66522,<br>HD66523                 |                                                                                                                                                      |

| CL1                   | To CL1 of<br>HD66522                             | To CL1 of<br>HD66522,<br>HD66523                 | From CL1<br>of HD66523                           | To CL1 of<br>HD66522                             | To CL1 of<br>HD66522,<br>HD66523                 |                                                                                                                                                      |

| υ                     | Ϋ́                                               | υ                                                | I                                                | I                                                | I                                                |                                                                                                                                                      |

| ٣                     | Ŗ                                                | ۲.<br>۲                                          | I                                                | I                                                | I                                                |                                                                                                                                                      |

| κ.                    |                                                  | u_ u_                                            |                                                  | External<br>Clock                                | External<br>Clock                                |                                                                                                                                                      |

| DISPOFF<br>CR         | oller $C_{f}$                                    | oller <sub>Cf</sub>                              | т                                                | oller                                            | ller                                             |                                                                                                                                                      |

| DISP                  | From<br>controller                               | From<br>controller                               | т                                                | From<br>controller                               | From<br>controller                               |                                                                                                                                                      |

| RESET                 | From MPU<br>or external<br>reset circuit         |                                                                                                                                                      |

| BP0                   | e number<br>for retrace                          | e number<br>for retrace                          | e number<br>for retrace                          | number<br>for retrace                            | or retrace                                       |                                                                                                                                                      |

| M/S DUTY BP4 to B     | Sets the number<br>of lines for retrac<br>period | H = V <sub>cc</sub> (Fixed)<br>L = GND (Fixed)<br>"" means "peen"<br>R <sub>f</sub> : Oscillation resistor<br>C <sub>f</sub> : Oscillarion capacitor |

| DUTY                  | т                                                | т                                                | т                                                | т                                                | т                                                | (Fixed)<br>(Fixed)<br>ans "opt<br>lation re<br>lation α                                                                                              |

| r i                   | т                                                | т                                                | -                                                | т                                                | т                                                | H = V <sub>CC</sub> (Fixed)<br>L = GND (Fixed)<br>"" means "open"<br>R; Oscillation resis<br>C <sub>f</sub> : Oscillarion capa                       |

| Connection<br>Example | ٩                                                | а                                                | ပ                                                | ۵                                                | ш                                                | Z de<br>s:<br>Z de<br>S de<br>S de<br>S de<br>S de<br>S de<br>S de<br>S de<br>S                                                                      |

1110

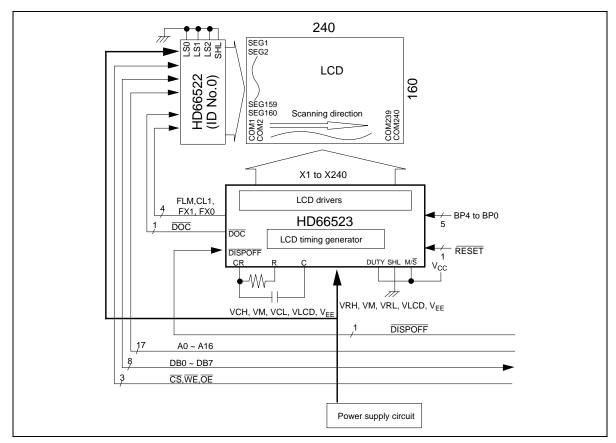

### **Example of System Configuration (1)**

Figure 7 shows system configuration for a 240 \* 160 dots LCD panel using segment driver HD66522 with internal bit-mapped RAM. All required functions can be prepared for liquid crystal display with just two LSIs except for liquid crystal display power supply circuit functions.

Figure 7 System Configuration (1)

## **Example of System Configuration (2)**

Figure 8 shows a system configuration for a 240 \* 320 dots LCD panel using segment driver HD66522 with internal bit-mapped RAM.

Figure 8 System Configuration (2)

### **Example of System Configuration (3)**

Figure 9 shows a system configuration for a 320 \* 480 dots LCD panel using segment driver HD66522 with internal bit-mapped RAM.

Figure 9 System Configuration (3)

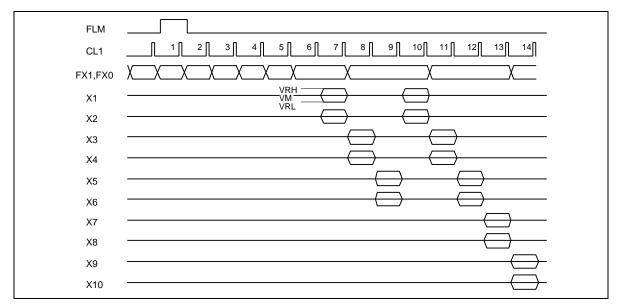

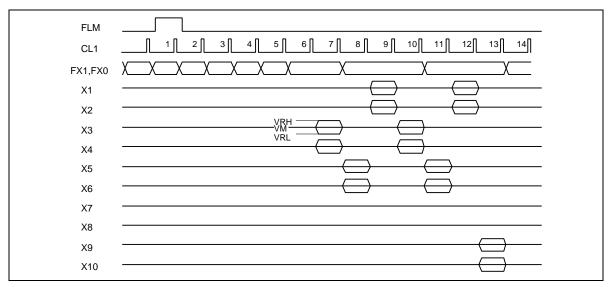

#### **LCD Drive Output**

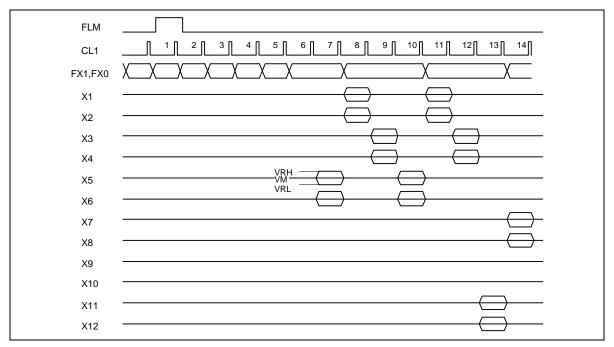

HD66523 outputs one of three levels, VRH, VM and VRL. VM is unselected level, VRH is high select level and VRL is low select level. Either VRH or VRL level is selected depending on the number of flames and lines. Output timings are showed in Figure 10 to 12.

Figure 10 LCD Drive Output Timing at 3n + 1's frame (n = 1, 2, 3, )

Figure 11 LCD Drive Output Timing at 3n + 2's frame (n = 1, 2, 3, )

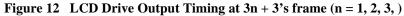

## **Power Supply Circuit**

The example of power circuit is shown in Figure 13. When you want to change contrast, both levels, VRH and VRL must be changed.

Figure 13 Example of Power Supply Circuit

## **Absolute Maximum Ratings**

| Symbol          | Rating                                                                                 | Unit                                                                                                                                                                                                                                                     | Note                                                                                                                                                                                                                                                                                                                  |

|-----------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>cc</sub> | –0.3 to + 7.0                                                                          | V                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                     |

| VRH             | -0.3 to +25.0                                                                          | V                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                       |

| VRL             | -20.0 to +0.3                                                                          | V                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                       |

| VT1             | –0.3 to V $_{\rm cc}$ +0.3                                                             | V                                                                                                                                                                                                                                                        | 1, 2                                                                                                                                                                                                                                                                                                                  |

| VT2             | $V_{\text{\tiny EE}}$ – 0.3 to VLCD + 0.3                                              | V                                                                                                                                                                                                                                                        | 1, 3                                                                                                                                                                                                                                                                                                                  |

| $T_{opr}$       | –20 to + 75                                                                            | °C                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                       |

| $T_{stg}$       | -40 to + 125                                                                           | °C                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                       |

|                 | Vcc           VRH           VRL           VT1           VT2           T <sub>opr</sub> | V <sub>cc</sub> -0.3 to + 7.0           VRH         -0.3 to +25.0           VRL         -20.0 to +0.3           VT1         -0.3 to V <sub>cc</sub> +0.3           VT2         V <sub>EE</sub> - 0.3 to VLCD + 0.3           T <sub>opr</sub> -20 to +75 | V <sub>cc</sub> -0.3 to + 7.0         V           VRH         -0.3 to +25.0         V           VRL         -20.0 to +0.3         V           VT1         -0.3 to V <sub>cc</sub> +0.3         V           VT2         V <sub>EE</sub> - 0.3 to VLCD + 0.3         V           T <sub>opr</sub> -20 to +75         °C |

Notes: 1. The reference point is GND (0V)

2. Applies to pins M/S, DUTY, BP4 to BP0, DOC, DISPOFF, SHL, RESET, CR, CL1, FLM, FX0 to FX1, and TEST1 to TEST0.

3. Applies to pins VM1 and VM2.

Supply the same voltage to pairs VRH1 and VRH2, VM1 and VM2, VRL1 and VRL2.

4. If the LSI is used beyond its absolute maximum rating, it may be permanently damaged. It should always be used within the limits of its electrical characteristics in order to prevent malfunction or unreliability.

#### **Electrical Characteristics**

DC Characteristics ( $V_{cc} = 2.4$  to 3.6V, GND = 0V, VLCD = 18 to 23V,  $V_{EE} = -12$  to -17V, Ta = -20 to  $+75^{\circ}$ C)

| ltem                         | Symbol           | Applicable<br>Pins                    | min.                | typ. | max.                | Unit | Measurement<br>Condition                                                                                                                                                                                                                    | Note<br>s |

|------------------------------|------------------|---------------------------------------|---------------------|------|---------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Input high level voltage     | $V_{\rm IH1}$    |                                       | $0.8 \times V_{cc}$ | —    | V <sub>cc</sub>     | V    |                                                                                                                                                                                                                                             | 1         |

| Input low level voltage      | $V_{IL1}$        |                                       | 0                   | _    | $0.2 \times V_{cc}$ | V    |                                                                                                                                                                                                                                             | 1         |

| Output high level voltage    | V <sub>OH</sub>  |                                       | $0.9 \times V_{cc}$ | _    | _                   | V    | Ι <sub>οн</sub> = -50 μΑ                                                                                                                                                                                                                    | 2         |

| Output low level voltage     | V <sub>ol</sub>  |                                       | _                   | _    | $0.1 \times V_{cc}$ | V    | Ι <sub>οL</sub> = 50 μΑ                                                                                                                                                                                                                     | 2         |

| Input leakage current (1)    | I <sub>IL1</sub> |                                       | -2.5                | _    | 2.5                 | μA   | $VIN = V_{cc}$ to GND                                                                                                                                                                                                                       | 1         |

| Input leakage<br>current (2) | I <sub>IL2</sub> | VRH1, VRH2,<br>VM1, VM2<br>VRL1, VRL2 | -25                 | _    | 25                  | μA   | VIN = VLCD to $V_{EE}$                                                                                                                                                                                                                      | 1         |

| Vi-Vj ON<br>resistance       | R <sub>on</sub>  | X1 to X240                            | _                   | 1.0  | 2.0                 | kΩ   | Ι <sub>οN</sub> = 100μΑ                                                                                                                                                                                                                     | 3         |

| Current consumption (1)      | I <sub>MS</sub>  |                                       | _                   |      | T.B.D.              | μA   | Master mode<br>1/240 duty cycle,<br>$C_r = 100 pF$<br>$R_r = 180 k\Omega$<br>$V_{cc} = 3.0 V$                                                                                                                                               | 4         |

| Current<br>consumption (2)   | I <sub>sl</sub>  |                                       |                     | _    | T.B.D.              | μA   | Slave mode<br>1/240 duty cycle,<br>$f_{CL} = 16.8 \text{ kHz},$<br>$V_{CC} = 3.0 \text{ V}$                                                                                                                                                 | 4         |

| Current<br>consumption (3)   | I <sub>LCD</sub> |                                       | _                   | —    | T.B.D.              | μΑ   | $\begin{array}{l} \text{Master mode} \\ 1/240 \text{ duty cycle,} \\ \text{C}_{r} = 100\text{pF} \\ \text{R}_{r} = 180\text{k}\Omega \\ \text{V}_{cc} = 3.0\text{V} \\ \text{VLCD} = 23\text{V} \\ \text{V}_{EE} = -17\text{V} \end{array}$ | 4         |

Notes: 1. Applied to input pins M/S, DUTY, BP4 to BP0, DISPOFF, SHL, RESET, TEST1, TEST0 and CR, and I/O pins, DOC, CL1 and FLM during input state.

2. Applied to output pins, FX1 and FX0, and I/O pins, DOC, CL1 and FLM, during output stagte.

3 Indicates the resistance between on pin from X1 to X240 and another pin from the V pins, VRH1/VRH2, VM1/VM2 and VRL1/VRL2, when load current is applied to the X pin; defined under the following conditions:

VRH = +23V, VRL = -17V

VM = 1/2 \* (VRH-VRL)

Input and Output currents are excluded. When a CMOS input is floating, excess current flows from the power supply to the input circuit. To avoid this, ViH and ViL must be held to V<sub>cc</sub> and GND levels, respectively.

| Item                        | Symbol            | min. | typ. | max. | Unit. | Measurement<br>Condition                     | Notes |

|-----------------------------|-------------------|------|------|------|-------|----------------------------------------------|-------|

| Operating<br>frequency (1)  | f <sub>opr1</sub> | 10   | —    | 200  | kHz   | Master mode<br>(External clock<br>operation) | 1     |

| Operating<br>frequency (2)  | f <sub>opr2</sub> | 5    | —    | 100  | kHz   | Slave mode<br>frequency of CL1               | 2     |

| Oscillation<br>frequency    | f <sub>osc</sub>  | 30   | 36   | 42   | kHz   | $C_f = 100 pF$<br>$R_f = 180 k\Omega$        |       |

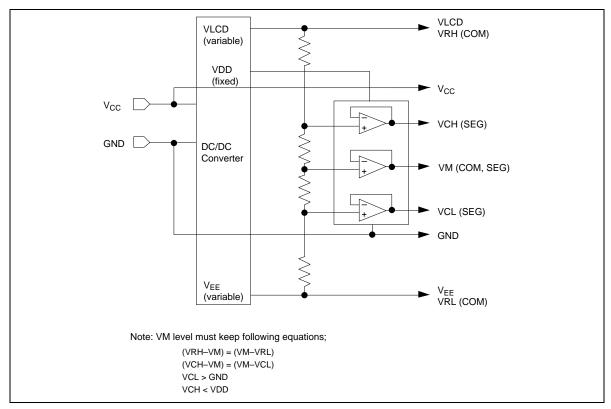

| External clock duty         | Duty              | 45   | 50   | 55   | %     | Master mode                                  | 3     |

| External clock rising time  | t,                |      | —    | 100  | ns    | Master mode                                  | 3     |

| External clock falling time | t <sub>f</sub>    | _    | _    | 100  | ns    | Master mode                                  | 3     |

Notes: 1. External clock is supplied to CR pin during master mode, and C and R pins must be left open.

2. Applies to the clock which is supplied to CL1 during slave mode. CR must be connected to GND, and C and R pins must be left open.

3. Applies to the external clock which is supplied to CR during a master mode.

Figure 14 External Clock

| AC Characteristic | $(V_{cc} = 2.4)$ | to 3.6V, GN | ND = 0V, Ta = | -20 to 75°C) |

|-------------------|------------------|-------------|---------------|--------------|

|-------------------|------------------|-------------|---------------|--------------|

| No. | Item                 | Symbol            | Applicable Pins | min. | max. | Units | Notes |

|-----|----------------------|-------------------|-----------------|------|------|-------|-------|

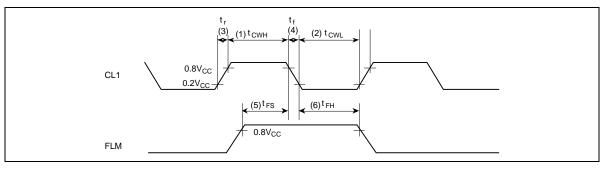

| (1) | CL1 high-level width | t <sub>cwH</sub>  | CL1             | 1.0  | _    | μs    | 1     |

| (2) | CL1 low-level width  | t <sub>cwL</sub>  | CL1             | 1.0  | _    | μs    | 1     |

| (3) | CL1 rise time        | t <sub>r</sub>    | CL1             | _    | 100  | ns    | 1     |

| (4) | CL1 fall time        | t,                | CL1             | _    | 100  | ns    | 1     |

| (5) | FLM setup time       | t <sub>FS</sub>   | FLM, CL1        | 2.0  | _    | μs    | 1     |

| (6) | FLM hold time        | t <sub>FH</sub>   | FLM, CL1        | 1.0  |      | μs    | 1     |

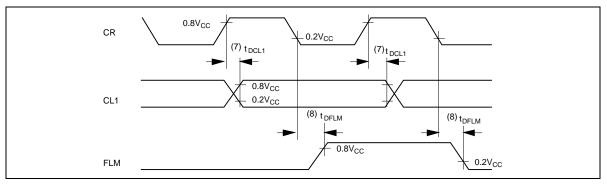

| (7) | CL1 delay time       | t <sub>cL1</sub>  | CL1             | 1.0  | _    | μs    | 2     |

| (8) | FLM delay time       | t <sub>dflm</sub> | FLM             | 1.0  | _    | μs    | 2     |

Notes: 1. Applies during slave mode

2. Applies during master mode

Figure 15 Slave Mode Timing

Figure 16 Master Mode Timing