# SONY

# **CXA3201AN**

# **RX Gain Control Amplifier**

#### Description

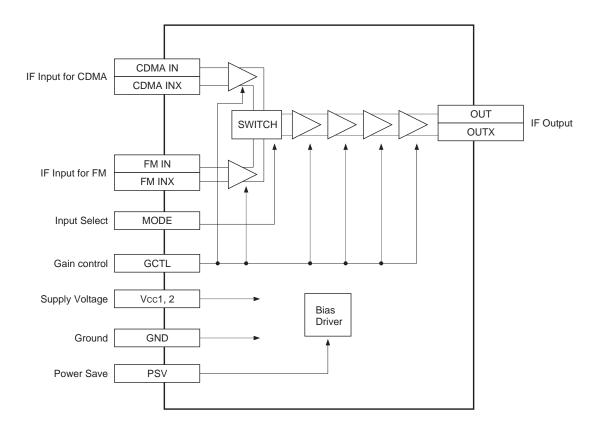

CXA3201AN is an RX gain control amplifier suitable for CDMA cellular/PCS phone.

#### **Features**

- · Wide gain control range

- Linear gain slope

- Wideband operation (50MHz to 300MHz)

- Very small package (16 Pin SSOP)

- · Low voltage operation

- Two input ports

- Power save function included

#### **Absolute Maximum Ratings**

| <ul> <li>Supply voltage</li> </ul>        | Vcc  | 6              | V     |

|-------------------------------------------|------|----------------|-------|

| <ul> <li>Operating temperature</li> </ul> | Topr | -55 to +125    | °C    |

| <ul> <li>Storage temperature</li> </ul>   | Tstg | -65 to +150    | °C    |

| • Allowable Power dissipation             | PD   | 330            | mW    |

| <ul> <li>Supply voltage range</li> </ul>  |      | -0.3 to 6      | V     |

| <ul> <li>Logic input voltage</li> </ul>   | _    | 0.3 to Vcc + 0 | ).3 V |

| <ul> <li>Signal input voltage</li> </ul>  | _    | 0.3 to Vcc + 0 | ).3 V |

| • Differential signal input voltage       | )    | 0 to 2.5       | V     |

# **Operating Condition**

Supply voltage Vcc 2.7 to 3.8 V

# **Applications**

CDMA cellular/PCS phone

#### Structure

Bipolar silicon monolithic IC

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

# **Block Diagram**

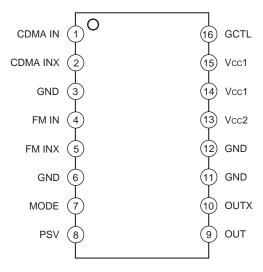

# **Pin Configuration**

# **Pin Description**

| Pin<br>No.         | Symbol   | Pin voltage<br>TYP (V) | Equivalent circuit | Description                                                 |  |

|--------------------|----------|------------------------|--------------------|-------------------------------------------------------------|--|

| 1                  | CDMA IN  | 1.15                   | Vcc1<br>2k ₹ 2k    | Differential input pins for received                        |  |

| 2                  | CDMA INX | 1.15                   | 2 GND              | CDMA IF signal.                                             |  |

| 3<br>6<br>11<br>12 | GND      | 0                      |                    | Ground.                                                     |  |

| 4                  | FM IN    | 1.15                   | Vcc1<br>2k  ≥ 2k   | Differential input pins for received                        |  |

| 5                  | FM INX   | 1.15                   | 5 GND              | FM IF signal.                                               |  |

| 7                  | MODE     | _                      | 7 WCC1 GND         | Input select pin.<br>CDMA IN for High FM IN for Low.        |  |

| 8                  | PSV      | _                      | 8 Vcc1 GND         | Power save function pin.<br>High: Active<br>Low: Power save |  |

| Pin<br>No. | Symbol | Pin voltage<br>TYP (V) | Equivalent circuit Description   |                                                       |

|------------|--------|------------------------|----------------------------------|-------------------------------------------------------|

| 9          | OUT    | _                      | 460 \$ 460<br>9 W 12.3k 12.3k    | Differential output pins for received CDMA IF signal. |

| 10         | OUTX   | _                      | GND                              | Open collector output.                                |

| 13         | Vcc2   | 3.0                    |                                  | Positive power supply for output stage.               |

| 14<br>15   | Vcc1   | 3.0                    |                                  | Positive power supply.                                |

| 16         | GCTL   |                        | 200 Vcc1  8k 8k  8k  6k  6k  6ND | Gain control pin.                                     |

# **Electrical Characteristics**

# **DC Characteristics**

$(Vcc = 3.0V, Ta = 27^{\circ}C)$

| Parameter             | Symbol | Conditions                            | Min. | Тур. | Max. | Unit |

|-----------------------|--------|---------------------------------------|------|------|------|------|

| Current consumption 1 | lcc1   | Vpsv = 3.0V, Vgctl = 1.5V, Pin 13, 14 | 7    | 10.2 | 15   | mA   |

| Current consumption 2 | lcc2   | Vpsv = 0 V, Vgctl = 1.5V, Pin 13, 14  | 10   | 27   | 50   |      |

| Input current pin 7H  | ImodeH | Vmode = 3.0V                          |      |      | 1    |      |

| Input current pin 7L  | ImodeL | Vmode = 0.5V                          | -1   |      |      |      |

| Input current pin 8H  | IpsvH  | Vpsv = 3.0V                           |      |      | 1    | μΑ   |

| Input current pin 8L  | lpsvL  | Vpsv = 0 V                            | -15  |      |      |      |

| Input current pin 16H | IgctlH | Vgctl = 3.0V                          |      |      | 1    |      |

| Input current pin 16L | IgctlL | Vgctl = 0.5V                          | -1   |      |      |      |

| MODE high voltage     | VmH    | Pin 7                                 | 2.5  |      |      |      |

| MODE low voltage      | VmL    | Pin 7                                 |      |      | 0.5  | v    |

| PSV high voltage      | VpsH   | Pin 8                                 | 2.5  |      |      | V    |

| PSV low voltage       | VpsL   | Pin 8                                 |      |      | 0.5  |      |

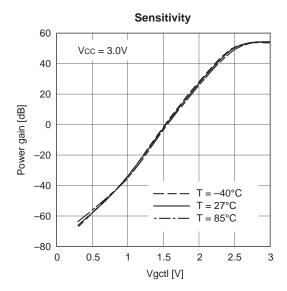

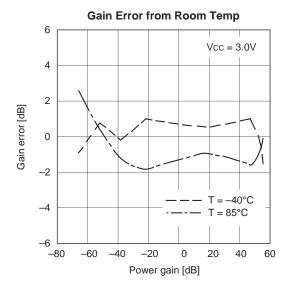

# **AC Characteristics**

$(Vcc = 3.0V, Ta = 27^{\circ}C)$

| Parameter                             | Symbol         | Conditions                                                                            | Min. | Тур. | Max. | Unit |

|---------------------------------------|----------------|---------------------------------------------------------------------------------------|------|------|------|------|

| Operating frequency range             | Fr             |                                                                                       | 50   |      | 300  | MHz  |

| Gain CDMA2.4                          | Gсрма2.4       | Vmode = "H", f = 210.38MHz, Vgctl = 2.4V                                              | 42   | 46   | 50   |      |

| Gain CDMA1.5                          | Gсрма1.5       | Vmode = "H", Vgctl = 1.5V                                                             | -7   | -3   | 1    | dB   |

| Gain CDMA0.6                          | Gсрма0.6       | Vmode = "H", Vgctl = 0.6V                                                             | -59  | -55  | -51  |      |

| CDMA Gain slope                       | GCLIN          | Vmode = "H", Gain CDMA at Vgctl = 2.0V<br>- Gain CDMA at Vgctl = 1.0V                 | 58   | 61   | 64   | dB/V |

| Gain FM2.4                            | Gгм2.4         | Vmode = "L", f = 85.38MHz, Vgctl = 2.4V                                               | 42   | 46   | 50   |      |

| Gain FM1.5                            | Gғм1.5         | Vmode = "L", Vgctl = 1.5V                                                             | -7   | -3   | 1    | dB   |

| Gain FM0.6                            | <b>G</b> Fм0.6 | Vmode = "L", Vgctl = 0.6V                                                             | -59  | -55  | -51  |      |

| FM Gain slope                         | GFMLIN         | Vmode = "L", Gain FM at Vgctl = 2.0V<br>- Gain FM at Vgctl = 1.0V                     | 58   | 61   | 64   | dB/V |

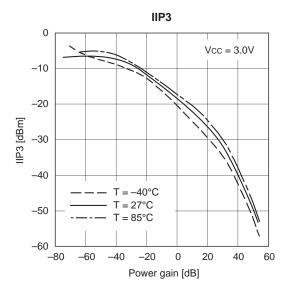

| Input level 3rd order intercept point | IIP3           | Vmode = "H", Gcdma = 40dB*1<br>f1 = 209.38MHz, f2 = 211.38MHz<br>Measure of 210.38MHz | -42  | -38  |      | dBm  |

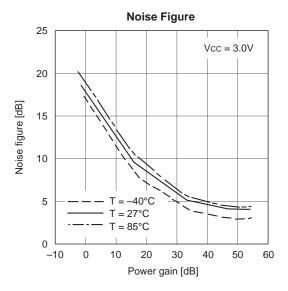

| Noise Figure                          | NF             | Vmode = "H", Gcdma = 40dB*1<br>Measure of 210.38MHz                                   |      | 5    | 8    | dB   |

<sup>\*1</sup> Adjust GCTL voltage, and set the overall gain to 40dB.

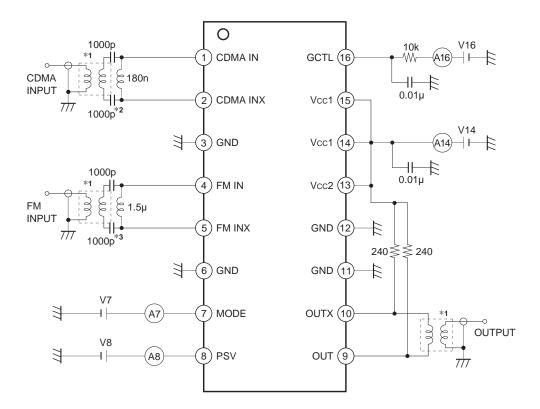

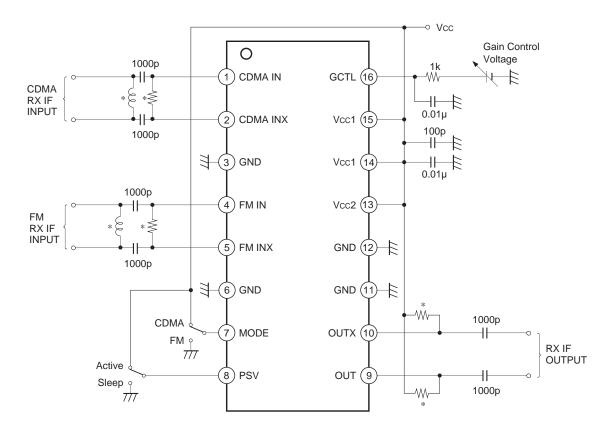

#### **Measurement Circuit**

<sup>\*1</sup> TOKO, Inc. B5FL 616DS-1135

<sup>\*2</sup> Coilcraft, Inc. 0805HS-181TKBC

<sup>\*3</sup> Coilcraft, Inc. 1008CS-152XKBC

#### **Application Circuit**

<sup>\*</sup> Must be adjusting values to result a best impedance matching between BPF filter and this IC.

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

#### **Design Reference Values**

#### Single ended measurement

$(Vcc = 3.0V, Ta = 27^{\circ}C)$

| Item               | Symbol | Conditions                      | Тур. | Unit |

|--------------------|--------|---------------------------------|------|------|

| Input resistance   | Rin    |                                 | 1.6  | kΩ   |

| Input capacitance  | Cin    | f = 210.38MHz, Vgctl = 1.5V     |      | pF   |

| Output resistance  | Rout   | 1 = 210.36(vii 12, vgcti = 1.3v | 5.9  | kΩ   |

| Output capacitance | Cout   |                                 | 0.85 | pF   |

#### **Notes on Operation**

- 1) This IC is a wideband amplifier with wide gain control range. The decouping capacitors between GND Pin and Vcc Pin should be as close to the IC as possible.

- 2) The resistors connected to Pins 9 and 10 should be as close to the IC as possible.

- 3) This IC assumes the excellent characteristics when the differential input impedance between Pins 1 and 2, Pins 4 and 5 is  $500\Omega$ . Refer to the Measurement Circuit for the external element settings, etc.

- 4) Pay attention to handling this IC because its electrostatic discharge strength is weak.

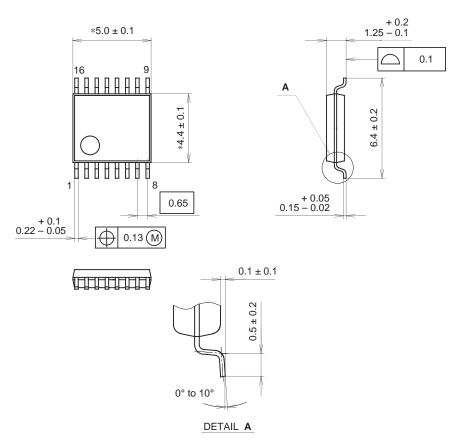

# Package Outline Unit: mm

# 16PIN SSOP (PLASTIC)

NOTE: Dimension "\*" does not include mold protrusion.

# PACKAGE STRUCTURE

| SONY CODE  | SSOP-16P-L01   |

|------------|----------------|

| EIAJ CODE  | SSOP016-P-0044 |

| JEDEC CODE |                |

| PACKAGE MATERIAL | EPOXY RESIN                   |

|------------------|-------------------------------|

| LEAD TREATMENT   | SOLDER / PALLADIUM<br>PLATING |

| LEAD MATERIAL    | 42/COPPER ALLOY               |

| PACKAGE MASS     | 0.1g                          |

NOTE: PALLADIUM PLATING

This product uses S-PdPPF (Sony Spec.-Palladium Pre-Plated Lead Frame).