### SONY®

# CX20172

## Balanced Transformer-less DUAL Amplifier for Audio Use

#### Description

The CX20172 is a bipolar IC designed as a BTL (balanced transformer-less) amplifier or a DUAL amplifier which can drive an  $8\,\Omega$  load with one dry cell (1.5 V).

#### **Features**

- Operates with one dry cell (operable if Vcc is reduced down to 0.9 V)

- Low power consumption (standard current without signals; 5 mA, 8 Ω load, BTL, Vcc=1.25V)

- Large output (BTL: 80 mW/8 Ω, EIAJ;

DUAL: 21 mW/CH, 8 Ω load, EIAJ;

Vcc = 1.5 V for both BTL and DUAL)

- The mode of either BTL amplifier or DUAL amplifier, as well as their gain setting, is selected by combining the IC with external components.

- Muting and power ON/OFF functions incorporated.

#### Structure

Bipolar silicon monolithic IC

##

#### Absolute Maximum Ratings (Ta = 25°C)

| <ul> <li>Supply voltage</li> </ul>              | Vcc  | 4.5           | V  |

|-------------------------------------------------|------|---------------|----|

| <ul> <li>Operating temperature</li> </ul>       | Topr | -20  to  +75  | °C |

| <ul> <li>Storage temperature</li> </ul>         | Tstg | -55  to  +150 | °C |

| <ul> <li>Allowable power dissipation</li> </ul> | PD   | 560           | mW |

#### **Recommended Operating Conditions**

Supply voltage

Vcc

0.9 to

2.2

V

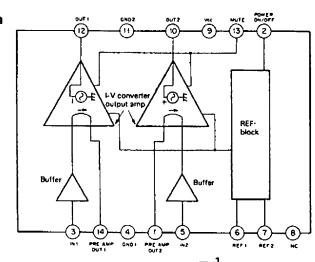

#### **Block Diagram**

60517-TO

### Pin Description

(Ta = 25°C, Supply voltage: 1.25 V)

| No. | Symbol        | Description                                                                                                                                                                                                                           | Standard pin<br>voltage (V) |

|-----|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 1   | Pre Amp out 2 | Pin to be connected with a load resistor in the preceding-stage buffer amplifier of CH2. See the Electrical Test Circuit application circuit of BTL mode, and DUAL mode.                                                              | 0.7                         |

| 2   | Power ON/OFF  | ON/OFF switching pin for the whole of the IC.  H: (power supply) IC ON L: (ground) IC OFF  (standard internal equivalent circuit)                                                                                                     | -                           |

| 3   | IN1           | Input pin for CH1. This pin is connected to the ground via a coupling capacitor, the same one as used for the input pin, when the pin is not used as an input pin in the BTL mode. Standard input resistance: $10  \mathrm{k} \Omega$ | _                           |

| 4   | GND1          | Grounding mainly for the preceding stage                                                                                                                                                                                              | _                           |

| 5   | IN2           | Input pin for CH2. This pin is connected to the ground via a coupling capacitor, the same one as used for the input pin, when the pin is not used as an input pin in the BTL mode. Standard input resistance: 10 k $\Omega$           | 0.7                         |

| 6   | REF1          | Output pin for internal reference voltage (high impedance) for phase compensation                                                                                                                                                     | 0.7                         |

| . 7 | REF2          | Output pin for internal reference voltage (low impedance)                                                                                                                                                                             | 0.7                         |

| 8   | NC            |                                                                                                                                                                                                                                       | _                           |

| 9   | Vcc           | Power supply pin                                                                                                                                                                                                                      |                             |

| 10  | OUT2          | Output pin for CH2                                                                                                                                                                                                                    | 0.55<br>(0.74 during MUTE   |

| 11  | GND2          | Grounding mainly for the output stage                                                                                                                                                                                                 | _                           |

| 12  | OUT1          | Output pin for CH1                                                                                                                                                                                                                    | 0.55<br>(0.74 during MUTE   |

| 13  | MUTE          | Switch pin to activate the MUTE operation  H: (power supply) normal operation L: (ground) MUTE  (standard internal equivalent circuit)                                                                                                | _                           |

| 14  | Pre Amp out 1 | Pin to be connected with a load resistor in the preceding stage buffer amplifier of CH1. See the Electrical Test Circuit application circuit of BTL mode, and DUAL mode.                                                              | 0.7                         |

| S         |

|-----------|

| <u>::</u> |

| <u>ত</u>  |

| ē         |

| ac        |

| ā         |

| ច         |

| Ä         |

| 걆         |

| ರ್ಷ       |

| 쁣         |

| E        | Electrical Characteristics                               | istics             |                                      |                          |                                                 |                           | Πa              | = 25°C, See the                                                              | 25°C, See the Electrical Characteristics Test Circuit)                              | teristi | ss Te | st Çi | cuit)   |

|----------|----------------------------------------------------------|--------------------|--------------------------------------|--------------------------|-------------------------------------------------|---------------------------|-----------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------|-------|-------|---------|

|          |                                                          |                    |                                      | Power                    | Power Source I/O Conditions                     | nditions                  |                 |                                                                              |                                                                                     |         |       |       |         |

| Š.       | . Test Item                                              | Symbol             | Switches to be set ON                | Supply<br>Voltage<br>Vcc | Signal Input<br>Vin                             | Signal<br>Output<br>Vot:T | Test<br>Points  | Measurement M                                                                | Measurement Method and Contents                                                     | Min.    | Тур.  | Мах.  | Unit    |

| -        | Current consumption 1                                    | l Ion              | SS                                   | 1.25(V)                  |                                                 |                           | A METER(DC)     | Current consumption in BTL with an In load and no signal input               | on in BTL with an 8                                                                 | 2.5     | 5.0   | 11.0  | ΨĄ      |

|          | <u>.</u>                                                 |                    | S7                                   |                          |                                                 |                           | Vout (DC)       | CH1 DC Output                                                                | (CH1 DC output<br>voltage) — (CH2 DC                                                | í       |       | 5     | :       |

| N        | Output offset voltage                                    | 71 QA              | S6                                   | -                        |                                                 |                           | Vour(DC)        | CH2 DC Output<br>voltage                                                     | calculated in BTL with<br>an 8 th load                                              | ا<br>ا  | >     | ₹     | È       |

| က        | Current consumption 2                                    | Loer               | S3. S4. S5                           | 2.0(V)                   |                                                 |                           | A METER(DC)     | Current consumptions in Power OFF, MUTE                                      | ns in Power OFF,                                                                    |         | 0     | 10    | /به     |

| 4        | Gain BTL 1                                               | Gerta              | SI                                   | 1.25(V)                  | Adjustment                                      | -20dBm                    | VIN, VOUT (AC)  | Gain for the output of _ 30 dBm                                              | of - 20 dBm                                                                         | 23.5    | 25.5  | 28.0  | θВ      |

| 22       | Gain BTL 2                                               | GHTL2              | 22                                   | 0.9(V)                   | -                                               | -                         |                 | Dani loi me outh                                                             |                                                                                     | 22.5    | 24.5  | 28.0  | фB      |

| ع        | ∆Gain BTL                                                | ∆Gsrt.             | Arithmetic                           | 1                        | ı                                               | ı                         | ١               | ∆GHTL = GHTLI GHTL!                                                          | 1,1                                                                                 | -       | 0.1   | 3.0   | dB      |

|          | THD BTL                                                  | Тноит              | SI                                   | 1.25(V)                  | Adjustment                                      | -10dBm                    | Vour (AC)       | THD (BTL) for the output of dBm                                              | ontput of - 10                                                                      |         | 1.5   | 2.5   | ×       |

| ∞        | EIAJ maximum output BTL                                  | Phtlmax            | S1                                   | 1.5(V)                   | <b>-</b>                                        | <b>7.010HT</b>            | Vour (AC)       | BTL output for the                                                           | BTL output for the output THD of 10%                                                | 02      | 28    | _ =   | ≱<br>E  |

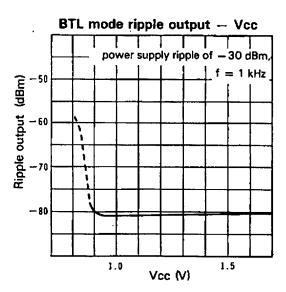

| 6        | Ripple output voluge BTL                                 | RIPBTL .           |                                      | 1.0(V)<br>+(-30dBm)      |                                                 |                           | VRIF. Vour(AC)  | Check the PTL output by overlaying the ripple voltage with I V power supply. | by overlaying the power supply.                                                     |         | - 79  | 65    | dBm     |

| 2        | Noise output voltage BTL                                 | NETL               |                                      | 2.0(V)                   |                                                 |                           | Vour (AC)       | Noise output voltage in BTL, with an<br>\( \) load and no signal input       | e in BTL with an 8<br>Input                                                         |         | - 80  | -75   | dВm     |

| =        | Output during MUTE                                       | Мвт                | S1, S4                               | 1.0(V)                   | -20dBm                                          |                           | Vour(AC)        | BTL output in the MUTE state                                                 | MUTE state                                                                          |         | •     | 100   | ₫Bm     |

|          | СНІ                                                      | Gurali             | S1, S7, S8, S9, S10, S11, S12        | 1.25(V)                  | Adjustment                                      | -264Вш                    | VIN, VOUT (AC)  | CHI input CHI autput                                                         | Gain for individual                                                                 | 0 0     | 91.0  | 0 76  | 4       |

| 2        | Cain DUAL CH2                                            | GDUAL2             | S2. S6, S8, S9, S10, S11, S12        | -                        | mb                                              | <b>→</b>                  | <b>→</b>        | CH2 input CH2 output                                                         | outputs of - 26<br>dBm. 8 Ω load                                                    |         |       | ;     | ;       |

| 13       | Channel balance                                          | ∆Gb12              | Arithmetic                           | l                        | 1                                               | ŀ                         | !               | DGD12 = GRALI - GIKALI                                                       | כאדג                                                                                | -1.5    | 0     | +1.5  | gg<br>B |

| :        | CHI                                                      | T <sub>HU</sub> pı | \$1, \$7, \$8, \$9, \$10, \$11, \$12 | 1.25(V)                  | Adjustment                                      | -16dBm                    | Vour(AC)        | CHI input CHI output                                                         | THD for individual                                                                  |         | •     |       | è.      |

| <u> </u> | THU DUAL CH2                                             | THD 02             | S2, S6, S8, S9, S10, S11, S12        | <b>→</b>                 | 1                                               | <b>-</b>                  | 1               | CH2 input CH2 output                                                         | outputs of 16<br>dBm.                                                               |         |       | :     | 2       |

| -        | EIAJ CHI                                                 | Pul MAK            | S1, S7, S8, S9, S10, S11, S12        | 1.5(V)                   | +                                               | THD10%                    | -               | CHI input CHI output                                                         | Output for the individual CH                                                        |         | <br>& |       |         |

| 3        | output<br>dUAL                                           | PDZ MAX            | S2, S6, S8, S9, S10, S11, S12        | -                        | <b>→</b>                                        | -                         |                 | CH2 input CH2 output                                                         | THD's of 10%. 8<br>Ω load                                                           |         |       |       |         |

| 2        | Cross talk -CH2                                          | Став               | S1, S6, S8, S9, S10, S11, S12        | 1.25(V)                  | Test 12<br>equivalent<br>to OSC in<br>Grand.    |                           | VIN, VINIT (AC) | Citt input Cit2 output                                                       | The output level at the CH                                                          |         |       |       | 43      |

| 3        | DUAL CH'S CH2                                            | Ствл               | S2, S7, S8, S9, S10, S11, S12        | <b>→</b>                 | Test 17<br>cquivalent<br>to OSC in<br>Girital 2 |                           | •••             | CH2 input CH1 output                                                         | opposite with the input CH                                                          |         |       |       |         |

|          | • Both signal input Vin and ripple input VRIP are I kHz. | nd ripple in       | put Vripare i kHz.                   |                          |                                                 |                           |                 | . dBm (600 Ω) 0 dB                                                           | dBm (600 Ω) 0 dBm: 774.6mVrms<br>BPF is set to 400 Hz to 30 kHz for AC measurement. | æsurem  | ent.  |       |         |

VOUT METER --- DC ---- AC 400Hz to 30kHz Fiter VOUT METER Vcc Ripple voltage (VRIP) o ss ٠٠٠٠ ميبار \$ 0 8 Jrmo 010 PRE AMP OUT 1 (14) ğ≰ 2 POWER ON/OFF PRE AMP OUT 2 REFI 9 ≹ă 722 V IN METER osc

8382383 0011193 508

Electrical Characteristics Test Circuit

#### **Description of Operation**

The CX20172 incorporates two buffer amplifiers in the preceding stage and two current input amplifiers in the succeeding stage. Selection between the BTL amplifier and DUAL amplifier is made by altering the method of attaching external components as shown in the Application Circuit.

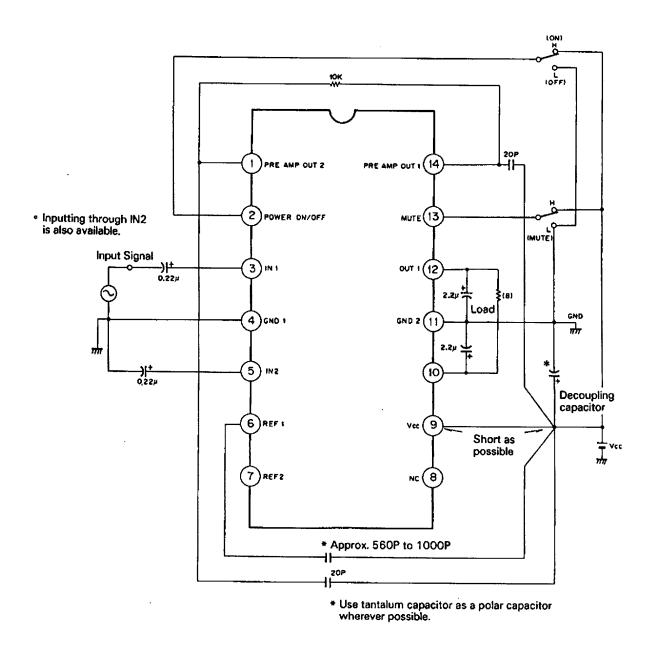

- 1. BTL mode (see the BTL mode Application Circuit)

- Items 1 to 11 in the Electrical Characteristics are the characteristics for the BTL mode.

- Input through either IN1 or IN2 results in a reverse-phase output at the output side of the input channel and in the same-phase output at the other, to enable BTL driving of the load between OUT1 and OUT2.

- Ground the unused input pins via a coupling capacitor which is the same one used for the input pin.

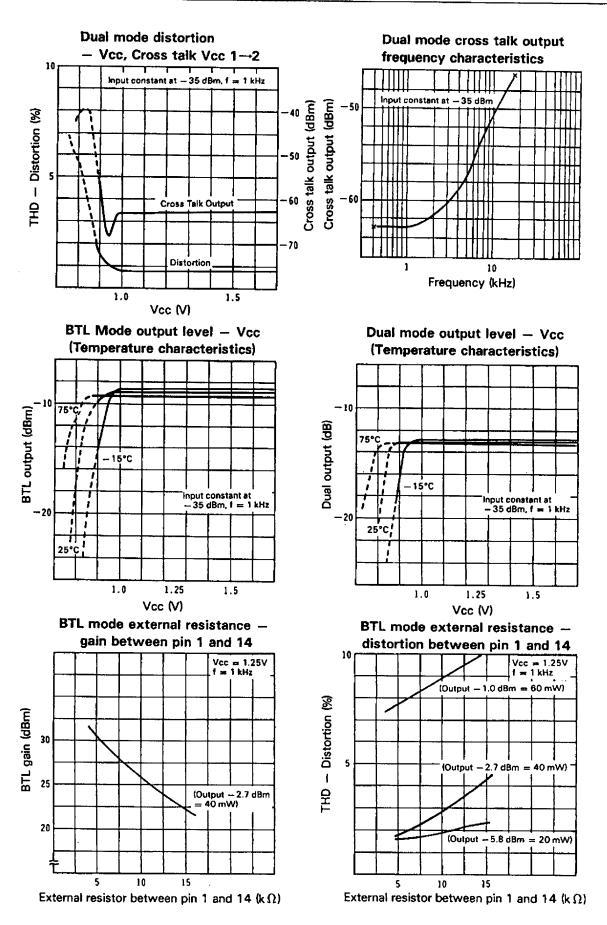

- Gain setting can be altered by changing values of external resistors connected between Pre Amplifier

out 1 and 2. Gain decreases as a resistor value between Pin 1 and Pin 14 increases. Reducing a resistor value to increase the gain results in larger output offset and current consumption. I/O characteristics, distortion factor and maximum output change according to resistor values. Specify a set value,

therefore, in view of input level, output level, distortion and power consumption.

- The value of a phase-compensation capacitor can be altered considerably according to patterns on mounting substrate.

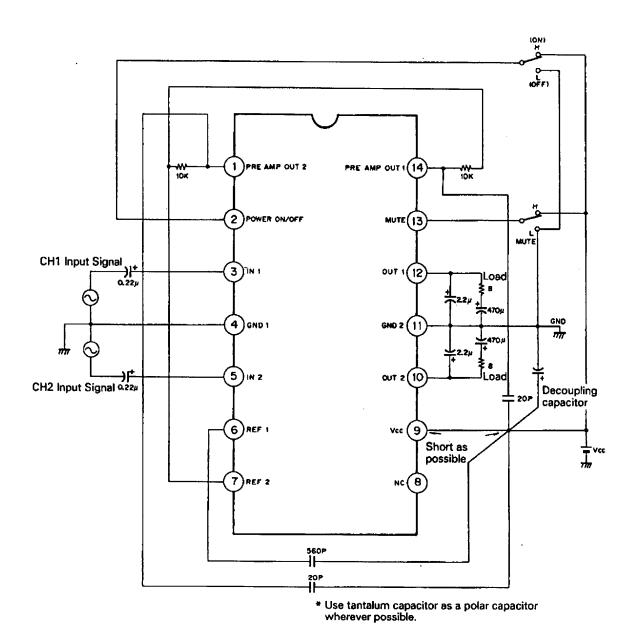

- 2. Dual mode (see the Dual mode Application Circuit)

- Items 12 to 16 in the Electrical Characteristics are the characteristics for the Dual mode.

- Simultaneous input through IN1 and IN2 results in reverse-phase outputs at both output pins to enable DUAL driving.

- Gain setting can be altered by changing values of external resistors connected between Pre Amplifier

out 1 and 2 and REF2, similarly to the BTL mode. Gain decreases as resistor value increases. I/O characteristics, distortion factor and maximum output change according to resistor values. The same consideration as in the BTL mode is, therefore, required. Current consumption has, however, less

dependency on the gain than in BTL.

- The value of a phase-compensation capacitor can be altered considerably according to patterns on mounting substrate.

- 3. Common functions

- 3.1 REF block

- Circuit block to generate reference voltage.

REF1 (Pin 6) is an output from the block (high impedance). This is reduced in its impedance through the buffer amplifier to generate REF2 (Pin 7).

- 3.2 Mute, Power ON/OFF block

- Grounding the Mute pin (Pin 13) results in the interrupt of the signal route to generate DC voltage of approx. 700 to 765 mV at both output sides of channel (CH).

- Grounding the Power ON/OFF pin (Pin 2) results in the OFF state of the REF block and the output is grounded.

#### **BTL Mode Application Circuit**

Note) Place a decoupling capacitor between Vcc and GND as close as possible to Vcc and GND2. Assuming this point as the point of power supply or grounding, place (\*)-marked components as close as possible.

Values of the decoupling capacitor can be altered according to the pattern layouts.

#### **Dual Mode Application Circuit**

Note) Notes for the above are almost same as in BTL.

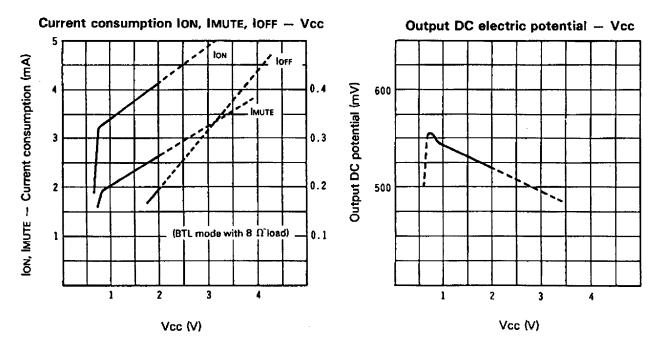

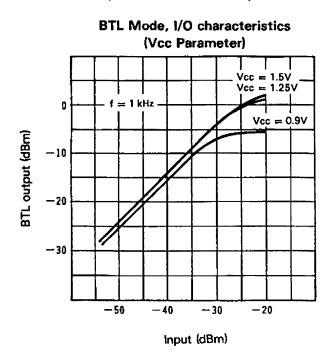

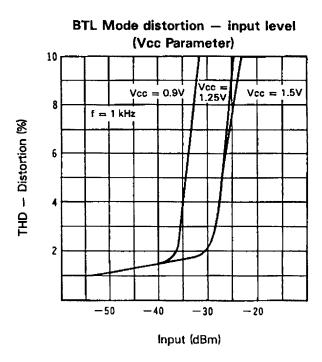

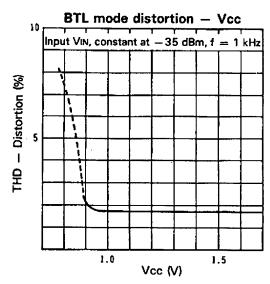

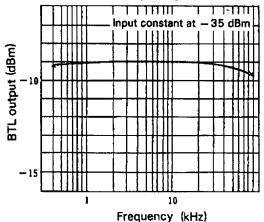

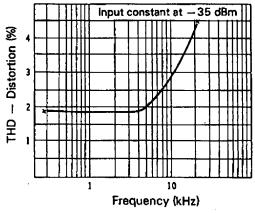

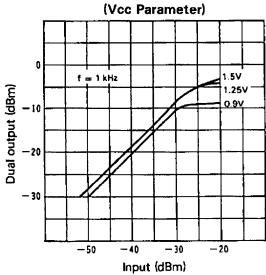

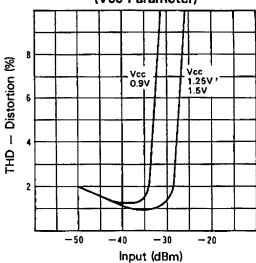

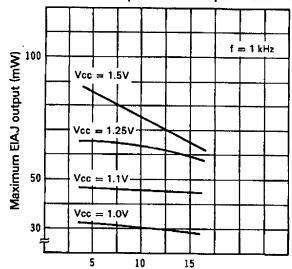

#### **Standard Characteristics**

- See "Electrical Characteristics Test Circuit" for the test circuit.

- A resistor between Pin 1 and Pin 14 to determine the gain is of 10 k $\Omega$ , unless otherwise specified.

- Measuring temperature is 25°C, unless otherwise specified.

lon and loff are measured conforming to the methods in the measurement 1 and 3. IMUTE represents the current consumption with S4 and S5 ON.

BTL mode output frequency characteristics

BTL mode distortion frequency characteristics

Dual mode I/O characteristics (Vcc Parameter)

Dual mode distortion — input level (Vcc Parameter)

# BTL mode external resistance — maximum output between pin 1 and 14

External resistor between pin 1 and 14  $(k \Omega)$