## Bt864A/Bt865A YCrCb to NTSC/PAL Digital Video Encoder

**Data Sheet**

### **Ordering Information**

| Model Number | Description                                                 | Package     |

|--------------|-------------------------------------------------------------|-------------|

| Bt864AKRF    | YCrCb to NTSC/PAL Digital Video Encoder without Macrovision | 52-Pin MQFP |

| Bt865AKRF    | YCrCb to NTSC/PAL Digital Video Encoder with Macrovision    | 52-Pin MQFP |

### **Revision History**

| Revision   | Date     | Description                                             |  |  |

|------------|----------|---------------------------------------------------------|--|--|

| А          | 08/26/97 | Initial release (document L865A)                        |  |  |

| В          | 09/26/00 | Company name change                                     |  |  |

| C 02/17/03 |          | Incorporates two Erratas: 102084A and d864er3 (100184B) |  |  |

© 2003, Conexant Systems, Inc. All Rights Reserved.

Information in this document is provided in connection with Conexant Systems, Inc. ("Conexant") products. These materials are provided by Conexant as a service to its customers and may be used for informational purposes only. Conexant assumes no responsibility for errors or omissions in these materials. Conexant may make changes to specifications and product descriptions at any time, without notice. Conexant makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Conexant's Terms and Conditions of Sale for such products, Conexant assumes no liability whatsoever.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF CONEXANT PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. CONEXANT FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. CONEXANT SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

Conexant products are not intended for use in medical, lifesaving or life sustaining applications. Conexant customers using or selling Conexant products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages resulting from such improper use or sale.

The following are trademarks of Conexant Systems, Inc.: Conexant<sup>®</sup> and the Conexant C symbol. Product names or services listed in this publication are for identification purposes only, and may be trademarks of third parties. Third-party brands and names are the property of their respective owners.

For additional disclaimer information, please consult Conexant's Legal Information posted at <a href="www.conexant.com">www.conexant.com</a> which is incorporated by reference

Reader Response: Conexant strives to produce quality documentation and welcomes your feedback. Please send comments and suggestions to conexant.tech.pubs@conexant.com. For technical questions, contact your local Conexant sales office or field applications engineer.

## Bt864A/Bt865A

# YCrCb to NTSC/PAL Digital Video Encoder Data Sheet

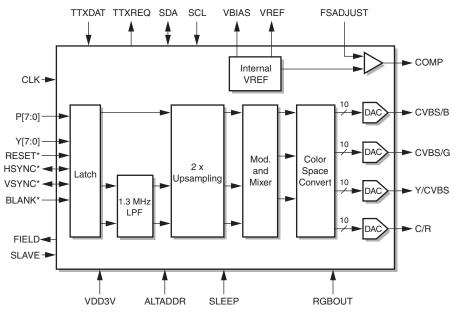

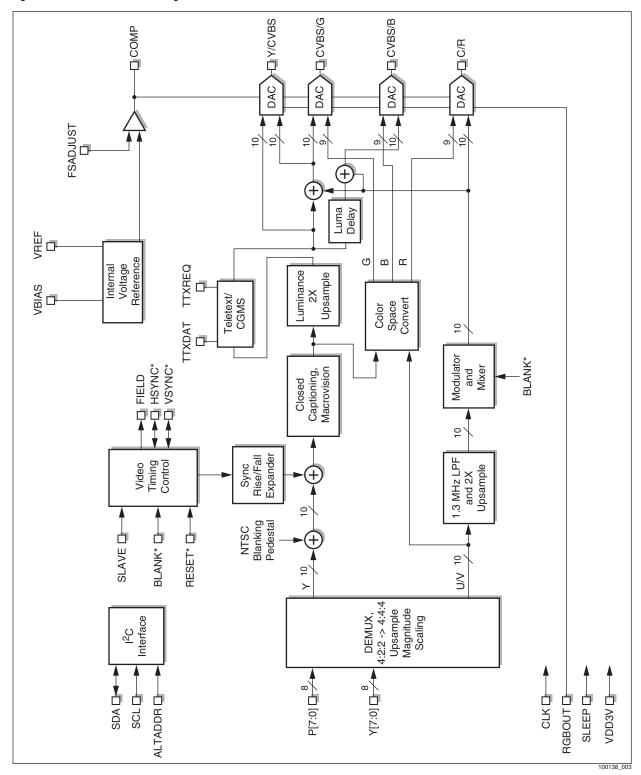

The Bt864A/Bt865A is specifically designed for video systems requiring the generation of composite, Y/C (S-video) or RGB (SCART) video signals from an 8- or 16-bit YCrCb digital video stream. Worldwide video standards are supported including NTSC-M (N. America, Taiwan, Japan), PAL-B,D,G,H,I (Europe, Asia), PAL-M (Brazil), PAL-N (Uruguay, Paraguay) and PAL-Nc (Argentina). The Bt864A and Bt865A are functionally identical, with the exception that Bt865A can output the Macrovision level 7 anticopy algorithm.

Horizontal sync (HSYNC\*) and vertical sync (VSYNC\*) may be configured as inputs (slave mode) or outputs (master mode). BLANK\* is an input and may be externally controlled. Horizontal and vertical blanking are automatically generated. The rise and fall times of sync, the burst envelope, and closed caption data are internally controlled.

Analog luminance (Y) and chrominance (C) information is available on the Y and C outputs for interfacing to S-video equipment. The composite analog video signal is output simultaneously onto two outputs. This allows one output to provide baseband composite video while the other drives an RF modulator. Analog RGB is also available to allow for support of the European SCART/PeriTV interface.

#### **Functional Block Diagram**

#### **Distinguishing Features**

- 8- or 16-bit 4:2:2 YCrCb inputs

- NTSC-M/PAL/PAL-M/PAL-N/PAL-Nc composite video outputs

- S-Video/RGB (SCART) outputs

- CCIR 601 or square pixel operation

- 2x oversampling

- ◆ 10-bit DACs

- · Master or slave video timing

- Auto mode detection function (slave mode)

- ◆ Interlaced/noninterlaced operation

- Macrovision 7 support (Bt865A only)

- Closed caption encoding

- Teletext encoding (WST system B)

- I<sup>2</sup>C Interface

- On-board voltage reference

- ◆ Power-down modes

- Programmable luma delay (singlechannel)

- ◆ 5 V or 3.3 V supply voltage

- Copy Generation Management System (CGMS)

#### **Related Products**

- ▶ Bt852

- ◆ Bt856/7

- ◆ Bt864/5

- ◆ Bt866/7

#### **Applications**

- Digital cable systems

- Satellite television setup boxes (DBS/DSS)

iii

- DVD players

- Digital VCR (DVC, DVHS)

- VideoCD players

- Portable VideoCD players

- Digital cameras

- PC add-on cards

## **Contents**

| Figui | res  | v                                            | ii |

|-------|------|----------------------------------------------|----|

| Table | es   | i                                            | Χ  |

| 1     | Circ | uit Description                              | 1  |

|       | 1.1  | Pin Descriptions                             | 1  |

|       | 1.2  | Clock TIming                                 |    |

|       | 1.3  | Pixel Input Timing                           |    |

|       |      | 1.3.1 8-bit YCrCb Input Mode                 |    |

|       |      | 1.3.2 16-bit YCrCb Input Mode                |    |

|       |      | 1.3.3 Pixel Synchronization                  |    |

|       | 1.4  | HSYNC* Timing. 1-                            |    |

|       |      | 1.4.1 Master Mode                            |    |

|       |      | 1.4.2 Slave Mode                             |    |

|       | 1.5  | Video Timing                                 |    |

|       |      | 1.5.1 Reset                                  |    |

|       |      | 1.5.2 Sync and Burst Timing                  |    |

|       |      | 1.5.3 Master Mode                            |    |

|       |      | 1.5.4 Slave Mode                             | 7  |

|       |      | 1.5.5 FIELD Output                           | 8  |

|       |      | 1.5.6 Pixel Blanking                         |    |

|       |      | 1.5.7 Burst Blanking                         |    |

|       |      | 1.5.8 Digital Processing                     |    |

|       |      | 1.5.9 Chrominance Disable                    | 8  |

|       |      | 1.5.10 Subcarrier Phasing                    | 1  |

|       |      | 1.5.11 Vertical Blanking Intervals           | 1  |

|       |      | 1.5.12 BLANK* Pin                            | 1  |

|       |      | 1.5.13 Noninterlaced Operation               | 1  |

|       | 1.6  | Power Saving Modes                           | 2  |

|       | 1.7  | Pixel Input Ranges and Colorspace Conversion | 2  |

|       |      | 1.7.1 YC Inputs (4:2:2 YCrCb)                |    |

|       |      | 1.7.2 DAC Coding                             |    |

|       | 1.8  | Closed Captioning                            | 4  |

|   | 1.9   | Teletext                                            | 1-25  |

|---|-------|-----------------------------------------------------|-------|

|   |       | 1.9.1 CCIR601 Operation (13.5 MHz pixel rate)       | 1-27  |

|   |       | 1.9.2 Square Pixel Operation (14.75 MHz pixel rate) | 1-27  |

|   |       | 1.9.3 Teletext Clock Generation                     | 1-27  |

|   |       | 1.9.4 Teletext Clock Output                         | 1-28  |

|   | 1.10  | Copy Generation Management System (CGMS) Encoding   | 1-28  |

|   | 1.11  | Anticopy Process (Bt865A Only)                      | 1-29  |

|   | 1.12  | Internal Color Bars                                 | 1-29  |

|   | 1.13  | SCART/PeriTV Support                                | 1-29  |

|   | 1.14  | I <sup>2</sup> C Interface                          | 1-29  |

|   | 1.15  | Analog Outputs                                      | 1-30  |

|   |       | 1.15.1 Luminance or CVBS (Y/CVBS) Output            | 1-30  |

|   |       | 1.15.2 Chrominance or Red (C/R) Output              | 1-30  |

|   |       | 1.15.3 Composite Video or Blue (CVBS/B) Output      | 1-30  |

|   |       | 1.15.4 Composite Video or Green (CVBS/G) Output     | 1-30  |

| 2 | Inter | nal Registers                                       | 2-1   |

| _ |       |                                                     |       |

|   | 2.1   | Essential Registers                                 |       |

|   | 2.2   | Important Registers                                 |       |

|   | 2.3   | Writing Addresses                                   |       |

|   | 2.4   | Programming Detail                                  | 2-3   |

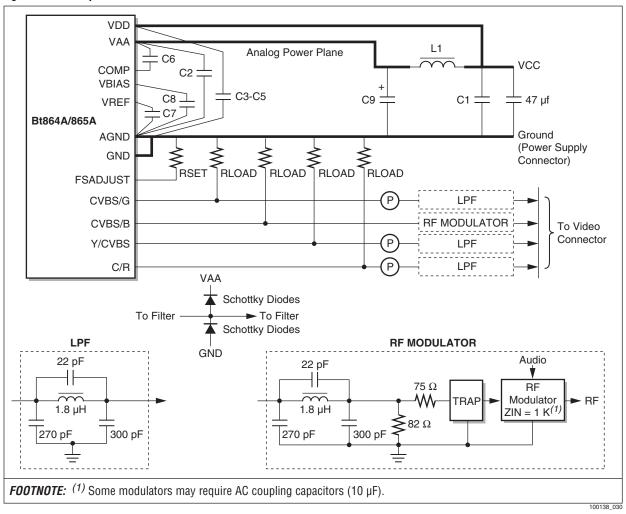

| 3 | PC B  | Board Considerations                                | 3-1   |

|   | 3.1   | Component Placement                                 | 3-1   |

|   | 3.2   | Power and Ground Planes                             | 3-1   |

|   | 3.3   | Decoupling                                          | 3-3   |

|   |       | 3.3.1 Device Decoupling                             | . 3-3 |

|   |       | 3.3.2 Power Supply Decoupling                       | . 3-3 |

|   |       | 3.3.3 COMP Decoupling                               | . 3-3 |

|   |       | 3.3.4 VREF Decoupling                               | . 3-4 |

|   |       | 3.3.5 VBIAS Decoupling                              | . 3-4 |

|   | 3.4   | Signal Interconnect                                 | 3-4   |

|   |       | 3.4.1 Digital Signal Interconnect                   | . 3-4 |

|   |       | 3.4.2 Analog Signal Interconnect                    | . 3-5 |

|   | 3.5   | Applications Information                            | 3-5   |

|   |       | 3.5.1 ESD and Latchup Considerations                |       |

|   |       | 3.5.2 Clock and Subcarrier Stability                | . 3-5 |

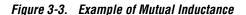

|   |       | 3.5.3 Mutual Inductance Concerns                    | . 3-6 |

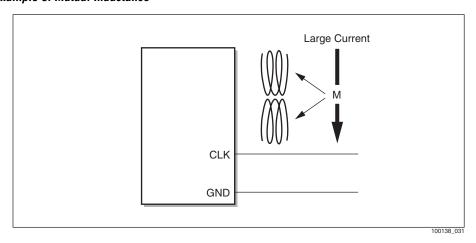

|   |       | 3.5.4 Reset Precautions                             | . 3-7 |

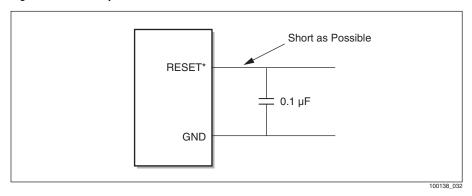

|   |       | 3.5.5 Filtering RF Modulator Connection             | . 3-7 |

|   |       | 3.5.6 Luminance Delay on CVBS/B                     |       |

|   | 3.6   | I <sup>2</sup> C Programming                        |       |

|   |       | 3.6.1 Data Transfer on the I <sup>2</sup> C Bus.    | . 3-9 |

| 4 | Para  | metric Information                                  | 4-1   |

|   | 4.1   | DC Electrical Parameters                            | 4-1   |

|   | 4.2   | AC Electrical Parameters                            |       |

|   |       |                                                     |       |

# **Figures**

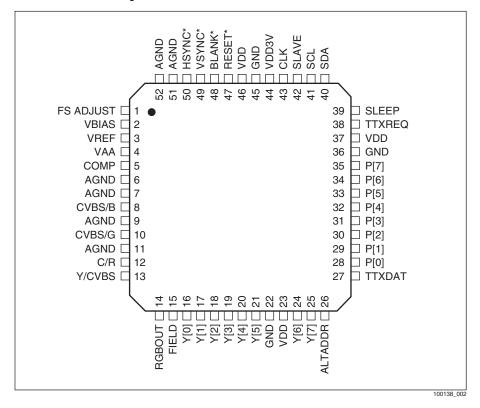

| Figure 1-1.  | Bt864A/Bt865A Pinout Diagram                                                | 1-3    |

|--------------|-----------------------------------------------------------------------------|--------|

| Figure 1-2.  | Detailed Block Diagram                                                      | 1-4    |

| Figure 1-3.  | HSYNC* Timing in Master Mode                                                | 1-7    |

| Figure 1-4.  | Interlaced 525-Line (TSC) Video Timing                                      | 1-8    |

| Figure 1-5.  | Interlaced 525-Line (PAL-M) Video Timing                                    | 1-9    |

| Figure 1-6.  | Interlaced 625-Line (PAL-B, D, G, H, I, Nc) Video Timing                    | . 1-10 |

| Figure 1-7.  | Interlaced 625-Line (PAL-B, D, G, H, I, Nc) Video Timing                    | . 1-11 |

| Figure 1-8.  | Interlaced 625-Line (PAL-N) Video Timing                                    | . 1-12 |

| Figure 1-9.  | Interlaced 625-Line (PAL-N) Video Timing                                    | . 1-13 |

| Figure 1-10. | Noninterlaced 262-Line (NTSC) Video Timing                                  | . 1-14 |

| Figure 1-11. | Noninterlaced 262-Line (PAL-M) Video Timing                                 | . 1-14 |

| Figure 1-12. | Noninterlaced 312-Line (PAL-B, D, G, H, I, N, N <sub>c</sub> ) Video Timing | . 1-14 |

| Figure 1-13. | Three-Stage Chrominance Filter                                              | . 1-19 |

| Figure 1-14. | Three-Stage Chrominance Filter (Passband)                                   | . 1-19 |

| Figure 1-15. | Luminance 2X Upsampling Filter Response                                     | . 1-20 |

| Figure 1-16. | Luminance 2X Upsampling Filter Response (Passband)                          | . 1-20 |

| Figure 1-17. | DAC Sinx/x Response                                                         | . 1-23 |

| Figure 1-18. | DAC Sinx/x Response (Passband)                                              | . 1-24 |

| Figure 1-19. | Teletext Timing for Tb864A/Bt865A Encoder                                   | . 1-26 |

| Figure 1-20. | PQ Ratio Counter                                                            | . 1-27 |

| Figure 1-21. | Typical CGMS Waveform                                                       | . 1-28 |

| Figure 1-22. | Y (Luminance) Video Output Waveform SETUPDIS = 0                            | . 1-31 |

| Figure 1-23. | Y (Luminance) Video Output Waveform SETUPDIS = 1                            | . 1-32 |

| Figure 1-24. | C (Chrominance) Video Output Waveform SETUPDIS = 0                          | . 1-33 |

| Figure 1-25. | C (Chrominance) Video Output Waveform SETUPDIS = 1                          | 1-34   |

| Figure 1-26. | CVBS (Composite) Video Output Waveform SETUPDIS = 0                         | . 1-35 |

| Figure 1-27. | CVBS (Composite) Video Output Waveform SETUPDIS = 1                         | . 1-36 |

| Figure 3-1.  | Simplified Schematic                                                        | 3-2    |

| Figure 3-2.  | Example Power Plane Layout                                                  | 3-3    |

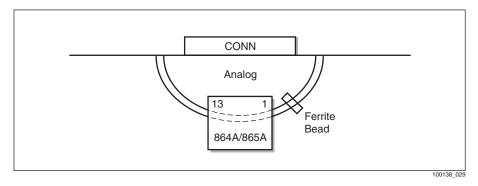

| Figure 3-3.  | Example of Mutual Inductance                                                | 3-6    |

| Figure 3-4.  | Wiring for the Reset Input Pin                                              | 3-7    |

| Figure 3-5.  | I <sup>2</sup> C Diagram                                                    | 3-9    |

| Figure 4-1.  | YCrCb Video Input and Output Timing                                         | 4-5    |

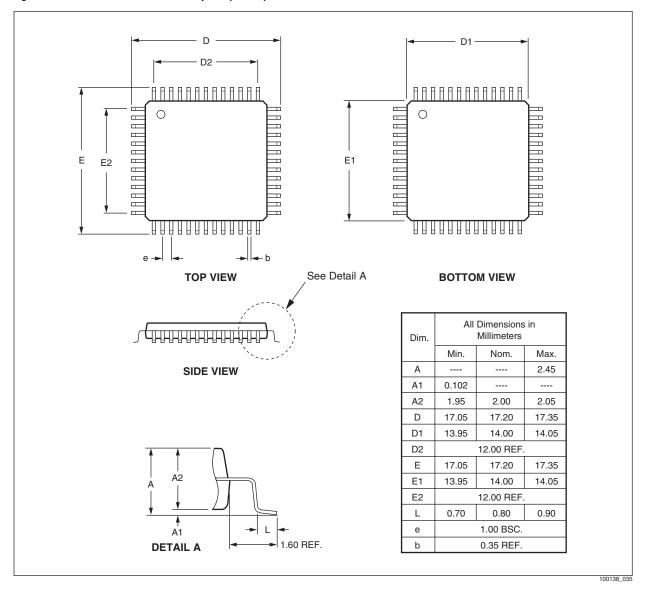

| Figure 4-2.  | 52-Pin Metric Quad Flatpack (MQFP)                                          | 4-6    |

|              |                                                                             |        |

## **Tables**

| lable 1-1.  | Pin Assignments                                                 | 1-1  |

|-------------|-----------------------------------------------------------------|------|

| Table 1-2.  | Field Resolution and Clock Rates for Various Modes of Operation | 1-15 |

| Table 1-3.  | Horizontal Counter Values for Various Video Timings             | 1-16 |

| Table 1-4.  | DAC Coding                                                      | 1-23 |

| Table 1-5.  | Legal Values to TXHS and TXHE                                   | 1-26 |

| Table 1-6.  | Teletext Clock P and Q Values                                   | 1-27 |

| Table 1-7.  | DAC Output Cross-Reference                                      | 1-30 |

| Table 1-8.  | Y (Luminance) Video Output Truth Table SETUPDIS = 0             | 1-31 |

| Table 1-9.  | Y (Luminance) Video Output Truth Table SETUPDIS = 1             | 1-32 |

| Table 1-10. | C (Chrominance) Video Output Truth Table SETUPDIS = 0           | 1-33 |

| Table 1-11. | C (Chrominance) Video Output Truth Table SETUPDIS = 1           | 1-34 |

| Table 1-12. | CVBS (Composite) Video Output Truth Table SETUPDIS = 0          | 1-35 |

| Table 1-13. | CVBS (Composite) Video Output Truth Table SETUPDIS = 1          | 1-36 |

| Table 1-14. | RGB Output Table (RGBOUT = 1)                                   | 1-37 |

| Table 2-1.  | Read-Back Bit Map                                               | 2-1  |

| Table 2-2.  | Register Bit Map                                                | 2-2  |

| Table 3-1.  | Recommended Component Values                                    | 3-2  |

| Table 4-1.  | Recommended Operating Conditions                                | 4-1  |

| Table 4-2.  | Absolute Maximum Ratings                                        | 4-1  |

| Table 4-3.  | DC Characteristics (VDD = 5 V)                                  | 4-2  |

| Table 4-4.  | AC Characteristics (VDD = 5 V, VAA = 5 V)                       |      |

## **Circuit Description**

## 1.1 Pin Descriptions

Pin names, input/output assignments, numbers, and descriptions are listed in Table 1-1. Figure 1-1 illustrates the Bt864A/Bt865A pinout diagram, and Figure 1-2 details the block diagram.

Table 1-1. Pin Assignments (1 of 2)

| Pin Name | I/O | Pin #         | Description                                                                                                                                                                                                                                                                                                                                                       |  |  |

|----------|-----|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CLK      | 1   | 43            | 2x pixel clock input (TTL compatible).                                                                                                                                                                                                                                                                                                                            |  |  |

| RESET*   | I   | 47            | Reset control input (TTL compatible). A logical zero disables and resets video timing (horizontal, vertical, subcarrier counters to the start of VSYNC of first field) and resets the I2C interface (but does not reset I2C registers). RESET* must be a logical one for normal operation.                                                                        |  |  |

| BLANK*   | I   | 48            | Composite blanking control input (TTL compatible). BLANK* is registered on the rising edge of CLK. The P[7:0] and Y[7:0] inputs are ignored while BLANK* is a logical zero.                                                                                                                                                                                       |  |  |

| VSYNC*   | 1/0 | 49            | Vertical sync input/output (TTL compatible). As an output (master mode operation), VSYNC* is output following the rising edge of CLK. As an input (slave mode operation), VSYNC* is registered on the rising edge of CLK.                                                                                                                                         |  |  |

| HSYNC*   | I/O | 50            | Horizontal sync input/output (TTL compatible). As an output (master mode operation), HSYNC* is output following the rising edge of CLK. As an input (slave mode operation), HSYNC* is registered on the rising edge of CLK.                                                                                                                                       |  |  |

| P[7:0]   | I   | 35–28         | YCrCb pixel inputs (TTL compatible) in 8-bit YCrCb mode. CrCb pixel inputs (TTL compatible) in 16-bit YCrCb mode. A higher index corresponds to a greater bit significance.                                                                                                                                                                                       |  |  |

| Y[7:0]   | I   | 25, 24, 21–16 | Y pixel inputs (TTL compatible) in 16-bit YCrCb mode. Y[7] enables internal color bars when operating in 8-bit YCrCb mode. A higher index corresponds to a greater bit significance. (1)                                                                                                                                                                          |  |  |

| TTXDAT   | ı   | 27            | Teletext bit stream input (TTL compatible). <sup>(1)</sup>                                                                                                                                                                                                                                                                                                        |  |  |

| TTXREQ   | 0   | 38            | Teletext request output (TTL compatible).                                                                                                                                                                                                                                                                                                                         |  |  |

| ALTADDR  | I   | 26            | Alternate slave address input (TTL compatible). A logical one configures the device to respond to an I2C address of 0x88; a logical zero configures the device to respond to an I2C address of 0x8A. (1)                                                                                                                                                          |  |  |

| SLAVE    | I   | 42            | Slave/master mode select input (TTL compatible). A logical one configures the device for slave video timing operation. A logical zero configures the device for master video timing operation. This pin may be connected directly to VDD or GND.                                                                                                                  |  |  |

| RGBOUT   | I   | 14            | Analog RGB control input (TTL compatible). A logical one configures the device to output analog RGB (RGBOUT mode) and one composite video output. A logical zero configures the device to generate S-video along with two composite video outputs. This pin may be connected directly to VDD or GND. The RGBOUT pin is logically ORed with the RGBO register bit. |  |  |

Table 1-1. Pin Assignments (2 of 2)

| Pin Name      | I/O | Pin #      | Description                                                                                                                                                                                                                                         |  |

|---------------|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| FIELD         | 0   | 15         | Field control output (TTL compatible). FIELD transitions after the rising edge of CLK, two clock cycles following falling VSYNC*. It is a logical zero during FIELD 1 and is a logical one during FIELD 2.                                          |  |

| SLEEP         | I   | 39         | Power-down control input (TTL compatible). A logical one configures the device for power-down mode. A logical zero configures the device for normal operation. This pin may be connected directly to VDD or GND.                                    |  |

| SDA           | 1/0 | 40         | Serial interface data input/output (TTL compatible). Data is written to and read from the device via this serial bus.                                                                                                                               |  |

| SCL           | I   | 41         | Serial interface clock input (TTL compatible). The maximum clock rate is 100 kHz.                                                                                                                                                                   |  |

| VDD3V         | I   | 44         | Input threshold adjustment. When low, indicates nominal supply voltage of 5 volts. When high, indicates nominal supply voltage of 3.3 volts.                                                                                                        |  |

| CVBS/B        | 0   | 8          | Composite video or Blue (with blanking and sync, and optionally, Macrovision encoding). Optional luma delay channel for composite video output.                                                                                                     |  |

| AGND (CVBS/B) |     | 6          | Analog ground for pin CVBS/B.                                                                                                                                                                                                                       |  |

| CVBS/G        | 0   | 10         | Composite video or Green (with blanking and sync, and optionally, Macrovision encoding).                                                                                                                                                            |  |

| AGND (CVBS/G) |     | 7          | Analog ground for pin CVBS/G.                                                                                                                                                                                                                       |  |

| C/R           | 0   | 12         | Modulated chrominance, or Red.                                                                                                                                                                                                                      |  |

| AGND (C/R)    |     | 9          | Analog ground for pin C/R.                                                                                                                                                                                                                          |  |

| Y/CVBS        | 0   | 13         | Luminance or composite video (with blanking, sync, and optionally, Macrovision encoding, and/or closed-captioning encoding).                                                                                                                        |  |

| AGND (Y/CVBS) |     | 11         | Analog ground for pin Y/CVBS.                                                                                                                                                                                                                       |  |

| FSADJUST      | I   | 1          | Full-scale adjust control pin. A resistor (RSET) connected between this pin and GND controls the full-scale output current on the analog outputs. For standard operation, use the nominal RSET values shown under Recommended Operating Conditions. |  |

| VBIAS         | 0   | 2          | DAC bias voltage. A 0.1 $\mu$ F ceramic capacitor must be used to decouple this pin to GND. The capacitor must be as close to the device as possible to keep lead lengths to an absolute minimum.                                                   |  |

| VREF          | 0   | 3          | Voltage reference pin. A 0.1 $\mu$ F ceramic capacitor must be used to decouple this pin to GND. The capacitor must be as close to the device as possible to keep lead lengths to an absolute minimum.                                              |  |

| COMP          | 0   | 5          | Compensation pin. A 0.1 $\mu$ F ceramic capacitor must be used to decouple this pin to VAA. The capacitor must be as close to the device as possible to keep lead lengths to an absolute minimum.                                                   |  |

| VAA           | -   | 4          | Analog power. Refer to PC Board Considerations section of this document.                                                                                                                                                                            |  |

| VDD           | -   | 37, 23, 46 | Digital power. Refer to the PC Board Considerations section of this document.                                                                                                                                                                       |  |

| AGND          | _   | 51, 52     | Analog ground. Refer to the PC Board Considerations section of this document.                                                                                                                                                                       |  |

| GND           | -   | 22, 36, 45 | Digital ground. Refer to the PC Board Considerations section of this document.                                                                                                                                                                      |  |

<sup>(1)</sup> Any unused inputs should not be left floating.

Figure 1-1. Bt864A/Bt865A Pinout Diagram

Figure 1-2. Detailed Block Diagram

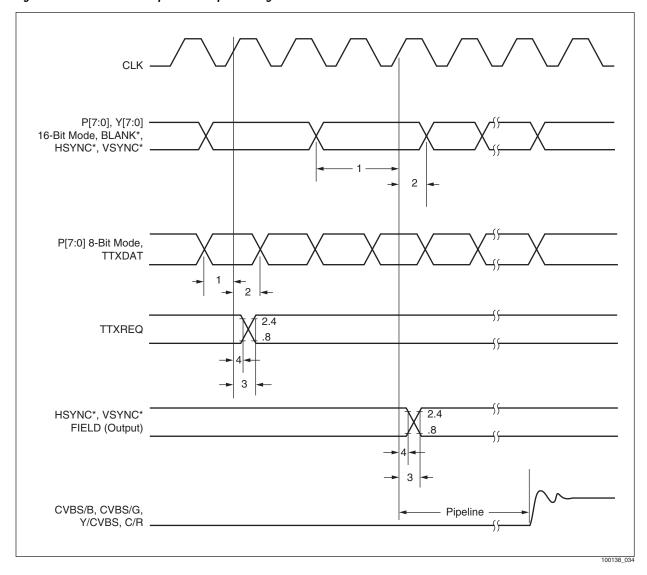

## 1.2 Clock Timing

A clock signal with a frequency twice the pixel sampling rate must be present at the CLK pin. The device generates an internal pixel CLOCK that in slave mode is synchronized to the HSYNC\* pin. This signal is used to increment the horizontal pixel and vertical line counters and to register the pixel (P[7:0], Y[7:0], TTXDAT, RESET\*, BLANK\*, SLAVE, HSYNC\*, and VSYNC\*) inputs. All setup and hold timing specifications are measured with respect to the rising edge of CLK.

## 1.3 Pixel Input Timing

### 1.3.1 8-bit YCrCb Input Mode

The 8-bit YCrCb multiplexed input mode is selected by default. Multiplexed Y, Cb, and Cr data is input through the P[7:0] inputs. By default, the input sequence for active video pixels must be Cb0, Y0, Cr0, Y1, Cb2, Y2, Cr2, Y3, etc. in accordance with CCIR656.

## 1.3.2 16-bit YCrCb Input Mode

The 16-bit mode is selected by setting the YC16 register bit. Y data is input through the Y[7:0] inputs. Multiplexed Cb and Cr data is input through the P[7:0] inputs.

### 1.3.3 Pixel Synchronization

The default input pixel sequence is such that the next clock after HSYNC\* goes low will be the start of the 4-byte Cb/Y/Cr/Y sequence in 8-bit mode, or Y/Cb sample pair in 16-bit mode. This is true for slave mode, and for master mode with the default HSYNC\* timing. This sequence can be changed by the SYNCDLY and CBSWAP bits in both master and slave modes, or by using the variable HSYNC\* timing in master mode.

The SYNCDLY bit will decrease the delay between the HSYNC\* pin and the analog output by one clock cycle. The pixel-to-analog out timing is unaffected. This makes the next pixel after the falling edge of HSYNC\* the last Y of the Cb/Y/Cr/Y sequence in 8-bit mode.

The CBSWAP bit will shift the sequence at the input such that the next sample after the falling edge of HSYNC\* will be the Cr sample of the Cb/Y/Cr/Y sequence in 8-bit mode, or the Y/Cr sample pair in 16-bit mode. The relationship between the HSYNC\* pin and the analog output is unaffected, as is the pixel-to-analog out timing.

## 1.4 HSYNC\* Timing

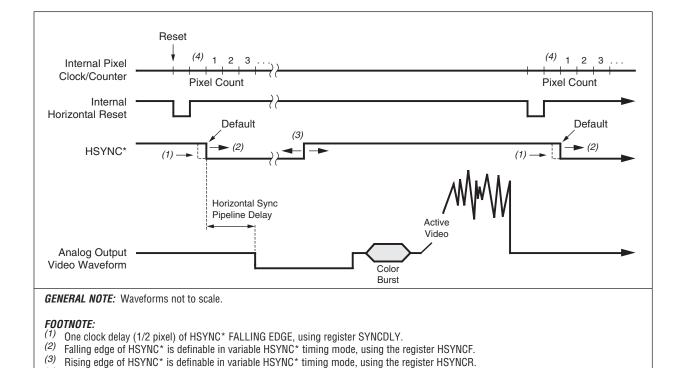

#### 1.4.1 Master Mode

There are two HSYNC\* timing modes in master mode; default mode and variable HSYNC\* timing mode. The variable HSYNC\* timing mode is enabled by setting ADJHSYNC high. This mode allows the user to specify the placement of the falling and rising edges of HSYNC\* by using the HSYNCF and HSYNCR registers, respectively. The values of registers HSYNCF and HSYNCR correspond to the pixel count of the internal pixel counter (see Figure 1-3). HSYNCF and HSYNCR cannot be zero and cannot be equal. Values must also be less than or equal to the total horizontal resolution given in Table 1-2. If the internal pixel counter resets before the rising edge occurs, the part will not automatically reset, but will wait until the pixel counter reaches the specified HSYNCR value. The placement of the analog horizontal sync pulse is fixed relative to the internal pixel counter, therefore when the rising and falling edges of HSYNC\* are moved, the pipeline delay between the HSYNC\* pulse and the analog horizontal sync pulse is altered. In this mode, the pipeline delay from HSYNC\* to analog sync out is 40-(2\*HSYNCF) if SYNCDLY = 0, and 41-(2\*HSYNCF) if SYNCDLY = 1. In the default HSYNC\* timing mode, the placement of the edges of the HSYNC\* pulse are fixed, with the exception of the one clock delay available through the register SYNCDLY. In this mode, the pipeline delay from HSYNC\* to analog sync out is 40 clocks if SYNCDLY = 0, and 41 clocks if SYNCDLY = 1. In the default mode, the delay from internal horizontal pixel counter reset to the falling edge of HSYNC\* is 2 clocks.

Figure 1-3. HSYNC\* Timing in Master Mode

100138\_00

#### 1.4.2 Slave Mode

Maximum horizontal resolution (see Table 1-2).

Slave mode does not support a variable HSYNC\* timing mode. The default pipeline delay from the HSYNC\* falling edge to analog sync out falling edge is 47 clocks if SYNCDLY = 0, and 46 clocks if SYNCDLY = 1. The default delay from the falling edge of HSYNC\* input to internal horizontal pixel counter reset is 5 clocks. In both master and slave modes, the pixel data pipeline delay is 52 clocks.

## 1.5 Video Timing

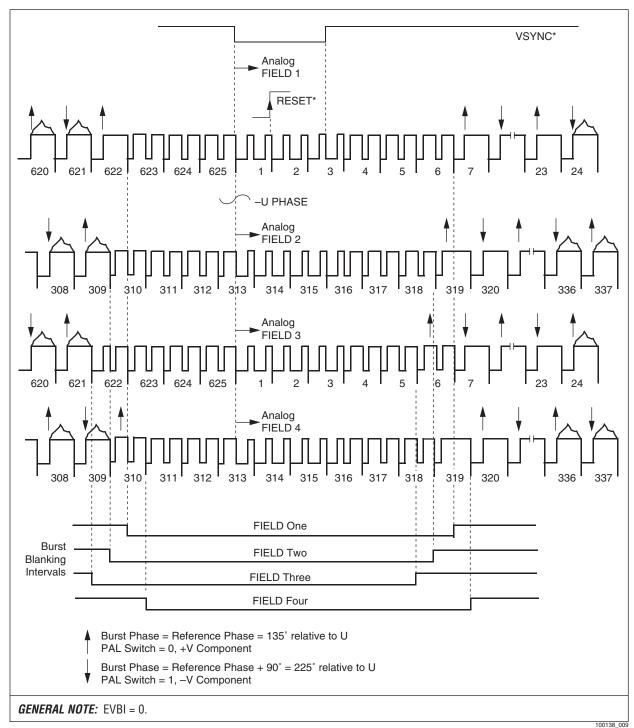

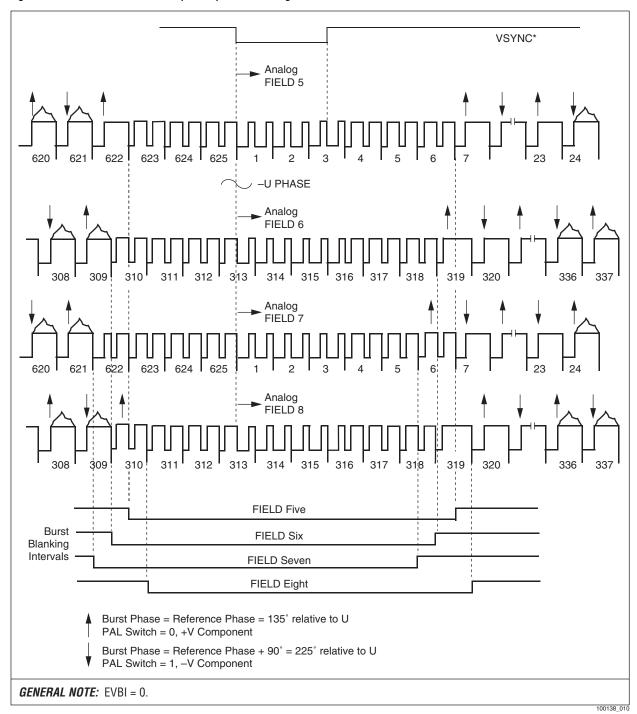

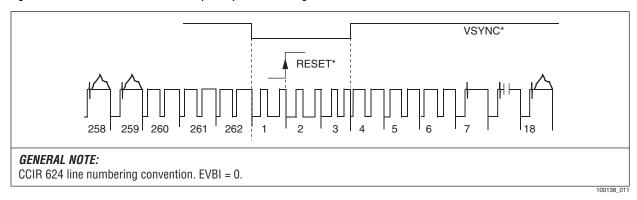

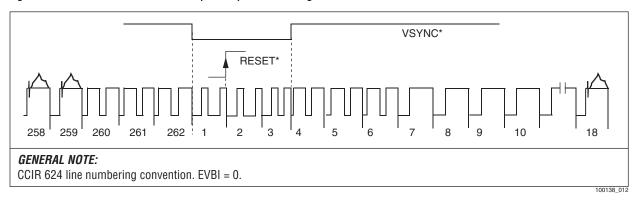

The width of the analog horizontal sync pulses and the start and end of color burst are automatically calculated and inserted for each mode according to ITU-RBT.470-3. Color burst is disabled on appropriate scan lines. Serration and equalization pulses are generated on appropriate scan lines. In addition, rise and fall times of sync, closed-caption data transitions, and the burst envelope are internally controlled. Figure 1-4 through show the timing characteristics for various Bt864A/Bt865A modes of operation.

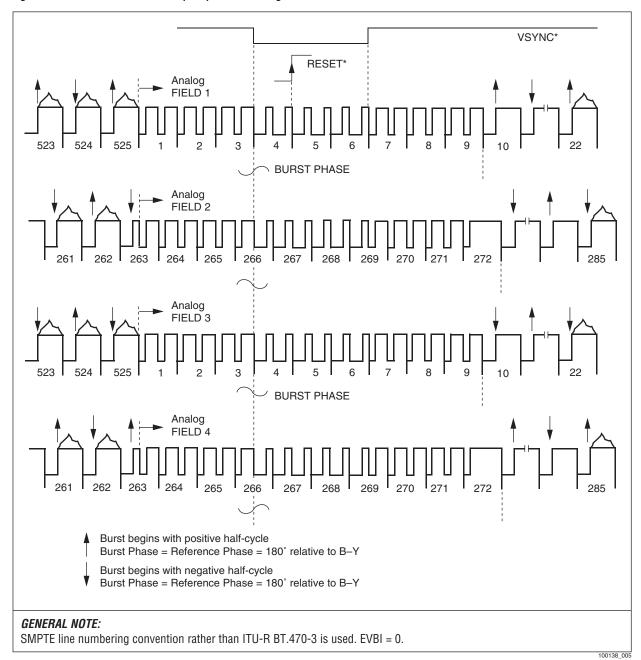

Figure 1-4. Interlaced 525-Line (TSC) Video Timing

1-8 Conexant 100138C

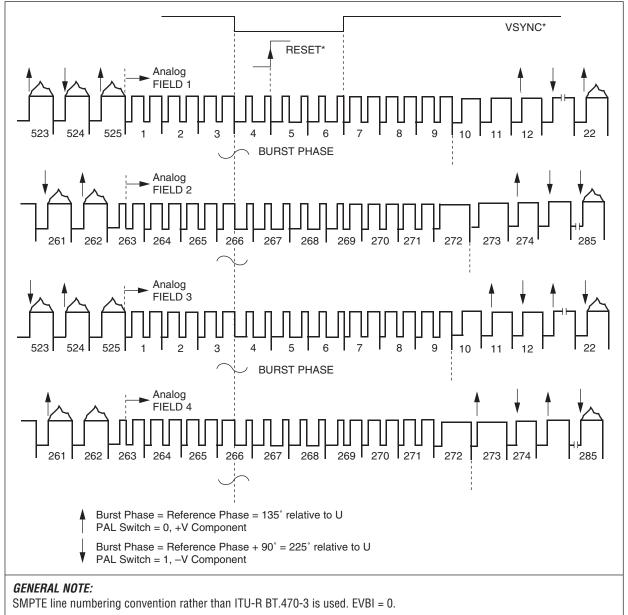

Figure 1-5. Interlaced 525-Line (PAL-M) Video Timing

00138\_006

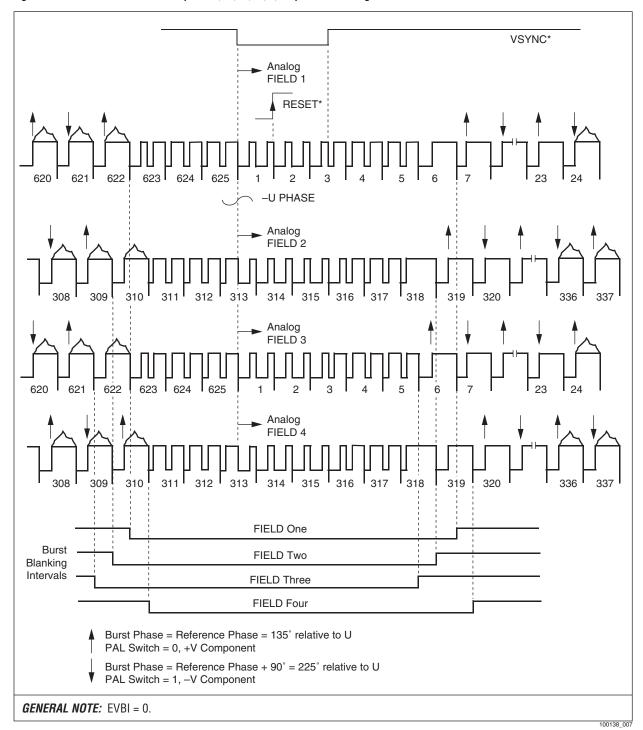

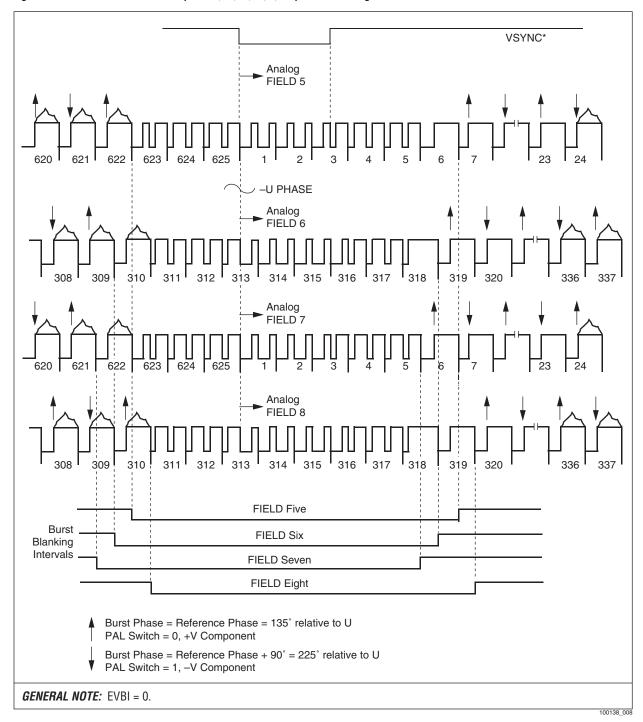

Figure 1-6. Interlaced 625-Line (PAL-B, D, G, H, I, Nc) Video Timing

Figure 1-7. Interlaced 625-Line (PAL-B, D, G, H, I, Nc) Video Timing

100138C **Conexant** 1-11 02/17/03

Figure 1-8. Interlaced 625-Line (PAL-N) Video Timing

1-12 **Conexant** 100138C 02/17/03

Figure 1-9. Interlaced 625-Line (PAL-N) Video Timing

Figure 1-10. Noninterlaced 262-Line (NTSC) Video Timing

Figure 1-11. Noninterlaced 262-Line (PAL-M) Video Timing

Figure 1-12. Noninterlaced 312-Line (PAL-B, D, G, H, I, N,  $N_c$ ) Video Timing

1-14 **Conexant** 100138C

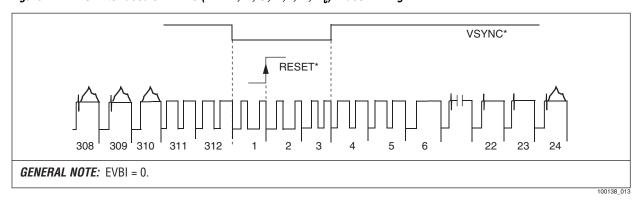

#### 1.5.1 Reset

If the RESET\* pin is held low during a single rising edge of CLK, the subcarrier phase is set to zero, and the horizontal and vertical counters are held to the first pixel and second line of FIELD1. Counting resumes on the first rising edge of CLK after rising RESET\*.

A software reset will occur immediately after writing a 1 to register SRESET. This will reset all software-programmable register bits to zero.

On power-up, the Bt864A/Bt865A will automatically perform a timing and software reset. The power-up state has the following configuration: interlaced, NTSC CCIR601 black burst (no active video), and zero chroma scaling. Setting register EACTIVE will enable active video. On power-up, the DACs are disabled for 8 fields or until register 0x67 (0xCE as 8-bit address) is written.

### 1.5.2 Sync and Burst Timing

Table 1-2 lists the resolutions and clock rates for the various modes of operation.

Table 1-2. Field Resolution and Clock Rates for Various Modes of Operation

|                                          | Active L   | uminance Re<br>(pixels)    | solution            | Total      | Luminance         |             |                    |

|------------------------------------------|------------|----------------------------|---------------------|------------|-------------------|-------------|--------------------|

| Operating Mode                           | Horizontal | Ver                        | tical               | Horizontal | Ver               | Pixel       |                    |

|                                          | Porch = 0  | Non<br>Interlaced<br>Field | Interlaced<br>Frame |            | Non<br>Interlaced | Interlaced  | Frequency<br>(MHz) |

| NTSC/PAL-MCCIR601                        | 711        | 241                        | 482                 | 858 ± 1    | 262 ± 1/4         | 262.5 ± 1/4 | 13.5000            |

| PAL-B, D, G, H, I, N, Nc<br>CCIR601      | 702        | 287                        | 575                 | 864 ± 1    | 312 ± 1/4         | 312.5 ± 1/4 | 13.5000            |

| NTSC/PAL-M Square Pixel                  | 647        | 241                        | 482                 | 780 ± 1    | 262 ± 1/4         | 262.5 ± 1/4 | 12.2727            |

| PAL-B, D, G, H, I, N, Nc<br>Square Pixel | 767        | 287                        | 575                 | 944 ± 1    | 312 ± 1/4         | 312.5 ± 1/4 | 14.7500            |

#### **GENERAL NOTE:**

- 1. Tolerances apply to slave mode. Cumulative errors over color frame interval may result in subcarrier glitches.

- 2. Due to upsampling filter response, pixels near the boundary of the active definition will be reduced in amplitude due to averaging with the blank level.

Table 1-3 lists the horizontal counter values for the end of horizontal sync, start of color burst, end of color burst, and the first active pixel for the various modes of operation. The front porch is the interval before the next expected falling HSYNC\* when outputs are automatically blanked.

The horizontal sync width is measured between the 50% points of the falling and rising edges of horizontal sync.

The start of color burst is measured between the 50% point of the falling edge of horizontal sync and the first 50% point of the color burst amplitude (nominally +20 IRE for NTSC/PAL-M and 150 mV for PAL-B, D, G, H, I, N, Nc above the blanking level).

The end of color burst is measured between the 50% point of the falling edge of horizontal sync and the last 50% point of the color burst envelope (nominally +20 IRE for NTSC/PAL-M and 150 mV for PAL-B, D, G, H, I, N, Nc above the blanking level).

Table 1-3. Horizontal Counter Values for Various Video Timings

|                              |      |                 |       |                          | Hori    | zontal C        | ounter V | alue       |            |       |                            |            |

|------------------------------|------|-----------------|-------|--------------------------|---------|-----------------|----------|------------|------------|-------|----------------------------|------------|

| Operating Mode               | -    | zation<br>Width | Serra | ontal/<br>ation<br>Width | Start o | f Burst Duratio |          |            | Back Porch |       | Front Porch <sup>(1)</sup> |            |

|                              | HCNT | μ <b>s</b>      | HCNT  | μ <b>s</b>               | HCNT    | ms              | HCNT     | μ <b>s</b> | HCNT       | ms    | HCNT                       | μ <b>s</b> |

| NTSC CCIR601                 | 32   | 2.37            | 63    | 4.67                     | 72      | 5.33            | 34       | 2.52       | 127        | 9.41  | 20                         | 1.48       |

| PAL-M CCIR601                | 32   | 2.37            | 63    | 4.67                     | 78      | 5.78            | 34       | 2.52       | 127        | 9.41  | 20                         | 1.48       |

| NTSC Square                  | 29   | 2.36            | 58    | 4.73                     | 65      | 5.30            | 31       | 2.53       | 115        | 9.37  | 18                         | 1.47       |

| PAL-M Square                 | 29   | 2.36            | 58    | 4.73                     | 71      | 5.79            | 31       | 2.53       | 115        | 9.37  | 18                         | 1.47       |

| PAL-B CCIR601                | 32   | 2.37            | 63    | 4.67                     | 76      | 5.63            | 30       | 2.22       | 142        | 10.52 | 20                         | 1.48       |

| PAL-Nc CCIR601               | 32   | 2.37            | 63    | 4.67                     | 76      | 5.63            | 34       | 2.52       | 142        | 10.52 | 20                         | 1.48       |

| PAL-B Square                 | 35   | 2.37            | 69    | 4.68                     | 83      | 5.63            | 33       | 2.24       | 155        | 10.51 | 22                         | 1.49       |

| PAL-Nc Square <sup>(2)</sup> | 35   | 2.37            | 69    | 4.68                     | 83      | 5.63            | 37       | 2.51       | 155        | 10.51 | 22                         | 1.49       |

#### **GENERAL NOTE:**

- 1. HCNT refers to the number of luminance pixel periods; there are twice as many CLK periods as HCNT periods.

- 2. Odd counts at front porch transitions indicate invalid chroma framing.

#### FOOTNOTE.

- (1) In slave mode, since Front Porch timing is triggered by the previous HSYNC pulse, any deviation from nominal line length can affect the front porch duration.

- (2) PAL-Nc refers to the PAL format used in Argentina (Combination N).

#### 1.5.3 Master Mode

Horizontal sync (HSYNC\*) and vertical sync (VSYNC\*) are generated from internal timing and from optional software bits. HSYNC\* and VSYNC\* are output following the rising edge of CLK.

The HSYNC\* output may be configured to have standard video timing (4.7  $\mu$ s wide, asserted at start of a line default after RESET cycle) or it may be programmed to specify the start of HSYNC\* (10-bit value) and the end of HSYNC\* (10-bit value). VSYNC\* is asserted for 3 scan lines for 262/525 line formats and 2.5 scan lines for 312/625 line formats (except for PAL-N which is 3 scan lines). When HSYNC\* is configured for standard video timing, coincident falling edges of HSYNC\* and VSYNC\* indicate the beginning of the first field (CCIR convention). Auto mode detection is not applicable under master mode operation.

#### 1.5.4 Slave Mode

The horizontal counter is incremented on every other rising edge of CLK. A falling edge of HSYNC\* resets it to one, indicating the start of a new line.

The vertical counter is incremented on the falling edge of HSYNC\*. A falling edge of VSYNC\* resets it to one, indicating the start of a new field (interlaced operation) or frame (noninterlaced operation).

A falling edge of VSYNC\* that occurs within  $\pm 1/4$  of a scan line from the falling edge of HSYNC\* indicates the beginning of FIELD 1. A falling edge of VSYNC\* that occurs within  $\pm 1/4$  scan line from the center of the line indicates the beginning of FIELD 2. Referring to Figure 1-4 through , start of VSYNC\* occurs on the falling HSYNC\* at the beginning of the next expected FIELD 1 and halfway between expected falling HSYNC\* edges at the beginning of the next expected FIELD 2.

HSYNC\* and VSYNC\* must remain low for at least 2 CLK cycles. The operating mode (NTSC/PAL, interlaced/noninterlaced, square pixel/CCIR601, and setup) is automatically determined when configured as a slave when the SETMODE bit is zero. 525-line operation is assumed, unless 625-line operation is detected by the number of lines in a field. Interlaced operation is detected by observing the sequence of FIELD 1 or FIELD 2; if the field timing (odd follows odd, even follows even) is repeated, then noninterlaced mode is assumed. The frequency of operation (square pixels or CCIR) is detected by counting the number of clocks per line. The pixel rate is assumed to be 13.5 MHz unless the exact horizontal count for square pixels, ±1 count, is detected in between two successive falling edges of HSYNC\*.

NOTE:

Square pixel 625-line operation with this sequence requires one frame to stabilize.

By setting SETMODE = 1, the video format control register bits (VIDFORM [3:0], SETUPDIS, NONINTL, and SQUARE) will determine the operating mode.

### 1.5.5 FIELD Output

The FIELD output indicates whether FIELD 1 (logical zero) or FIELD 2 (logical one) is being generated. This corresponds directly to the "bottom/top" convention of some MPEG decoders. Field transitions after the rising edge of CLK, two clock periods after the falling edge of VSYNC\* if SYNCDLY = 0, or three clock periods after the falling edge of VSYNC\* if SYNCDLY = 1.

To invert the sense of the FIELD output, set the FIELDI bit to a logical one.

### 1.5.6 Pixel Blanking

BLANK\* is registered on the rising edge of CLK. For video outputs, BLANK\* is pipelined to match the luminance and chrominance paths and is applied to the digital video before analog conversion. The automatic horizontal blanking sequence described in Table 1-3 takes precedence over the BLANK\* input.

### 1.5.7 Burst Blanking

For interlaced NTSC, color burst information is automatically disabled on scan lines 1–9 and 264–272, inclusive. (SMPTE line numbering convention.)

For interlaced PAL-M color burst information is automatically disabled on scan lines 1–11 and 263–273 and 525 of FIELD 1 and FIELD 2 and scan lines 1–10 and 262–272 of FIELDs 3 and 4.

For interlaced PAL–B, D, G, H, I, N, Nc, color burst information is automatically disabled on scan lines 1–6, 310–318, and 623–625, inclusive, for FIELDs 1, 2, 5, and 6. During FIELDs 3, 4, 7, and 8, color burst information is disabled on scan lines 1–5, 311–319, and 622–625, inclusive.

For noninterlaced NTSC, color burst information is automatically disabled on scan lines 1–6 and 260–262, inclusive.

For noninterlaced PAL-M, color burst information is automatically disabled on scan lines 1–10 and 260–262.

For noninterlaced PAL–B, D, G, H, I, N, Nc, color burst information is automatically disabled on scan lines 1–6 and 310–312, inclusive. See Figure 1-4 through .

## 1.5.8 Digital Processing

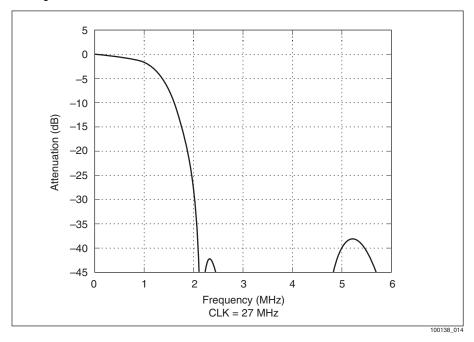

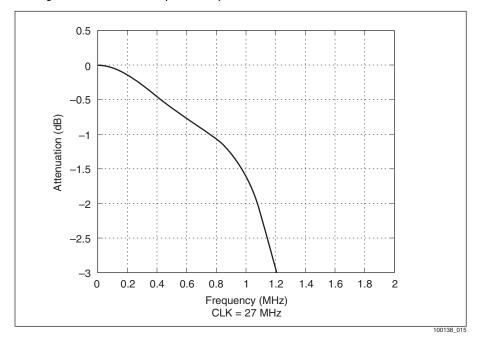

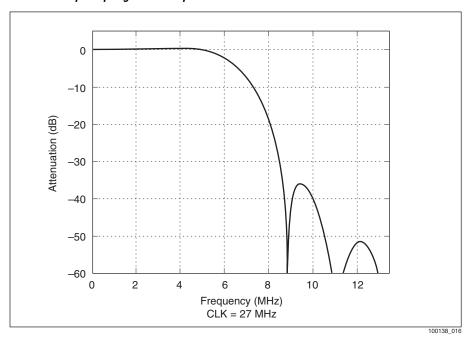

The input is scaled to YUV format. For the CVBS, Y, and C outputs, the UV components are low-pass filtered with a filter response shown in Figure 1-13 and 1-14 (linearly scalable by clock frequency). The Y and filtered UV components are upsampled to CLK frequency by a digital filter whose response is shown in Figure 1-15 and 1-16. For the RGB outputs, the scaled YUV is color space converted and output.

#### 1.5.9 Chrominance Disable

The chrominance subcarrier may be turned off by setting the DCHROMA bit to a logical one. This kills burst as well, providing luminance only signals on the CVBS outputs and a static blank level on the C/R output (RGBOUT = 0).

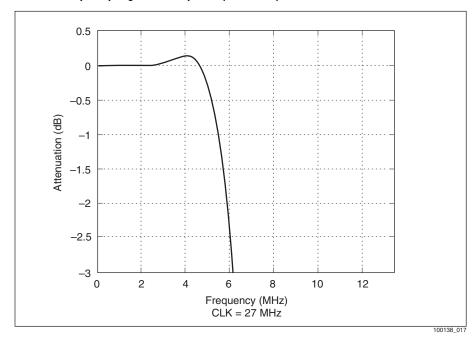

Figure 1-13. Three-Stage Chrominance Filter

Figure 1-14. Three-Stage Chrominance Filter (Passband)

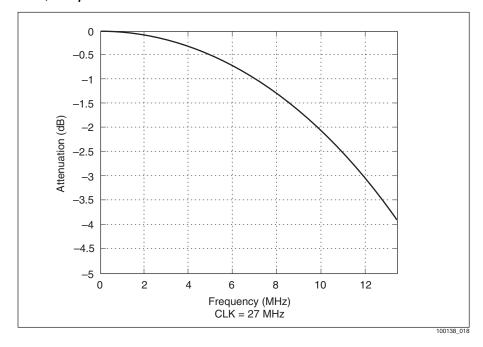

Figure 1-15. Luminance 2X Upsampling Filter Response

Figure 1-16. Luminance 2X Upsampling Filter Response (Passband)

### 1.5.10 Subcarrier Phasing

In order to maintain correct SC-H phasing, the subcarrier phase is set to zero on the falling edge of HSYNC\* associated with VSYNC\* every four (NTSC) or eight (PAL) fields, unless the SCRESET bit is set to a logical one.

In slave mode, falling HSYNC\* may lag falling VSYNC\* by 1/4 scan line but cannot precede falling VSYNC\* by more than seven CLK periods for correct SC-H reset.

Setting SCRESET to one may be useful in situations where the ratio of CLK/2 to HSYNC\* edges in a color frame is noninteger, which could produce a significant phase impulse by resetting to zero.

## 1.5.11 Vertical Blanking Intervals

For interlaced NTSC/PAL-M, if EVBI = 0, scan lines 1–21 and 263–284, inclusive, are always blanked regardless of the BLANK\* input (SMPTE line numbering convention).

For interlaced PAL–B, D, G, H, I, N, Nc, if EVBI = 0, scan lines 1–23, 311–335, and 624–625, inclusive, are always blanked regardless of the BLANK\* input.

For noninterlaced NTSC/PAL-M, if EVBI = 0, scan lines 1–17 and 261–262, inclusive, are always blanked regardless of the BLANK\* input. For noninterlaced PAL-B, D, G, H, I, N, Nc, if EVBI = 0, scan lines 1–22 and 311–312, inclusive, are always blanked regardless of the BLANK\* input.

Alternately, all displayed lines in the vertical blanking interval (10–21 and 273–284 for interlaced NTSC/PAL–M; 6–23 and 320–335 for interlaced PAL–B, D, G, H, I, N, Nc; 10–21 for noninterlaced NTSC/PAL–M, 7–23 for noninterlaced PAL–B, D, G, H, I, N, Nc) may be enabled by setting the EVBI bit to a logical one (except for caption lines controlled by bits ECCF1 or ECCF2, or the Macrovision process).

#### 1.5.12 BLANK\* Pin

The BLANK\* pin can be used to BLANK any portion of the active display lines (including those enabled by EVBI) by driving the pin to a logical zero.

## 1.5.13 Noninterlaced Operation

When the Bt864A/Bt865A is programmed for noninterlaced master mode, the Bt864A/Bt865A always displays FIELD 1, meaning that the falling edges of HSYNC\* and VSYNC\* will be output coincidentally. FIELD will be held low if FIELDI = 0. Additionally, a 30 Hz offset will be subtracted from the color subcarrier frequency while in NTSC mode so that the color subcarrier phase will be inverted from field to field.

Transition from interlaced to noninterlaced in master mode, occurs during FIELD 1 to prevent synchronization disturbance. In slave mode, transition occurs after a subsequent falling edge of VSYNC\*.

NOTE:

Consumer VCRs can record noninterlaced video with minor noise artifacts, but special effects (e.g., scan > 2x) may not function properly.

## 1.6 Power Saving Modes

In SLEEP power-down mode (SLEEP pin set to 1), all analog and digital circuitry is disabled, and total device current consumption approaches 0 mA. Register states are preserved, but other chip functionality (including I<sup>2</sup>C communication) is disabled. This mode should be set when the Bt864A/Bt865A may be subjected to clock and data frequencies outside its functional range.

In DACOFF power-down mode, (DACOFF register is set to 1) all DACs are disabled and analog current is reduced to approximately 0 mA. All other digital circuitry remains operational, permitting system timing and other functions to continue.

When DACs are disabled by either SLEEP or DACOFF, VREF will go to approximately 0.5 V below VAA.

## 1.7 Pixel Input Ranges and Colorspace Conversion

## 1.7.1 YC Inputs (4:2:2 YCrCb)

Y has a nominal range of 16–235; Cb and Cr have a nominal range of 16–240, with 128 equal to zero. Values of 0 and 255 are interpreted as 1 and 254, respectively. Y values of 1–15 and 236–254, and CrCb values of 1–15 and 241–254, are interpreted as valid linear values.

The SETUPDIS bit will alter pixel scaling and disable or enable the 7.5 IRE setup. When this bit is enabled, PAL–B, D, G, H, I, N, Nc video can be generated using NTSC/PAL–M blanking levels and 7.5 IRE setup, and NTSC/PAL–M pixel scaling is performed (Y range of 16–235 represents 7.5–100 IRE); or, NTSC/PAL–M video can be generated using PAL–B, D, G, H, I, N, Nc scaling (Y range of 16–235 represents 0–100 IRE) without the 7.5 IRE setup. NTSC/PAL–M mode with setup disabled has 2% less black-to-white range than NTSC/PAL–M mode with setup enabled.

For RGBOUT mode, 4:2:2 YCrCb digital component video will be upsampled to 4:4:4 and used to generate composite video and will be converted to the RGB colorspace to drive the RGB DACs. The Y input range of 16–235 will produce a range of 0.7 V at the output. Since YC values outside of the nominal range are allowed, the black level is raised above zero volts to allow for Y values less than 16, and the output range of the DACs can exceed 0.7 V to allow for Y values above 235. The conversion is linearly scaled in the overshoot and undershoot regions. The following matrix, based on CCIR601, is used to convert YCrCb to RGB:

- R = Y + 1.371\*Cr

- G = Y 0.699\*Cr 0.337\*Cb

- B = Y + 1.733\*Cb

Values are rounded to 9 bits at the DAC.

## 1.7.2 DAC Coding

For all video formats, the input luma and chroma values are scaled internally such that, after sync and setup (if enabled) are added, the output from sync to 100% white (for CVBS/Y outputs) is approximately 1.00 V.

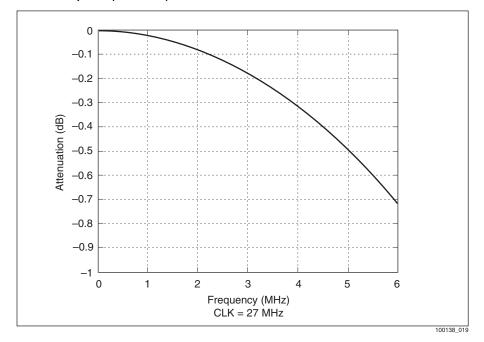

In addition, the chroma is boosted to compensate for the sinx/x rolloff due to the DAC (see Figures 1-17 and 1-18). The amount of boost is determined by SETUPDIS. Table 1-4 summarizes the blank, black, and 100% white DAC codes and chroma gain values as a function of SETUPDIS.

Table 1-4. DAC Coding

| SETUPDIS | Blank | Black | 100% White | Chroma Gain |

|----------|-------|-------|------------|-------------|

| 0        | 228   | 272   | 801        | 1.02944     |

| 1        | 1 224 |       | 800        | 1.0458      |

Figure 1-17. DAC Sinx/x Response

Figure 1-18. DAC Sinx/x Response (Passband)

## 1.8 Closed Captioning

The Bt864A/Bt865A encodes NTSC/PAL—M closed captioning on scan line 21 and NTSC/PAL—M extended data services on scan line 284. Four 8-bit registers (CCF1B1, CCF1B2, CCF2B1, and CCF2B2) provide the data while bits ECCF1and ECCF2 enable display of the data. A logical zero corresponds to the blanking level of 0 IRE, while a logical one corresponds to 50 IRE above the blanking level.

Closed captioning for PAL–B, D, G, H, I, N, Nc is similar to that for NTSC. Closed caption encoding is performed for 625-line systems according to the system proposed by the National Captioning Institute; clock and data timing is identical to that of NTSC system, except that encoding is provided on lines 22 and 335.

The Bt864A/Bt865A generates the clock run-in and appropriate timing automatically. Pixel inputs are ignored during CC encoding. See FCC Code of Federal Regulations (CFR) 47 Section 15.119 (10/91 edition or later) for programming information. EIA608 describes ancillary data applications for FIELD 2 Line 21 (line 284).

When CCF1B2 is written, CCSTAT1 is set; when CCF2B2 is written CCSTAT2 is set (CCSTAT1 and CCSTAT2 are defined in Table 2-1). After the closed-caption bytes for FIELD 1 are encoded, CCSTAT1 is cleared; after the closed-caption bytes for FIELD 2 are encoded, CCSTAT2 is cleared. If the ECCGATE bit is set, no further encoding will be performed until the appropriate registers are again written; a NULL with odd parity will be transmitted on the appropriate closed caption line in that case. User must set the odd parity bit. If the ECCGATE bit is not set, the user must rewrite the closed-caption registers prior to reaching the closed-caption line, otherwise the last bytes will be re-encoded.

Closed-caption will override EVBI inserted data on lines 21 and 284 for 525-line formats, and lines 22 and 335 for 625-line formats. Closed-caption will be overridden by teletext if teletext is enabled on these lines.

Closed caption data registers are double buffered and can be loaded without the risk of corrupting data as it is being encoded onto the appropriate video line (line 21 or 284 for 525-line formats, line 22 or 335 for 625-line formats).

## 1.9 Teletext

Teletext encoding is accomplished via a two-wire interface, TTXDAT and TTXREQ, and internal registers that are programmed through the I<sup>2</sup>C interface. Teletext encoding in the Bt864A/Bt865A conforms to Teletext B for 625/50 television systems. See "Recommendation 653-1 Teletext Systems" for further information about the standard. Teletext should be disabled for 525-line television systems.

The internal registers allow for the enable/disable of teletext and the programming of the start and stop of the TTXREQ signal, the active teletext lines in an FIELD 1, and the active teletext lines in FIELD 2. Active teletext lines override closed caption, Macrovision, the BLANK\* input, and active video. See the "Internal Registers" section for more details.

The TTXREQ signal is generated by the encoder to indicate to external devices when teletext data is required. The start and end of the TTXREQ signal waveform is determined by the value of registers TXHS and TXHE, respectively. The values of registers TXHS and TXHE correspond to the internal clock (CLK) counter (see Figure 1-19). The proper selection of these edges will allow the user to adjust for the propagation delay of the teletext source, so that the teletext data is provided to the TTXDAT pin at the proper time. If the falling edge of TTXREQ does not occur by the end of the video line, the beginning of the new video line will automatically reset TTXREQ. Legal values for these registers are given in Table 1-5.

The data to TTXDAT is sampled on every rising input clock edge and must meet the following protocol for proper teletext data insertion. The protocol demands that the teletext data bit duration is the required number of CLKs.

Internal to the chip is a sequencer and a data shaper to minimize the jitter. Using the midpoint of the falling edge of the horizontal sync pulse as it appears at the output Y/CVBS or CVBS/G, the teletext data protocol must begin 262 to 264 CLKs later for CCIR601(13.5 MHz pixel rate) or 286 to 288 CLKs later for Square Pixel Operation (14.75 MHz pixel rate). Relative to the internally generated teletext window, the protocol must start 5 to 7 clocks earlier. The teletext window begins at  $10.2 \,\mu sec$  from the horizontal sync pulse's falling edge and the data rate is the specified 6.9375 Mbits/sec.

(2) TTXREQ <u>t</u>PD<sup>(3)</sup> → -tttxint<sup>(4)</sup> TTXDAT tTTXOWS (5) CVBS(6) CVBS/G Y/CVBS tttxiws<sup>(7)</sup> Internal Horizontal Reset Internal 2 3 4 5 . . 2345. Clock (CLK) Counter<sup>(9)</sup>

Figure 1-19. Teletext Timing for Tb864A/Bt865A Encoder

#### **GENERAL NOTE:**

1. TXE is enabled and video line is a valid teletext line. See "teletext" on page 1-26.

#### FOOTNOTE:

- (1) Placement of rising edge of TTXREQ is definable using register TXHS[10:0].

- (2) Placement of falling edge of TTXREQ is definable using register TXHE[10:0].

- TTXREQ is generated by the encoder using programmable registers TXHS and TXHE. This allows the user to adjust for the propagation delay  $(t_{PD})$  in CLK cycles of the teletext data source.

- (4) TTXDAT is supplied to the encoder at the proper time to be interpolated by the encoder (t<sub>TTXINT</sub>) and inserted into the video output signals. The Teletext data must follow the correct protocol. See "Teletext" on page 1-26.

- $t_{\text{TTXOWS}}$  is the start of the teletext output window and is fixed internally by the encoder at 10.2 usec.

- (6) Luma Delay is set to zero.

- (7)  $t_{TTXIWS}$  is the start of the teletext input window and is fixed internally.

- (8) If the falling edge of TTXREQ does not occur by the end of a video line, the beginning of a new line will automatically reset TTXREQ.

- (9) 2 clock (CLK) counts = 1 pixel clock count.

100138\_020

Table 1-5. Legal Values to TXHS and TXHE

|            | Pixel rate | TXHS  | ТХНЕ     |

|------------|------------|-------|----------|

| Min. Value | 13.5 MHz   | 2     | TXHS + 2 |

| Max. Value | 13.5 MHz   | 0x6BE | 0x7FF    |

| Min. Value | 14.75 MHz  | 2     | TXHS + 2 |

| Max. Value | 14.75 MHz  | 0x75E | 0x7FF    |

Bt864A/Bt865A Data Sheet Circuit Description

### 1.9.1 CCIR601 Operation (13.5 MHz pixel rate)

The bit duration follows this pattern which repeats every 37 teletext bits. Each teletext data bit is carried by four CLKs except bits 10, 19, 28, and 37 which are three CLKs in duration. This pattern continues until all 360 bits (1402 CLKs) have been transferred.

### 1.9.2 Square Pixel Operation (14.75 MHz pixel rate)

This bit pattern repeats after every 111 teletext bits: After every teletext bit that is carried by five CLKs the next three teletext bits are carried by four CLKs except for the first bit of the pattern which is five CLKs in duration and only the next two bits are carried by four CLKs. This pattern continues until all 360 bits (1531 CLKs) have been transferred. The repeating bit duration pattern starting at bit 1 would be:

Bit number: 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15...

Duration in 5 4 4 5 4 4 4 5 4 4 5 4 4 5 4 4 5 ...

CLKs:

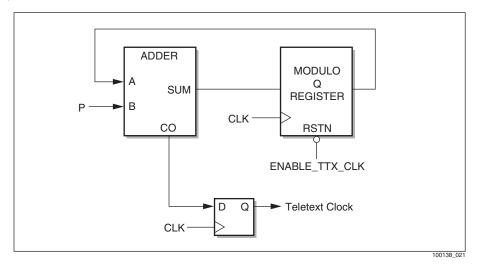

#### 1.9.3 Teletext Clock Generation

Figure 1-20 shows how to generate a teletext clock using a P:Q ratio counter for shifting out the teletext data serially to the Bt864A/Bt865A. The diagram is for illustrative purposes only. The actual implementation is left to the user.

Figure 1-20. PQ Ratio Counter

Table 1-6. Teletext Clock P and Q Values

| CLK      | Pixel Rate | Р   | Q   |

|----------|------------|-----|-----|

| 27 MHz   | 13.5 MHz   | 37  | 144 |

| 29.5 MHz | 14.75 MHz  | 111 | 472 |

Circuit Description Bt864A/Bt865A Data Sheet

### 1.9.4 Teletext Clock Output

The Bt864A/Bt865A can output the teletext clock from the TTXREQ pin by setting TXRM = 1. In this mode, this teletext clock would only be output on active teletext lines and each line would have exactly 360 clocks to be used to synchronize the teletext data to the Bt864A/Bt865A. The rising edge of clock could be used to latch the data on the output of the device providing the teletext data. The falling of the clock indicates that the Bt864A/Bt865A has received the teletext data.

# 1.10 Copy Generation Management System (CGMS) Encoding

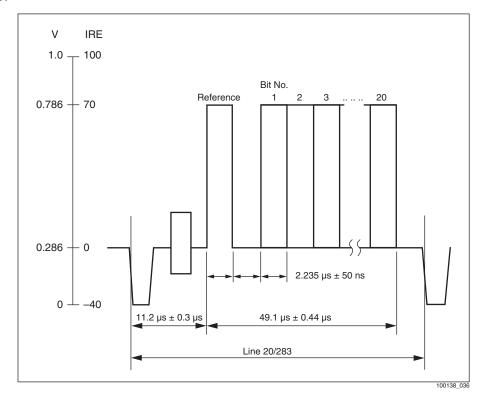

Copy Generation Management System (CGMS) is used in 525-line systems on lines 20 and 283 (a.k.a. line 20, field 2). The CGMS data is 20 bits long and is entered on register bits WSDAT[20:1].

- Set register bit EWSF1 to 1 to enable CGMS on field 1, line 20.

- Set register bit EWSF2 to 1 to enable CGMS on field 2, line 283.

Although there is no clock run-in in CGMS, a reference pulse is provided automatically.

CRC data is not calculated and must be provided by the user. Figure 1-21 illustrates a typical CGMS signal. Note that bit 1 is closest to the HSYNC pulse and bit 20 is farthest. The amplitude of the CGMS pulses are 70 IRE when high, and 0 IRE when low. For further CGMS details, see specifications *EIA-J CPR-1202*, *EIA-J CPR-1204*, and *IEC 61880*.

Figure 1-21. Typical CGMS Waveform

Bt864A/Bt865A Data Sheet Circuit Description

## 1.11 Anticopy Process (Bt865A Only)

The anticopy process contained within the Bt865A is implemented according to the Macrovision version 7 specification developed by Macrovision Corporation in Sunnyvale, California. All luminance, chrominance, and composite video waveforms include the Macrovision Anticopy Process. The Bt865A incorporates an anticopy process technology that is protected by U.S. patents and other intellectual property rights. The anticopy process is licensed for noncommercial, home use only. Reverse engineering or disassembly is prohibited.

Conexant cannot ship Bt865A encoders to any customer until that customer has been licensed by Macrovision. Contact Macrovision Corporation to facilitate this license agreement. Parties who have obtained a Macrovision license may receive the Bt865A Macrovision Supplement by contacting Conexant.

## 1.12 Internal Color Bars

The Bt864A/Bt865A can be configured to internally generate colorbar test patterns (100/7.5/75/7.5 with SETUPDIS = 0 for NTSC/PAL-M,N; 100/0/75/0 with SETUPDIS = 1 for NTSC-Japan, PAL, BDGHI, Nc).

Internal color bars can be enabled by setting the ECBAR bit to a logical one. In 8-bit YCrCb mode, setting the Y[7] pin to a logical one also enables color bars, thereby simplifying testing of various modes. Internal color bars can be enabled in all video formats.

## 1.13 SCART/PeriTV Support

RGBOUT mode can be enabled by setting the RGBOUT pin to a logical one, or by setting register bit RGBO. The Bt864A/Bt865A can generate analog RGB video signals to interface to a SCART/PeriTV connector (see Table 1-7). Composite video will be present on the Y/CVBS DAC. RGB outputs are nominally 700 mVpp (black to white without setup).

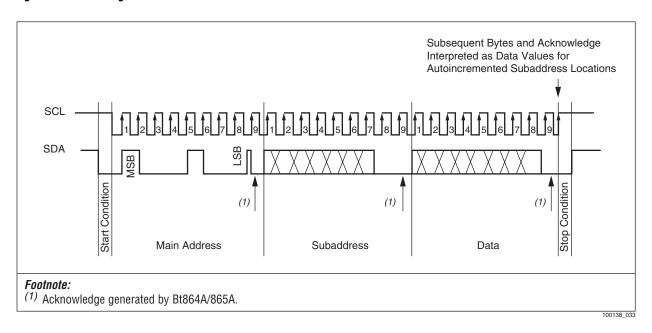

## 1.14 I<sup>2</sup>C Interface

A simplified 100 kbps I<sup>2</sup>C interface is provided for programming the registers. CLK must be applied and remain stable for I<sup>2</sup>C communication. Activating SLEEP or RESET\* will disable I<sup>2</sup>C communication.

Circuit Description Bt864A/Bt865A Data Sheet

## 1.15 Analog Outputs

All digital-to-analog converters are designed to drive standard video levels into a combined RLOAD of 37.5  $\Omega$  Unused outputs should be connected directly to ground to minimize supply switching currents. In standard mode, one S-Video (Y/C), and two composite video outputs are available. In RGBOUT mode, one composite video output along with analog RGB are available (see Table 1-7). If the SLEEP pin is high or DACOFF = 1, the DACs are essentially turned off and only the leakage current is present. The D/A converter values for 100% saturation, 100% amplitude color bars are shown in Figures 1-22 through 1-27. Both composite video and analog RGB video (to provide support for SCART/PeriTV) may be generated simultaneously.

Pin Number Pin Function **DAC Name** Signal **AGND** Std Mode **RGB Out Mode** CVBS/B 8 6 **CVBS** В CVBS/G 7 10 **CVBS** G C/R 12 9 C R Υ 13 Y/CVBS 11 **CVBS**

Table 1-7. DAC Output Cross-Reference

### 1.15.1 Luminance or CVBS (Y/CVBS) Output

Digital luminance information drives the 10-bit D/A converter that generates the analog Y video output (Figures 1-22 and 1-23 and Tables 1-8 and 1-9). This DAC can also provide CVBS for SCART/PeriTV synchronization when RGBOUT is enabled.

## 1.15.2 Chrominance or Red (C/R) Output

Digital chrominance information drives the 10-bit D/A converter that generates the analog C video output (Figures 1-24 and 1-25 and Tables 1-10 and 1-11). This DAC can also provide Red for SCART/PeriTV when RGBOUT is enabled.

## 1.15.3 Composite Video or Blue (CVBS/B) Output

Digital composite video information drives the 10-bit D/A converter that generates the analog NTSC or PAL video output (Figures 1-26 and 1-27 and Tables 1-12 and 1-13). This DAC can also provide Blue for SCART/PeriTV when RGBOUT is enabled. An optional luminance delay can be enabled on this pin (in standard mode only) by setting the LUMADLY bits. The luma can be delayed 0 to 3 pixels (up to 200–245 ns) to compensate for group delays introduced in the chroma path by external filters or vestigial sideband processing.

## 1.15.4 Composite Video or Green (CVBS/G) Output

Digital composite video information drives the 10-bit D/A converter that generates the analog video output (Table 1-14). This DAC can also provide Green for SCART/PeriTV when RGBOUT mode is enabled.

Bt864A/Bt865A Data Sheet Circuit Description

٧ mΑ 801 White Level 26.68 1.000 100 IRE 9.07 0.340 Black Level 7.5 IRE 0.285 Blank Level 7.60 40 IRE 0.00 0.000 Sync Level **GENERAL NOTE:** Typical with 37.5  $\Omega$  load, nominal RSET. SMPTE 170 M levels are assumed. 100% saturation color bars (100/7.5/100/7.5) are shown.

Figure 1-22. Y (Luminance) Video Output Waveform SETUPDIS = 0

100138\_023

Table 1-8. Y (Luminance) Video Output Truth Table SETUPDIS = 0

| Description | lout (mA) | DAC Data | Sync Interval | BLANK* <sup>(1)</sup> |

|-------------|-----------|----------|---------------|-----------------------|

| White       | 26.68     | 801      | 0             | 1                     |

| Black       | 9.07      | 272      | 0             | 1                     |

| Blank       | 7.60      | 228      | 0             | 0                     |

| Sync        | 0         | 0        | 1             | 0                     |

#### **GENERAL NOTE:**

#### FOOTNOTE:

<sup>1.</sup> Typical with 37.5  $\Omega$  load, nominal RSET, and setup on. SMPTE 170 M levels are assumed. 100% saturation color bars (100/ 7.5/100/7.5) are shown.

Circuit Description Bt864A/Bt865A Data Sheet

Figure 1-23. Y (Luminance) Video Output Waveform SETUPDIS = 1

Table 1-9. Y (Luminance) Video Output Truth Table SETUPDIS = 1

| Description | lout (mA) | DAC Data | Sync Interval | BLANK* <sup>(1)</sup> |

|-------------|-----------|----------|---------------|-----------------------|

| White       | 28.68     | 800      | 0             | 1                     |

| Black       | 8.00      | 240      | 0             | 1                     |

| Blank       | 8.00      | 240      | 0             | 0                     |

| Sync        | 0         | 0        | 1             | 0                     |

100138\_024

#### GENERAL NOTE:

#### FOOTNOTE:

<sup>1.</sup> Typical with 37.5  $\Omega$  load and nominal RSET. ITU-RBT.470-3 levels are assumed. 100% saturation (100/0/100/0) color bars are shown.

Bt864A/Bt865A Data Sheet Circuit Description

٧  $\mathsf{m}\mathsf{A}$ Green Black 28.21 1.058 20.88 0.783 **20 IRE** Blank 17.07 0.640 Level **20 IRE** 13.27 0.498 Color Burst (9 Cycles) 5.93 0.222

Figure 1-24. C (Chrominance) Video Output Waveform SETUPDIS = 0

**GENERAL NOTE:**

Typical with 37.5  $\Omega$  load, nominal RSET, and chroma on. SMPTE 170 M levels are assumed. 100% saturation color bars (100/7.5/100/7.5) are shown.

Table 1-10. C (Chrominance) Video Output Truth Table SETUPDIS = 0

| Description        | lout (mA)     | DAC Data  | Sync Interval | BLANK* <sup>(1)</sup> |

|--------------------|---------------|-----------|---------------|-----------------------|

| Peak Chroma (High) | 28.21 [25.56] | 856 [770] | х             | 1                     |

| Burst (High)       | 20.88 [20.88] | 629 [629] | х             | Х                     |

| Blank              | 17.07 [17.07] | 512 [512] | Х             | 0                     |

| Burst (Low)        | 13.27 [13.27] | 395 [395] | х             | Х                     |

| Peak Chroma (Low)  | 5.93 [8.53]   | 168 [254] | Х             | 1                     |

#### **GENERAL NOTE:**

- 1. Typical with 37.5  $\Omega$  load, nominal RSET, and chroma on. SMPTE 170 M levels are assumed. 100% saturation color bars (100/ 7.5/100/7.5) are shown.

- 2. Bracketed values indicate expected values when using the internal color bars (100/7.5/75/7.5).

Circuit Description Bt864A/Bt865A Data Sheet

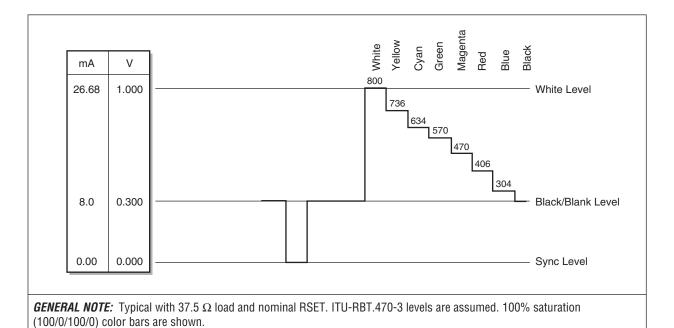

Figure 1-25. C (Chrominance) Video Output Waveform SETUPDIS = 1

**GENERAL NOTE:** Typical with 37.5  $\Omega$  load, nominal RSET, and chroma on. ITU-RBT.470-3 levels are assumed. 100% saturation (100/0/100/0) color bars are shown.

100138\_026

Table 1-11. C (Chrominance) Video Output Truth Table SETUPDIS = 1

| Description        | lout (mA)     | DAC Data  | Sync Interval | BLANK* <sup>(1)</sup> |

|--------------------|---------------|-----------|---------------|-----------------------|

| Peak Chroma (High) | 28.88 [26.06] | 877 [785] | Х             | 1                     |

| Burst (High)       | 21.08 [21.08] | 635 [635] | Х             | Х                     |

| Blank              | 17.07 [17.07] | 512 [512] | Х             | 0                     |

| Burst (Low)        | 13.07 [13.07] | 389 [389] | Х             | Х                     |

| Peak Chroma (Low)  | 5.27 [7.97]   | 147 [239] | Х             | 1                     |

#### GENERAL NOTE:

- 1. Typical with 37.5  $\Omega$  load, nominal RSET, and chroma on. ITU-RBT.470-3 levels are assumed. 100% saturation (100/0/100/0) color bars are shown.

- 2. Bracketed values indicate expected values when using the internal color bars (100/0/75/0).

#### FOOTNOTE

Bt864A/Bt865A Data Sheet Circuit Description

Magenta Yellow Green Cyan mΑ ٧ 1.221 32.55 **34 IRE** 801 26.68 1.000 White Level 740 583 100 IRE 489 429 Color Burst (9 Cycles) 332 11.41 0.423 0.340 9.07 Black Level 20 IRE 7.5 IRE 7.60 0.285 Blank Level **20 IRE** 3.80 0.143 40 IRE 3.20 0.120 0.000 0.00 Sync Level **GENERAL NOTE:** Typical with 37.5  $\Omega$  load, nominal RSET, clipping off, and chroma on. SMPTE 170 M levels are assumed. 100% saturation

Figure 1-26. CVBS (Composite) Video Output Waveform SETUPDIS = 0

color bars (100/7.5/100/7.5) are shown.

Table 1-12. CVBS (Composite) Video Output Truth Table SETUPDIS = 0

| Description        | lout (mA)     | DAC Data  | Sync Interval | BLANK*(1) |

|--------------------|---------------|-----------|---------------|-----------|

| Peak Chroma (High) | 32.55 [30.38] | 988 [922] | 0             | 1         |

| White              | 26.68 [26.68] | 801 [801] | 0             | 1         |

| Burst (High)       | 11.41 [11.41] | 345 [345] | 0             | Х         |

| Black              | 9.07 [9.07]   | 272 [272] | 0             | 1         |

| Blank              | 7.60 [7.60]   | 228 [228] | 0             | 0         |

| Burst (Low)        | 3.80 [3.80]   | 111 [111] | 0             | Х         |

| Peak Chroma (Low)  | 3.20 [5.32]   | 85 [149]  | 0             | 1         |

| Sync               | 0 [0]         | 0 [0]     | 1             | 0         |

#### GENERAL NOTE:

- 1. Typical with 37.5  $\Omega$  load, nominal RSET, clipping off, and chroma on. SMPTE 170 M levels are assumed. 100% saturation color bars (100/7.5/100/7.5) are shown.

- 2. Bracketed values indicate expected values when using the internal color bars (100/7.5/75/7.5).

Circuit Description Bt864A/Bt865A Data Sheet

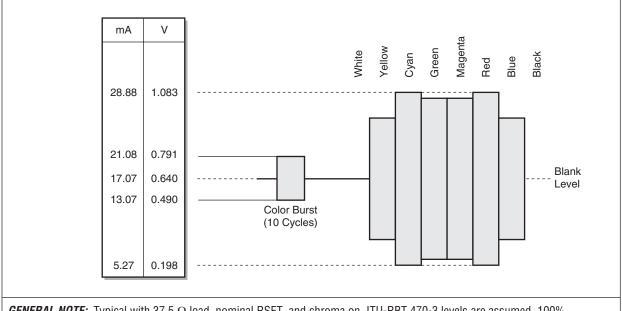

Magenta Green mΑ ٧ 32.88 1.233 800 White Level 26.68 1.000 634 570 470 Color Burst 406 (10 Cycles) 12.01 0.450 304 8.00 0.300 Black/Blank Level 4.00 0.150 1.80 0.068 0.00 0.000 Sync Level GENERAL NOTE: Typical with 37.5  $\Omega$  load, nominal RSET, and clipping off. ITU-RBT.470-3 levels are assumed. 100% amplitude, 100% saturation (100/0/100/0) color bars are shown.

Figure 1-27. CVBS (Composite) Video Output Waveform SETUPDIS = 1

00138\_028

Table 1-13. CVBS (Composite) Video Output Truth Table SETUPDIS = 1

| Description        | lout (mA)     | DAC Data       | Sync Interval | BLANK* <sup>(1)</sup> |

|--------------------|---------------|----------------|---------------|-----------------------|

| Peak Chroma (High) | 32.88 [30.61] | 998 [929]      | 0             | 1                     |

| White              | 26.68 [26.68] | 800 [800]      | 800 [800] 0   |                       |

| Burst (High)       | 12.01 [12.01] | 1] 363 [363] 0 |               | Х                     |

| Black              | 8.00 [8.00]   | 240 [240]      | 0             | 1                     |

| Blank              | 8.00 [8.00]   | 240 [240]      | 0             | 0                     |

| Burst (Low)        | 4.00 [4.00]   | 117 [117]      | 0             | Х                     |

| Peak Chroma (Low)  | 1.80 [3.76]   | 41 [110]       | 0             | 1                     |

| Sync               | 0 [0]         | 0 [0]          | 1             | 0                     |

#### **GENERAL NOTE:**

- 1. Typical with 37.5  $\Omega$  load, nominal RSET, and clipping off. ITU-RBT.470-3 levels are assumed. 100% amplitude, 100% saturation (100/0/100/0) color bars are shown.

- 2. Bracketed values indicate expected values when using the internal color bars (100/0/75/0).

#### **FOOTNOTE**

Bt864A/Bt865A Data Sheet Circuit Description

Table 1-14. RGB Output Table (RGBOUT = 1)

| Description | SETUPDIS = 1           |     | SETUP     | BLANK* <sup>(1)</sup> |       |

|-------------|------------------------|-----|-----------|-----------------------|-------|

| Description | lout (mA) DAC Data lou |     | lout (mA) | DAC Data              | DLANK |

| White       | 18.68                  | 560 | 18.68     | 560                   | 1     |

| Black       | 0                      | 0   | 1.47      | 44                    | 1     |

| Blank       | 0                      | 0   | 0         | 0                     | 0     |

**GENERAL NOTE:** lout typical with 37.5  $\Omega$  load, nominal RSET.

FOOTNOTE:

<sup>(1)</sup> BLANK occurs by external BLANK\* pin or internally generated BLANK

Circuit Description Bt864A/Bt865A Data Sheet

## **Internal Registers**