# ST1111J

Version : A.005 Issue Date : 2004/07/12 File Name : SP-ST1111J-A.005.doc Total Pages : 8

# **PWM Input Control**

# Single Coil Brushless DC Motor Drivers

# (1.5 to 7.5 Volts)

SILICON TOUCH TECHNOLOGY INC. 新竹市科學園區展業一路九號7樓之1— 9-7F-1 Prosperity Road 1 Science-Based Industrial Park Hsinchu, Taiwan 300, R.O.C. Tel: 886-3-5645656 Fax: 886-3-5645626

## ST1111J

# **PWM Input Control**

# **Single Coil Brushless DC Motor Drivers**

# (1.5 to 7.5 Volts)

#### **General Specifications**

The device is a single coil DC brushless motor driver IC with pwm control, lock protection, power polarity reverse protection and frequency generator function. The driver is optimal for single coil fan applications with less external components.

#### Features and Benefits

- Support single-phase full wave Brushless DC Motor Driver

- Low voltage startup

- High output sinking and driving capability

- Lock detection and automatic self-restart

- Without external timing capacitor, reduces the numbers of external component required

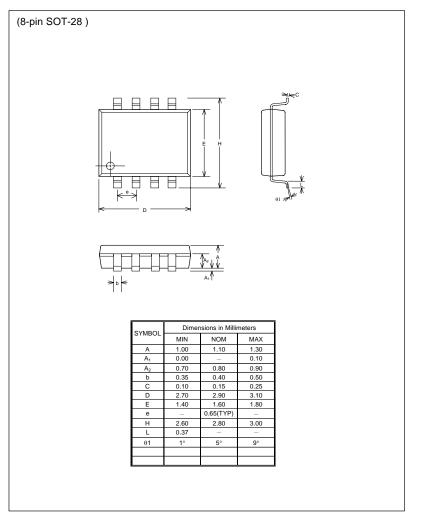

- Thin, compact, highly reliable package (SOT-28)

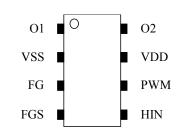

#### **Pin Description**

| NO. | NAME | DESCRIPTION                   |  |  |

|-----|------|-------------------------------|--|--|

| 1   | O1   | Output driving & sinking pin  |  |  |

| 2   | VSS  | Ground pin                    |  |  |

| 3   | FG   | Frequency Generator           |  |  |

| 4   | FGS  | FG output Frequency Selection |  |  |

| 5   | HIN  | Input from HALL IC            |  |  |

| 6   | PWM  | Input pin from Hall IC        |  |  |

| 7   | VDD  | Power supply pin              |  |  |

| 8   | 02   | Output driving & sinking pin  |  |  |

**Absolute Maximum Ratings** (Unless otherwise noted,  $T_A = 25 \text{ °C}$ )

| Characteristic                                | Symbol           | Rating               | Unit |

|-----------------------------------------------|------------------|----------------------|------|

| Supply Voltage                                | V <sub>DD</sub>  | 7.5                  | V    |

| Input Voltage from a Hall Effect Latch Output | V <sub>IN</sub>  | V <sub>DD</sub> +0.4 | V    |

| Output Current (peak)                         | I <sub>OL</sub>  | 1000 *               | mA   |

| Output Current                                | I <sub>OUT</sub> | 400                  | mA   |

| Power Dissipation                             | PD               | 350                  | mW   |

| Operating Temperature Range                   | T <sub>OPR</sub> | -40 ~ 125            | °C   |

| Storage Temperature Range                     | T <sub>STG</sub> | -65 ~ 150            | °C   |

\*Note: When operating large output current, do not excess allowable  $\mathsf{P}_\mathsf{D}$  & temperature range.

ST1111J

| Characteristic                                | Sym.                | Condition                    |                     | Limit |                      |            |  |

|-----------------------------------------------|---------------------|------------------------------|---------------------|-------|----------------------|------------|--|

|                                               |                     |                              | Min.                | Тур.  | Max.                 | Unit       |  |

| Supply Voltage                                | $V_{DD}$            | Operating                    | 1.5                 | 5     | 7.5                  | V          |  |

| Supply Current                                | I <sub>DD0</sub>    | (Lock protection)            | -                   | 0.5   | 1                    | mA         |  |

| Supply Current                                | I <sub>DD0</sub>    | Operating                    | -                   | 5     | 10                   | mA         |  |

| Input Voltage "H"                             | V <sub>IH</sub>     | -                            | 0.8*V <sub>DD</sub> | -     | V <sub>DD</sub> +0.4 | V          |  |

| Input Voltage "L"                             | V <sub>IL</sub>     | -                            | -0.4                | -     | 0.2*V <sub>DD</sub>  | V          |  |

| Input Current "H"                             | I <sub>IH</sub>     | $V_{IN} = V_{DD}$            | -                   | -     | ±1                   | $\mu A$    |  |

| Input Current "L"                             | IIL                 | $V_{IN} = 0V$                | -                   | -     | ±5                   | mA         |  |

| O1/O2 Output Terminal ( $T_J = 25^{\circ}C$ ) |                     |                              |                     |       |                      |            |  |

| Output Voltage High                           | V <sub>OH</sub>     | I <sub>OUT</sub> = 300 mA    | 4.4                 | -     | -                    | V          |  |

| Output Voltage Low                            | V <sub>OL</sub>     | I <sub>OUT</sub> = 300 mA    | -                   | -     | 0.6                  | V          |  |

| Output Current                                | I <sub>OUT</sub>    | <b>R</b> <sub>L</sub> = 30 Ω | -                   | 148   | -                    | mA         |  |

| FG Open-Drain Terminal (                      | T <sub>J</sub> = 25 | °C)                          |                     |       |                      |            |  |

| Output Leakage Current                        | I <sub>Leak</sub>   | $V_{FG} = 5V$                | -                   | -     | 5                    | μ <b>Α</b> |  |

| Output Current                                | I <sub>FG</sub>     | $V_{FGOL} = 0.4V$            | 6                   | -     | -                    | mA         |  |

| Output Voltage Low                            | $V_{\text{FGOL}}$   | I <sub>FG</sub> = 6 mA       | -                   | -     | 0.4                  | V          |  |

| Automatic Self-Restart Circuit                |                     |                              |                     |       |                      |            |  |

| On Time                                       | T <sub>ON</sub>     | -                            | -                   | 215   | -                    | ms         |  |

| Duty Ratio                                    | $FG_R$              | $T_{OFF}/T_{ON}$             | 6                   | 7     | 8                    |            |  |

#### Electrical Characteristics ( $T_A=25^{\circ}C$ , $V_{DD}=5V$ )

#### **Truth Table**

| HIN              | FGS | PWM | O1  | O2  | FG output<br>Frequency |

|------------------|-----|-----|-----|-----|------------------------|

| н                | (H) | (H) | Н   | L   | FG/2                   |

| L                | (H) | (H) | L   | н   | FG/2                   |

| -                | -   | L   | OFF | OFF | -                      |

| H/L<br>operating | L   | (H) | -   | -   | FG/1                   |

\* The (H) state is pull-high through the internal pull-up resistor in IC.

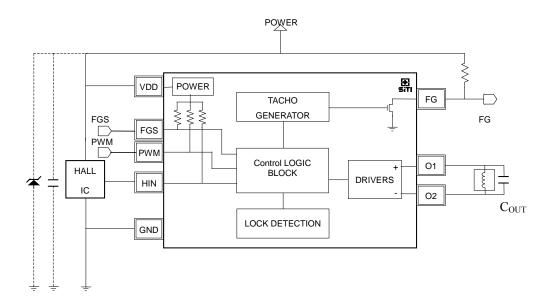

### **Block Diagram & Application Circuit**

#### **Application Notes**

- □ The capacitor  $C_{OUT}$  between output nodes is required for high current application. The capacitor  $C_{OUT}$  is dependent on coil load and external PWM frequency. The recommended capacitor  $C_{OUT}$  is about 0.1µF for external PWM frequency larger than 20KHz and about 1µF for external PWM frequency less than 2KHz.

- □ The output driver node O1/O2 will be "turned to sink/drive" for V(HIN) = logic low. Similarly, the output O1/O2 will be "turned to drive/sink" for V(HIN) = logic high .

- □ The **FG** pin is an open-drained output and the output frequency is dependent on the logical voltage of FGS pin. The output frequency is the same with HIN input signal when V(FGS) is logical low and 1/2 HIN frequency when V(FGS) is logical high. If there is no need for FG output, let FG output pin open.

- The pull-up resistors are built-in at pins HIN, PWM and FGS. For multiple usage of PCB, connecting  $0\Omega$  resistor between the FGS pin and GND will select FG output function or floating  $0\Omega$  resistor will select FG/2 function.

- □ There is no need of external timing capacitor for lock protection and auto-restart function. For 5V application, the drivers will be shut down roughly 1 to 3 seconds after the motor is locked. When the drivers have been shut down, the automatic self-restart circuit will try to power up the drivers every 1 to 3 seconds until lock is released.

- □ The power polarity reverse protection circuit is built-in. The external protection diode for power reverse fault is no need.

- □ There is no requirement of the bypass capacitor or Zener Diode between VDD and GND in normal applications. The connection of this capacitor or Zener Diode between VDD and GND will reduce noise effect and increase stability of operation, if required.

SP-ST1111J-A.005

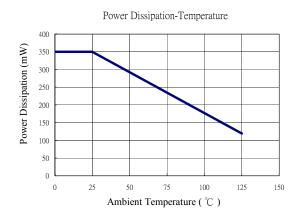

□ The power dissipated by the IC varies widely with the supply voltage, the output current, and loading. It is important to ensure the application does not exceed the allowable power dissipation of the IC package. The recommended motor driver power dissipation versus temperature is depicted as follows:

ST1111J

#### Package

The products listed herein are designed for ordinary electronic applications, such as electrical appliances, audio-visual equipment, communications devices and so on. Hence, it is advisable that the devices should not be used in medical instruments, surgical implants, aerospace machinery, nuclear power control systems, disaster/crime-prevention equipment and the like. Misusing those products may directly or indirectly endanger human life, or cause injury and property loss.

Silicon Touch Technology, Inc. will not take any responsibilities regarding the misusage of the products mentioned above. Anyone who purchases any products described herein with the above-mentioned intention or with such misused applications should accept full responsibility and indemnify. Silicon Touch Technology, Inc. and its distributors and all their officers and employees shall defend jointly and severally against any and all claims and litigation and all damages, cost and expenses associated with such intention and manipulation.

SP-ST1111J-A.005