National Semiconductor

# DP8406 (54F/74F632) 32-Bit Parallel Error Detection and Correction Circuit

## **General Description**

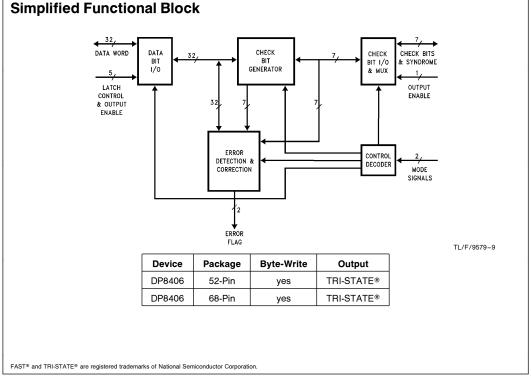

The DP8406 device is a 32-bit parallel error detection and correction circuit (EDAC) in a 52-pin or 68-pin package. The EDAC uses a modified Hamming code to generate a 7-bit check word from a 32-bit data word. This check word is stored along with the data word during the memory write cycle. During the memory read cycle, the 39-bit words from memory are processed by the EDAC to determine if errors have occurred in memory.

Single-bit errors in the 32-bit data word are flagged and corrected.  $\ensuremath{\mathsf{C}}$

Single-bit errors in the 7-bit check word are flagged, and the CPU sends the EDAC through the correction cycle even though the 32-bit data word is not in error. The correction cycle will simply pass along the original 32-bit data word in this case and produce error syndrome bits to pinpoint the error-generating location.

Dual-bit errors are flagged but not corrected. These errors may occur in any two bits of the 39-bit word from memory (two errors in the 32-bit data word, two errors in the 7-bit check word, or one error in each word). The gross-error condition of all LOWs or all HIGHs from memory will be detected. Otherwise, errors in three or more bits of the 39-bit word are beyond the capabilities of these devices to detect.

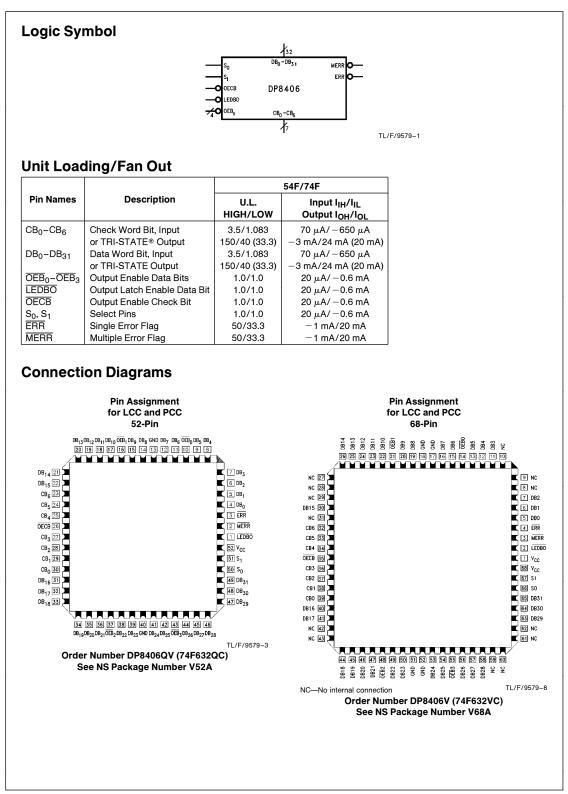

Read-modify-write (byte-control) operations can be performed by using output latch enable,  $\overline{\text{LEDBO}}$ , and the individual  $\overline{\text{OEB}}_0$  through  $\overline{\text{OEB}}_3$  byte control pins.

Diagnostics are performed on the EDACs by controls and internal paths that allow the user to read the contents of the Data Bit and Check Bit input latches. These will determine if the failure occurred in memory or in the EDAC.

#### Features

- Detects and corrects single-bit errors

- Detects and flags dual-bit errors

- Built-in diagnostic capability

- Fast write and read cycle processing times

- Byte-write capability

- Guaranteed 4000V minimum ESD protection

- Fully pin and function compatible with TI's SN74ALS632A thru SN74ALS635 series

© 1995 National Semiconductor Corporation TL/F/9575

RRD-B30M105/Printed in U. S. A

May 1991

Downloaded from  $\underline{\text{Elcodis.com}}$  electronic components distributor

# Connection Diagram (Continued)

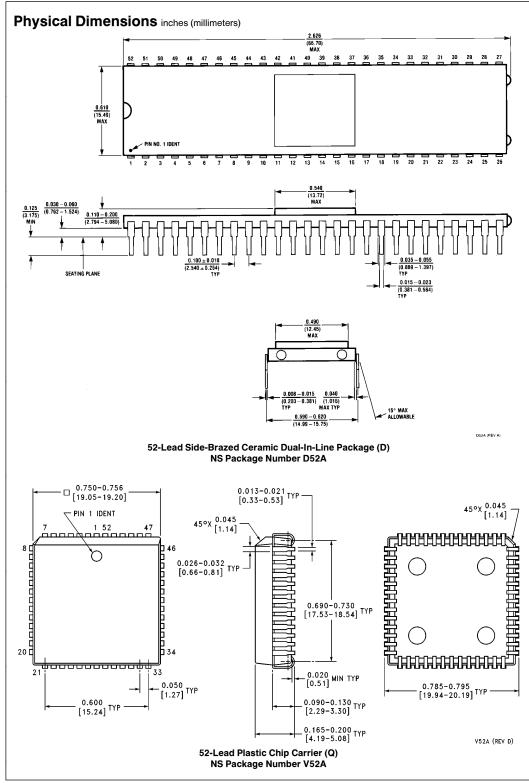

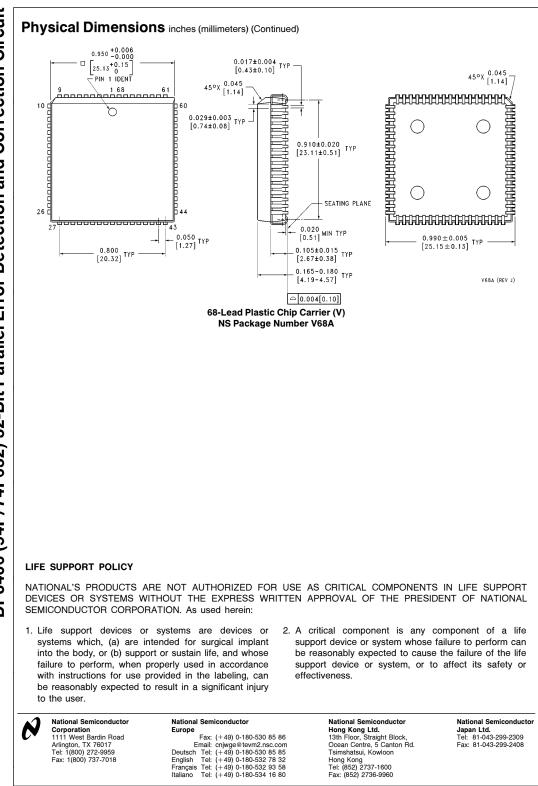

Order Number DP8406D (74F632DC) See NS Package Number D52A

# **Functional Description**

### MEMORY WRITE CYCLE DETAILS

During a memory write cycle, the check bits (CB<sub>0</sub> through CB<sub>6</sub>) are generated internally in the EDAC by seven 16-input parity generators using the 32-bit data word as defined in Table II. These seven check bits are stored in memory along with the original 32-bit data word. This 32-bit word will later be used in the memory read cycle for error detection and correction.

#### ERROR DETECTION AND CORRECTION DETAILS

During a memory read cycle, the 7-bit check word is retrieved along with the actual data. In order to be able to determine whether the data from memory is acceptable to use as presented to the bus, the error flags must be tested to determine if they are at the HIGH level.

The first case in Table III represents the normal, no-error conditions. The EDAC presents HIGHs on both flags. The next two cases of single-bit errors give a HIGH on MERR and a LOW on ERR, which is the signal for a correctable error, and the EDAC should be sent through the correction cycle. The last three cases of double-bit errors will cause the EDAC to signal LOWs on both ERR and MERR, which is the interrupt indication for the CPU.

Error detection is accomplished as the 7-bit check word and the 32-bit data word from memory are applied to internal parity generators/checkers. If the parity of all seven groupings of data and check bits is correct, it is assumed that no error has occurred and both error flags will be HIGH.

# TABLE I. Write Control Function

TL/F/9579-2

| Memory<br>Cycle | EDAC<br>Function       | Cor<br>S <sub>1</sub> | ntrol<br>S <sub>0</sub> | Data I/O | DB Control<br>OEB <sub>n</sub> | DB Output<br>Latch<br>LEDBO | Check I/O            | CB<br>Control<br>OECB | Error<br>ERR | Flags<br>MERR |

|-----------------|------------------------|-----------------------|-------------------------|----------|--------------------------------|-----------------------------|----------------------|-----------------------|--------------|---------------|

| Write           | Generate<br>Check Word | L                     | L                       | Input    | н                              | х                           | Output<br>Check Bit* | L                     | н            | Н             |

\*See Table II for details of check bit generation.

|                 |       |         |        |        |       |        |      |       |        | T/ | BL | E II. | Pari  | ity A | lgo | rithr | n    |      |    |     |    |    |   |   |       |              |    |     |      |    |   |

|-----------------|-------|---------|--------|--------|-------|--------|------|-------|--------|----|----|-------|-------|-------|-----|-------|------|------|----|-----|----|----|---|---|-------|--------------|----|-----|------|----|---|

| heck Word       |       |         |        |        |       |        |      |       |        |    |    |       | 32    | 2-Bit | Dat | a W   | ord  |      |    |     |    |    |   |   |       |              |    |     |      |    |   |

| Bit             | 31    | 30      | 29     | 28     | 27    | 26     | 25   | 24    | 23     | 22 | 21 | 20    | 19    | 18    | 17  | 16    | 15   | 14   | 13 | 12  | 11 | 10 | 9 | 8 | 7     | 6            | 5  | 4   | 3    | 2  | 1 |

| CB <sub>0</sub> | x     |         | Х      | Х      |       | х      |      |       |        |    | х  |       | х     | х     | х   |       |      | х    |    |     | Х  |    | х | х | х     | х            |    | х   |      |    |   |

| CB <sub>1</sub> |       |         |        | х      |       | X      |      | x     |        | х  |    | х     |       | х     | х   | Х     |      |      |    | х   |    | х  |   | х |       | х            |    | х   |      | X  | х |

| CB <sub>2</sub> | x     |         | х      |        |       | x      | х    |       | х      |    |    | х     | х     |       |     | Х     | x    |      | х  |     |    | х  | х |   | х     |              |    | х   | х    |    |   |

| CB <sub>3</sub> |       |         | Х      | Х      | х     |        |      |       | х      | Х  | х  |       |       |       | х   | Х     |      |      | Х  | х   | Х  |    |   |   | х     | х            | х  |     |      |    | Х |

| CB <sub>4</sub> | х     | x       |        |        |       |        |      |       | х      | х  | х  | х     | Х     | х     |     |       | х    | х    |    |     |    |    |   |   | х     | х            | х  | x   | х    | х  |   |

| CB <sub>5</sub> | x     | х       | х      | х      | х     | х      | х    | х     |        |    |    |       |       |       |     |       | х    | х    | Х  | х   | Х  | х  | х | х |       |              |    |     |      |    |   |

| CB <sub>6</sub> | x     | х       | х      | х      | х     | x      | х    | x     |        |    |    |       |       |       |     |       |      |      |    |     |    |    |   |   | х     | х            | x  | x   | x    | X  | х |

| The seven che   | OCK D | its are | e pari | ty Dit | s der | ivea 1 | rom  | the m | latrix |    |    |       | . Eri |       | -   |       |      | τ.   |    |     |    |    |   |   |       |              |    |     |      |    |   |

|                 |       | То      | tal N  | lum    | ber   | of E   | rro  | rs    |        |    |    |       |       |       |     | E     | rror | Flag | js |     |    |    |   |   | Dat   | ta C         | or | rec | ctio | 'n |   |

| 32-Bit I        | Data  | Wo      | rd     |        |       |        | 7-Bi | t Ch  | eck    | Wo | rd |       |       | Ī     | ERR | 1     |      |      | М  | ERR | 1  |    |   |   |       |              |    |     |      |    |   |

|                 | 0     |         |        |        |       |        |      |       | 0      |    |    |       |       |       | н   |       |      |      |    | н   |    |    |   |   |       | t Ap         | •  |     | ole  |    |   |

|                 | 1     |         |        |        |       |        |      |       | 0      |    |    |       |       |       | L   |       |      |      |    | H   |    |    |   |   |       | rec          |    |     |      |    |   |

|                 | 0     |         |        |        |       |        |      |       | 1      |    |    |       |       |       | L   |       |      |      |    | H   |    |    |   |   |       | rrec<br>erru |    | n   |      |    |   |

|                 |       |         |        |        |       |        |      |       |        |    |    |       |       |       | L   |       |      |      |    | L   |    |    |   |   | iiiie |              |    |     |      |    |   |

|                 | 2     |         |        |        |       |        |      |       | 0      |    |    |       |       |       |     |       |      |      |    | 1   |    |    |   |   | Inte  | erru         | nt |     |      |    |   |

L = LOW Voltage Level

If the parity of one or more of the check groups is incorrect, an error has occurred and the proper error flag or flags will be set LOW. Any single error in the 32-bit data word will change the state of either three or five bits of the 7-bit check word. Any single error in the 7-bit check word changes the state of only that one bit. In either case, the single error flag (ERR) will be set LOW while the dual error flag (MERR) will remain HIGH.

Any 2-bit error will change the state of an even number of check bits. The 2-bit error is not correctable since the parity tree can only identify single-bit errors. Both error flags are set LOW when any 2-bit error is detected.

Three or more simultaneous bit errors can cause the EDAC to believe that no error, a correctable error, or an uncorrectable error has occurred and will produce erroneous results in all three cases. It should be noted that the gross-error conditions of all LOWs and all HIGHs will be detected.

As the corrected word is made available on the data I/O port (DB<sub>0</sub> through DB<sub>31</sub>), the check word I/O port (CB<sub>0</sub> through CB<sub>6</sub>) presents a 7-bit syndrome error code. This syndrome error code can be used to locate the bad memory chip. See Table V for syndrome decoding.

#### **READ-MODIFY-WRITE (BYTE CONTROL) OPERATIONS**

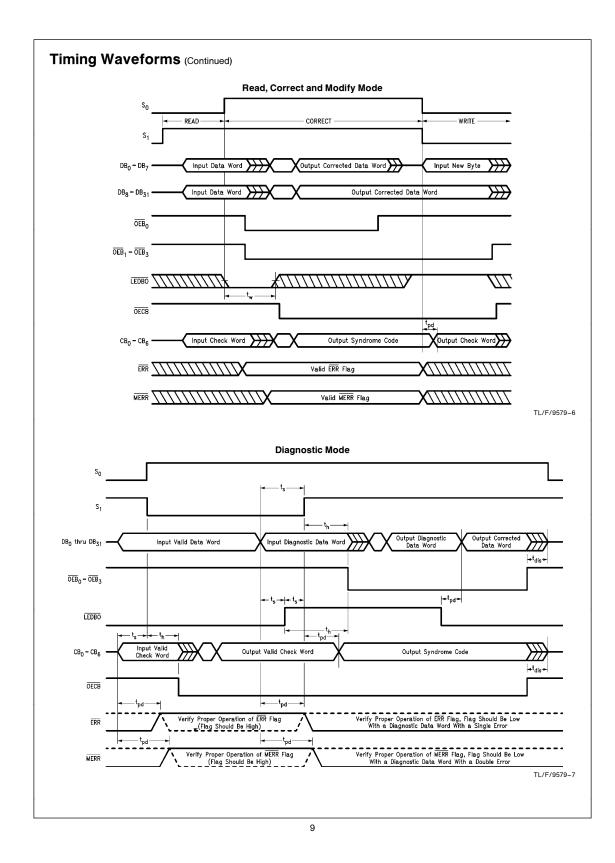

The 'F632 device is capable of byte-write operations. The 39-bit word from memory must first be latched into the Data Bit and Check Bit input latches. This is easily accomplished by switching from the read and flag mode (S<sub>1</sub> = H, S<sub>0</sub> = L) to the latch input mode (S<sub>1</sub> = H, S<sub>0</sub> = H). The EDAC will then make any corrections, if necessary, to the data word and place it at the input of the output data latch. This data word must then be latched into the output data latch by taking LEDBO from a LOW to a HIGH.

Byte control can now be employed on the data word through the  $\overline{OEB_0}$  through  $\overline{OEB_3}$  controls.  $\overline{OEB_0}$  controls  $DB_0-DB_7$  (byte 0),  $\overline{OEB_1}$  controls  $DB_8-DB_{15}$  (byte 1),  $\overline{OEB_2}$  controls  $DB_{16}-DB_{23}$  (byte 2), and  $\overline{OEB_3}$  controls  $DB_{24}-DB_{31}$  (byte 3). Placing a HIGH on the byte control will disable the output and the user can modify the byte. If a LOW is placed on the byte control, then the original byte is allowed to pass onto the data bus unchanged. If the original data word is altered through byte control, a new check word must be generated before it is written back into memory. This is easily accomplished by taking controls  $S_1$  and  $S_0$  LOW. Table VI lists the read-modify-write functions.

#### **DIAGNOSTIC OPERATIONS**

The 'F632 is capable of diagnostics that allow the user to determine whether the EDAC or the memory is failing. The diagnostic function tables will help the user to see the possibilities for diagnostic control. In the diagnostic mode  $(S_1 = L, S_0 = H)$ , the check word is latched into the input latch while the data input latch remains transparent. This lets the user apply various data words against a fixed known check word. If the user applies a diagnostic data word with an error in any bit location, the ERR flag should be LOW. If a diagnostic data word with two errors in any bit location is applied, the MERR flag should be LOW. After the check word is latched into the input latch, it can be verified by taking OECB LOW. This outputs the latched check word. The diagnostic data word can be latched into the output data latch and verified. By changing from the diagnostic mode (S<sub>1</sub> = L, S<sub>0</sub> = H) to the correction mode (S<sub>1</sub> = H, S<sub>0</sub> H), the user can verify that the EDAC will correct the diagnostic data word. Also, the syndrome bits can be produced to verify that the EDAC pinpoints the error location. Table VII lists the diagnostic functions.

| Func            | tional Desci                                | riptic                |                        |                                  | id, Flag and C                 | orrect Functio              | on                                  |                       |                         |

|-----------------|---------------------------------------------|-----------------------|------------------------|----------------------------------|--------------------------------|-----------------------------|-------------------------------------|-----------------------|-------------------------|

| Memory<br>Cycle | EDAC<br>Function                            | Con<br>S <sub>1</sub> | trol<br>S <sub>0</sub> | Data I/O                         | DB Control<br>OEB <sub>n</sub> | DB Output<br>Latch<br>LEDBO | Check I/O                           | CB<br>Control<br>OECB | Error Flags<br>ERR MERR |

| Read            | Read & Flag                                 | н                     | L                      | Input                            | н                              | х                           | Input                               | н                     | Enabled (Note 1)        |

| Read            | Latch Input<br>Data & Check<br>Bits         | Н                     | Н                      | Latched<br>Input<br>Data         | Н                              | L                           | Latched<br>Input<br>Check Word      | н                     | Enabled (Note 1)        |

| Read            | Output<br>Corrected Data<br>& Syndrome Bits | н                     | н                      | Output<br>Corrected<br>Data Word | L                              | х                           | Output<br>Syndrome<br>Bits (Note 2) | L                     | Enabled (Note 1)        |

Note 1: See Table III for error description.

Note 2: See Table V for error location.

#### **TABLE V. Syndrome Decoding**

|             |             | Syne             | drome            | Bits             |                  |                  | Error                                                  |

|-------------|-------------|------------------|------------------|------------------|------------------|------------------|--------------------------------------------------------|

| 6           | 5           | 4                | 3                | 2                | 1                | 0                | Entor                                                  |

| L<br>L<br>L | L<br>L<br>L | L<br>L<br>L      | L<br>L<br>L      | L<br>L<br>L      | L<br>L<br>H<br>H | L<br>H<br>L      | unc<br>2-Bit<br>2-Bit<br>unc                           |

| L<br>L<br>L | L<br>L<br>L | L<br>L<br>L      | L<br>L<br>L      | H<br>H<br>H<br>H | L<br>L<br>H<br>H | L<br>H<br>L<br>H | 2-Bit<br>unc<br>unc<br>2-Bit (Note 2)                  |

| L<br>L<br>L | L<br>L<br>L | L<br>L<br>L      | H<br>H<br>H<br>H | L<br>L<br>L      | L<br>L<br>H<br>H | L<br>H<br>L<br>H | 2-Bit<br>unc<br>DB <sub>31</sub><br>2-Bit              |

| L<br>L<br>L | L<br>L<br>L | L<br>L<br>L      | H<br>H<br>H<br>H | H<br>H<br>H<br>H | L<br>L<br>H<br>H | L<br>H<br>L<br>H | unc<br>2-Bit<br>2-Bit<br>DB <sub>30</sub>              |

| L<br>L<br>L | L<br>L<br>L | H<br>H<br>H      | L<br>L<br>L      | L<br>L<br>L      | L<br>L<br>H<br>H | L<br>H<br>L<br>H | 2-Bit<br>unc<br>DB <sub>29</sub><br>2-Bit              |

| L<br>L<br>L | L<br>L<br>L | H<br>H<br>H      | L<br>L<br>L      | H<br>H<br>H<br>H | L<br>L<br>H<br>H | L<br>H<br>L<br>H | DB <sub>28</sub><br>2-Bit<br>2-Bit<br>DB <sub>27</sub> |

| L<br>L<br>L | L<br>L<br>L | H<br>H<br>H      | H<br>H<br>H<br>H | L<br>L<br>L      | L<br>L<br>H<br>H | L<br>H<br>L<br>H | DB <sub>26</sub><br>2-Bit<br>2-Bit<br>DB <sub>25</sub> |

| L<br>L<br>L | L<br>L<br>L | H<br>H<br>H<br>H | H<br>H<br>H<br>H | H<br>H<br>H<br>H | L<br>L<br>H<br>H | L<br>H<br>L<br>H | 2-Bit<br>DB <sub>24</sub><br>unc<br>2-Bit              |

|             |                  | Syn              | drome            | Bits             |                  |                  | Error                                                |

|-------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------------------------------------------|

| 6           | 5                | 4                | 3                | 2                | 1                | 0                | EIIO                                                 |

| L<br>L<br>L | H<br>H<br>H<br>H | L<br>L<br>L      | L<br>L<br>L      | L<br>L<br>L      | L<br>L<br>H<br>H | L<br>H<br>L<br>H | 2-Bit<br>unc<br>DB <sub>7</sub><br>2-Bit             |

| L<br>L<br>L | H<br>H<br>H<br>H | L<br>L<br>L      | L<br>L<br>L      | H<br>H<br>H<br>H | L<br>L<br>H      | L<br>H<br>L<br>H | DB <sub>6</sub><br>2-Bit<br>2-Bit<br>DB <sub>5</sub> |

| L<br>L<br>L | H<br>H<br>H<br>H | L<br>L<br>L      | H H H H          | L<br>L<br>L      | L<br>L<br>H<br>H | L<br>H<br>L<br>H | DB <sub>4</sub><br>2-Bit<br>2-Bit<br>DB <sub>3</sub> |

| L<br>L<br>L | H<br>H<br>H<br>H | L<br>L<br>L      | H<br>H<br>H<br>H | H<br>H<br>H<br>H | L<br>L<br>H      | L<br>H<br>L<br>H | 2-Bit<br>DB <sub>2</sub><br>unc<br>2-Bit             |

| L<br>L<br>L | H<br>H<br>H<br>H | H<br>H<br>H<br>H | L<br>L<br>L      | L<br>L<br>L      | L<br>L<br>H<br>H | L<br>H<br>L<br>H | DB <sub>0</sub><br>2-Bit<br>2-Bit<br>unc             |

| L<br>L<br>L | ннн              | ΗΗΗ              | L<br>L<br>L      | ннн              | L<br>L<br>H<br>H | L<br>H<br>L<br>H | 2-Bit<br>DB <sub>1</sub><br>unc<br>2-Bit             |

| L<br>L<br>L | H<br>H<br>H<br>H | H H H H          | H H H H          | L<br>L<br>L      | L<br>L<br>H      | L<br>H<br>L<br>H | 2-Bit<br>unc<br>unc<br>2-Bit                         |

| L<br>L<br>L | H<br>H<br>H<br>H | H<br>H<br>H<br>H | H<br>H<br>H<br>H | H<br>H<br>H<br>H | L<br>L<br>H      | L<br>H<br>L<br>H | unc<br>2-bit<br>2-bit<br>CB <sub>6</sub>             |

$\begin{array}{l} CB_X = \mbox{Error in check bit } X \\ DB_Y = \mbox{Error in data bit } Y \\ 2\mbox{-Bit} = \mbox{Double-bit error} \\ \mbox{unc} = \mbox{Uncorrectable multi-bit error} \end{array}$

Note: 2-bit and unc condition will cause both ERR and MERR to be LOW Note 1: Syndrome bits for all LOWs. MERR and ERR LOW for all LOWs, only ERR LOW for DB<sub>30</sub> error. Note 2: Syndrome bits for all HIGHs.

# Functional Description (Continued)

| TABLE V. Syndrome Decod | ding (Continued) |

|-------------------------|------------------|

|-------------------------|------------------|

|                  |             | Syn              | drome            | Bits             |                  |                  | Error                                                  |                  |

|------------------|-------------|------------------|------------------|------------------|------------------|------------------|--------------------------------------------------------|------------------|

| 6                | 5           | 4                | 3                | 2                | 1                | 0                | 20.                                                    | 6                |

| H<br>H<br>H<br>H | L<br>L<br>L | L<br>L<br>L      | L<br>L<br>L      | L<br>L<br>L      | L<br>L<br>H<br>H | L<br>H<br>L<br>H | 2-Bit<br>unc<br>unc<br>2-Bit                           | H<br>H<br>H      |

| H<br>H<br>H<br>H | L<br>L<br>L | L<br>L<br>L      | L<br>L<br>L      | H<br>H<br>H<br>H | L<br>L<br>H<br>H | L<br>H<br>L<br>H | unc<br>2-Bit<br>2-Bit<br>unc                           | H<br>H<br>H      |

| HHHH             | L<br>L<br>L | L<br>L<br>L      | нннн             | L<br>L<br>L      | L<br>L<br>H      | L<br>H<br>L<br>H | unc<br>2-Bit<br>2-Bit<br>DB <sub>15</sub>              | H<br>H<br>H      |

| H<br>H<br>H<br>H | L<br>L<br>L | L<br>L<br>L      | НННН             | НННН             | L<br>L<br>H<br>H | L<br>H<br>L<br>H | 2-Bit<br>unc<br>DB <sub>14</sub><br>2-Bit              | H<br>H<br>H      |

| H<br>H<br>H<br>H | L<br>L<br>L | H<br>H<br>H<br>H | L<br>L<br>L      | L<br>L<br>L      | L<br>L<br>H<br>H | L<br>H<br>L<br>H | unc<br>2-Bit<br>2-Bit<br>DB <sub>13</sub>              | H<br>H<br>H      |

| H<br>H<br>H      | L<br>L<br>L | H<br>H<br>H<br>H | L<br>L<br>L      | H<br>H<br>H      | L<br>L<br>H<br>H | L<br>H<br>L<br>H | 2-Bit<br>DB <sub>12</sub><br>DB <sub>11</sub><br>2-Bit | H<br>H<br>H<br>H |

| H<br>H<br>H<br>H | L<br>L<br>L | H<br>H<br>H<br>H | H<br>H<br>H<br>H | L<br>L<br>L      | L<br>L<br>H<br>H | L<br>H<br>L<br>H | 2-Bit<br>DB <sub>10</sub><br>DB <sub>9</sub><br>2-Bit  | H<br>H<br>H<br>H |

| HHH              | L<br>L<br>L | ΗΗΗ              | ΗΗΗ              | ΗΗΗ              | L<br>L<br>H<br>H | L<br>H<br>L<br>H | DB <sub>8</sub><br>2-Bit<br>2-Bit<br>CB <sub>5</sub>   | H<br>H<br>H<br>H |

|                  |                  | Syn              | drome            | Bits             |                  |                  | Error                                                  |

|------------------|------------------|------------------|------------------|------------------|------------------|------------------|--------------------------------------------------------|

| 6                | 5                | 4                | 3                | 2                | 1                | 0                | 2.1101                                                 |

| エエエ              | H<br>H<br>H<br>H | L<br>L<br>L      | L<br>L<br>L      | L<br>L<br>L      | L<br>L<br>H      | L<br>H<br>L<br>H | unc<br>2-Bit<br>2-Bit<br>DB <sub>23</sub>              |

| H<br>H<br>H<br>H | H<br>H<br>H<br>H | L<br>L<br>L      | L<br>L<br>L      | H<br>H<br>H<br>H | L<br>L<br>H<br>H | L<br>H<br>L<br>H | 2-Bit<br>DB <sub>22</sub><br>DB <sub>21</sub><br>2-Bit |

| エエエエ             | н<br>н<br>н<br>н | L<br>L<br>L      | H<br>H<br>H<br>H | L<br>L<br>L      | L<br>L<br>H<br>H | L<br>H<br>L<br>H | 2-Bit<br>DB <sub>20</sub><br>DB <sub>19</sub><br>2-Bit |

| НННН             | HHHH             | L<br>L<br>L      | H H H H          | НННН             | L<br>L<br>H<br>H | L<br>H<br>L<br>H | DB <sub>18</sub><br>2-Bit<br>2-Bit<br>CB <sub>4</sub>  |

| H<br>H<br>H<br>H | НННН             | H<br>H<br>H<br>H | L<br>L<br>L      | L<br>L<br>L      | L<br>L<br>H<br>H | L<br>H<br>L<br>H | 2-Bit<br>DB <sub>16</sub><br>unc<br>2-Bit              |

| НННН             | НННН             | H<br>H<br>H<br>H | L<br>L<br>L      | НННН             | L<br>L<br>H<br>H | L<br>H<br>L<br>H | DB <sub>17</sub><br>2-Bit<br>2-Bit<br>CB <sub>3</sub>  |

| Н Н Н<br>Н Н     | H<br>H<br>H<br>H | H<br>H<br>H<br>H | H<br>H<br>H<br>H | L<br>L<br>L      | L<br>L<br>H      | L<br>H<br>L<br>H | unc (Note 1)<br>2-Bit<br>2-Bit<br>CB <sub>2</sub>      |

| Н Н Н Н          | H<br>H<br>H<br>H | H<br>H<br>H<br>H | H<br>H<br>H<br>H | H<br>H<br>H<br>H | L<br>L<br>H<br>H | L<br>H<br>L<br>H | 2-Bit<br>CB <sub>1</sub><br>CB <sub>0</sub><br>None    |

$\begin{array}{l} CB_X = Error \mbox{ in check bit } X \\ DB_Y = Error \mbox{ in data bit } Y \\ 2\text{-Bit} = Double-bit \mbox{ error} \\ unc = Uncorrectable \mbox{ multi-bit error} \end{array}$

Note : Syndrome bits for all LOWs. MERR and ERR LOW for all LOWs, only ERR LOW for DB<sub>30</sub> error. Note 2: Syndrome bits for all HIGHs.

6

|                                                             |                                             |                       |                        | ТА                        | ABLE VI                         | . Read            | -Modi | fy-W | rite Funct                | ion                                            |                       |                         |

|-------------------------------------------------------------|---------------------------------------------|-----------------------|------------------------|---------------------------|---------------------------------|-------------------|-------|------|---------------------------|------------------------------------------------|-----------------------|-------------------------|

| Memory<br>Cycle                                             | ED/<br>Func                                 |                       | Co<br>S <sub>1</sub>   | ntrol<br>S <sub>0</sub>   | ВҮТ                             | En*               | OEB   | Īn*  | DB Outp<br>Latch<br>LEDBC | Check I/O                                      | CB<br>Control<br>OECB | Error Flags<br>ERR MERF |

| Read                                                        | Read & F                                    | lag                   | н                      | L                         | Input                           |                   | н     |      | х                         | Input                                          | н                     | Enabled                 |

| Read                                                        | Latch Inp<br>Data &<br>Check B              |                       | н                      | Н                         | Latche<br>Input<br>Data         | əd                | н     |      | L                         | Latched<br>Input<br>Check Word                 | н                     | Enabled                 |

| Read                                                        | Latch Co<br>Data Wo<br>Output L             | rd into               | н                      | н                         | Latche<br>Outpu<br>Data<br>Word |                   | н     |      | Н                         | High Z<br>Output<br>Syndrome<br>Bits           | L                     | Enabled                 |

| Modify/<br>Write                                            | Modify<br>Appropri<br>Byte or E<br>& Genera | Bytes                 | L                      | L                         | Input<br>Modifi<br>BYTE         | 0                 | н     |      | н                         | Output<br>Check Word                           | L                     | нн                      |

| *OFRa cor                                                   | Check W                                     |                       |                        | atrole DBa                | Uncha<br>BYTE                   | 0                 | L     |      | Bro-DBoo (F               | 3YTE <sub>2</sub> ); OEB <sub>3</sub> controls | DBar-DBar (f          |                         |

| 0280 001                                                    |                                             | B7 (B11E0)            | , OEB1 CO              |                           |                                 |                   | -     |      | Function                  |                                                | 0824-0831 (0          | 511E3).                 |

| ED/<br>Func                                                 |                                             | Con<br>S <sub>1</sub> | trol<br>S <sub>0</sub> | Data                      | 1/0                             | DB E<br>Con<br>OE | trol  |      | 3 Output<br>Latch<br>EDBO | Check I/O                                      | CB<br>Control<br>OECB | Error Flags<br>ERR MERF |

| Read & F                                                    | ag                                          | Н                     | L                      | Input C<br>Data W         |                                 | F                 | ł     |      | х                         | Input Correct<br>Check Bits                    | н                     | н                       |

| Latch Inp<br>Word whi<br>Input Lato<br>Remains<br>Transpare | e Data<br>h                                 | L                     | Н                      | Input<br>Diagno<br>Data W |                                 | F                 | ł     |      | L                         | Latched<br>Input<br>Check Bits                 | Н                     | Enabled                 |

| Latch Dia<br>Data Wor<br>Output La                          | d into                                      | L                     | н                      | Input<br>Diagnc<br>Data W |                                 | F                 | ł     |      | Н                         | Output<br>Latched<br>Check Bits                | L                     | Enabled                 |

|                                                             |                                             |                       |                        |                           |                                 |                   |       |      |                           | High Z                                         | н                     |                         |

| Latch Dia<br>Data Wor<br>Input Lato                         | d into                                      | н                     | н                      | Latche<br>Input<br>Diagnc |                                 | F                 | 1     |      | н                         | Output<br>Syndrome<br>Bits                     | L                     | Enabled                 |

| •                                                           |                                             |                       |                        | Data W                    | /ord                            |                   |       |      |                           | High Z                                         | н                     |                         |

| •                                                           | anastia                                     |                       | н                      | Output<br>Diagno          |                                 | L                 |       |      | н                         | Output<br>Syndrome<br>Bits                     | L                     | Enabled                 |

| Output Di<br>Data Wor<br>Syndrome                           | d &                                         | Н                     |                        | -                         | /ord                            |                   | 1     |      |                           |                                                |                       |                         |

| Output Di<br>Data Wor                                       | d &                                         | Н                     |                        | Data W                    | /ord                            |                   |       |      |                           | High Z                                         | н                     |                         |

# Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Storage Temperature                                                                 | -65°C to +150°C          |

|-------------------------------------------------------------------------------------|--------------------------|

| Ambient Temperature under Bias                                                      | -55°C to +125°C          |

| Junction Temperature under Bias                                                     | -55°C to +175°C          |

| V <sub>CC</sub> Pin Potential to<br>Ground Pin                                      | -0.5V to +7.0V           |

| Input Voltage (Note 2)                                                              | -0.5V to +7.0V           |

| Input Current (Note 2)                                                              | -30 mA to $+5.0$ mA      |

| Voltage Applied to Output<br>in HIGH State (with $V_{CC} = 0V$ )<br>Standard Output | -0.5V to V <sub>CC</sub> |

| TRI-STATE Output                                                                    | -0.5V to +5.5V           |

#### Current Applied to Output

in LOW State (Max)

twice the rated  $I_{\mbox{OL}}$  (mA)  $$4000\mbox{V}$$

ESD Last Passing Voltage (Min) 4000V Note 1: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

# Recommended Operating Conditions

####

## **DC Electrical Characteristics**

| Symbol             | Parame                                | ***                                                                                                                                                          |                                        | 54F/74 | F                 | Units | V    | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------|-------------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol             | Parame                                | ter                                                                                                                                                          | Min                                    | Тур    | Мах               | Units | Vcc  | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VIH                | Input HIGH Voltage                    |                                                                                                                                                              | 2.0                                    |        |                   | V     |      | Recognized as a HIGH Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VIL                | Input LOW Voltage                     |                                                                                                                                                              |                                        |        | 0.8               | V     |      | Recognized as a LOW Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| V <sub>CD</sub>    | Input Clamp Diode V                   | 'oltage                                                                                                                                                      |                                        |        | -1.2              | V     | Min  | $I_{IN} = -18 \text{ mA}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>OH</sub>    | Output HIGH<br>Voltage                | 54F 10% V <sub>CC</sub><br>54F 10% V <sub>CC</sub><br>74F 10% V <sub>CC</sub><br>74F 10% V <sub>CC</sub><br>74F 5% V <sub>CC</sub><br>74F 5% V <sub>CC</sub> | 2.5<br>2.4<br>2.5<br>2.4<br>2.7<br>2.7 |        |                   | V     | Min  | $ \begin{split} & I_{OH} = -1 \text{ mA} \left( \overline{\text{ERR}}, \overline{\text{MERR}}, DB_n, CB_n \right) \\ & I_{OH} = -3 \text{ mA} \left( DB_n, CB_n \right) \\ & I_{OH} = -1 \text{ mA} \left( \overline{\text{ERR}}, \overline{\text{MERR}}, DB_n, CB_n \right) \\ & I_{OH} = -3 \text{ mA} \left( DB_n, CB_n \right) \\ & I_{OH} = -1 \text{ mA} \left( \overline{\text{ERR}}, \overline{\text{MERR}}, DB_n, CB_n \right) \\ & I_{OH} = -3 \text{ mA} \left( DB_n, CB_n \right) \end{split} $ |

| V <sub>OL</sub>    | Output LOW<br>Voltage                 | 54F 10% V <sub>CC</sub><br>74F 10% V <sub>CC</sub><br>74F 10% V <sub>CC</sub>                                                                                |                                        |        | 0.5<br>0.5<br>0.5 | v     | Min  | $\begin{split} I_{OL} &= 20 \text{ mA} \left( \overline{\text{ERR}}, \overline{\text{MERR}}, \text{DB}_n, \text{CB}_n \right) \\ I_{OL} &= 20 \text{ mA} \left( \overline{\text{ERR}}, \overline{\text{MERR}} \right) \\ I_{OL} &= 24 \text{ mA} \left( \text{DB}_n, \text{CB}_n \right) \end{split}$                                                                                                                                                                                                       |

| IIH                | Input HIGH<br>Current                 | 54F<br>74F                                                                                                                                                   |                                        |        | 20.0<br>5.0       | μΑ    | Max  | $V_{IN} = 2.7V (S_0, S_1, \overline{OEB}_n, \overline{OECB}, \overline{LEDBO})$                                                                                                                                                                                                                                                                                                                                                                                                                             |

| I <sub>BVI</sub>   | Input HIGH Current<br>Breakdown Test  | 54F<br>74F                                                                                                                                                   |                                        |        | 100<br>7.0        | μΑ    | Max  | $V_{IN} = 7.0V (S_0, S_1, \overline{OEB}_n, \overline{OECB}, \overline{LEDBO})$                                                                                                                                                                                                                                                                                                                                                                                                                             |

| I <sub>BVIT</sub>  | Input HIGH Current<br>Breakdown (I/O) | 54F<br>74F                                                                                                                                                   |                                        |        | 1.0<br>0.5        | mA    | Max  | $V_{IN} = 5.5V (CB_n, DB_n)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ICEX               | Output HIGH<br>Leakage Current        | 54F<br>74F                                                                                                                                                   |                                        |        | 250<br>50         | μΑ    | Max  | $V_{OUT} = V_{CC}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>ID</sub>    | Input Leakage<br>Test                 | 74F                                                                                                                                                          | 4.75                                   |        |                   | v     | 0.0  | $I_{ID} = 1.9 \ \mu A$<br>All Other Pins Grounded                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| I <sub>OD</sub>    | Output Leakage<br>Circuit Current     | 74F                                                                                                                                                          |                                        |        | 3.75              | μΑ    | 0.0  | $V_{IOD} = 150 \text{ mV}$<br>All Other Pins Grounded                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| IIL                | Input LOW Current                     |                                                                                                                                                              |                                        |        | -0.6              | mA    | Max  | $V_{IN} = 0.5V (S_0, S_1, \overline{OEB}_n, \overline{OECB}, \overline{LEDBO})$                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $I_{IH} + I_{OZH}$ | Output Leakage Cur                    | rent                                                                                                                                                         |                                        |        | 70                | μΑ    | Max  | $V_{I/O} = 2.7V (CB_n, DB_n)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $I_{IL} + I_{OZL}$ | Output Leakage Cur                    | rent                                                                                                                                                         |                                        |        | -650              | μΑ    | Max  | $V_{I/O} = 0.5V (CB_n, DB_n)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I <sub>OZH</sub>   | Output Leakage Cur                    | rent                                                                                                                                                         |                                        |        | 70                | μΑ    | Max  | $V_{I/O} = 2.7V (CB_n, DB_n)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I <sub>OZL</sub>   | Output Leakage Cur                    | rent                                                                                                                                                         |                                        |        | -650              | μΑ    | Max  | $V_{I/O} = 0.5V (CB_n, DB_n)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I <sub>OS</sub>    | Output Short-Circuit                  | Current                                                                                                                                                      | -60                                    |        | -150              | mA    | Max  | $V_{OUT} = 0V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| I <sub>ZZ</sub>    | Bus Drainage Test                     |                                                                                                                                                              |                                        |        | 500               | μΑ    | 0.0V | $V_{OUT} = 5.25V (CB_n, DB_n)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| I <sub>CC</sub>    | Power Supply Currer                   | nt                                                                                                                                                           |                                        |        | 340               | mA    | Max  | $T_{A} = 0^{\circ}C - 25^{\circ}C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ICC                | Power Supply Currer                   | nt                                                                                                                                                           |                                        |        | 325               | mA    | Max  | $T_{A} = 25^{\circ}C - 70^{\circ}C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PHL DB or CB to ERR 4.0 10.5 18.0 4.0 20.0   PLH Propagation Delay<br>DB to ERR 4.0 21.0 27.0 4.0 31.0   PHL DB or CB to ERR 4.0 14.0 18.0 4.0 20.0   PLH Propagation Delay<br>PHL 5.0 17.0 27.0 5.0 31.0   PHL DB or CB to MERR 5.0 16.0 27.0 5.0 31.0   PHL DB to MERR 5.0 23.0 27.0 5.0 31.0   PHL DB to MERR 5.0 12.0 16.0 4.0 20.0   PLH Propagation Delay<br>S <sub>0</sub> and S <sub>1</sub> , LOW, to DB 4.0 12.0 16.0 4.0 20.0   PLH Propagation Delay<br>S <sub>0</sub> or S <sub>1</sub> to ERR or MERR 2.0 11.5 13.0 4.0 15.0   PLH Propagation Delay<br>S <sub>0</sub> or S <sub>1</sub> to ERR or MERR 2.0 11.0 13.0 2.0 14.0   PHL Degation Delay<br>S <sub>0</sub> or S <sub>1</sub> to ERR or MERR 2.0 11.0                                                                                                                                                                                                                                                                                                                                                                        | Unit                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| PLH Propagation Delay 4.0 14.0 27.0 4.0 31.0   PHL DB or CB to ERR 4.0 10.5 18.0 4.0 20.0   PLH Propagation Delay 4.0 21.0 27.0 4.0 31.0   PHL DB to ERR 4.0 14.0 18.0 4.0 20.0   PLH Propagation Delay 5.0 17.0 27.0 5.0 31.0   PLH Propagation Delay 5.0 17.0 27.0 5.0 31.0   PLH Propagation Delay 5.0 23.0 27.0 5.0 31.0   PLH Propagation Delay 5.0 19.0 27.0 5.0 31.0   PHL So and S1, LOW, to DB 4.0 12.0 16.0 4.0 20.0   PHL Propagation Delay 4.0 10.5 14.0 4.0 15.0   PHL So and S1, LOW, to DB 4.0 10.5 14.0 4.0 15.0   PHL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ns<br>ns<br>ns<br>ns |

| PHL<br>PHLDB or CB to ERR4.010.518.04.020.0 $P_{PHL}$ Propagation Delay<br>DB to ERR4.021.027.0<br>4.04.031.0<br>4.0 $P_{PHL}$ DB to ERR5.017.027.0<br>27.05.031.0<br>5.0 $P_{PHL}$ Propagation Delay<br>DB or CB to MERR5.017.027.0<br>5.05.031.0<br>5.0 $P_{PHL}$ Propagation Delay<br>DB to MERR5.023.027.0<br>27.05.031.0<br>5.0 $P_{PLL}$ Propagation Delay<br>DB to MERR5.012.016.0<br>27.04.020.0 $P_{PLL}$ Propagation Delay<br>S_0 and S1, LOW, to DB4.012.016.0<br>4.04.020.0 $P_{PLL}$ Propagation Delay<br>S_0 and S1, LOW, to DB4.010.514.0<br>4.04.020.0 $P_{PLL}$ Propagation Delay<br>S_0 or S1 to ERR or MERR2.011.513.02.014.0 $P_{PLH}$ Propagation Delay<br>S_0 or S1 to ERR or MERR2.011.513.02.014.0 $P_{PLL}$ Propagation Delay<br>S_0 or S1 to ERR or MERR2.011.013.02.014.0 $P_{PLL}$ Propagation Delay<br>S_0 or S1 to ERR or MERR2.011.013.02.014.0 $P_{PLL}$ Propagation Delay<br>DB to CB2.011.013.02.014.0 $P_{PLL}$ Propagation Delay<br>LEDB to DB2.011.010.010.0 $P_{PLL}$ Output Enable Time<br>OEB_n to DB1.0 <t< th=""><th>ns<br/>ns<br/>ns<br>ns</br></th></t<> | ns<br>ns<br>ns<br>   |

| PHL DB to ERR 4.0 14.0 18.0 4.0 20.0   PPLL Propagation Delay 5.0 17.0 27.0 5.0 31.0   PHL DB or CB to MERR 5.0 16.0 27.0 5.0 31.0   PHL Propagation Delay 5.0 23.0 27.0 5.0 31.0   PHL DB to MERR 5.0 19.0 27.0 5.0 31.0   PHL DB to MERR 5.0 19.0 27.0 5.0 31.0   PHL Propagation Delay 4.0 12.0 16.0 4.0 20.0   PHL So and S1, LOW, to DB 4.0 10.5 14.0 4.0 20.0   PHL Propagation Delay 4.0 10.5 14.0 4.0 15.0   PHL Propagation Delay 2.0 11.5 13.0 2.0 14.0   PLH Propagation Delay 4.0 16.0 23.0 4.0 25.0   PHL DB to C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ns<br>ns<br>ns       |

| DB or CB to MERR 5.0 16.0 27.0 5.0 31.0   PLH Propagation Delay<br>DB to MERR 5.0 23.0 27.0 5.0 31.0   PHL DB to MERR 5.0 19.0 27.0 5.0 31.0   PHL DB to MERR 5.0 19.0 27.0 5.0 31.0   PLH Propagation Delay<br>PHL 4.0 12.0 16.0 4.0 20.0   PLH Propagation Delay<br>PHL 4.0 10.5 14.0 4.0 15.0   PLH Propagation Delay<br>S1 to CB 4.0 9.0 14.0 4.0 15.0   PLH Propagation Delay<br>S_0 or S_1 to ERR or MERR 2.0 11.5 13.0 2.0 14.0   PLH Propagation Delay<br>S_0 or S_1 to ERR or MERR 2.0 11.0 13.0 2.0 14.0   PHL DB to CB 4.0 16.0 23.0 4.0 25.0   PHL Propagation Delay<br>PHL 2.0 11.0 13.0 2.0 14.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ns                   |

| PHL DB to MERR 5.0 19.0 27.0 5.0 31.0   PLH Propagation Delay 4.0 12.0 16.0 4.0 20.0   PHL S_0 and S_1, LOW, to DB 4.0 12.0 16.0 4.0 20.0   PLH Propagation Delay 4.0 10.5 14.0 4.0 15.0   PLH Propagation Delay 4.0 10.5 14.0 4.0 15.0   PLH Propagation Delay 4.0 10.5 14.0 4.0 15.0   PLH Propagation Delay 2.0 11.5 13.0 2.0 14.0   PLH Propagation Delay 4.0 16.0 23.0 4.0 25.0   PHL DB to CB 4.0 18.0 23.0 4.0 25.0   PHL Propagation Delay 2.0 11.0 13.0 2.0 14.0   PHL EEDBO to DB 2.0 11.0 13.0 2.0 14.0   PZH Outpu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ns                   |

| PHL S <sub>0</sub> and S <sub>1</sub> , LOW, to DB 4.0 12.0 16.0 4.0 20.0   PLH Propagation Delay 4.0 10.5 14.0 4.0 15.0   PHL S <sub>1</sub> to CB 4.0 9.0 14.0 4.0 15.0   PLH Propagation Delay 4.0 9.0 14.0 4.0 15.0   PLH Propagation Delay 2.0 11.5 13.0 2.0 14.0   PLH Propagation Delay 4.0 16.0 23.0 4.0 25.0   PHL DB to CB 4.0 18.0 23.0 4.0 25.0   PHL EEDB to DB 2.0 11.0 13.0 2.0 14.0   PHL LEDB to DB 2.0 11.0 13.0 2.0 14.0   PZH Output Enable Time 1.0 6.0 10.0 1.0 10.0   PZL Output Disable Time 1.0 5.0 10.0 1.0 10.0   PZL Output Enabl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |

| PLH Propagation Delay 4.0 10.5 14.0 4.0 15.0   PHL S <sub>1</sub> to CB 4.0 9.0 14.0 4.0 15.0   PLH Propagation Delay 2.0 11.5 13.0 2.0 14.0   PLH Propagation Delay 2.0 11.5 13.0 2.0 14.0   PLH Propagation Delay 4.0 16.0 23.0 4.0 25.0   PHL DB to CB 4.0 18.0 23.0 4.0 25.0   PHL Propagation Delay 2.0 11.0 13.0 2.0 14.0   PHL DB to CB 2.0 11.0 13.0 2.0 14.0   PHL LEDBO to DB 2.0 11.0 13.0 2.0 14.0   PZH Output Enable Time 1.0 6.0 10.0 1.0 10.0   PZL OLEB <sub>n</sub> to DB 1.0 5.0 10.0 1.0 10.0   PLT Output Disable Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ns                   |

| PLH Propagation Delay<br>S <sub>0</sub> or S <sub>1</sub> to ERR or MERR 2.0 11.5 13.0 2.0 14.0   PLH Propagation Delay<br>DB to CB 4.0 16.0 23.0 4.0 25.0   PHL Propagation Delay<br>DB to CB 4.0 18.0 23.0 4.0 25.0   PLH Propagation Delay<br>DB to CB 2.0 11.0 13.0 2.0 14.0   PHL Propagation Delay<br>LEDBO to DB 2.0 11.0 13.0 2.0 14.0   PHL LEDBO to DB 2.0 11.0 13.0 2.0 14.0   PHL LEDBO to DB 2.0 11.0 13.0 2.0 14.0   PZH Output Enable Time 1.0 6.0 10.0 1.0 10.0   PHZ Output Disable Time 10 5.0 10.0 1.0 10.0   PLZ OEB <sub>n</sub> to DB 1.0 4.0 10.0 1.0 10.0   PZH Output Enable Time 1.0 6.0 10.0 1.0 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      |

| PLH<br>PHL Propagation Delay<br>DB to CB 4.0 16.0 23.0 4.0 25.0   PHL DB to CB 4.0 18.0 23.0 4.0 25.0   PLH Propagation Delay<br>LEDBO to DB 2.0 11.0 13.0 2.0 14.0   PHL Propagation Delay<br>LEDBO to DB 2.0 11.0 13.0 2.0 14.0   PZH Output Enable Time 1.0 6.0 10.0 1.0 10.0   PHZ Output Disable Time 10 5.0 10.0 1.0 10.0   PLZ OEB <sub>n</sub> to DB 1.0 4.0 10.0 1.0 10.0   PLZ Output Enable Time 10 5.0 10.0 1.0 10.0   PZH Output Enable Time 1.0 4.0 10.0 1.0 10.0   PLZ Output Enable Time 1.0 6.0 10.0 1.0 10.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ns                   |

| PLH<br>PPLL Propagation Delay<br>LEDBO to DB 2.0 11.0 13.0 2.0 14.0   PZH<br>PZL Output Enable Time<br>OEB <sub>n</sub> to DB 1.0 6.0 10.0 1.0 10.0   PZL Output Enable Time<br>OEB <sub>n</sub> to DB 1.0 6.0 10.0 1.0 10.0   PHZ Output Disable Time<br>OEB <sub>n</sub> to DB 10 5.0 10.0 1.0 10.0   PHZ Output Enable Time<br>OEB <sub>n</sub> to DB 1.0 4.0 10.0 1.0 10.0   PZH Output Enable Time 1.0 6.0 10.0 1.0 10.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ns                   |

| Difference Output Enable Time 1.0 6.0 10.0 1.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0 10.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ns                   |

| Dutput Disable Time 10 5.0 10.0 1.0 10.0   PLZ Output Disable Time 10 4.0 10.0 1.0 10.0   PZH Output Enable Time 1.0 6.0 10.0 1.0 10.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ns                   |

| PZH Output Enable Time 1.0 6.0 10.0 1.0 1.0 10.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ns                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ns                   |

| PHZ Output Disable Time 1.0 5.0 10.0 1.0 10.0   PLZ OECB to CB 1.0 4.0 10.0 1.0 10.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |

| Symbol                       | Parameter                                                                                                                                                                                                 | 74F                                    |       | 54F                                                                                                                                                                                                                                            | 74F                                    |       |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------|

|                              |                                                                                                                                                                                                           | $T_A = +25^{\circ}$<br>$V_{CC} = +5.0$ |       | , V <sub>CC</sub> = Mil                                                                                                                                                                                                                        | T <sub>A</sub> , V <sub>CC</sub> = Com | Uni   |

|                              |                                                                                                                                                                                                           |                                        | ax Mi | n Max                                                                                                                                                                                                                                          | Min Max                                | -     |

| s                            | Setup Time, HIGH or LOW<br>DB/CB before S <sub>0</sub> HIGH (S <sub>1</sub> HIGH)                                                                                                                         | 3.0                                    |       |                                                                                                                                                                                                                                                | 3.0                                    | ns    |

| <sub>s</sub> (H)             | Setup Time, HIGH<br>S <sub>0</sub> HIGH before LEDBO HIGH                                                                                                                                                 | 12.0                                   |       |                                                                                                                                                                                                                                                | 14.0                                   | ns    |

| s(H)                         | $\frac{\text{Setup Time, HIGH}}{\text{LEDBO HIGH before S}_0 \text{ or S}_1 \text{ LOW}}$                                                                                                                 | 0                                      |       |                                                                                                                                                                                                                                                | 0                                      | n     |

| s(H)                         | Setup Time, HIGH<br>LEDBO HIGH before S <sub>1</sub> HIGH                                                                                                                                                 | 0                                      |       |                                                                                                                                                                                                                                                | 0                                      | ns    |

| s                            | Setup Time, HIGH or LOW<br>Diagnostic DB before S <sub>1</sub> HIGH                                                                                                                                       | 0                                      |       |                                                                                                                                                                                                                                                | 0                                      | n     |

| s                            | Setup Time, HIGH or LOW<br>Diagnostic CB before<br>S <sub>1</sub> LOW or S <sub>0</sub> HIGH                                                                                                              | 3.0                                    |       |                                                                                                                                                                                                                                                | 3.0                                    | n     |

| s                            | Setup Time, HIGH or LOW<br>Diagnostic DB before<br>LEDBO HIGH (S <sub>1</sub> LOW, S <sub>0</sub> HIGH)                                                                                                   | 8.0                                    |       |                                                                                                                                                                                                                                                | 8.0                                    | n     |

| t <sub>h</sub> (L)           | Hold Time, LOW<br>S <sub>0</sub> LOW after S <sub>1</sub> HIGH                                                                                                                                            | 8.0                                    |       |                                                                                                                                                                                                                                                | 8.0                                    | n     |