# ATOM Family

BM-ATOM1.0-V1.6

# Brief Manual of ATOM1.0 Family

# 4-bit Microcontrollers with Reduced 8051 Architecture

V1.6 July 2008

- CORERIVER Semiconductor reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time.

- CORERIVER shall give customers at least a three month advance notice of intended discontinuation of a product or a service through its homepage.

- Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.

- The CORERIVER products listed in this document are intended for usage in general electronics applications. These CORERIVER products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury.

www.coreriver.com (E-mail: tech@coreriver.com)

### **Contents**

### **Preliminary**

- 1. Product Overview

- 2. Features

- 3. Block Diagram

- 4. Pin Configurations

- 5. Pin Descriptions

- 6. Function Descriptions

- CPU Descriptions

- Memory Organization

- SFR Map and Description

- Instruction Set Summary

- CPU Timing

- Peripheral Descriptions

- I/O Ports

- Clock Configuration

- Carrier Frequency Generation

- LVD (Low Voltage Detector)

- WDT (Watchdog Timer)

- Reset Circuit

- Power Management

- IAP (In Application Programming)

- 7. Absolute Maximum Ratings

- 8. DC Characteristics

- 9. AC Characteristics

- 10. Package Dimensions

- 11. Product Numbering System

- 12. Supporting Tools

#### 13. Appendix

- A. Instruction Set

- **B.** SFR Descriptions

- C. Update History

### 1. Product Overview (1/2)

**Preliminary**

#### ◆ ATOM1.0 Family - GC49C501 Series (Low Cost, Low Power Application MCU)

| Product          | Mask-ROM<br>(byte) | FLASH<br>(byte) | EEPROM<br>(byte) | RAM<br>(Nibble) | Volt<br>(V) | Freq.<br>(MHz) | T/C<br>(16bits) | Serial<br>I/O | WDT | REM<br>Output | IR. LED<br>Drive Tr. | I/O<br>Pins | Package             | Others                                       | Available<br>Time |

|------------------|--------------------|-----------------|------------------|-----------------|-------------|----------------|-----------------|---------------|-----|---------------|----------------------|-------------|---------------------|----------------------------------------------|-------------------|

| GC49C501G0-SO24I | -                  | 1K              | (128)            | 64              | 1.8~5.5     | 10<br>(5)      | -               | -             | 1   | 1             | Yes                  | 18<br>(20)  | 24-SOIC             | POR/LVD<br>Ring OSC<br>ISP/IAP               | NOW               |

| GC49C501G0-SO20I | -                  | 1K              | (128)            | 64              | 1.8~5.5     | 10<br>(5)      | -               | -             | 1   | 1             | Yes                  | 14<br>(16)  | 20-SOIC<br>(Narrow) | POR/LVD<br>Ring OSC<br>ISP/IAP               | NOW               |

| GC49C501G0-SJ20I | -                  | 1K              | (128)            | 64              | 1.8~5.5     | 10<br>(5)      | -               | -             | 1   | 1             | Yes                  | 14<br>(16)  | 20-SOIC<br>(JEDEC)  | POR/LVD<br>Ring OSC<br>ISP/IAP               | NOW               |

| GC49C501R0-SO24I | -                  | 1K              | (128)            | 64              | 1.8~5.5     | 10<br>(5)      | -               | -             | 1   | 1             | Yes                  | 18<br>(20)  | 24-SOIC             | POR/LVD<br>Calibrated<br>Ring OSC<br>ISP/IAP | NOW               |

| GC49C501R0-SO20I | -                  | 1K              | (128)            | 64              | 1.8~5.5     | 10<br>(5)      | -               | -             | 1   | 1             | Yes                  | 14<br>(16)  | 20-SOIC<br>(Narrow) | POR/LVD<br>Calibrated<br>Ring OSC<br>ISP/IAP | NOW               |

| GC49C501R0-SJ20I | -                  | 1K              | (128)            | 64              | 1.8~5.5     | 10<br>(5)      | -               | -             | 1   | 1             | Yes                  | 14<br>(16)  | 220-SOIC<br>(JEDEC) | POR/LVD<br>Calibrated<br>Ring OSC<br>ISP/IAP | NOW               |

| GC49C501RP-SO8I  | -                  | 1K              | (128)            | 64              | 1.8~5.5     | 10<br>(5)      | -               | -             | 1   | -             | -                    | 6           | 8-SOIC              | POR/LVD<br>Calibrated<br>Ring OSC<br>ISP/IAP | NOW               |

| GC49C501RP-SP8I  | -                  | 1K              | (128)            | 64              | 1.8~5.5     | 10<br>(5)      | -               | -             | 1   | -             | -                    | 6           | 8-SPDIP             | POR/LVD<br>Calibrated<br>Ring OSC<br>ISP/IAP | NOW               |

<sup>\*</sup> User may use part of program area (128 bytes) as EEPROM, which can be modified by IAP function during S/W operation.

$<sup>^{*}</sup>$  Max. operating frequency of ATOM1.0 family is 5 MHz when VDD is less than 2.7 V.

ATOM1.0 Family

[3]

# 1. Product Overview (2/2)

**Preliminary**

#### ◆ ATOM1.0 Family - GC49C501 Series (Low Cost, Low Power Application MCU)

| Product          | Mask-ROM<br>(byte) | FLASH<br>(byte) | EEPROM<br>(byte) | RAM<br>(Nibble) | Volt<br>(V) | Freq.<br>(MHz) | T/C<br>(16bits) | Serial<br>I/O | WDT | REM<br>Output | IR. LED<br>Drive Tr. | I/O<br>Pins | Package             | Others              | Available<br>Time |

|------------------|--------------------|-----------------|------------------|-----------------|-------------|----------------|-----------------|---------------|-----|---------------|----------------------|-------------|---------------------|---------------------|-------------------|

| GC41C501G0-SO24I | 1K                 | -               | -                | 64              | 1.8~5.5     | 10<br>(5)      | -               | -             | 1   | 1             | Yes                  | 18<br>(20)  | 24-SOIC             | POR/LVD<br>Ring OSC | NOW               |

| GC41C501G0-SO20I | 1K                 | -               | -                | 64              | 1.8~5.5     | 10<br>(5)      | -               | -             | 1   | 1             | Yes                  | 14<br>(16)  | 20-SOIC<br>(Narrow) | POR/LVD<br>Ring OSC | NOW               |

| GC41C501G0-SJ20I | 1K                 | -               | -                | 64              | 1.8~5.5     | 10<br>(5)      | 1               | -             | 1   | 1             | Yes                  | 14<br>(16)  | 20-SOIC<br>(JEDEC)  | POR/LVD<br>Ring OSC | NOW               |

| GC41C501G0-SO8I  | 1K                 | -               | -                | 64              | 1.8~5.5     | 10<br>(5)      | 1               | -             | 1   | 1             | -                    | 6           | 8-SOIC              | POR/LVD<br>Ring OSC | NOW               |

| GC41C501G0-SP8I  | 1K                 | -               | -                | 64              | 1.8~5.5     | 10<br>(5)      | -               | -             | 1   | ı             | -                    | 6           | 8-SPDIP             | POR/LVD<br>Ring OSC | NOW               |

<sup>\*</sup> Max. operating frequency of ATOM1.0 family is 5 MHz when VDD is less than 2.7 V.

ATOM1.0 Family

[4]

$<sup>^{*}</sup>$  User may use part of program area (128 bytes) as EEPROM, which can be modified by IAP function during S/W operation.

#### 2. Features

### **Preliminary**

- CPU

- √ 4-bit reduced 8051 architecture

- Continuous program addressing, not paged.

- √ 51 instructions including push, pop and logic inst.

- ✓ Instruction cycle : F<sub>sys</sub>/6

- Multi-level subroutine nesting with RAM based stack.

- On-chip Memories

- ✓ FLASH: 1024 bytes (including 128 EEPROM)

- ✓ RAM: 64 nibbles (including stack)

- ISP (In System Programming) of FLASH

- IAP (In Application Programming) of FLASH

- I/O Ports

- ✓ P0 : 4-bit parallel I/O (Open drain output)

- ✓ P1 : Parallel I/O (Open drain output), 4-bit for 24-pin, 2-bit for 20-pin.

- ✓ P2, P3 : 4-bit parallel/bit-selectable I/O (Open drain output)

- ✓ P4 : Parallel I/O (Open drain output).

Two bits if internal clock is used.

Additional two bits for 24-pin packages.

- REM output (Remote control transmitter)

- ✓ Built-in Transistor for I.R. LED Drive

- $\checkmark$  I<sub>OI</sub> = 300 mA (Max.) at V<sub>DD</sub> = 3V and V<sub>O</sub> = 0.4V

- Carrier Pulse Generation: 7 types

- Built-in Oscillator

- ✓ Crystal/Ceramic resonator

- Precision internal oscillator

Factory Calibrated to  $\pm$  3% at 2.1  $\sim$  3.3V Factory Calibrated to  $\pm$  1% at 2.5V

- √ The Factory Calibration for 7.28MHz is applied only for GC49C501RX devices.

- Built-in Reset

- ✓ Power-on Reset, Power-fail Reset

- ✓ WDT (Watch-Dog Timer) Reset

- Clock switching reset

- Power Management

- ✓ Power-down (stop) mode

- ✓ Release stop by input changes

- Sleep mode

### 2. Features

**Preliminary**

- Power Consumption

- $\checkmark$  Stop mode : < 0.1uA (Typ.) at 2.0V

- 1 uA (Max.) at 5.0V

- $\checkmark$  Normal mode : 400 uA (Typ.) at 2.0V,  $F_{SYS} = 4$  MHz

- Operating frequency vs. voltage

- $\checkmark$  Max. F<sub>OSC</sub>= 10 MHz (2.7 V  $\le$  V<sub>DD</sub>  $\le$  5.5V)

- $\checkmark$  Max.  $F_{OSC}$ = 5 MHz (1.8 V  $\le$  V<sub>DD</sub> < 2.7V)

- ◆ Operating temperature : -20 °C ~ 85 °C

- ESD protection up to 2,000V

- Latch-up protection up to ±200mA

- Package

- ✓ 24-pin SOIC

- √ 20-pin SOIC

- √ 8-pin SOIC/SPDIP

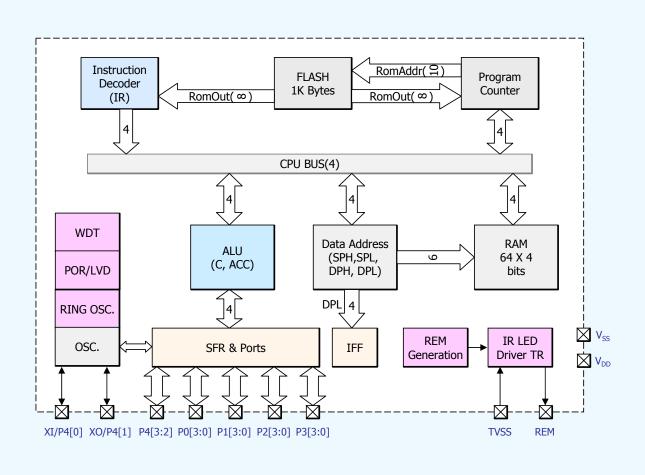

# 3. Block Diagram (24-PIN)

**Preliminary**

ATOM1.0 Family

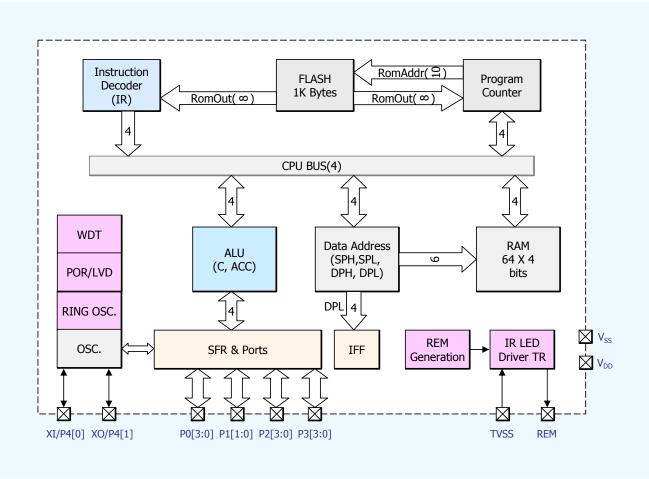

# 3. Block Diagram (20-PIN)

**Preliminary**

ATOM1.0 Family

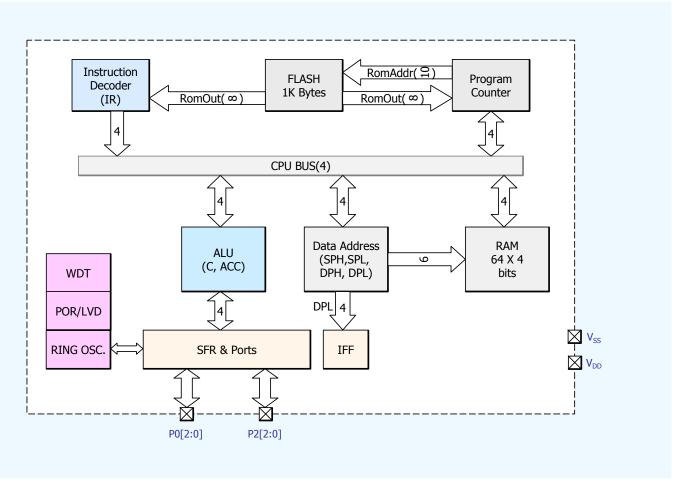

# 3. Block Diagram (8-PIN)

**Preliminary**

ATOM1.0 Family

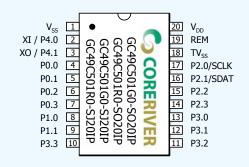

### 4. Pin Configurations

### **Preliminary**

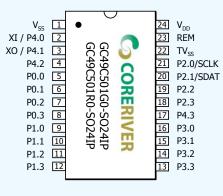

[ 20-SOIC]

GC49C501G0-SO20I

GC49C501R0-SO20I

GC49C501G0-SJ20I

GC49C501R0-SJ20I

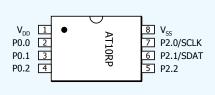

[ 8-SOIC/SPDIP] GC49C501RP-SO8I GC49C501RP-SP8I

[ 24-SOIC] GC49C501G0-SO24I GC49C501R0-SO24I

ATOM1.0 Family

[10]

# 5. Pin Description (20-pin/24-pin)

| Symbol           | Direction    | Description                                                                                                                                                                                                                                            | Remark |

|------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| $V_{DD}$         | Power        | Power Supply                                                                                                                                                                                                                                           |        |

| $V_{SS}$         | Power        | Ground                                                                                                                                                                                                                                                 |        |

| REM              | Output       | Output for IR LED drive Transistor. The transistor is n-channel device.                                                                                                                                                                                |        |

| TV <sub>SS</sub> | Power        | Ground for IR LED drive Transistor                                                                                                                                                                                                                     |        |

| XI / P4[0]       | Input/Output | Input to the inverting oscillator amplifier. If configured, P4[0] of parallel Input/Output port. Schmitt Trigger input and open-drain output with internal pull-up TR.                                                                                 |        |

| XO / P4[1]       | Input/Output | Output from the inverting oscillator amplifier. If configured, P4[1] of parallel Input/Output port. Schmitt Trigger input and open-drain output with internal pull-up TR.                                                                              |        |

| P4[3:2]          | Input/Output | Parallel Input/Output port (Only for 24-pin packages) Each bit can be individually set or cleared. Schmitt Trigger input and open-drain output with internal pull-up TR.                                                                               |        |

| P0[3:0]          | Input/Output | Parallel Input/Output port.<br>Schmitt Trigger input and open-drain output with internal pull-up TR.<br>The STOP mode is released by "L" input of each pin.                                                                                            |        |

| P1[1:0]          | Input/Output | Parallel Input/Output port.<br>Schmitt Trigger input and open-drain output with internal pull-up TR.<br>The STOP mode is released by "L" input of each pin.                                                                                            |        |

| P1[3:2]          | Input/Output | Parallel Input/Output port (Only for 24-pin packages) Schmitt Trigger input and open-drain output with internal pull-up TR. The STOP mode is released by "L" input of each pin.                                                                        |        |

| P2[3:0]          | Input/Output | Parallel Input/Output port. Each bit can be individually set or cleared. Schmitt Trigger input and open-drain output with internal pull-up TR. P2 can be configured as a push-pull output port. P2[0] and P2[1] are also used for ISP of FLASH memory. |        |

| P3[3:0]          | Input/Output | Parallel Input/Output port. Each bit can be individually set or cleared.<br>Schmitt Trigger input and open-drain output with internal pull-up TR.                                                                                                      |        |

ATOM1.0 Family

[11]

# 5. Pin Description (8-pin)

| Symbol          | Direction                                                                | Description                                                                                                                                           | Remark |

|-----------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| $V_{DD}$        | Power                                                                    | Power Supply                                                                                                                                          |        |

| V <sub>SS</sub> | Power                                                                    | Ground                                                                                                                                                |        |

| P0[2:0]         | Input/Output                                                             | Parallel Input/Output port. Schmitt Trigger input and open-drain output with internal pull-up TR. The STOP mode is released by "L" input of each pin. |        |

| P2[2:0]         | Parallel Input/Output port. Each bit can be individually set or cleared. |                                                                                                                                                       |        |

ATOM1.0 Family

[12]

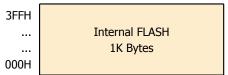

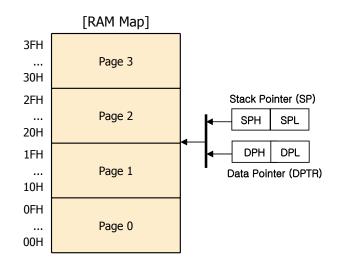

### 6.1. Memory Organization

**Preliminary**

#### Address Space

- Program memory: 1K Bytes.

Continuously addressed by Byte.

- Indirect data memory: 64 Nibbles.

Bit accessible.

- Special function registers : 16 Registers.

Directly addressed.

- ✓ Indirect function flags : 16 bits. Bit position is selected by DPL.

#### [Program Memory Map]

#### [Special Function Register Map]

| 0CH | P3 | CKCFG  | IOCFG | LVCFG |

|-----|----|--------|-------|-------|

| 08H | P2 | IAPCON | GDL   | GDH   |

| 04H | P1 | REMC   | SPL   | SPH   |

| 00H | P0 | P4     | DPL   | DPH   |

#### [Indirect Function Flag Map]

| 15   | 14    | 13   | 12   | 11   | 10   | 9    | 8    |

|------|-------|------|------|------|------|------|------|

| STOP | SLEEP | WDTE | WDTR | MAP1 | MAP0 | P4.2 | P4.3 |

| 7    | 6     | 5    | 4    | 3    | 2    | 1    | 0    |

| P3.3 | P3.2  | P3.1 | P3.0 | P2.3 | P2.2 | P2.1 | P2.0 |

**ATOM1.0 Family** [13]

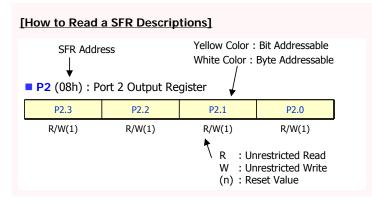

### 6.2. SFR Brief Description

**Preliminary**

| Register | Address | Description                                                                                                 | Power-On<br>Reset Value | Other<br>Reset Value |

|----------|---------|-------------------------------------------------------------------------------------------------------------|-------------------------|----------------------|

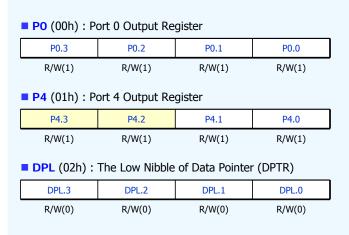

| P0       | 00H     | Port 0 output register.                                                                                     | 1111                    | 1111                 |

| P4       | 01H     | Port 4 output register.                                                                                     | 1111                    | 1111                 |

| DPL      | 02H     | The low nibble of data pointer (DPTR).                                                                      | 0000                    | 0000                 |

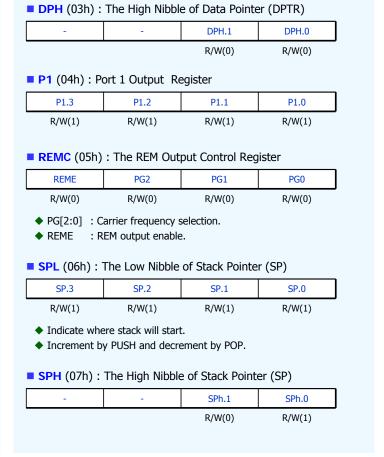

| DPH      | 03H     | The high nibble of data pointer (DPTR).                                                                     | 00                      | 00                   |

| P1       | 04H     | Port 1 output register.                                                                                     | 1111                    | 1111                 |

| REMC     | 05H     | REM output control register.                                                                                | 0000                    | 0000                 |

| SPL      | 06H     | The low nibble of stack pointer (SP).                                                                       | 1111                    | 1111                 |

| SPH      | 07H     | The high nibble of stack pointer (SP).                                                                      | 01                      | 01                   |

| P2       | 08H     | Port 2 output register.                                                                                     | 1111                    | 1111                 |

| IAPCON   | 09H     | IAP (In Application Programming) Control register. Can be accessed only if MAP1 is set and MAP0 is cleared. | 0000                    | 0000                 |

| GDL      | 0AH     | The low nibble of general purpose data register                                                             | 0000                    | 0000                 |

| GDH      | 0BH     | The high nibble of general purpose data register                                                            | 0000                    | 0000                 |

| P3       | 0CH     | Port 3 output register.                                                                                     | 1111                    | 1111                 |

| CKCFG    | 0DH     | The clock configuration register. Initialized only by power-on-reset.                                       | 0000                    | uuuu                 |

| IOCFG    | 0EH     | The I/O port configuration register. Initialized only by power-on-reset.                                    | 0000                    | uu0u                 |

| LVCFG    | 0FH     | The LVD configuration register. Initialized only by power-on-reset.                                         | 1x00                    | uxuu                 |

-: Unimplemented bit. Read as 0.

u: Remains unchanged.

x: The value of the bit is not determined.

Note for 8-pin devices.

- Not supported SFRs: P1, P3, P4, REMC.

- Writing to the not-supported SFRs may cause unexpected behavior.

ATOM1.0 Family

[14]

### 6.2. Indirect Function Flag (IFF) Description

**Preliminary**

- ◆ Indirect Function Flag (IFF)

- ✓ Write only, access using the instructions: MOV L, #n, SETB @L, CLR @L

- ✓ The individual set/clear of ports is available only if the package type supports corresponding parallel port.

| Flag  | Address (DPL) | Description                                                                                                                                                                                                                                        | Reset Value |

|-------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| STOP  | 15            | Enter stop mode. Not set until all pins of P0 and P1 are high.                                                                                                                                                                                     | 0           |

| SLEEP | 14            | Enter sleep mode. Released by WDT reset.                                                                                                                                                                                                           | 0           |

| WDTE  | 13            | Enable flag of WDT. If this flag is cleared, WDT stops running and holds the state. This flag can be modified if and only if MAP1 bit is set and MAP0 bit is cleared. This flag is also set by H/W when user sets SLEEP flag or writes IAPCON SFR. | 1           |

| WDTR  | 12            | Reset Watch Dog Timer. Set by S/W. Cleared by H/W after WDT is reset.                                                                                                                                                                              | 0           |

| MAP1  | 11            | Address map extension bit 1 for SFR/IFF.                                                                                                                                                                                                           | 0           |

| MAP0  | 10            | Address map extension bit 0 for SFR/IFF. Do not set this flag for the future compatibility.                                                                                                                                                        | 0           |

| P4.2  | 9             | Individual bit set/clear for P4                                                                                                                                                                                                                    | 1           |

| P4.3  | 8             | Individual bit set/clear for P4                                                                                                                                                                                                                    | 1           |

| P3.3  | 7             | Individual bit set/clear for P3                                                                                                                                                                                                                    | 1           |

| P3.2  | 6             | Individual bit set/clear for P3                                                                                                                                                                                                                    | 1           |

| P3.1  | 5             | Individual bit set/clear for P3                                                                                                                                                                                                                    | 1           |

| P3.0  | 4             | Individual bit set/clear for P3                                                                                                                                                                                                                    | 1           |

| P2.3  | 3             | Individual bit set/clear for P2                                                                                                                                                                                                                    | 1           |

| P2.2  | 2             | Individual bit set/clear for P2                                                                                                                                                                                                                    | 1           |

| P2.1  | 1             | Individual bit set/clear for P2                                                                                                                                                                                                                    | 1           |

| P2.0  | 0             | Individual bit set/clear for P2                                                                                                                                                                                                                    | 1           |

ATOM1.0 Family

[15]

# 6.3. Instruction Set Summary (1/2)

**Preliminary**

Refer to Appendix A (Instruction Set) for more details.

| Туре          | Instruction                                                                                                                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arithmetic    | ADD A, #data INC A DEC A ADD A, @DP ADDC A, @DP SUB A, @DP INC @DP DEC @DP                                                                                    | Add data to ACC. Increment ACC. Decrement ACC. Add the indirect memory nibble to ACC. Add the indirect memory nibble to ACC with the Carry in C. Subtract the indirect memory nibble from ACC. Increment the indirect memory nibble. Decrement the indirect memory nibble.                                                                                                                                                                                                                                                                                                                                             |

| Logical       | CLR A CPL A RRC A ANL A, @DP ORL A, @DP XRL A, @DP                                                                                                            | Clear ACC. Complement ACC. Rotate right ACC with Carry flag. Logical AND for ACC and the indirect memory nibble. Logical OR for ACC and the indirect memory nibble. Logical Exclusive-OR for ACC and the indirect memory nibble.                                                                                                                                                                                                                                                                                                                                                                                       |

| Data Transfer | MOV dir, A MOV A, dir MOV A, @DP MOV A, #data MOV L, @DP MOV @DP, A MOVI @DP, A MOVD @DP, A XCH A, @DP MOVI @DP, #data MOV L, #data MOV H, #data PUSH A POP A | Move ACC to the special function register.  Move the special function register to ACC.  Move the indirect memory nibble to ACC.  Move data to ACC.  Move the indirect memory nibble to DPL.  Move ACC to the indirect memory nibble.  Move ACC to the indirect memory nibble and increment the data pointer (DPH,DPL).  Move ACC to the indirect memory nibble and decrement the data pointer (DPH,DPL).  Exchange ACC and the indirect memory nibble.  Move data to the indirect memory nibble and increment the data pointer (DPH,DPL).  Move data to DPL.  Move data to DPH.  Push ACC to stack.  Pop stack to ACC. |

ATOM1.0 Family

[16]

# 6.3. Instruction Set Summary (2/2)

Preliminary

Refer to Appendix A (Instruction Set) for more details.

| Туре        | Instruction                                                                                                                                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Branch      | CJNE @DP, #data, rel CJNE L, #data, rel CJNE A, dir, rel CJNE A, @DP, rel CJLE A, @DP, rel CJNE A, #data, rel DJNZ A, rel JB bit, rel JNB bit, rel JC rel JNC rel JMP addr CALL addr RET NOP | Jump if the indirect memory nibble is not equal to the data.  Jump if DPL is not equal to the data.  Jump if ACC is not equal to the special function register.  Jump if ACC is not equal to the indirect memory nibble.  Jump if ACC is less than or equal to the indirect memory nibble.  Jump if ACC is not equal to the data.  Decrement ACC. Jump if the result is not zero.  Jump if the indirect memory bit is 1.  Jump if the indirect memory bit is 0.  Jump if C is 1.  Jump if C is 0.  Jump to given address.  Call subroutine.  Return from subroutine.  No operation. |

| Bit & Misc. | SETB @L CLR @L SETB bit CLR bit SETB C CLR C INC DPTR DEC DPTR                                                                                                                               | Set the indirect function flag. Clear the indirect function flag. Set the indirect memory bit. Clear the indirect memory bit. Set Carry flag. Clear Carry flag. Increment the data pointer. Decrement the data pointer.                                                                                                                                                                                                                                                                                                                                                             |

ATOM1.0 Family

[17]

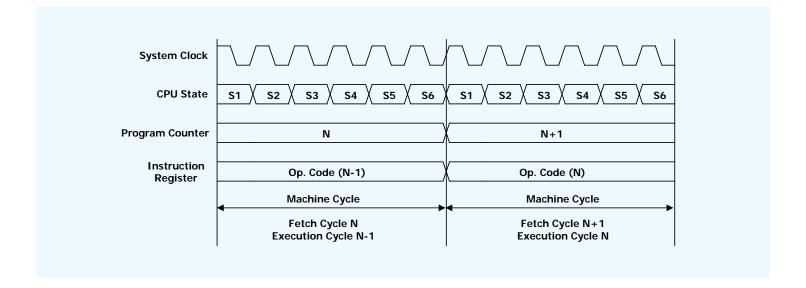

6.4. CPU Timing

**Preliminary**

- CPU takes 6 clocks for a machine cycle.

- ◆ Any instruction except branch instructions completes in one machine cycle.

- ◆ All branch instruction consumes 2 machine cycles whether the branch is taken or not.

- ◆ The state of SFR, I/O ports, or IFF flags changes at the end of an instruction (S6).

ATOM1.0 Family

[18]

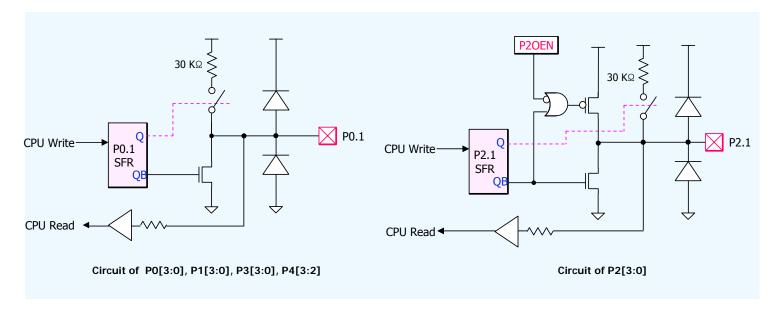

### 6.5. I/O Ports : PORT0 ~ PORT4

**Preliminary**

- All ports are initialized asynchronously on power-up.

- Pull-up enable and input by default (reset).

- Open drain active low output.

- ◆ P2[3:0] may be configured as push-pull output port.

- CPU always write to SFR register, but reads port pin.

- Retains the previous state in stop mode or sleep mode.

ATOM1.0 Family

[19]

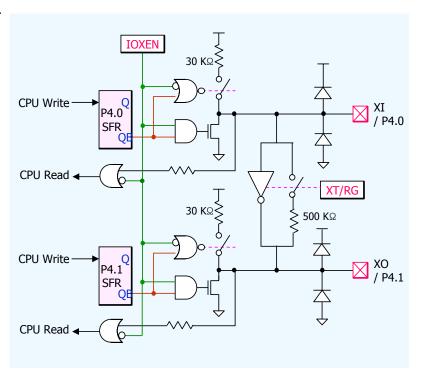

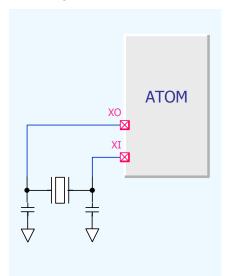

### 6.5. I/O Ports: PORT4[1:0] (XI/XO)

**Preliminary**

- XI/XO for Clock Input/Output

- ✓ Enabled if XT/RG bit in CKCFG SFR is set.

- Disabled in STOP mode (XI and XO are in low state).

- XI/XO as an I/O Port

- XI and XO can be configured as I/O port if IOXEN bit in IOCFG SFR is set.

- ✓ User should not set XT/RG and IOXEN at the same time.

- ✓ Pull-up enable and input by default (reset).

- Open drain active low output.

- CPU always write to SFR register, but reads port pin.

- Retains the previous state at stop mode.

#### ✓ IOCFG (0Eh) : I/O Port Configuration Register

| IOMAP1 | IOMAP0 | P2OEN  | IOXEN  |

|--------|--------|--------|--------|

| R/W(0) | R/W(0) | R/W(0) | R/W(0) |

- IOXEN: Enable XI and XO as I/O ports.

- 0 = XI and XO are used for clock input (Default).

- 1 = XI and XO is used for PORT4[1:0].

- P2OEN: Configure P2 as a push-pull output port.

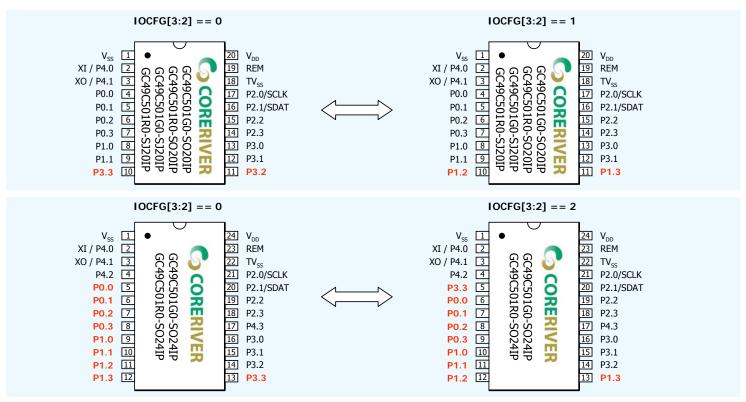

- IOMAP[1:0] : Configure I/O ports mapping .

| IOMAP1 | IOMAP0 | Ports Mapping                    |

|--------|--------|----------------------------------|

| 0      | 0      | Default.                         |

| 0      | 1      | Optional 20-pin I/O Port Mapping |

| 1      | 0      | Optional 24-pin I/O Port Mapping |

| 1      | 1      | Reserved                         |

#### IOCFG

- ✓ This SFR is initialized to default state only by power-onreset. Only the P2OEN bit is cleared by other resets.

- For 8-pin devices, only P2OEN bit is available. User should not set other bits.

ATOM1.0 Family

[20]

**Preliminary**

### 6.5. I/O Ports: I/O Mapping

- User may select I/O port mapping by setting IOCFG SFR.

- The functionality of each I/O pins is the same for any mapping.

- This configuration option is useful when the pin-to-pin compatibility with existing devices is essential.

**CORERIVER**

ATOM1.0 Family

[21]

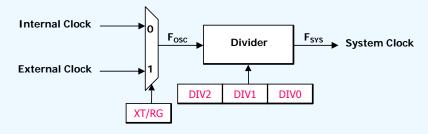

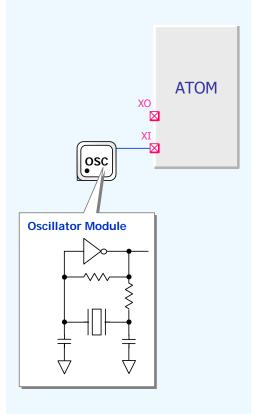

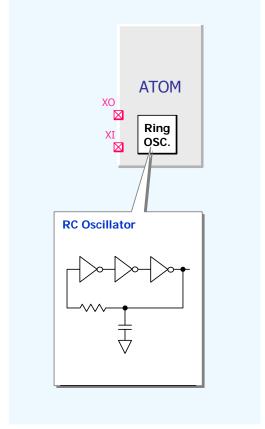

### 6.6. Clock Configuration

**Preliminary**

- ◆ Two System Clock Sources: Internal Ring OSC. or External Resonator/Crystal

- Default System Clock is Ring OSC.

- ♦ When user changes the clock source (XT/RG bit), internal reset is generated.

- Internal reset does not affect CKCFG.

- ◆ The configuration SFR (CKCFG) is initialized by power-on reset.

- User may change clock frequency during operation by changing divide option.

#### ✓ CKCFG (0Dh): The clock configuration register.

| XT/RG  | DIV2   | DIV1   | DIV0   |

|--------|--------|--------|--------|

| R/W(0) | R/W(0) | R/W(0) | R/W(0) |

- XT/RG: System clock source selection.

- 0 = Internal Ring oscillator is selected as system clock. External clock osc. is disabled.

- 1 = External clock is selected as system clock.

Internal Ring oscillator is disabled.

Do not set this bit for 8-pin devices.

- DIV[2:0] : System clock divider selection.

| DIV2 | DIV1 | DIV0 | $F_{SYS}$            |

|------|------|------|----------------------|

| 0    | 0    | 0    | F <sub>osc</sub>     |

| 0    | 0    | 1    | F <sub>osc</sub> /2  |

| 0    | 1    | 0    | F <sub>osc</sub> /4  |

| 0    | 1    | 1    | F <sub>osc</sub> /8  |

| 1    | 0    | 0    | F <sub>osc</sub> /16 |

| 1    | 0    | 1    | F <sub>osc</sub> /32 |

| 1    | 1    | 0    | F <sub>osc</sub> /64 |

| 1    | 1    | 1    | -                    |

ATOM1.0 Family

[22]

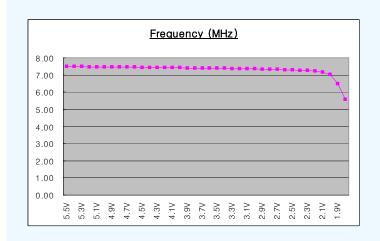

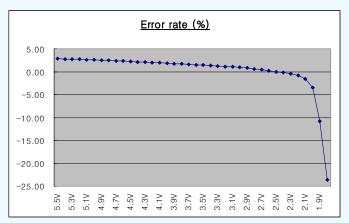

### 6.6. Clock Configuration: Internal Ring OSC.

**Preliminary**

- The Internal Ring OSC. Provides a Fixed System Clock

- ✓ Factory calibrated to  $\pm 3\%$  at 2.1V  $\sim 3.3$ V.

- ✓ Factory calibrated to  $\pm 1\%$  at 2.5V.

- ◆ The Factory Calibration for 7.28MHz is applied only for GC49C501RX devices.

**VOLTAGE-FREQUENCY GRAPH**

ATOM1.0 Family

[23]

### 6.6. Clock Configuration: Guideline

**Preliminary**

- Resonator/ Crystal Oscillator

- Oscillator Module

- Internal Ring Oscillator

CORERIVER

ATOM1.0 Family

[24]

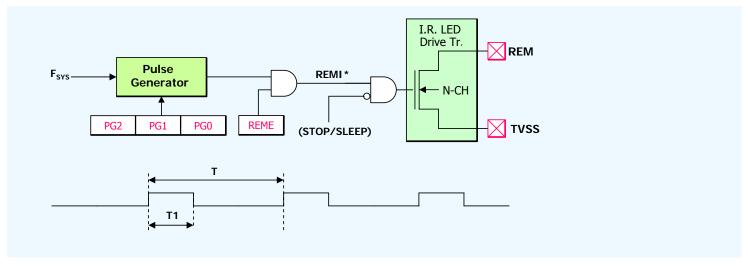

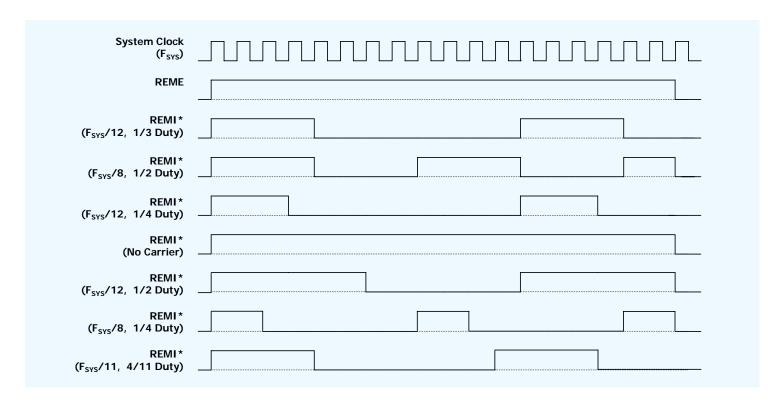

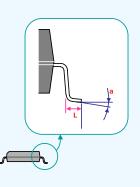

# 6.7. Carrier Frequency Generation

**Preliminary**

Support 7 types of carrier frequency.

✓ **REMC** (05h) : The REM Output Control Register.

| REME   | PG2    | PG1    | PG0    |

|--------|--------|--------|--------|

| R/W(0) | R/W(0) | R/W(0) | R/W(0) |

- PG[2:0] : Carrier Frequency Selection.

- REME : REM Output Enable.

| REME | PG2 | PG1 | PG0 | Transmission Control ( REMI )           |

|------|-----|-----|-----|-----------------------------------------|

| 0    | Χ   | Х   | Х   | 0 (Disable)                             |

| 1    | 0   | 0   | 0   | $1/T = F_{SYS}/12$ , $T1/T = 1/3$       |

| 1    | 0   | 0   | 1   | $1/T = F_{SYS}/8$ , $T1/T = 1/2$        |

| 1    | 0   | 1   | 0   | $1/T = F_{SYS}/12$ , $T1/T = 1/4$       |

| 1    | 0   | 1   | 1   | 1 (No Carrier)                          |

| 1    | 1   | 0   | 0   | $1/T = F_{SYS}/12$ , $T1/T = 1/2$       |

| 1    | 1   | 0   | 1   | $1/T = F_{SYS}/8$ , $T1/T = 1/4$        |

| 1    | 1   | 1   | 0   | 1/T = F <sub>SYS</sub> /11, T1/T = 4/11 |

| 1    | 1   | 1   | 1   | 1 (No Carrier)                          |

ATOM1.0 Family

[25]

### 6.7. Carrier Frequency Generation

**Preliminary**

#### Waveform Example

- ✓ REM output is the inverse of REMI\*

- ✓ Since the IR. LED drive transistor in ATOM is a N-Type, IR. LED is turned on when REMI\* is high.

ATOM1.0 Family

[26]

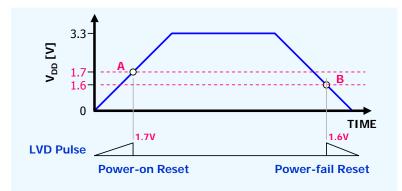

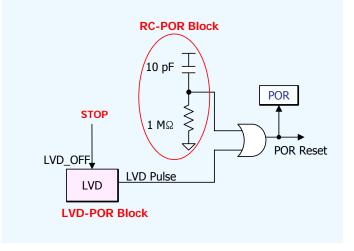

### 6.8. POR & LVD: Power-On Reset

- On-chip power-on reset is a logical OR of RC-POR and LVD-POR

- RC-POR operates when the rising time of power (V<sub>DD</sub>) is short.

- On-chip LVD

- Provides power-on reset when the rising time of power is relatively long.

- ✓ Power-on reset voltage is 1.7 V.

- Provides power-fail reset when the power goes down below 1.6 V.

- After POR pulse is off, the internal clock stabilization counter starts to run, which lengthens power-on reset about 4.5 ms.

✓ LVCFG (0Fh) : LVD Configuration Register

| POR    | Reserved | Reserved | Reserved |

|--------|----------|----------|----------|

| R/W(1) | R(X)     | R/W(0)   | R/W(0)   |

- Reserved: Do not set these bits for the future compatibility.

- POR : Power-on-reset flag to distinguish cold reset.

User need to mask out the reserved bits by AND oprtation when referring to this bit.

ATOM1.0 Family

[27]

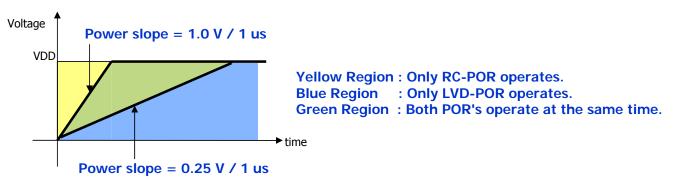

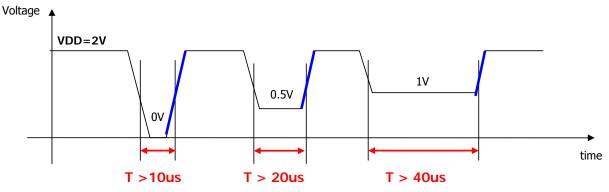

### 6.8. POR & LVD: Condition for power notch

Power-on-reset is independent of power-rising slope.

The cases of reset generation by VDD notch

When VDD fails for a short time, the duration of notch (T) has limitation like above for the successful POR operation.

The duration (T) will be changed by the VDD value and the transition time

ATOM1.0 Family

[28]

### 6.9. WDT (Watchdog Timer)

**Preliminary**

#### WDT

- ✓ Free running counter which resets CPU every 2<sup>17</sup> system clock cycles.

- ✓ Although the counter length is fixed, WDT overflow period may vary according to the current frequency of system clock.

- ✓ WDT is halt in STOP mode or disabled by user.

#### WDT is reset by

- User S/W set WDTR bit in IFF[12]. WDTR bit is automatically cleared by H/W after WDT is reset.

- ✓ Internal reset caused by any source is activated.

- Entering SLEEP mode.

- ✓ Start of FLASH programming (erase/write) by IAP.

#### Run Control of WDT

- ✓ WDT may be disabled if WDTE flag in IFF[13] is cleared.

- When disabled WDT holds the state before.

- ✓ User can modify WDTE if and only if MAP1 flag in IFF[11] is set and MAP0 flag in IFF[10] is cleared.

- ✓ WDTE is set by internal reset and also set by H/W when user sets SLEEP flag in IFF[14] or writes IAPCON SFR.

#### Program Sequence to disable WDT

MOV L, #11

SETB @L ; Enable MAP1

MOV L, #13

CLR @L ; Disable WDT

MOV L, #11

CLR @L ; Disable MAP1

#### [Example of WDT Period]

| XT/RG | DIV2 | DIV1 | DIV0 | F <sub>OSC</sub> (MHz) | F <sub>SYS</sub>     | WDT Period (ms) |

|-------|------|------|------|------------------------|----------------------|-----------------|

| 1     | 0    | 1    | 1    | 3.64                   | F <sub>OSC</sub> /8  | 288             |

| 0     | 0    | 0    | 0    | 7.28                   | F <sub>osc</sub>     | 18              |

| 0     | 1    | 1    | 0    | 7.28                   | F <sub>osc</sub> /64 | 1152            |

ATOM1.0 Family

[29]

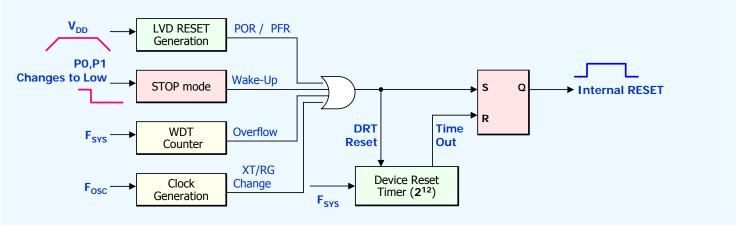

### 6.10. Reset Circuit

**Preliminary**

#### Reset Sources

- ✓ Power-on Reset (POR) when Power-Up.

- ✓ Power-fail Reset

- ✓ STOP mode Wake-up by changes in input port P0 or P1.

- ✓ WDT Overflow for abnormal condition or SLEEP mode.

- ✓ Clock source change (State change of CKCFG[3]).

#### Device Reset Timer

- ✓ Once set, internal reset remains high until the DRT (Device Reset Timer) is expired.

- ✓ The reset time depends on the configuration of system clock in CKCFG SFR.

- $\checkmark$  For an instance, the period for  $2^{12}$  is 9 ms when  $F_{SYS}$  is 455 KHz.

- ✓ Note that CKCFG is not affected by internal reset.

- ✓ For power-on reset, the reset time is about 4.5 ms.

ATOM1.0 Family

[30]

### 6.11. Power Management : 3 Modes

**Preliminary**

- Active Mode

- CPU and peripheral are running.

- Sleep Mode

- Only WDT is running.

- ✓ I/O ports hold the state before sleep mode.

- ✓ Wake-up by WDT overflow.

- ✓ The longest period of WDT overflow is 1.1 second when the internal RING clock is used.

- ✓ Device is reset.

- Stop Mode

- ✓ All of the device function including external clock oscillator stops running.

- ✓ I/O ports hold the state before stop mode.

- ✓ Wake-up by input pin (P0, P1) changes.

- Device is reset.

ATOM1.0 Family

[31]

### 6.12. In Application Programming (IAP)

### **Preliminary**

#### In Application Programming

- User S/W can read or modify specific regions of FLASH with IAP function during operation.

- ✓ The EEP0/1 regions may be used as program memory or data memory.

- CPU is halt during IAP and continues execution after IAP from the next instruction which set IAPCON.

- ✓ It takes 6 system clocks to read a byte with IAP.

- ✓ It takes about 2 ms to write(erase) a byte with IAP.

- ✓ When user attempts to write IAPCON, WDTE bit in IFF[13] is also set.

- ✓ If IAP operation is erase or write, WDT is reset before the programming is started.

#### IAP Related SFR

- ✓ DPH / DPL : Least significant 6-bit address for IAP.

- ✓ GDH / GDL : 8-bit data buffer for read or write by IAP.

- ✓ IAPCON: IAP control SFR. Automatically cleared to zero after IAP is done.

#### IAP Enable Condition

- ✓ IAP can not erase or write INFO region.

- ✓ IAPCON can be written if and only if

- MAP0 bit in IFF[10] is cleared,

- MAP1 bit in IFF[11] is set,

- and corresponding bit in CFGWD[2:1] is set.

- ✓ When IAP is blocked by above condition, "MOV IAPCON, A" instruction is like "NOP" instruction.

#### ✓ IAPCON (09h) : IAP Control Register

| RGS1   | RGS0   | OPS1   | OPS0   |

|--------|--------|--------|--------|

| R/W(0) | R/W(0) | R/W(0) | R/W(0) |

- RGS[1:0] : Select IAP region

- OPS[1:0] : Select IAP function

| RGS | 1 | RGS0 | IAP Region           |

|-----|---|------|----------------------|

| 0   |   | 0    | EEP0 (0x1C0 ~ 0x1FF) |

| 0   |   | 1    | EEP1 (0x3C0 ~ 0x3FF) |

| 1   |   | 0    | INFO (0x0 ~ 0x7)     |

| 1   |   | 1    | Reserved             |

| OPS1 | OPS0 | IAP Function |

|------|------|--------------|

| 0    | 0    | No operation |

| 0    | 1    | Byte Read    |

| 1    | 0    | Byte Erase   |

| 1    | 1    | Byte Write   |

ATOM1.0 Family

[32]

### 6.12. In Application Programming (IAP)

**Preliminary**

#### Electrical Characteristic of IAP

- Note that the program time depends on the configuration of system clock frequency.

- ✓ If the system clock frequency is out of IAP range, user need to change F<sub>SYS</sub> before and after IAP by configuring CKCFG SFR.

| Parameter                 | Symbol           | MIN | TYP | MAX | Unit |

|---------------------------|------------------|-----|-----|-----|------|

| Power Supply<br>Voltage   | V <sub>DD</sub>  | 2.7 | -   | 5.5 | V    |

| System Clock<br>Frequency | F <sub>SYS</sub> | 5   | 8   | 11  | MHz  |

| Write /Erase<br>Time      | Тр               | 1.5 | 2.0 | 3.3 | ms   |

#### FLASH Regions

✓ EEPROM area is a part of program memory.

#### Information Region

| ADDRESS  | 0     | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|----------|-------|---|---|---|---|---|---|---|

| Mnemonic | CFGWD |   |   |   |   |   |   |   |

- The first byte contains CFGWD

- ✓ May be used to store user ID, or checksum, etc.

- Only the full chip erase function of ISP can erase this region.

#### CFGWD : Configuration Word

- ✓ CFGWD[0] (ISP\_LOCK) : Disable read, write, or erase by ISP except the full chip erase.

- ✓ CFGWD[1] (IAP\_RE): Enable read by IAP.

- ✓ CFGWD[2] (IAP\_PE) : Enable write or erase by IAP.

ATOM1.0 Family

[33]

# 7. Absolute Maximum Ratings

Preliminary

#### Absolute Maximum Ratings

| Symbol           | Parameter                | Rating                       | Unit |

|------------------|--------------------------|------------------------------|------|

| V <sub>DD</sub>  | DC supply voltage        | -0.5 to 6.5                  | V    |

| V <sub>IN</sub>  | DC input voltage         | -0.5 to V <sub>DD</sub> +0.5 | V    |

| V <sub>OUT</sub> | DC output voltage        | -0.5 to V <sub>DD</sub> +0.5 | V    |

| т                | DC authorit high armount | One I/O pin active : -25     | mA   |

| I <sub>OH</sub>  | DC output high current   | All I/O pin active : -100    | mA   |

| T                | DC autout law august     | One I/O pin active: 30       | mA   |

| $I_{OL}$         | DC output low current    | All I/O pin active: 150      | mA   |

| T <sub>STG</sub> | Storage temperature      | -55 to 125                   | °C   |

#### Recommended Operating Conditions

| Symbol         | Parameter                    | Rating     | Unit |

|----------------|------------------------------|------------|------|

| $V_{DD}$       | DC supply voltage            | 1.8 to 5.5 | V    |

| T <sub>A</sub> | Industrial temperature range | -20 to 85  | °C   |

ATOM1.0 Family

[34]

### 8. DC Characteristics

**Preliminary**

\* TA = = -20 °C  $\sim$  +85 °C,  $V_{DD}$  = 1.8V  $\sim$  5.5V unless otherwise specified.

|                               | Symbol Pin         |                                     | Value                                                                                 |                         |      |                         |      |

|-------------------------------|--------------------|-------------------------------------|---------------------------------------------------------------------------------------|-------------------------|------|-------------------------|------|

| Parameter                     |                    | Pin                                 | Conditions                                                                            | Min.                    | Тур. | Max.                    | Unit |

| Input Low Voltage             | $V_{IL1}$          | P0, P1 ,P2 ,P3, P4.3, P4.2          | V <sub>DD</sub> = 1.8V~5.5V                                                           | -0.5                    | -    | 0.2V <sub>DD</sub> -0.1 | - V  |

|                               | V <sub>IL2</sub>   | XI / P4.0, XO / P4.1                |                                                                                       | -0.5                    | -    | 0.3V <sub>DD</sub>      |      |

| Input high Voltage            | $V_{\mathrm{IH1}}$ | P0, P1 ,P2 ,P3, P4.3, P4.2          | V <sub>DD</sub> = 1.8V~5.5V                                                           | 0.2V <sub>DD</sub> +1.0 | -    | V <sub>DD</sub> +0.5    | V    |

|                               | $V_{IH2}$          | XI / P4.0, XO / P4.1                |                                                                                       | 0.7V <sub>DD</sub>      | -    | V <sub>DD</sub> +0.5    |      |

| Input High<br>Leakage Current | ${ m I_{IH}}$      | All pins except XI, XO              | $V_{IN} = V_{DD}$                                                                     | -1                      | -    | +1                      | μА   |

| Output Low Voltage            | V <sub>OL</sub>    | P0, P1, P2, P3, P4                  | $I_{OL} = 20 \text{mA } @V_{DD} = 5V$<br>$(I_{OL} = 3 \text{mA } @V_{DD} = 2.2V)$     | -                       | -    | 0.3V <sub>DD</sub>      | V    |

| Output Low Voltage            | V <sub>OL2</sub>   | REM                                 | I <sub>OL2</sub> = 280mA @V <sub>DD</sub> =3V                                         | -                       | -    | 0.4                     | ٧    |

| Output High Voltage           | V <sub>OH</sub>    | P2 (Configured as push-pull output) | $I_{OH} = -15 \text{mA } @V_{DD} = 5V$<br>$(I_{OH} = -2 \text{mA } @V_{DD} = 2.2V)$   | 0.7V <sub>DD</sub>      | -    | -                       | ٧    |

| Output High Voltage           | V <sub>OHP</sub>   | Pull-up current                     | $I_{OHP}$ = -40uA @V <sub>DD</sub> =5V<br>( $I_{OHP}$ = -15uA @V <sub>DD</sub> =2.2V) | 0.7V <sub>DD</sub>      | -    | -                       | V    |

| Pin Capacitance               | C <sub>IO</sub>    | All                                 | $V_{DD} = 5V$                                                                         | -                       | 10   | -                       | pF   |

ATOM1.0 Family

[35]

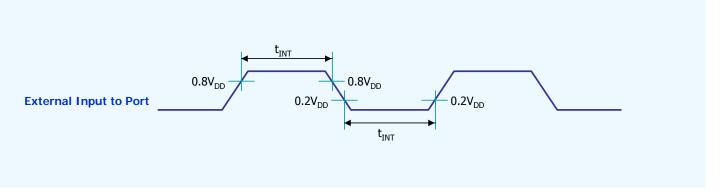

# 9. AC Characteristics

\* TA = -20 °C  $\sim$  +85 °C unless otherwise specified. TBD = To Be Determined.

| Parameter                                | Symbol                  | Dire                                                     | Conditions                                                       | Value |      |      | 11               |

|------------------------------------------|-------------------------|----------------------------------------------------------|------------------------------------------------------------------|-------|------|------|------------------|

|                                          |                         | Pin                                                      |                                                                  | Min.  | Тур. | Max. | Unit             |

| Oscillator Frequency<br>(Internal Clock) | F <sub>osc</sub>        |                                                          | $2.7~\textrm{V} \leq \textrm{V}_\textrm{DD} \leq 5.5~\textrm{V}$ | -     |      | 10   | MHz              |

|                                          |                         |                                                          | $1.8 \text{ V} \le \text{V}_{\text{DD}} < 2.7 \text{ V}$         | -     |      | 5    |                  |

| Oscillator Frequency<br>(External Clock) | F <sub>OSC</sub> XI, XO | VI VO                                                    | $2.7~\textrm{V} \leq \textrm{V}_\textrm{DD} \leq 5.5~\textrm{V}$ | -     | -    | 10   | MI I-            |

|                                          |                         | $1.8 \text{ V} \le \text{V}_{\text{DD}} < 2.7 \text{ V}$ | -                                                                | -     | 5    | MHz  |                  |

| System Frequency                         | F <sub>SYS</sub>        |                                                          | $1.8~\textrm{V} \leq \textrm{V}_\textrm{DD} \leq 5.5~\textrm{V}$ | 1/64  | -    | 1    | F <sub>OSC</sub> |

| External Input Width                     | t <sub>INT</sub>        | P0, P1, P2, P3, P4                                       | $1.8~\textrm{V} \leq \textrm{V}_\textrm{DD} \leq 5.5~\textrm{V}$ | 12    | -    | -    | F <sub>SYS</sub> |

ATOM1.0 Family

[36]

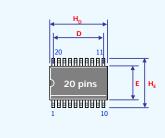

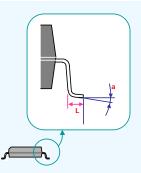

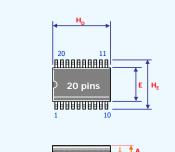

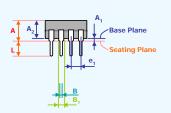

## 10. Package Dimensions : 20-SOIC(Narrow/JEDEC)

#### [20-SOIC (Narrow)]

| Symbol         | Dim   | ension in Inc | ches  | Dimension in mm |       |       |  |

|----------------|-------|---------------|-------|-----------------|-------|-------|--|

| Syllibol       | Min.  | Nom.          | Max.  | Min.            | Nom.  | Max.  |  |

| A              | -     | -             | 0.890 | -               | -     | 2.25  |  |

| A <sub>1</sub> | 0.002 | -             | -     | 0.05            | -     | -     |  |

| b              | 0.014 | 0.018         | 0.022 | 0.35            | 0.45  | 0.55  |  |

| D              | -     | 0.450         | -     | -               | 11.43 | -     |  |

| E              | 0.197 | 0.209         | 0.220 | 5.00            | 5.30  | 5.60  |  |

| H <sub>D</sub> | 0.492 | 0.500         | 0.510 | 12.50           | 12.70 | 12.95 |  |

| H <sub>E</sub> | 0.291 | 0.307         | 0.323 | 7.40            | 7.80  | 8.20  |  |

| L              | 0.012 | -             | 0.031 | 0.30            | -     | 0.80  |  |

| а              | 0°    | -             | 8°    | 0°              | -     | 8°    |  |

| e              |       | 0.050 BSC     |       | 1.27 BSC        |       |       |  |

#### [20-SOIC (JEDEC)]

| Symbol         | Dim   | ension in Inc | ches  | Dimension in mm |      |        |  |

|----------------|-------|---------------|-------|-----------------|------|--------|--|

| Syllibol       | Min.  | Nom.          | Max.  | Min.            | Nom. | Max.   |  |

| Α              | -     | -             | 0.106 | -               | -    | 2.7    |  |

| Α,             | 0.004 | -             | ,     | 0.1             | ,    | -      |  |

| b              | 0.013 | 0.016         | 0.020 | 0.324           | 0.4  | 0.51   |  |

| E              | 0.264 | 0.295         | 0.324 | 6.71            | 7.5  | 8.23   |  |

| H <sub>D</sub> | 0.495 | 0.504         | 0.512 | 12.57           | 12.8 | 13     |  |

| H <sub>F</sub> | 0.394 | 0.406         | 0.419 | 10.0            | 10.3 | 10.643 |  |

| L              | 0.016 | -             | 0.052 | 0.406           | -    | 1.32   |  |

| а              | 0°    | -             | 8°    | 0°              |      | 8°     |  |

| e              |       | 0.050 BSC     |       | 1.27 BSC        |      |        |  |

- Notes:

1. Dimension D & E include mold mismatch and are determined at the mold parting line.

2. General appearance spec. should be based on final visual inspection spec.

ATOM1.0 Family

[37]

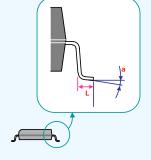

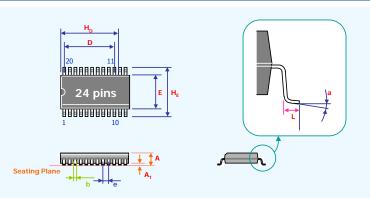

## 10. Package Dimensions: 24-SOIC

#### [24-SOIC]

| Symbol         | Dim   | ension in In | ches  | Dimension in mm |       |       |  |  |

|----------------|-------|--------------|-------|-----------------|-------|-------|--|--|

| Зуппоот        | Min.  | Nom.         | Max.  | Min.            | Nom.  | Max.  |  |  |

| A              | 0.094 | 0.098        | 0.102 | 2.40            | 2.50  | 2.60  |  |  |

| A <sub>1</sub> | 0.004 | 0.008        | 0.012 | 0.10            | 0.20  | 0.30  |  |  |

| b              | 0.014 | 0.017        | 0.019 | 0.36            | 0.42  | 0.49  |  |  |

| D              | -     | 0.550        | -     | -               | 13.97 | -     |  |  |

| E              | 0.291 | 0.295        | 0.299 | 7.40            | 7.50  | 7.60  |  |  |

| H <sub>D</sub> | 0.598 | 0.606        | 0.614 | 15.20           | 15.40 | 15.60 |  |  |

| H <sub>E</sub> | 0.398 | 0.406        | 0.413 | 10.10           | 10.30 | 10.50 |  |  |

| L              | 0.004 | 0.010        | 0.016 | 0.10            | 0.25  | 0.40  |  |  |

| а              | 0°    | -            | 8°    | 0°              | -     | 8°    |  |  |

| e              |       | 0.050 BSC    |       | 1.27 BSC        |       |       |  |  |

#### Notes:

- Dimension D & E include mold mismatch and are determined at the mold parting line.

- General appearance spec. should be based on final visual inspection spec

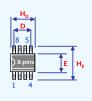

# 10. Package Dimensions : 8-SPDIP/SOIC

#### [8-SPDIP]

| Symbol         | Dim   | ension in Inc | ches  | Dir   | nension in n | nm    |

|----------------|-------|---------------|-------|-------|--------------|-------|

| Syllibol       | Min.  | Nom.          | Max.  | Min.  | Nom.         | Max.  |

| Α              | -     | 0.155         | -     | -     | 3.93         | -     |

| A <sub>1</sub> | 0.015 | -             | -     | 0.380 | -            | -     |

| A <sub>2</sub> |       | 0.140         | -     | -     | 3.55         | -     |

| В              | 0.015 | 0.019         | 0.022 | 0.38  | 0.47         | 0.56  |

| B <sub>1</sub> | 0.050 | 0.057         | 0.065 | 1.27  | 1.46         | 1.65  |

| С              | 0.008 | 0.011         | 0.014 | 0.20  | 0.28         | 0.36  |

| D              | 0.367 | 0.377         | 0.387 | 9.33  | 9.58         | 9.83  |

| E              | -     | 0.299         |       | -     | 7.60         | -     |

| E <sub>1</sub> | 0.240 | 0.250         | 0.260 | 6.10  | 6.35         | 6.60  |

| e <sub>1</sub> | -     | 0.100         | -     | -     | 2.54         |       |

| L              | 0.120 | 0.130         | 0.140 | 3.05  | 3.30         | 3.55  |

| а              | 0°    | -             | 15°   | 0°    | -            | 15°   |

| e <sub>A</sub> | 0.330 | 0.350         | 0.370 | 8.382 | 8.89         | 9.398 |

- Notes:

1. Dimension D Max. & S include mold flash or tie bar Burns.

2. Dimension E<sub>1</sub> dose not include interlead flash.

3. Dimension D & E<sub>1</sub> include mold mismatch and are determined at the mold parting line.

4. Dimension B<sub>1</sub> does not include dambar protrusion/intrusion.

5. General appearance spec. should be based on final visual inspection spec.

#### [8-SOIC]

| Symbol         | Dim   | ension in In | ches  | Dimension in mm |      |      |  |

|----------------|-------|--------------|-------|-----------------|------|------|--|

| Syllibol       | Min.  | Nom.         | Max.  | Min.            | Nom. | Max. |  |

| A              | 0.068 | 0.072        | 0.075 | 1.73            | 1.82 | 1.90 |  |

| A <sub>1</sub> | 0.004 | 0.007        | 0.010 | 0.10            | 0.18 | 0.26 |  |

| b              | 0.012 | 0.016        | 0.020 | 0.31            | 0.41 | 0.51 |  |

| D              |       | 0.150        |       | -               | 3.81 | -    |  |

| E              | 0.146 | 0.154        | 0.161 | 3.70            | 3.90 | 4.10 |  |

| H <sub>D</sub> | 0.185 | 0.193        | 0.201 | 4.70            | 4.90 | 5.10 |  |

| H <sub>E</sub> | 0.224 | 0.236        | 0.248 | 5.70            | 6.00 | 6.30 |  |

| L              | 0.017 | 0.026        | 0.035 | 0.42            | 0.65 | 0.88 |  |

| а              | 0°    | -            | 8°    | 0°              | -    | 8°   |  |

| e              |       | 0.050 BSC    |       | 1.27 BSC        |      |      |  |

- Notes:

1. Dimension D & E include mold mismatch and are determined at the mold parting line.

2. General appearance spec. should be based on final visual inspection spec.

ATOM1.0 Family

[39]

### 11. Product Numbering System

#### **Preliminary**

```

XX

X X X

X

X X X

General Core

Version

0-9 = Revision

P = Power position

MCU Series

P = Pb-Free

Core Type

Temperature

= 4 bits

= 0^{\circ}C \sim 70^{\circ}C

= 8 bits

= -20°C ~ 85°C

16 = 16 bits

= -40^{\circ}C \sim 85^{\circ}C

32 = 32 \text{ bits}

= -40^{\circ}C \sim 125^{\circ}C

Α

ROM Type

Package Pins

0 = ROMless

1 = Mask ROM

7 = EPROM

Package Type

8 = EEPROM

P = PDIP

TS = TSSOP

DF = DFN

9 = FLASH

SP = SPDIP

LQ = LQFP

ML = MLF

PL = PLCC

MQ = MQFP

WL = WLCSP

= SOP/SOICTQ = TQFP

W = Wafer Biz.

Operating Voltage

CO = COB

= Chip Biz.

SS = SSOP

= Common

(1.8V \sim 5.5V)

= Low Voltage

Custom ROM Code

(1.2V \sim 2.7V)

Application

(Option)

= General

ROM Size

= ADC

320 = ROMIess

= RCLK Calibration

500 = 2KB

= Battery

501 = 1KB

= LCD

L

510 = 4KB

U

= USB

520 = 8KB

Р

= Printer

54X = 16KB

Ε

= Edu./Toy

58X = 32KB

т

= Telecom

59X = 64KB

= Home Application

```

ATOM1.0 Family

[40]

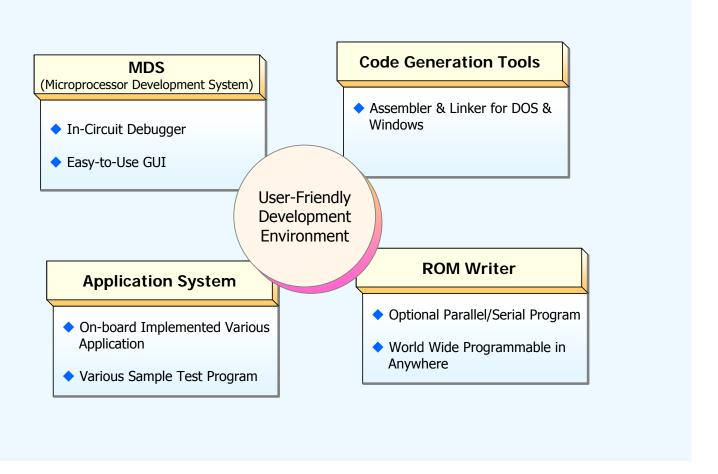

### 12. Supporting tools

**Preliminary**

ATOM1.0 Family

[41]

## **Appendix A : Instruction Set (1/19)**

**Preliminary**

#### Abbreviations and Symbols

| Symbol   | Description                                                                        | Symbol            | Description                                                                       |

|----------|------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------|

| PC       | The program counter.                                                               | (PC)              | The contents of PC.                                                               |

| Α        | The accumulator register (ACC).                                                    | (A)               | The contents of ACC.                                                              |

| С        | The carry flag.                                                                    | (C)               | The contents of C.                                                                |

| SP       | The stack pointer register. Concatenation of SPH and SPL.                          | M[SP]             | The contents of RAM addressed by SP.                                              |

| (DP)     | The contents of DPTR.                                                              | (SP)              | The contents of SP.                                                               |

| DP       | The data pointer register (DPTR). Concatenation of DPH and DPL.                    | M[DP]             | The contents of RAM addressed by DPTR.                                            |

| Н        | The high nibble of the data pointer (DPH).                                         | (H)               | The contents of DPH.                                                              |

| L        | The low nibble of the data pointer (DPL).                                          | (L)               | The contents of DPL.                                                              |

| F[L]     | The contents of indirect function flag (IFF) addressed by DPL.                     | rel               | 8-bit signed displacement value for relative branch (-128 $\leq$ rel $\leq$ 127). |

| #data    | 4-bit data operand                                                                 | addr              | 12-bit absolute branch address.                                                   |

| dir      | 4-bit direct address of SFRs $(0 \le dir \le 15)$                                  | R[dir]            | The contents of SFR or read value of ports.                                       |

| bit      | 2-bit pointer of the bit in data memory addressed by DPTR (0 $\leq$ bit $\leq$ 3). | M[DP].bit         | The value of memory bit which is addressed by DPTR and bit.                       |

| @        | Prefix for indirect address                                                        | Pm.n              | Value of bit n of I/O port m.                                                     |

| $\leq$   | Less than or equal to                                                              | •                 | Value of PC for current instruction.                                              |

| <b>←</b> | Transfer                                                                           | $\leftrightarrow$ | Exchange                                                                          |

| =        | Equal to                                                                           | #                 | Not equal to                                                                      |

| >        | Greater than                                                                       | <                 | Less than                                                                         |

| +        | Addition                                                                           | -                 | Subtraction                                                                       |

| &        | Bitwise logical AND                                                                | I                 | Bitwise logical OR                                                                |

| ^        | Bitwise logical Exclusive-OR                                                       | ~                 | Bitwise logical complement                                                        |

| {b,b}    | Concatenation of bits                                                              |                   |                                                                                   |

ATOM1.0 Family

[42]

## Appendix A: Instruction Set (2/19)

**Preliminary**

#### OPCODE Map

| H | 0                | 1                  | 2                      | 3                      | 4                 | 5                     | 6          | 7          | 8                | 9                 | Α     | В                | С                | D                | Е                | F        |

|---|------------------|--------------------|------------------------|------------------------|-------------------|-----------------------|------------|------------|------------------|-------------------|-------|------------------|------------------|------------------|------------------|----------|

| 0 | NOP              | SETB<br>C          | PUSH<br>A              | POP<br>A               | INC<br>DPTR       | DEC<br>DPTR           | INC<br>@DP | DEC<br>@DP | ADD<br>A,<br>@DP | ADDC<br>A,<br>@DP | CPL A | SUB<br>A,<br>@DP | ANL<br>A,<br>@DP | ORL<br>A,<br>@DP | XRL<br>A,<br>@DP | RRC<br>A |

| 1 | CLR C            | INC A              | ADD A,                 | #data                  |                   |                       |            |            |                  |                   |       |                  |                  |                  |                  | DEC<br>A |

| 2 | MOV L,           | #data              |                        |                        |                   |                       |            |            |                  |                   |       |                  |                  |                  |                  |          |

| 3 | MOV H, #data     |                    |                        |                        |                   |                       |            |            |                  |                   |       |                  |                  |                  |                  |          |

| 4 | MOVI @DP, #data  |                    |                        |                        |                   |                       |            |            |                  |                   |       |                  |                  |                  |                  |          |

| 5 | CLR A            | CLR A MOV A, #data |                        |                        |                   |                       |            |            |                  |                   |       |                  |                  |                  |                  |          |

| 6 | MOV dir, A       |                    |                        |                        |                   |                       |            |            |                  |                   |       |                  |                  |                  |                  |          |

| 7 | MOV A,           | dir                |                        |                        |                   |                       |            |            |                  |                   |       |                  |                  |                  |                  |          |

| 8 | MOV<br>A,<br>@DP | XCH<br>A,<br>@DP   | MOV<br>L,<br>@DP       | MOV<br>@DP,<br>A       | MOVI<br>@DP,<br>A | MOV<br>D<br>@DP,<br>A | CLR<br>@L  | SETB<br>@L | CLR bit          |                   |       |                  | SETB bi          | t                |                  |          |

| 9 | RET              | DJNZ<br>A, rel     | CJNE<br>A,@D<br>P, rel | CJLE<br>A,@D<br>P, rel |                   |                       | JNC<br>rel | JC rel     | JNB bit,         | , rel             |       |                  | JB bit, r        | el               |                  |          |

| Α | CJNE L,          | #data, re          | el                     |                        |                   |                       |            |            |                  |                   |       |                  |                  |                  |                  |          |

| В | CJNE @           | DP, #data          | a, rel                 |                        |                   |                       |            |            |                  |                   |       |                  |                  |                  |                  |          |

| С | CJNE A,          | #data, re          | el                     |                        |                   |                       |            |            |                  |                   |       |                  |                  |                  |                  |          |

| D | CJNE A,          | dir, rel           |                        |                        |                   |                       |            |            |                  |                   |       |                  |                  |                  |                  |          |

| Е | JMP add          | dr                 |                        |                        |                   |                       |            |            |                  |                   |       |                  |                  |                  |                  |          |

| F | CALL ad          | ldr                |                        |                        |                   |                       |            |            |                  |                   |       |                  |                  |                  |                  |          |

ATOM1.0 Family

[43]

# Appendix A: Instruction Set (3/19)

## Preliminary

| ADD A, #data                                                       |                                                                                                                                                                                                                                                         | ADDC A, @DP                                         |                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Binary Code Description  Operation Carry Flag Bytes Cycles Example | O001 dddd  Adds the 4-bit data to the Accumulator.  The result is stored in Accumulator.  When adding unsigned integers, the carry flag indicates an overflow.  (A) ← (A) + #data  Set if a carry occurred, cleared otherwise.  1  1  CLR A ; Clear ACC | Binary Code Description  Operation Carry Flag Bytes | Simultaneously adds the contents of indirect data memory, the carry flag and the Accumulator. The result is stored in Accumulator.  When adding unsigned integers, the carry flag indicates an overflow.  (A) ← (A) + M[DP] + (C)  Set if a carry occurred, cleared otherwise. |

| Lxample                                                            | ADD A, #2 ; Add 2 to ACC. ACC contains 2.                                                                                                                                                                                                               | Cycles<br>Example                                   | 1 ; Assumes M[DP] contains 2 and C is 1.                                                                                                                                                                                                                                       |

| ADD A, @DP                                                         |                                                                                                                                                                                                                                                         |                                                     | MOV A, #8 ; Set ACC as 8.                                                                                                                                                                                                                                                      |

| Binary Code Description Operation Carry Flag                       | 0000 1000  Adds the contents of indirect data memory to the Accumulator. The result is stored in Accumulator. When adding unsigned integers, the carry flag indicates an overflow.  (A) ← (A) + M[DP]  Set if a carry occurred, cleared otherwise.      |                                                     | ADDC A, @DP; The result, 11 is stored in ACC.                                                                                                                                                                                                                                  |