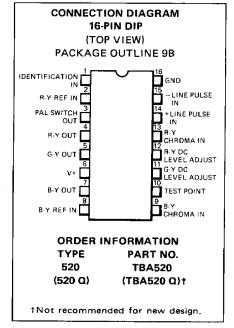

# TBA520 PAL TV CHROMA DEMODULATOR

FAIRCHILD LINEAR INTEGRATED CIRCUIT

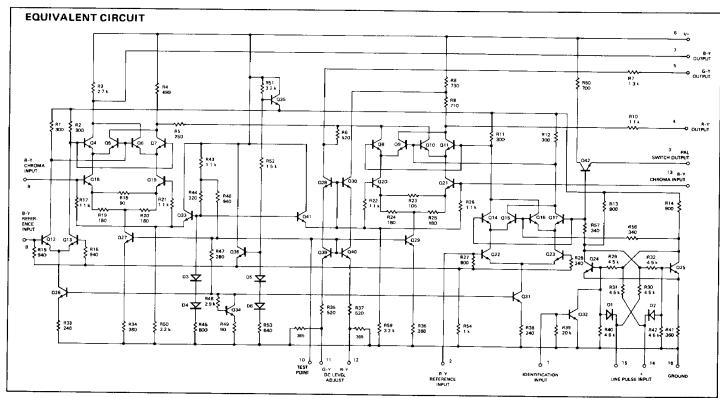

**GENERAL DESCRIPTION** — The TBA520 is a synchronous demodulator for direct drive of color video output stages. It is constructed on a single silicon chip using the Fairchild Planar\* epitaxial process. The TBA520 is designed for use in color television receivers, operating on the Phase Alternate Line {PAL} system. This circuit consists of two synchronous demodulators, a decoding matrix and a PAL switch with internal multivibrator.

- DOUBLE BALANCED SYNCHRONOUS DEMODULATOR

- INTERNAL DECODING MATRIX

- INTERNAL PAL SWITCH

- PROVISION FOR OUTPUT DC LEVEL MATCHING

### **ABSOLUTE MAXIMUM RATINGS**

Supply Voltage

Internal Power Dissipation

Voltage on Identification Input

Current into Identification Input

Operating Temperature Range

Storage Temperature Range

Pin Temperature (Soldering, 10 s)

phistic ge Quip

13.2 V 550 mW 5.0 V 1.0 mA -20°C to +60°C -55°C to +125°C 260°C

## **FAIRCHILD • TBA520**

| CHARACTERISTICS                                                 | CONDITIONS                                                  | MIN  | TYP      | MAX | UNITS              |

|-----------------------------------------------------------------|-------------------------------------------------------------|------|----------|-----|--------------------|

| Supply Current (I <sub>6</sub> )                                |                                                             |      | 32       |     | mA                 |

| Color Difference Gain                                           |                                                             |      |          |     |                    |

| R-Y Channel                                                     |                                                             |      | 7.0      |     | V/V                |

| B-Y Channel                                                     | $V_9 = V_{13} = 50 \text{ mV}_{pk-pk}, f = 4.4 \text{ MHz}$ |      | 12.5     |     | V/V                |

| G-Y Channel                                                     |                                                             |      | (Note 1) |     |                    |

| Maximum Color Difference Output Voltage (Notes 2,3)             |                                                             |      |          |     |                    |

| R-Y Output (V <sub>4 pk-pk</sub> )                              | (Notes 2,3)                                                 |      | 3.2      |     | V <sub>pk-pk</sub> |

| B-Y Output (V <sub>7 pk-pk)</sub>                               | ·                                                           |      | 4.0      |     | V <sub>pk-pk</sub> |

| G-Y Output (V <sub>5 pk-pk</sub> )                              |                                                             |      | 1.8      |     | V <sub>pk-pk</sub> |

| Color Difference dc Output Voltage                              |                                                             |      |          |     |                    |

| R-Y Output (V <sub>4</sub> )                                    |                                                             |      | 7.9      |     | V                  |

| B-Y Output (V <sub>7</sub> )                                    |                                                             |      | 7.9      |     | V                  |

| G-Y Output (V <sub>5</sub> )                                    |                                                             |      | 7.9      |     | V                  |

| Input Resistance of Chroma Inputs (R9, R13)                     | V9 = V <sub>13</sub> = 20 mVrms (Sinusoidal)                | 800  |          |     | Ω                  |

| Input Capacitance of Chroma Inputs (C9, C13)                    | f = 4.4 MHz                                                 |      |          | 10  | pF                 |

| Output Resistance at Color Difference<br>Terminals (R4, R5, R7) |                                                             |      | 2.7      |     | kΩ                 |

| Input Resistance of Reference Inputs (R2, R8)                   |                                                             |      | 1.0      |     | kΩ                 |

| Peak-to-Peak PAL Switch Output Voltage<br>(V3 pk-pk)            | (Note 4)                                                    |      | 2.5      |     | V <sub>pk-pk</sub> |

| Activation Threshold Voltage (V <sub>1</sub> )                  | Identification O' (1) A di                                  | 0.75 | -        |     | V                  |

| Activation Threshold Current (I <sub>1</sub> )                  | Identification Circuit is Active                            | 80   |          |     | μА                 |

| Deactivation Threshold Voltage (V <sub>1</sub> )                | Identification Circuit is Inactive                          |      |          | 0.4 | V                  |

- 1. G-Y output is typically equal to -0.51 (R-Y) -0.19 (B-Y).

- Gain is equal to 0.7 of small signal gain.

- 3. Reference input ( $V_{2pk-pk}$  and  $V_{8pk-pk}$ ) range is 0.5 V to 2.0 V. 4.  $f_{out} = 0.5 \times$  line pulse frequency;  $V_{14} = V_{15} = -3.0 \, \text{V}$  to  $-4.5 \, \text{V}$  (peak).

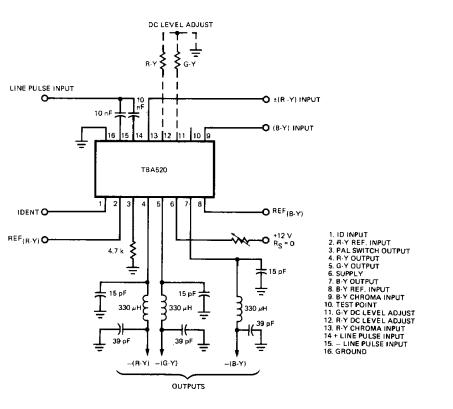

# **TEST CIRCUIT**

#### APPLICATION INFORMATION

The function is quoted against the corresponding pin numbers,

#### 1. Identification bias

The input current required to stop the flip-flop, "Ident on":  $I_{ON} \ge 80 \,\mu A$ . For "Ident off":  $V_{Off} = -5.0 \, \text{to} + 0.4 \, \text{V}$ .

#### 2. R-Y subcarrier reference input

An 1.0 V peak-to-peak signal is required via a dc blocking capacitor. Under no circumstances should this signal be less than 0.5 V peak-to-peak. The input resistance at this pin is typically  $1 \,\mathrm{k}\Omega$ .

- 3. PAL square wave output The amplitude is 2.5 V peak-to-peak from an emitter follower.

- 4. R-Y signal output (G-Y at pin 5 and B-Y at pin 7)

No external dc load needed except that direct connection must be made via the low pass filter to the R G B matrix of the TBA530.

The signals produced are in the following ratios:

$$V_{B-Y} = 1.3 V_{R-Y}$$

(a)

$$V_{G-Y} = 0.76 V_{R-Y}$$

(b)

$$V_{G-Y} = 0.26 V_{R-Y}$$

Condition (a) refers to (B-Y) + (R-Y) addition in the G-Y matrix. Condition (b) refers to the phase reversed (R-Y) input signal where (G-Y) is obtained by subtraction.

The dc levels should each be adjusted, starting with the (B-Y) to +7.5 V at nominal supply voltage.

The maximum peak-to-peak voltages for the condition m ≥ 0.7 (m = ratio of minimum to maximum differential gains) are:

$$V_{R-Y(pk-pk)} = 3.2 V$$

$$V_{G-Y(pk-pk)} = 1.8 V$$

$$V_{B-Y(pk-pk)} = 4.0 V$$

The output impedance for each signal is 2.7 k $\Omega$ .

The drifts in dc levels of the color difference output signals for a change in ambient temperature of 40°C (after equilibrium is reached from switch-on) are typically:

| Absolute shift                                | -50 to +50 mV             |

|-----------------------------------------------|---------------------------|

| VR-Y relative to VB-Y                         | $-20$ to $+20\mathrm{mV}$ |

| V <sub>G-Y</sub> realtive to V <sub>B-Y</sub> | $-20$ to $+20\mathrm{mV}$ |

| VB-Y relative to VG-Y                         | -20 to +20 mV             |

The changes in do level with supply voltage are approximately linear and track together,

The  $-3.0\,\mathrm{dB}$  bandwidth of the color difference signals is 1.5 MHz.

- 5. G-Y signal output (see pin 4)

- 6. Positive supply

Also do level setting for B-Y output (pin 7). The maximum allowable voltage on this pin is 13.2 V. The minimum supply voltage to insure setting the B-Y output do level correctly (+7.5 V) is 11.6 V (in such case R<sub>S</sub> would be set to zero).

- 7. B-Y signal output (see pin 4)

- 8. B-Y subcarrier reference input The requirements here are identical with those for pin 2.

- 9. Chrominance B-Y input signal

An input signal up to 360 mV peak-to-peak (color bars) is advisable. For driving the TBA530 an input signal of 160 mV is required.

- 19. Internally connected No external connection should be made.

- 11. DC level setting for G-Y output signal (circuit diagram on page 2).

- 12. DC level setting for R-Y output (see circuit diagram on page 2).

- 13. Chrominance R-Y input signal

An input signal up to 500 mV peak-to-peak (color bars) is advisable. The input impedance is the same as for pin 9.

#### 14. Line pulse input (flip-flop synchronizing)

A 4.0 V peak negative going line flyback pulse should be applied via separate 10 nF capacitors to pins 14 and 15. Pulse amplitude to lie between 3.0 V and 4.5 V peak-to-peak.

15. Line pulse input (see pin 14).

16. Ground.

#### **BLOCK DIAGRAM** B-Y OUTPUT G-Y OUTPUT TEST POINT B Y OUTPUT SUPPLY 👌 6 RESISTOR 8-Y DEMODULATOR CURRENT → R-Y REFERENCE REFERENCE SWITCH EMITTER FOLLOWER GROUND 616 FLIP-FLOP DENTIFICATION 13 R-Y CHROMA INPUT G-Y DC LEVEL ADJUST R-Y DC LEVEL ADJUST