# SONY

# **CXD2085M**

# **ID-1** Detection

# Description

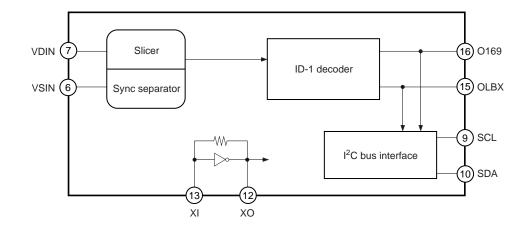

The CXD2085M is an IC which has the function of detecting ID-1 (EIAJ, CPX1204) from the video signal.

# Features

- · Can detect the ID-1 signal on the NTSC video signal.

- Includes I<sup>2</sup>C bus interface. Also, IC can operate without the I<sup>2</sup>C bus.

- Includes a 2-bit general-purpose I/O port function. (When using I<sup>2</sup>C bus)

# Applications

TVs

# Structure

Silicon gate CMOS IC

# Absolute Maximum Ratings

| <ul> <li>Supply voltage</li> </ul> | Vdd | Vss – 0.5 to +7.0      | V |

|------------------------------------|-----|------------------------|---|

| <ul> <li>Input voltage</li> </ul>  | Vı  | Vss - 0.5 to Vdd + 0.5 | V |

| <ul> <li>Output voltage</li> </ul> | Vo  | Vss - 0.5 to Vdd + 0.5 | V |

• Storage temperature

°C -55 to +150 Tstg

# **Recommended Operating Conditions**

Supply voltage Vdd 4.75 to 5.25 V

Operating temperature Topr

°C -20 to +70

# **Block Diagram**

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

# **Pin Description**

| Pin No. | Symbol | I/O | Input level | Description                                                                                                                    |

|---------|--------|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------|

| 1       | XRST   | Ι   | TTL*1, *4   | Reset at "0".                                                                                                                  |

| 2       | TST    | I   | TTL*2       | Test input; connect to Vss.                                                                                                    |

| 3       | MCON   | I   | CMOS        | Switching between use and no use of $I^2C$ bus; No $I^2C$ bus when Low.                                                        |

| 4       | ISET   | I   | ANALOG      | Bias current setting.                                                                                                          |

| 5       | AVdd   |     |             | Analog power supply.                                                                                                           |

| 6       | VSIN   | I   | ANALOG      | Sync separation input.                                                                                                         |

| 7       | VDIN   | Ι   | ANALOG      | Data slicer input.                                                                                                             |

| 8       | AVss   |     |             | Analog GND.                                                                                                                    |

| 9       | SCL    | Ι   | CMOS*1      | l <sup>2</sup> C bus clock.                                                                                                    |

| 10      | SDA    | I/O | CMOS*1, *3  | I <sup>2</sup> C bus data.                                                                                                     |

| 11      | Vdd    |     |             | Digital power supply.                                                                                                          |

| 12      | хо     | 0   |             | Oscillator connection. (14.318MHz)                                                                                             |

| 13      | XI     | I   | CMOS        | Oscillator connection, or clock input.                                                                                         |

| 14      | Vss    |     |             | Digital GND.                                                                                                                   |

| 15      | OLBX   | I/O | TTL         | Letter-box bit output when ID detection result is output.<br>Or, general-purpose I/O port by the I <sup>2</sup> C bus setting. |

| 16      | O169   | I/O | TTL         | Full-mode bit output when ID detection result is output.<br>Or, general-purpose I/O port by the I <sup>2</sup> C bus setting.  |

\*1 Schmitt input \*2 With pull-down resistor \*3 Open drain \*4 With pull-up resistor

Connect SCL (Pin 9) to Vss in no  $I^2C$  bus mode with MCON (Pin 3) to Low. Connect SDA (Pin 10) to Vss or VDD in no  $I^2C$  bus mode.

# **Electrical Characteristics**

# DC Characteristics (Logic section)

$(V_{DD} = 5.0V \pm 5\%, V_{SS} = 0V, Ta = 25^{\circ}C)$

| Item                | Symbol | Conditions                 | Min.              | Тур. | Max.              | Unit | Remarks                |  |

|---------------------|--------|----------------------------|-------------------|------|-------------------|------|------------------------|--|

|                     | Vон    | Іон = –2mA                 | Vdd - 0.8         |      |                   | V    | Dine 45 40             |  |

| Output voltage      | Vol    | IoL = 4mA                  |                   |      | 0.4               | V    | Pins 15, 16            |  |

| Output valtage      | Vон    | Іон = –3mA                 | Vdd/2             |      |                   | V    | Pin 12                 |  |

| Output voltage      | Vol    | IoL = 3mA                  |                   |      | Vdd/2             | V    |                        |  |

| Output voltage      | Vol    | IoL = 3mA                  |                   |      | 0.4               | V    | Pin 10                 |  |

| Input voltage       | Vін    |                            | 2.0               |      |                   | V    | Dine 45 40             |  |

| input voltage       | VIL    |                            |                   |      | 0.8               | V    | Pins 15, 16            |  |

|                     | Vін    |                            | 2.2               |      |                   | V    | Direc 4, 0             |  |

| Input voltage       | VIL    |                            |                   |      | 0.8               | V    | Pins 1, 2              |  |

| Input voltogo       | Vін    |                            | 0.7 	imes Vdd     |      |                   | V    | Dine 2, 42             |  |

| Input voltage       | VIL    |                            |                   |      | 0.3 	imes Vdd     | V    | Pins 3, 13             |  |

| Input voltage       | Vін    |                            | $0.8 \times V$ dd |      |                   | V    | Dine 0, 40             |  |

| input voltage       | VIL    |                            |                   |      | $0.2 \times V$ DD | V    | Pins 9, 10             |  |

| Input hysteresis    | Vhys   |                            |                   | 0.6  |                   | V    | Pins 9, 10             |  |

| width               | VIIyS  |                            |                   | 0.4  |                   | V    | Pin 1                  |  |

| Input leak current  | li     | VIN = Vss or VDD           | -10               |      | +10               | μA   | Pins 3, 9              |  |

| Output leak current | loz    | VIN = Vss or VDD           | -40               |      | +40               | μA   | Pins 10, 15, 16        |  |

| Input current       | li     | VIN = Vss                  | -40               | -100 | -240              | μA   | Pin 1                  |  |

| Input current       | li     | Vin = Vdd                  | 40                | 100  | 240               | μA   | Pin 2                  |  |

| Feedback resistance | Rfbk   | XI (Pin 13) = Vss or VDD   | 250k              | 1M   | 2.5M              | Ω    | Between Pins 12 and 13 |  |

| Current consumption | Idd    | Clock frequency: 14.318MHz |                   | 9    |                   | mA   | Sum of Pins 5 and 11   |  |

## **AC Characteristics**

$(V_{DD} = 5.0V \pm 5\%, V_{SS} = 0V, Ta = 25^{\circ}C)$

| Item            | Symbol | Conditions | Min. | Тур.   | Max. | Unit | Remarks                                                  |

|-----------------|--------|------------|------|--------|------|------|----------------------------------------------------------|

| Clock frequency | fxi    |            |      | 14.318 |      | MHz  | Pin 13 input, or<br>oscillator between<br>Pins 12 and 13 |

## I/O Pin Capacitance

| Item                   | Symbol | Conditions                    | Min. | Тур. | Max. | Unit | Remarks |

|------------------------|--------|-------------------------------|------|------|------|------|---------|

| Input pin capacitance  | CIN    | $V_{DD} = V_I = 0V, f = 1MHz$ |      |      | 9    | pF   |         |

| Output pin capacitance | Соит   | $V_{DD} = V_I = 0V, f = 1MHz$ |      |      | 11   | pF   |         |

| I/O pin capacitance    | CI/O   | $V_{DD} = V_I = 0V, f = 1MHz$ |      |      | 11   | pF   |         |

# Pin and Electrical Characteristics

# Analog Section

$(V_{DD} = 5.0V \pm 5\%, V_{SS} = 0V, T_a = 25^{\circ}C)$

| Pin<br>No. | Symbol | Equivalent circuit                                                                                       | Description                                                                           |

|------------|--------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| 5          | AVDD   | Not connected to VDD (Pin 11) in the IC.                                                                 | Analog power supply.<br>Connect a low-noise power supply from the digital system.     |

| 8          | AVss   | Not connected to Vss (Pin 14) in the IC.                                                                 | Analog ground.<br>Connect to the same potential as Vss.                               |

| 4          | ISET   | AVDD<br>(4)<br>TTTTTTTTTTTTTTTTTTTTTTTTTTTTTTTTTTTT                                                      | Bias setting.<br>Connect to AVod (Pin 5) with 33kΩ.                                   |

| 6          | VSIN   | AVDD<br>6<br>4<br>4<br>6<br>4<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7 | Sync tip clamp, sync separation input.<br>Input with the capacitance coupled.         |

| 7          | VDIN   | AVDD<br>7<br>AVSS                                                                                        | Pedestal clamp,<br>ID signal data slice input.<br>Input with the capacitance coupled. |

**1. Description of ID-1 (transmission system of additional video information, aspect ratio identification)** As shown in the table below, the additional video information consists of 14-bits data, and a 6-bit CRCC is added to the data to form 20-bit data in total. This is carried on lines 20 and 283 in the vertical blanking area of the NTSC video signal.

# Table 1. Description of ID-1 signal

|                                                                                                                            | Bit No |             | Description                                                                                                                                         | "1"                            | "0"                |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------|--------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------|--|--|--|

| WORD0                                                                                                                      | A      | 1<br>2<br>3 | Transmission aspect ratio<br>Screen display format<br>Not defined                                                                                   | Full-mode (16:9)<br>Letter-box | 4:3<br>Normal<br>— |  |  |  |

| WORDU                                                                                                                      | В      | 4<br>5<br>6 | Identification information relating to the video signals and other signals (auc<br>signals, etc.) transmitted simultaneously with the video signals |                                |                    |  |  |  |

| WORD14bitsIdentification signal dependent on WORD0WORD24bitsIdentification signal and other information dependent on WORD0 |        |             |                                                                                                                                                     |                                | RD0                |  |  |  |

(From the Provisional standard of EIAJ, CPX-1204)

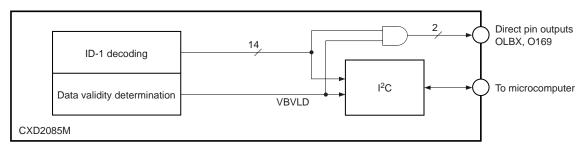

In the CXD2085M, the above 14-bit data are obtained in the I<sup>2</sup>C bus for I<sup>2</sup>C bus mode. Also, first two bits only can be output to OLBX (Pin 15) and O169 (Pin 16) set as the direct output pins.

# 2. Difference between ID-1 Data from the I<sup>2</sup>C Bus and Direct Output Pin

As shown in the figure above, the data validity determination which detects that the valid ID signal is exist or not, and the decoded result are obtained independently during ID-1 decoding. These two results are output to the direct output pins after taking their logical AND.

Processing inside the microcomputer which has acquired the information from the I<sup>2</sup>C bus is performed either by simply outputting this data directly to the pins or by taking the logical AND as above.

In addition, performing the processing when the data validity determination (VBVLD) is "1" and the decoding results bits 1 and 2 are "0" allows the video to be identified as 4:3 video.

# 3. General-Purpose I/O Port Function

In I<sup>2</sup>C bus mode, the CXD2085M can use two pins OLBX (Pin 15) and O169 (Pin 16) as the general-purpose I/O ports. The three types of setting are available; both two pins for inputs, for outputs, and one for input and another for output. While resetting by XRST (Pin 1) in I<sup>2</sup>C bus mode, two pins are set as the general-purpose input ports. Perform the power-on reset by XRST when there is a possibility that the IC external circuit and the OLBX and O169 signals could collide. Be sure to set the OLBX and O169 pins as the output pins when they are not used.

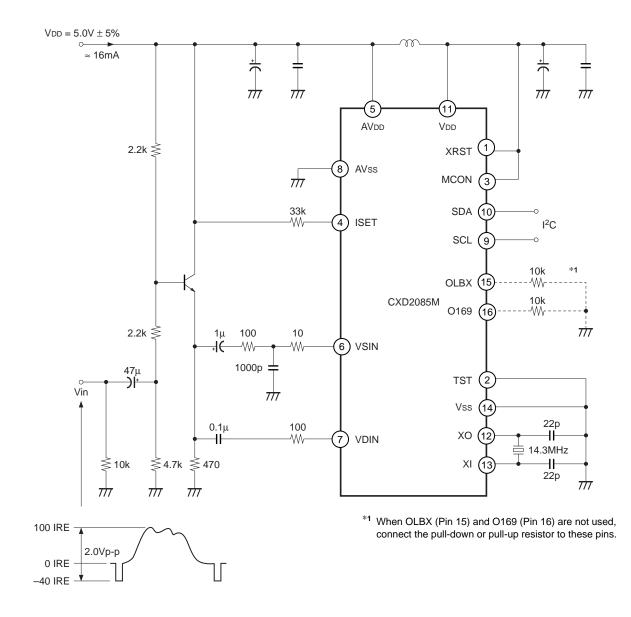

# 4. Clock

The CXD2085M requires a 4fsc clock (14.318MHz). When using a crystal oscillator, connect it between XI (Pin 13) and XO (Pin 12).

When inputting the clock from an external source, input it to XI (Pin 13).

# 5. Various Settings and Data I/O

The various settings and data I/O can be made by using the pin directly or using I<sup>2</sup>C bus interface.

# 5-1. I<sup>2</sup>C bus

By setting MCON (Pin 3) to High, the various settings and data extraction can be made with the I<sup>2</sup>C bus.

The CXD2085M supports the I<sup>2</sup>C bus slave RECEIVER and slave TRANSMITTER modes. The slave address is 40 (H).

In addition to standard mode (max. 100K bits/s), this IC also supports high-speed mode (max. 400K bits/s). Even when the power supply falls to 0V, it does not occupy the I<sup>2</sup>C bus. However, the absolute maximum ratings should not be exceeded.

The I<sup>2</sup>C bus transmission process is shown in the figure below.

The number of transmission data is one byte for write (RECEIVER) and two bytes for read (TRANSMITTER). There is no sub-address setting function. Note that the I<sup>2</sup>C bus transmission cannot be performed during resetting by the XRST pin (Pin 1).

# Data write (RECEIVER mode)

|    | 7654321 | 0  | 1  | 76543210 | 1  |   |

|----|---------|----|----|----------|----|---|

| Sm | SLAm    | Wm | As | DATAm    | As | Р |

# Data read (TRANSMITTER mode)

|    | 7654321 | 0  | 1  | 76543210 | 1  | 76543210 | 1   |   |

|----|---------|----|----|----------|----|----------|-----|---|

| Sm | SLAm    | Rm | As | DATAs    | Am | DATAs    | XAm | Р |

| Symbol | Description                             |  |  |  |  |

|--------|-----------------------------------------|--|--|--|--|

| *m     | from Master to Slave                    |  |  |  |  |

| *s     | from Slave to Master                    |  |  |  |  |

| S      | Start Condition                         |  |  |  |  |

| Р      | Stop Condition                          |  |  |  |  |

| SLA    | Slave Address                           |  |  |  |  |

| DATA   | Data                                    |  |  |  |  |

| W      | 0: Write Master $\rightarrow$ Slave     |  |  |  |  |

| R      | 1: Read Slave $\rightarrow$ Master      |  |  |  |  |

| A      | Clock pulse for Acknowledgment (SDA: L) |  |  |  |  |

| XA     | Acknowledgment none (SDA: H)            |  |  |  |  |

- 6 -

# Table 2. List of I<sup>2</sup>C bus controls

| R/W |                                                                                                                                                                             | E    | Bit                           | Symbol |                                                                                                                                             |                                                                              | Descriptio                         | n         |            |             |       |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------|-----------|------------|-------------|-------|

|     |                                                                                                                                                                             | bit7 | MSB                           | POLBX  | OLBX Output value when the OLBX pin used as the general-purpose output port.                                                                |                                                                              |                                    |           |            |             |       |

|     |                                                                                                                                                                             | bit6 |                               | PO169  | Ou                                                                                                                                          | tput value when the O1                                                       | 69 pin used as                     | the gene  | ral-purpos | se output p | port. |

|     |                                                                                                                                                                             |      |                               |        |                                                                                                                                             | ttings whether the OLB<br>of decoding result or a                            |                                    |           |            | e direct o  | utput |

|     |                                                                                                                                                                             | bit5 |                               | PORT2  |                                                                                                                                             | PORT2                                                                        | 0                                  | 0         | 1          | 1           |       |

|     |                                                                                                                                                                             |      |                               |        |                                                                                                                                             | PORT1                                                                        | 0                                  | 1         | 0          | 1           |       |

|     |                                                                                                                                                                             |      |                               |        |                                                                                                                                             | OLBX pin function                                                            | Direct output                      | Genera    | -purpose   | I/O port    |       |

|     | e                                                                                                                                                                           |      |                               |        |                                                                                                                                             |                                                                              |                                    | Output    | Input      | Input       |       |

| WR  | st byte                                                                                                                                                                     | bit4 |                               | PORT1  |                                                                                                                                             | O169 pin function                                                            | Direct output                      | General   | -purpose   | I/O port    |       |

|     | - <u></u>                                                                                                                                                                   |      |                               |        |                                                                                                                                             |                                                                              |                                    | Output    | Output     | Input       |       |

|     |                                                                                                                                                                             | bit3 |                               | TST    | Te                                                                                                                                          | st signal. Be sure to se                                                     | t to Low.                          |           |            |             |       |

|     |                                                                                                                                                                             | bit2 |                               | XJGLK  | Normally set to Low When Low the decoding re                                                                                                |                                                                              |                                    |           |            |             |       |

|     | bit1 LNJ1 Normally set to Low. When Low, the ID signal car<br>the line where it should locate but for one line before<br>decoding is performed only to the line where the I |      |                               |        |                                                                                                                                             |                                                                              | he before and after it. When High, |           |            |             |       |

|     |                                                                                                                                                                             | bit0 | LSB                           | RES    | Normally set to Low. When High, the decoding function is reset. Reset immediately after switching the input signal such as for TV channels. |                                                                              |                                    |           |            |             |       |

|     |                                                                                                                                                                             | bit7 | MSB                           | ID5    | ID                                                                                                                                          | decoding result 5th bit.                                                     |                                    |           |            |             |       |

|     |                                                                                                                                                                             | bit6 |                               | ID4    | ID                                                                                                                                          | decoding result 4th bit.                                                     |                                    |           |            |             |       |

|     |                                                                                                                                                                             | bit5 |                               | ID3    | B ID decoding result 3rd bit.                                                                                                               |                                                                              |                                    |           |            |             |       |

|     | e                                                                                                                                                                           | bit4 |                               | ID1    | ID                                                                                                                                          | decoding result 1st bit.                                                     |                                    |           |            |             |       |

|     | 1st byte                                                                                                                                                                    | bit3 |                               | ID2    | ID                                                                                                                                          | decoding result 2nd bit                                                      | •                                  |           |            |             |       |

|     | <del>,</del>                                                                                                                                                                | bit2 |                               | VBVLD  | Hig                                                                                                                                         | h when the valid ID sig                                                      | gnal is detected                   | d.        |            |             |       |

|     |                                                                                                                                                                             | bit1 |                               | IOLBX  | Inp                                                                                                                                         | ut value when OLBX is                                                        | s used as the g                    | jeneral-p | urpose in  | put port.   |       |

| RD  |                                                                                                                                                                             | bit0 | LSB                           | IO169  | ID                                                                                                                                          | ut value when O169 is<br>decoding result 14th bi<br>put port or as the direc | t when O169 is                     | •         | • •        | •           | ose   |

|     |                                                                                                                                                                             | bit7 | MSB                           | ID13   | ID                                                                                                                                          | decoding result 13th bi                                                      | t.                                 |           |            |             |       |

|     |                                                                                                                                                                             | bit6 |                               | ID12   | D12 ID decoding result 12th bit.                                                                                                            |                                                                              |                                    |           |            |             |       |

|     |                                                                                                                                                                             | bit5 |                               | ID11   | ID                                                                                                                                          | decoding result 11th bi                                                      | t.                                 |           |            |             |       |

|     | bit4 ID10                                                                                                                                                                   |      | ID10                          | ID     | decoding result 10th bi                                                                                                                     | t.                                                                           |                                    |           |            |             |       |

|     | 2nd byte                                                                                                                                                                    | bit3 | ID9 ID decoding result 9th bi |        |                                                                                                                                             | decoding result 9th bit.                                                     |                                    |           |            |             |       |

|     |                                                                                                                                                                             | bit2 |                               | ID8    | ID                                                                                                                                          | decoding result 8th bit.                                                     |                                    |           |            |             |       |

|     |                                                                                                                                                                             | bit1 |                               | ID7    | ID                                                                                                                                          | decoding result 7th bit.                                                     |                                    |           |            |             |       |

|     |                                                                                                                                                                             | bit0 | LSB                           | ID6    | ID                                                                                                                                          | decoding result 6th bit.                                                     |                                    |           |            |             |       |

# 5-2. No bus mode

No bus mode is established when setting the MCON pin (Pin 3) to Low and then the CXD2085M can be operates without using the  $I^2C$  bus.

In this case, the contents to be set by the I<sup>2</sup>C bus is fixed as shown below. OLBX and O169 obtain the decoding results as they become the direct output pins.

| R/W |        | Bit            | Symbol                                                                              | Contents                                                                                           |

|-----|--------|----------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

|     |        | bit7 MSB POLBX | Fixed to Low. In no I <sup>2</sup> C bus mode, there is no general-purpose I/O port |                                                                                                    |

|     |        | bit6           | PO169                                                                               | function and this bit's operation is not affected.                                                 |

|     |        | bit5           | PORT2                                                                               | PORT1 and PROT2 fixed to Low. The OLBX and O169 pins are the                                       |

|     | byte   | bit4           | PORT1                                                                               | direct output pins of the ID decoding result.                                                      |

| WR  | 1st by | bit3           | TST                                                                                 | SCL (Pin 9) input reflected as it is. Therefore, connect the SCL pin to Vss in no $I^2C$ bus mode. |

|     |        | bit2           | XJGLK                                                                               | SCL (Pin 9) input reflected as it is. Fixed to Low as the SCL pin is surely                        |

|     |        | bit1           | LNJ1                                                                                | connected to Vss.                                                                                  |

|     |        | bit0 LSB       | RES                                                                                 | Fixed to Low. When resetting is required, use the XRST pin (Pin 1).                                |

Table 3. Settings in No Bus Mode (Pin 3, MCON = Low)

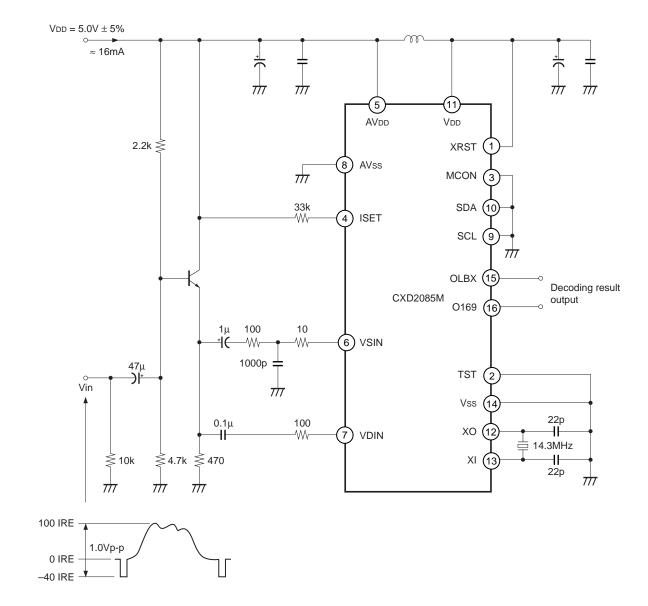

#### Application Circuit For 2Vp-p input amplitude, using the I<sup>2</sup>C bus

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

# Application Circuit For 1Vp-p input amplitude not using the I<sup>2</sup>C bus

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

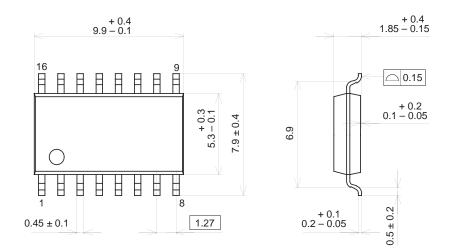

Package Outline Unit: mm

16PIN SOP (PLASTIC)

| PACKAGE STRUCTURE |

|-------------------|

|-------------------|

| SONY CODE  | SOP-16P-L01   |

|------------|---------------|

| EIAJ CODE  | SOP016-P-0300 |

| JEDEC CODE |               |

| r                |                |

|------------------|----------------|

| PACKAGE MATERIAL | EPOXY RESIN    |

| LEAD TREATMENT   | SOLDER PLATING |

| LEAD MATERIAL    | COPPER ALLOY   |

| PACKAGE MASS     | 0.2g           |