# M66330SP/FP

#### BAND COMPRESSION AND EXPANSION CONTROLLER

#### **DESCRIPTION**

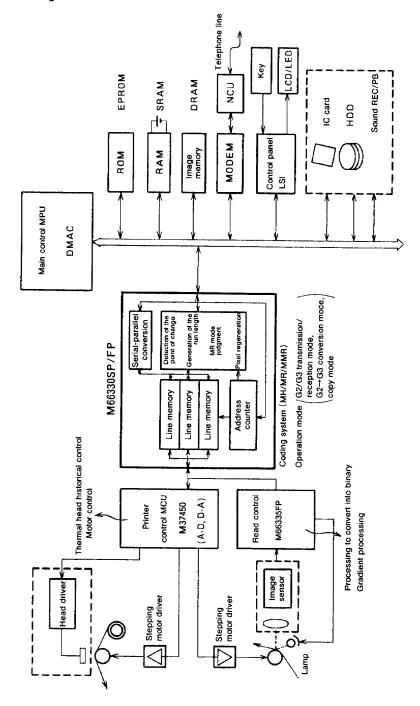

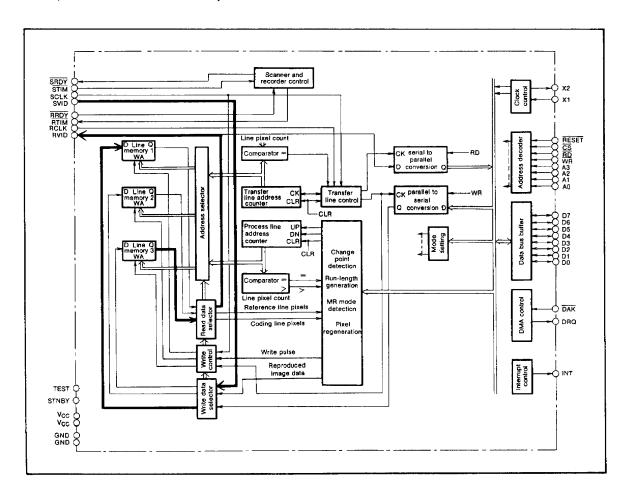

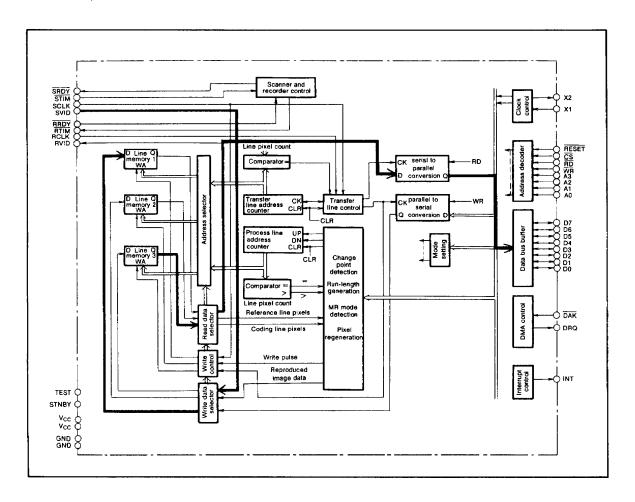

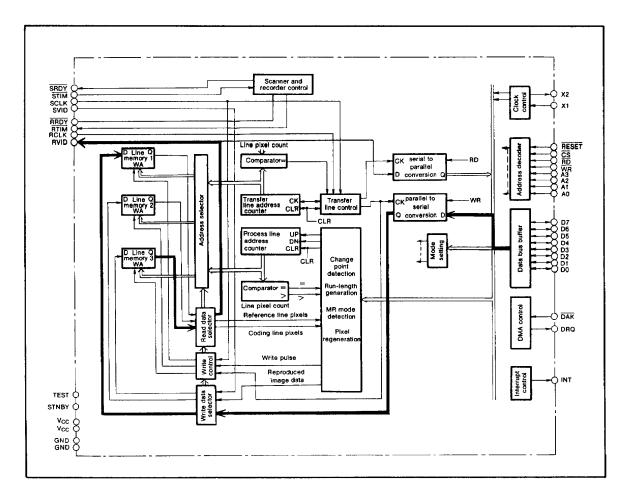

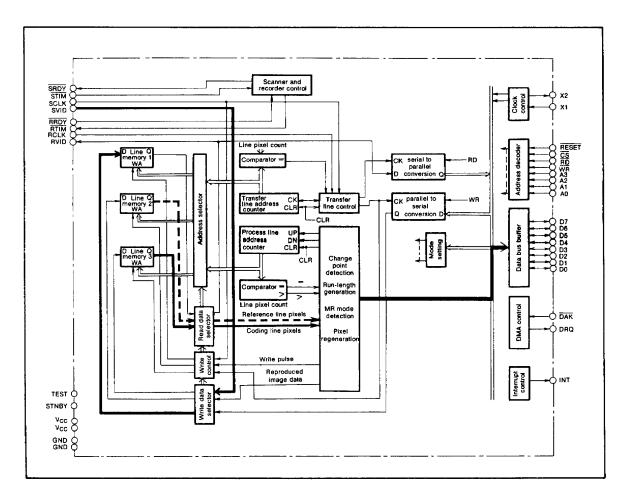

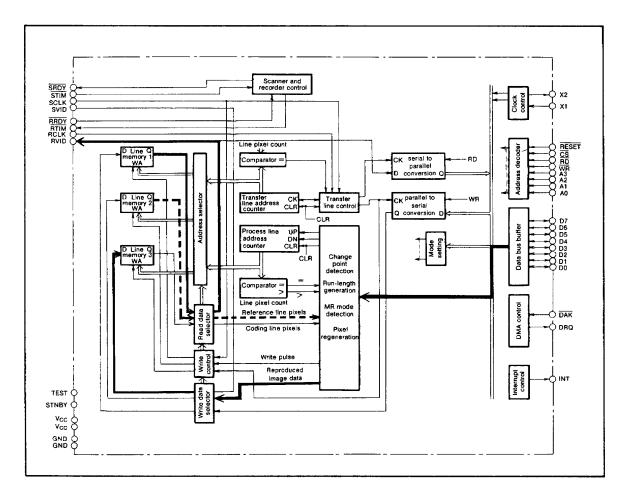

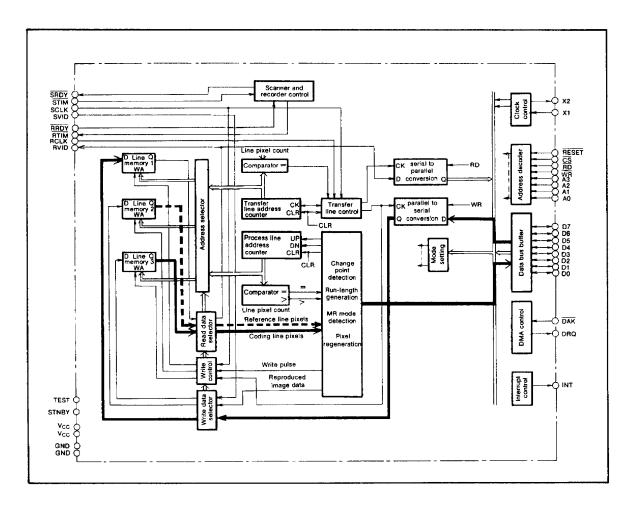

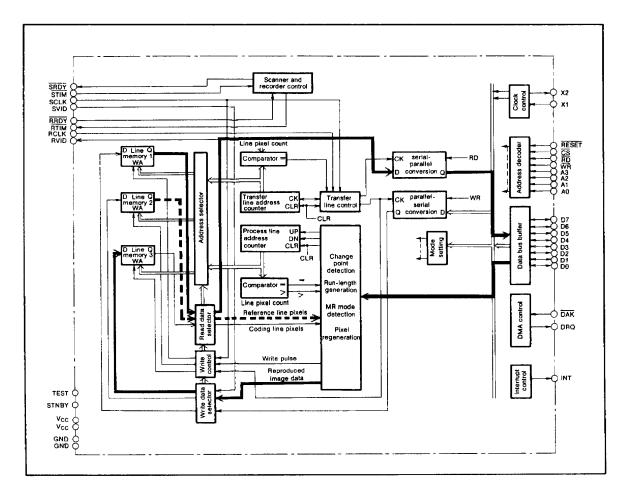

The M66330 is a high-speed coder & decoder (CODEC) LSI under the control of a micro-processor unit (MPU). The M66330 supports coding and decoding of MH, MR, and MMR methods.

Commands from the MPU specify and set the scan line length, operating mode, method of coding or decoding, and image processing.

The controller includes three 2048-bit line memories. In addition to the MPU bus, there are serial buses for scanning and recording and MR mode detection circuit. M66330 permits fast coding and decoding of data.

#### **FEATURES**

- Supports MH, MR, and MMR coding methods recommended by CCITT

- · Various operating modes

- · G2 send/receive mode

- G3 send/receive mode (MH/MR/MMR coding and decoding methods)

- · G2 to G3 conversion and vice versa

- · Copy mode

- Image processing functions

- · Up to 2048 pixels per line

- · Reduction (B4 to A4)

- Addition of sender identification (in G2 to G3 conversion mode)

- Recording of receiver identification (in G2 receive mode)

- · Journal output (in G2 receive mode)

- Processing for transfer of image data to a recording system

Alignment function (recording with left alignment, right alignment, or centered)

Edge blanking (16 or 32 bits)

- High-speed processing

- Three internal 2048-bit line memories for scanning and recording

- Circuits for change point detection, run-length generation, and pixel reproduction (MH method)

- Circuits for MR mode detection and pixel reproduction (MR and MMR methods)

- . Control circuit for external DMA

- · Efficient bus configurations

- Serial buses for scanning and recording

#### **APPLICATION**

Facsimile machines

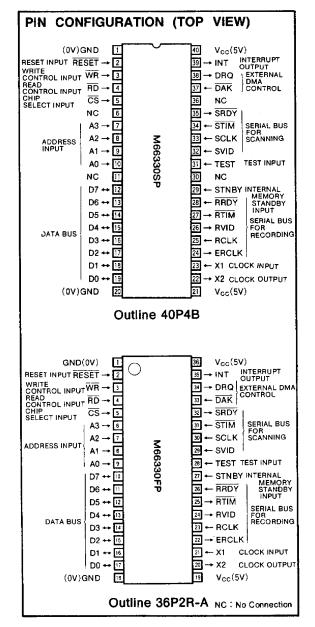

## PIN DESCRIPTIONS

| Di-            | Classification          | Input/           |                                                                                                                                                                                                |

|----------------|-------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin            | Classification          | Output           | Descriptions                                                                                                                                                                                   |

| RESET          |                         | Input            | Input for resetting system                                                                                                                                                                     |

| cs             |                         | Input            | Chip select signal required by MPU to access M66330                                                                                                                                            |

| RD             |                         | Input            | Control signal line for input when MPU reads data from M66330                                                                                                                                  |

| WR             |                         | Input            | Control signal line for input when MPU writes data to M66330                                                                                                                                   |

| A0~A3          | MPU bus interface       | Input            | Address signal lines for accessing M66330 registers                                                                                                                                            |

| D0~D7          | MFO bus interface       | Input/<br>Output | 8-bit bidirectional bus buffer                                                                                                                                                                 |

| INT            |                         | Output           | Interrupt request signal output from M66330 to MPU                                                                                                                                             |

| DRQ            |                         | Output           | DMA request signal for image data input-output by external DMA controller.  DMA transfer is possible in the following modes G2 send, G2 receive, G2 to G3 conversion, and G3 to G2 conversion. |

| DAK            |                         | Input            | DAM acknowledge signal from DMA controller. This signal is paired with the above DRQ signal.                                                                                                   |

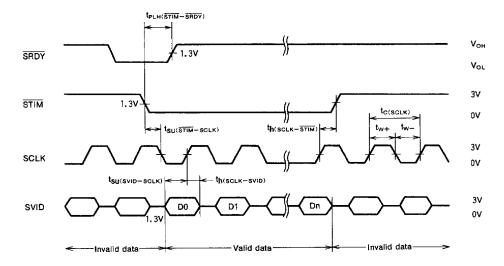

| SRDY           |                         | Output           | Outputs ready signal for scanner for starting data transfer                                                                                                                                    |

| STIM           | Serial bus for scanning | Input            | Defines scanner data transfer interval                                                                                                                                                         |

| SCLK           | Serial bus for scanning | Input            | Inputs sync clock signal for image data transfer from scanner                                                                                                                                  |

| SVID           |                         | Input            | Serial input of image data from scanner                                                                                                                                                        |

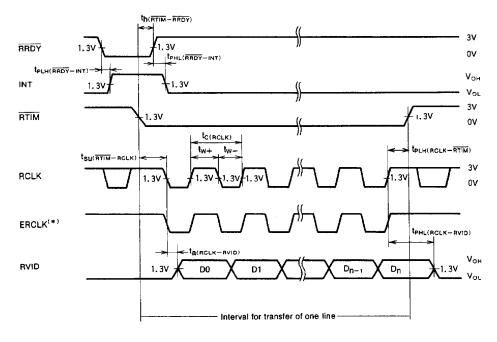

| RRDY           |                         | Input            | Inputs ready signal for recorder for starting data transfer                                                                                                                                    |

| RTIM           |                         | Output           | Defines recorder data transfer interval                                                                                                                                                        |

| RCLK           | Serial bus for recorder | Input            | Inputs sync clock signal for image data transfer to recorder                                                                                                                                   |

| ERCLK          |                         | Output           | Outputs sync clock signal (= $f_{\chi_5}/4$ ) for transfer of data to recorder. This pin is connected to pin RCLK during operation.                                                            |

| RVID           |                         | Output           | Serial output of image data to recorder                                                                                                                                                        |

| X <sub>1</sub> |                         | Input            | Connected to quartz oscillator. Also used as input pin for X <sub>1</sub> with external clock input. In such a case, X <sub>2</sub> re-                                                        |

| X <sub>2</sub> |                         | Output           | mains open.                                                                                                                                                                                    |

| Voc            |                         | _                | Positive power supply pin                                                                                                                                                                      |

| GND            | Others                  | -                | Ground (GND) pin                                                                                                                                                                               |

| STNBY          |                         | -                | When set to level "H", the internal memory is placed in standby mode. Set to level "L" during operation.                                                                                       |

| TEST           |                         | _                | Test pin. Set level permanently to "L".                                                                                                                                                        |

# M66330SP/FP

## BAND COMPRESSION AND EXPANSION CONTROLLER

## **REGISTER STRUCTURE**

- The numerics in brackets under the register name are the address in hexadecimal.

- The numerics in brackets under the bit allocation show the register status after reset. (X: undefined)

## (1) Command Registers

| Register name                     | R/W | Bit allocation      | Description                                                                                                                                                                                                                                                                                   |  |  |  |  |

|-----------------------------------|-----|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| System reset<br>(6H)              | w   | D7 D0 (0)           | Resets the controller D0 0 : Reset off 1 : Reset on Always set the reset off after setting the reset on.                                                                                                                                                                                      |  |  |  |  |

| Interrupt enable<br>(OH)          | w   | D7 D0 (0 0 0 0)     | Enables or disables interrupt requests  D0: Transfer line input-output completion interrupt (1: enable)  D1: Code/decode completion and process line output completion interrupt  (1: enable)  D2: Recorder ready interrupt  D3: Image data input-output ready interrupt (Note 1) (1: enable) |  |  |  |  |

| Line pixel count<br>(4H)          | w   | D7 D0 (0 0)         | Sets the pixel count and reduction ratio for the line memory for image data input    D1                                                                                                                                                                                                       |  |  |  |  |

| Output image data processing (8H) | W   | D7 D0 (0 0 0 0 0 0) | Sets format of data for output to recorder                                                                                                                                                                                                                                                    |  |  |  |  |

| Operating mode<br>(2H)            | w   | D7 D0 (0 0 0)       | D2                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Register name            | R/W | Bit allocation | Description                                                                                         |        |        |         |   |

|--------------------------|-----|----------------|-----------------------------------------------------------------------------------------------------|--------|--------|---------|---|

| Coding & decoding method | w   | D7 D0 (0)      | Sets coding-decoding method D0 0 : One-dimensional method (MH) 1 : Two-dimensional method (MR, MMR) |        |        |         |   |

| Line memory              | w   |                | Allocates line memory                                                                               |        |        |         |   |

| (5H)                     |     |                | D2                                                                                                  | D1     | D0     | Cycle   |   |

|                          |     |                | 0                                                                                                   | 0      | 0      | 0       |   |

|                          |     | D7 D0          | 0                                                                                                   | 0      | 1      | 1       |   |

| ì                        |     |                | 0                                                                                                   | 1      | 0      | 2       |   |

|                          |     | (0 0 0)        | 1                                                                                                   | 0      | 0      | 4       |   |

|                          |     |                | 1                                                                                                   | 0      | 1      | 5       |   |

| 1                        |     |                | 1                                                                                                   | 1      | 0      | 6       | i |

|                          |     |                | Refer t                                                                                             | o Tabl | e 4 on | page 8. |   |

## (2) Status register

| Register name              | R/W | Bit allocation  | Description                                                                                                                                                                                                                                         |

|----------------------------|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal<br>status<br>(1H) | R   | D7 D0 (X X 0 0) | Indicates internal status  D0: Completion of transfer line input-output (1:completed)  D1: Completion of coding/decoding and process line output  (1:completed)  D2: Recorder ready (1:ready)  D3: Image data input-output ready (Note 1) (1:ready) |

## (3) Data registers

| Register name                | R/W | Bit allocation                               | Description                                                                                                                                                               |          |                        |                        |  |  |

|------------------------------|-----|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------|------------------------|--|--|

| Image data<br>input<br>(7H)  | w   | D7 D0 (× × × × × × × × × × × × × × × × × × × | inputs image data from MPU to M66330 in G2 receive mode and G2 to G3 conversion mode.  (The least significant bit (LSB: D0) corresponds to the top left on the document.) |          |                        |                        |  |  |

| Image data<br>output<br>(7H) | R   | D7 D0 (0 0 0 0 0 0 0)                        | Outputs image data from M66330 to MPU in G2 send mode and G to G2 conversion mode.  (The least significant bit (LSB: D0) corresponds to the top left of the document.)    |          |                        |                        |  |  |

| Coded data 1                 | R   | R D7 D0                                      | Indicates the result of G3 coding                                                                                                                                         |          |                        |                        |  |  |

| (9H)                         |     |                                              |                                                                                                                                                                           | D2 D1 D0 | One-dimensional coding | Two-dimensional coding |  |  |

|                              |     | $(0 1 \times \times 0 0 0)$                  | 0 0 0                                                                                                                                                                     | _        | -                      |                        |  |  |

|                              |     |                                              | 0 0 1                                                                                                                                                                     | _        | V (0) mode             |                        |  |  |

|                              |     |                                              | 0 1 0                                                                                                                                                                     | _        | V <sub>∟</sub> mode    |                        |  |  |

|                              |     |                                              | 0 1 1                                                                                                                                                                     |          | V <sub>R</sub> mode    |                        |  |  |

|                              |     |                                              | 1 0 0 1                                                                                                                                                                   | MH mode  | H mode (a0 a1)         |                        |  |  |

|                              |     |                                              | 1 0 1                                                                                                                                                                     | _        | H mode (a1 a2)         |                        |  |  |

|                              |     |                                              | 1 1 0                                                                                                                                                                     | _        | P mode                 |                        |  |  |

| 1                            |     |                                              | 1 1 1                                                                                                                                                                     | _        | 1                      |                        |  |  |

| Register name              | R/W | Bit allocation                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------|-----|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            |     |                                              | D4         D3         Distance of a1 to b1 in V <sub>R</sub> /V <sub>L</sub> mode           0         0         -           0         1         1           1         0         2           1         1         3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Coded data 2               | R   | DZ DO                                        | D6 D5 Coding status  0 0 Mode detection in progress  0 1 Mode detection complete  1 0 -  1 1 Detection of last mode complete (end of 1 line)  Shows terminate run length in MH and H modes of MR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| (AH)                       |     | D7 D0 (× × × × × × × × × × × × × × × × × × × | D5 to D0 : Terminate run length (0 to 63) D6 : Color specification (1 : black) D7 : Existence of make-up coding (1 : exists)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Coded data 3<br>(BH)       | R   | D7 D0 (X X X X X X X)                        | Shows make-up run length in MH and H modes of MR D5 to D0: Make-up run length (64, 128, 192, ···, 2560) D6: Color specification (1: black)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Decoding<br>data 1<br>(9H) | W   | D7 D0 (0 0 0 0 0)                            | Sets G3 decoding mode           D2         D1         D0         One-dimensional decoding         Two-dimensional decoding           0         0         0         —         —           0         0         1         —         V (0) mode           0         1         0         —         V <sub>L</sub> mode           0         1         1         —         V <sub>R</sub> mode           1         0         0         MH mode (a0 a1)         H mode (a1 a2)           1         1         0         —         P mode           1         1         1         —         —           D4         D3         Distance of a1 to b1 in V <sub>B</sub> /V <sub>L</sub> mode         —           0         0         —         —         —           0         1         1         1         1         1           1         0         2         1         3         3 |

| Decoding<br>data 2<br>(AH) | w   | D7 D0 (0 0 0 0 0 0)                          | Shows terminate run-length in MH and H modes of MR D5 to D0 : Terminate run length (0 to 63)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Decoding<br>data 3<br>(BH) | w   | D7 D0 (0 0 0 0 0 0)                          | Shows make-up run length in MH and H modes of MR D5 to D0: Make-up run length (64, 128, 192, ···, 2560)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Decoding<br>status<br>(8H) | R   | D7 D0 (0 0 0)                                | D2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

#### (4) Control registers

| Register name                         | R/W | Bit allocation | Description                               |

|---------------------------------------|-----|----------------|-------------------------------------------|

| Transfer line counter reset (CH)      | W   | D7 D0          | Resets transfer line address counter      |

| Transfer line start                   | w   | D7 D0          | Starts input-output of transfer line data |

| Process line<br>counter reset<br>(EH) | W   | D7 D0          | Resets process line address counter       |

| Process line<br>start<br>(FH)         | w   | D7 D0          | Starts or restart process line            |

Note 1: Image data input-output ready

In the G2 send mode, G2 receive mode, G2 to G3 conversion mode and G3 to G2 conversion mode, this signal indicates that the input-output of image data is enabled on the MPU data bus.

Note 2: Decoding mode setting error

This error is occured if '000' or '111' is set for D2, D1, and D0 in the G3 decoding mode for decoding data 1.

#### **FUNCTIONAL OVERVIEW**

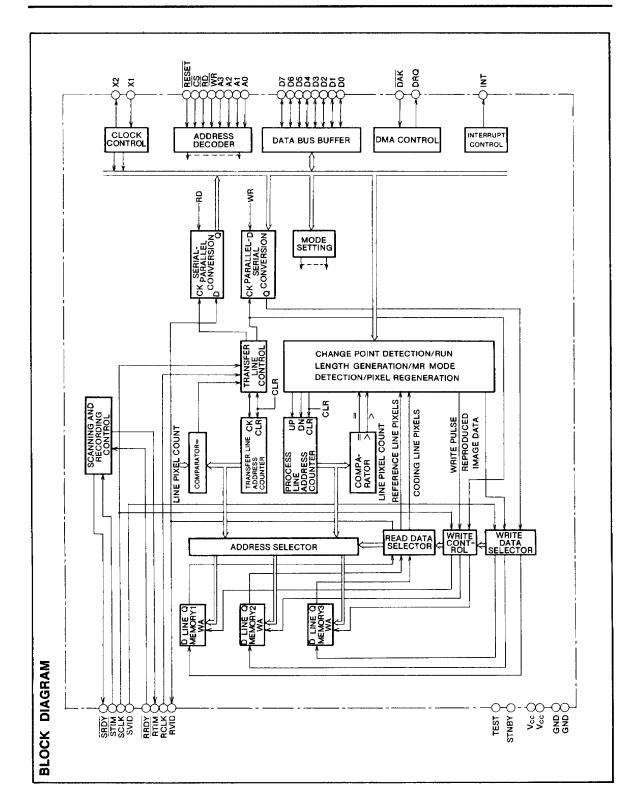

#### (1) Overview

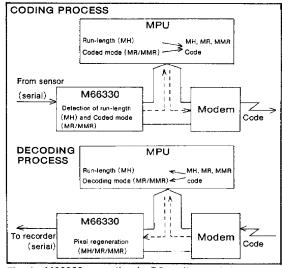

The M66330 is a CODEC LSI for high speed coding and decoding of image data under the control of an MPU.

- Pixels: Maximum 2048 bits/line (for B4-size) Binary image data is treated according to Table 1.

- Coding and decoding methods: MH, MR, and MMR

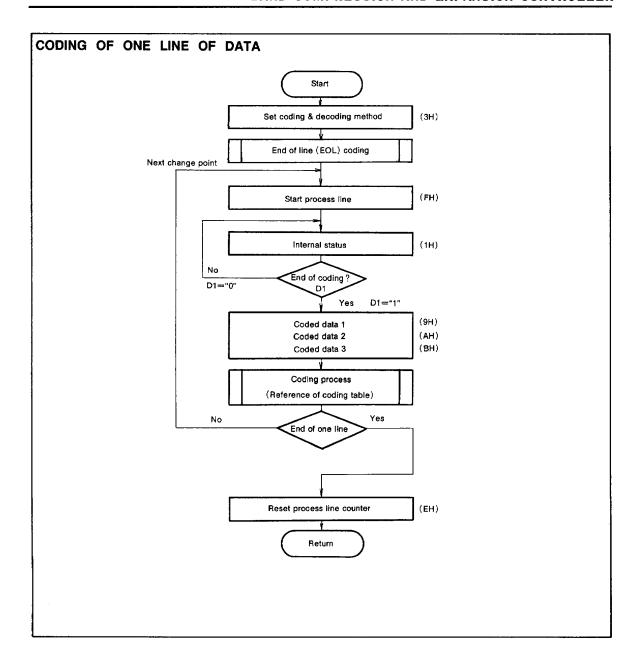

- Operation in the coding and decoding processes Table 2 and Figure 1 show the operations of the M66330 and MPU during the MH, MR, and MMR coding and decoding processes.

Table 1 Expression of binary data

| Pixel       | Binary form |

|-------------|-------------|

| White level | 0           |

| Black level | 1           |

M66330 operation in G3 coding and decoding Fig. 1 processes

Table 2 M66330 operation in coding and decoding processes

| Method    | Process  | M66330                                                                                                                                                                        | MPU                                                                                                                                |  |  |

|-----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MH        | Coding   | Generates black and white run-length data from the image data input from the scanning sensors. This data is sent to the MPU.                                                  | Codes the black and white run-length data input from the M66330 using the MH coding method. This coded data is sent to the modern. |  |  |

| MH        | Decoding | Generates image data from the black and white run-<br>length data supplied by the MPU. This image data is<br>sent to the recording device.                                    | Converts the MH-coded string input from the modem into black and white run-length data. This data is sent to the M66330.           |  |  |

| MR<br>MMR | Coding   | Detects the MR mode of the image data input from the scanning sensors and sends the information to the MPU.  In horizontal mode, the run-length data is also sent to the MPU. | Codes the result of MR mode detection input from the M66330. The result is coded by the MR method and sent to the modern.          |  |  |

|           | Decoding | Regenerates the image data on the basis of the result of MR mode detection input from the MPU. The regenerated image data is sent to the recording device.                    | Converts the MR-coded string input from the modem to MR mode, and sends the data to the M66330.                                    |  |  |

#### (2) Operating mode

The following operating modes can be set using operating mode commands.

- Copy mode

- G3 to G2 conversion mode

- •G2 to G3 conversion mode

- •G3 receive mode (MH, MR, and MMR methods)

- •G2 receive mode

- •G3 send mode (MH, MR, and MMR methods)

- G2 send mode

#### (3) Internal line memory operation

The M66330 has three line memories of 2048 bits per line. These are the transfer line memory, process line memory, and reference line memory.

The transfer line memory is used as a data input-output buffer, and the writing or reading position of data is controlled according to the transfer line address counter.

The process line memory is used mainly for handling the line data for the coding and decoding processes. The memory is controlled by the process line address counter.

The reference line memory is used as a reference line data buffer for use in two-dimensional coding and decoding. As with the process line memory, the data writing or reading position is controlled by the process line address counter.

Table 3 shows the operation of each type of line memory in each operating mode.

Table 3 Internal line memory operation in each operating mode

| Line memory              | Transfer line                 | Reference line                   | Process line               |

|--------------------------|-------------------------------|----------------------------------|----------------------------|

| Operating mode           | Transfer line address counter | Process line                     | e address counter          |

| Copy mode                | Data buffer for scanning      | -                                | Data buffer for recording  |

| G3 to G2 conversion mode | Data buffer for MPU output    | Reference line data for decoding | Decoded line data          |

| G2 to G3 conversion mode | Data buffer for MPU input     | Reference line data for coding   | Coding line data           |

| G3 receive mode          | Data buffer for recording     | Reference line data for decoding | Decoded line data          |

| G2 receive mode          | Data buffer for MPU input     | _                                | Data buffer for recording  |

| G3 send mode             | Data buffer for scanning      | Reference line data for coding   | Coding line data           |

| G2 send mode             | Data buffer for scanning      | _                                | Data buffer for MPU output |

The three line memories (LM1, LM2, and LM3) are allocated cyclically by the line memory commands to the transfer line, reference line, and process line.

Table 4 shows the relationship between the roles of the line memories and the line memory cycle.

Table 4 Line memory switching cycle

| Line memory    | Cycle | 0   | 1   | 2   | 4   | 5   | 6   |

|----------------|-------|-----|-----|-----|-----|-----|-----|

| Transfer line  |       | LM1 | LM2 | LM3 | LM2 | LM3 | LM1 |

| Reference line |       | LM2 | LM3 | LM1 | LM1 | LM2 | LM3 |

| Process line   |       | LM3 | LM1 | LM2 | LM3 | LM1 | LM2 |

# MITSUBISHI (DIGITAL ASSP) M66330SP/FP

#### BAND COMPRESSION AND EXPANSION CONTROLLER

## (4) Interrupt requests

As shown in Table 5, the M66330 has seven interrupt factors. The interrupt enable command is used to enable and disable each interrupt request. When an in-

terrupt is generated, the factor is determined by reading the internal status register. Table 6 shows which interrupt factors can be generated in each operating mode.

Table 5 M66330 interrupt factors

| No. | laborate forter                               | In | ternal status | (1H) bit patte | ern | latavy at mant time                    |  |

|-----|-----------------------------------------------|----|---------------|----------------|-----|----------------------------------------|--|

| NO. | Interrupt factor                              | D3 | D2            | D1             | D0  | Interrupt reset timing                 |  |

| 1   | Completion of transfer line data input/output | 0  | 0             | 0              | 1   | WR of transfer line counter reset (CH) |  |

| 2   | Completion of coding                          | 0  | 0             | 1              | О   | RD of coded data 1 (9H)                |  |

| 3   | Completion of decoding                        | 0  | 0             | 1              | 0   | RD of decoding status (8H)             |  |

| 4   | Completion of process line data output        | 0  | 0             | 1              | 0   | WR of process fine counter reset (EH)  |  |

| 5   | Recorder ready                                | 0  | 1             | 0              | 0   | RRDY input inactive                    |  |

| 6   | Image data output ready                       | 1  | 0             | 0              | С   | RD of image data output (7H)           |  |

| 7   | Image data input ready                        | 1  | 0             | 0              | 0   | WR of image data input (7H)            |  |

Values in brackets indicate hexadecimal address of the register.

Table 6 Interrupt factors in each operating mode

|                     |     |                                               |    | Interna  | l statu | s  |                                                                        |                                             |

|---------------------|-----|-----------------------------------------------|----|----------|---------|----|------------------------------------------------------------------------|---------------------------------------------|

| Operating mode      | No. | Interrupt factor                              |    | it patte | _       | 1) | Interrupt set timing                                                   | Interrupt reset timing                      |

|                     |     |                                               | D3 | D2       | D1      | D0 |                                                                        |                                             |

|                     | 1   | Completion of transfer line input/output      | 0  | 0        | 0       | 1  | Scanning system to M66330 at completion of input of one line of data   | WR of transfer line counter reset (CH)      |

| Сору                | 5   | Recorder ready                                | 0  | 1        | 0       | 0  | Recording system to M66330 when RRDY input active                      | RRDY input inactive                         |

|                     | 4   | Completion of process line data output        | 0  | 0        | 1       | 0  | M66330 to recording system at completion of output of one line of data | WR of process line counter reset (EH)       |

| G3 send             | 1   | Completion of transfer line data input/output | 0  | 0        | 0       | 1  | Scanning system to M66330 at completion of input of one line of data   | WR of transfer line counter reset (CH)      |

|                     | 2   | Completion of coding                          | 0  | 0        | 1       | 0  | At completion of coding                                                | RD of coded data 1 (9H)                     |

|                     | 1   | Completion of transfer line data input/output | 0  | 0        | 0       | 1  | Scanning system to M66330 at completion of input of one line of data   | WR of transfer line counter re-<br>set (CH) |

| G2 send             | 6   | Image data output ready                       | 1  | 0        | 0       | 0  | When DRQ output for G2 data output is active                           | RD of image data output (7H)                |

|                     | 4   | Completion of process line data output        | 0  | 0        | 1       | 0  | At completion of output of one line of data for G2 data output         | WR of process line counter re-<br>set (EH)  |

|                     | 3   | Completion of decoding                        | 0  | 0        | 1       | 0  | At completion of decoding                                              | RD of decoding status (8H)                  |

| G3 receive          | 5   | Recorder ready                                | 0  | 1        | 0       | 0  | Recorder to M66330 when RRDY input is active                           | RRDY input inactive                         |

|                     | 1   | Completion of transfer line data input/output | 0  | 0        | 0       | †  | M66330 to recording system at completion of output of one line of data | WR of transfer line counter reset (CH)      |

|                     | 7   | Image data input ready                        | 1  | 0        | 0       | 0  | When DRQ output for G2 data input is active                            | WR of image data input (7H)                 |

|                     | 1   | Completion of transfer line data input/output | 0  | 0        | 0       | 1  | At completion of input of one line of data for G2 data input           | WR of transfer line counter re-<br>set (CH) |

| G2 receive          | 5   | Recorder ready                                | 0  | 1        | 0       | 0  | Recording system to M66330 when RRDY input active                      | RRDY input inactive                         |

|                     | 4   | Completion of process line data output        | 0  | 0        | 1       | 0  | M66330 to recording system at completion of output of one fine of data | WR of process line counter reset (EH)       |

|                     | 3   | Completion of decoding                        | 0  | 0        | 1       | 0  | At completion of decoding                                              | RD of decoding status (8H)                  |

| G3 to G2 conversion | 6   | Image data output ready                       | 1  | 0        | 0       | 0  | When DRQ output for G2 data output is active                           | RD of image data output(7H)                 |

|                     | 1   | Completion of transfer line data input/output | 0  | 0        | 0       | 1  | At completion of output of one line of data for G2 data output         | WR of transfer line counter re-<br>set (CH) |

|                     | 7   | Image data input ready                        | 1  | 0        | 0       | 0  | When DRQ output for G2 data input is active                            | WR of image data input (7H)                 |

| G2 to G3 conversion | 1   | Completion of transfer line data input/output | 0  | 0        | 0       | 1  | At completion of input of one line of data for G2 data input           | WR of transfer line counter re-<br>set (CH) |

|                     | 2   | Completion of coding                          | 0  | 0        | 1       | 0  | At completion of coding                                                | RD of coded data 1 (9H)                     |

Values in brackets indicate hexadecimal address of the register.

#### (5) M66330 data input/output

The M66330 has three data buses. These are the MPU bus, the serial bus for the scanner, and the serial bus for the recorder.

These buses are used for the input and output of image data, coded data, and decoding data. The input/output sequences for these data types are shown on the subsequent pages.

Table 7 M66330 data input/output

| No. | Data                      | Input/output | Data bus                | Applicable modes                   | Fig. |

|-----|---------------------------|--------------|-------------------------|------------------------------------|------|

| 1   | Image data                | Input        | Serial bus for scanner  | Copy, G2 send, and G3 send         | 3    |

| 2   | Image data                | Output       | Serial bus for recorder | Copy, G2 receive, and G3 receive   | 4    |

| 3   | Coded data                | Output       | MPU bus                 | G3 send and G2 to G3 conversion    | 5,6  |

| 4   | Decoding data             | Input        | MPU bus                 | G3 receive and G3 to G2 conversion | 7,8  |

| 5   | Image data                | Input        | MPU bus                 | G2 receive and G2 to G3 conversion | 9    |

| 6   | Image data : DMA transfer | Input        | MPU bus                 | G2 receive and G2 to G3 conversion | 10   |

| 7   | Image data                | Output       | MPU bus                 | G2 send and G3 to G2 conversion    | 11   |

| 8   | Image data : DMA transfer | Output       | MPU bus                 | G2 send and G3 to G2 conversion    | 12   |

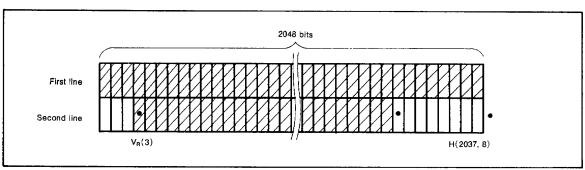

Fig. 2 Image data used in the coding/decoding data I/O sequence

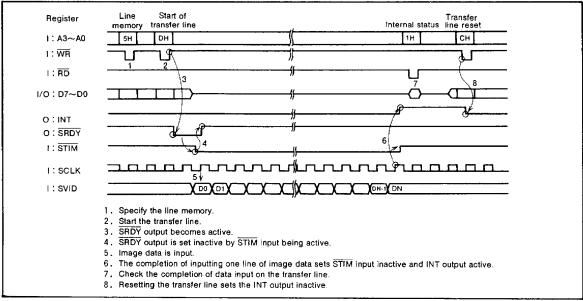

Fig. 3 Input sequence for one line of image data (serial bus for scanning)

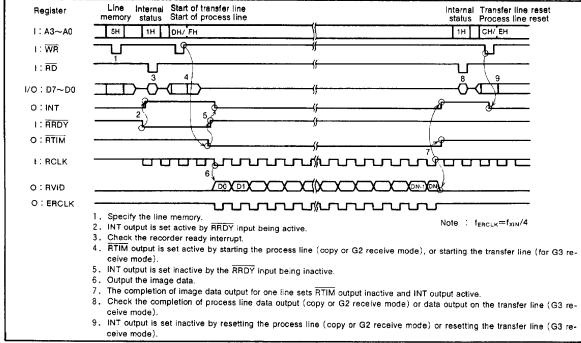

Fig. 4 Output sequence for one line of image data (serial bus for recording)

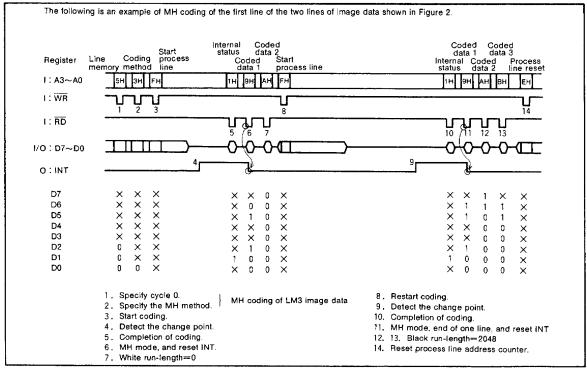

Fig. 5 Output sequence for one line of MH-coded data (MPU bus)

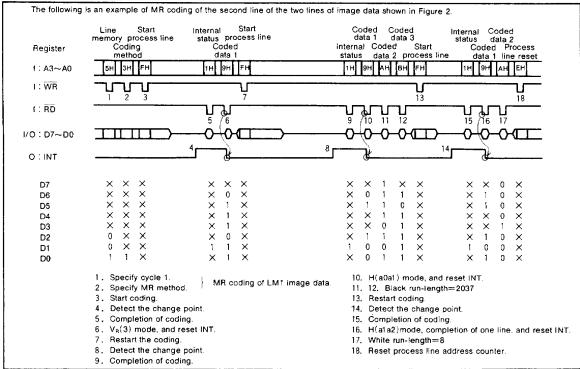

Fig. 6 Output sequence for one line of MR-coded data (MPU bus)

## M66330SP/FP

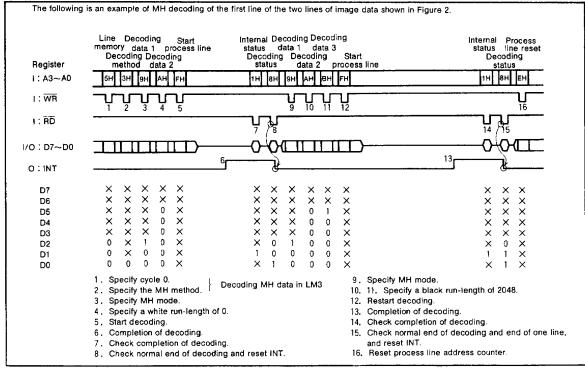

Fig. 7 Input sequence for one line of MH-decoding data (MPU bus)

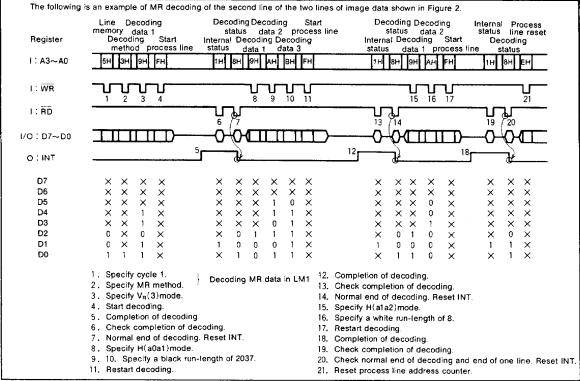

Fig. 8 Input sequence for one line of MR-decoding data (MPU bus)

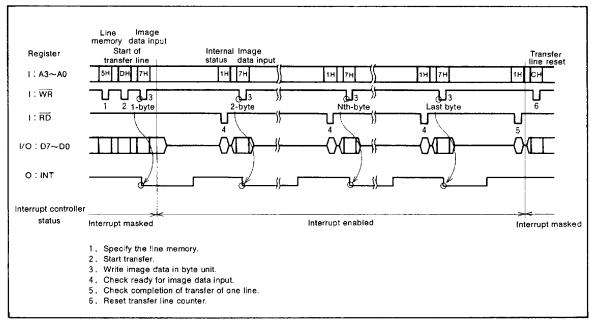

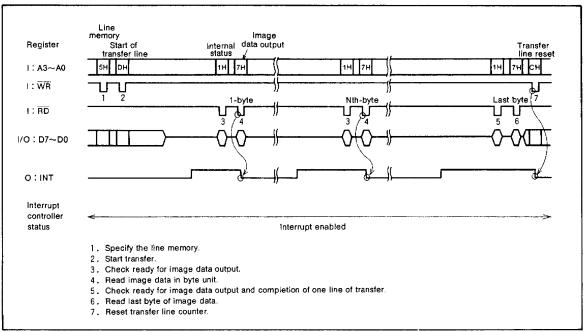

Fig. 9 Input sequence for one line of image data (MPU bus)

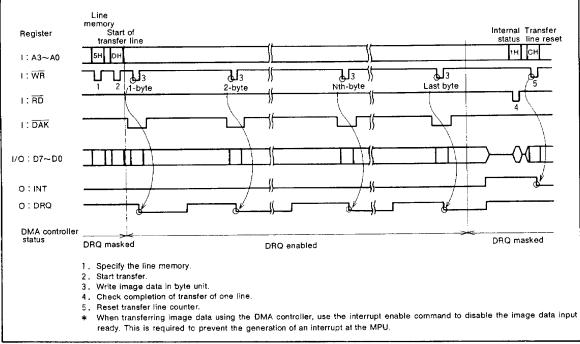

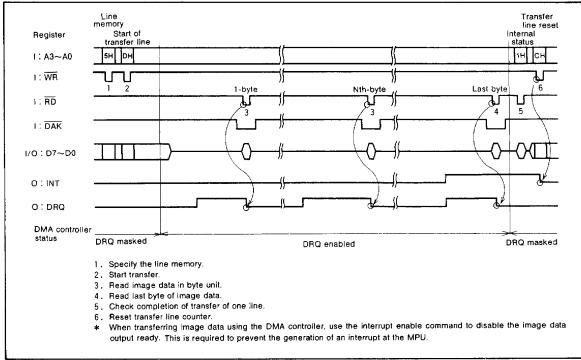

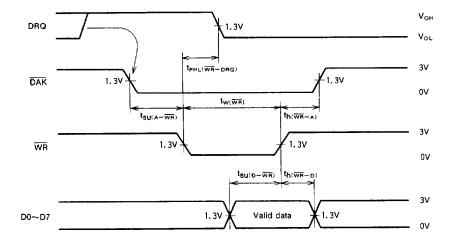

Fig. 10 Input sequence for one line of image data (MPU bus using DMA controller)

Fig. 11 Output sequence for one line of image data (MPU bus)

Fig. 12 Output sequence for one line of image data (MPU bus using DMA controller)

#### (6) Image processing function

The M66330 has three 2048-bit line memories. This allows the image data up to B4-size. The following describes the image processing functions of the M66330. These functions can be implemented using commands from the MPU.

Reduction function (B4 to A4)

Use the line pixel count command in G2 or G3 send modes to select reduction from B4 to A4 (reduction ratio: 9/11). Image data scanned at the B4-size is reduced in the horizontal scanning direction to A4-size for transfer. An MPU program reduces the dimensions in the vertical scanning direction by the same ratio.

Addition of sender identification

In G3 send mode, use the operating mode command to select the G2 to G3 conversion mode. In this mode, image data of the sender identification is input via the MPU bus of the M66330, is coded, and is sent appended to the coded data for the document. This allows the sender identification to be printed.

Recording of receiver identification

In G2 and G3 receive modes, use the **operating mode command** to select G2 receive mode. In this mode, receiver identification data is input via the MPU bus of the M66330, is output via the serial bus for the recorder, and is appended to the received image data. This allows the receiver identification to be printed.

Journal output

Use the **operating mode command** to select G2 receive mode. In this mode, journal data is input via the MPU bus of the M66330 and output via the serial bus for the recorder. This allows journal output.

Processing for image data transferred to recorder system

Use the output image processing command for the following settings

These settings are possible when image data in the M66330 line memories is output via the serial bus for recording.

#### ① Alignment function

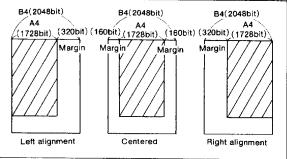

When recording A4-size (1728-bit) images on B4-size (2048-bit) recording paper, a white margin can be added before and after the image data. This allows the image to be right-aligned, centered, or left-aligned. Figure 13 shows examples.

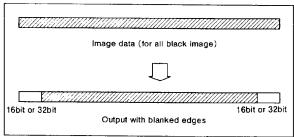

#### ② Edge blanking function

As shown in Figure 14, this function allows forcible blanking of 16 bits (2mm) or 32 bits (4mm) on both side of the output image data.

This function is used in the following cases:

To correct for the difference between the A4 image sensor width (1728 bits: 216mm) and the JIS standard A4 paper size (1680 bits : 210mm)

- To delete the shadow around a scanned document when recording A4-size image data on B4-size recording paper

- To prevent the thermal head from burning the platen when the thermal head of the recorder is misaligned with the recording paper. This situation can occur when B4 images are being printed on B4 paper, or A4 images are being printed on A4 paper.

Fig. 13 Alignment function

Fig. 14 Edge blanking function

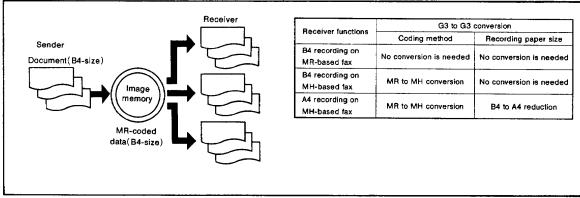

#### (7) G3 to G3 conversion function

In facsimile machines with memory functions, image data is first compressed and stored in memory. For the data to be transferred, the sender must convert the

coding method and/or recording paper size according to the functions of the receiver. With the M66330, G3 to G3 conversion is achieved by the appropriate commands from the MPU.

Fig. 15 Conversion functions in facsimile machines with memory functions

#### Coding method conversion

The G3 to G2 conversion mode of the M66330 is used to decode G3-coded data stored in image memory to image data in the line memory. The G2 to G3 conversion mode is then used to re-code the data into G3 format.

Operating sequences and line memory cycles are shown in Table 8.

#### Paper size conversion

The G3 to G2 conversion mode of the M66330 is used to decode G3-coded data (B4-size) stored in image

memory to image data in the line memory. The G2 to G3 conversion mode is then used to specify a reduction from B4 to A4 (line pixel count command) and to recode the data into G3 format. This allows the dimensions in the horizontal scanning direction to be reduced from B4 to A4.

An MPU program is used to reduce the dimensions in the vertical scanning direction in the same ratio.

Operating sequences and line memory cycles are shown in Table 9.

Table 8 G3 to G3 operating sequence (without paper size conversion)

| Data I/O                   | Operating mode      | Coding/decoding |                                | Operating sequence |        |        |                                                                  |      |  |

|----------------------------|---------------------|-----------------|--------------------------------|--------------------|--------|--------|------------------------------------------------------------------|------|--|

| G3 data input              | G3 to G2 conversion | Decoding        | 0 line<br>(All white<br>image) | 1 line             | 2 line | 3 line |                                                                  | Last |  |

| G3 data output             | G2 to G3 conversion | Coding          | -                              | 1 line             | 2 line | 3 line |                                                                  | Last |  |

|                            | Line mem            | 2               | 0                              | 1                  | 2      |        |                                                                  |      |  |

|                            | Transf              | er line         | LM3(-)                         | LM1()              | LM2(0) | LM3(1) | Repeat the same line memory cycle as 1st line to 3rd line to las |      |  |

| line memory Reference line |                     | nce line        | LM1(-)                         | LM2(0)             | LM3(1) | LM1(2) | line.                                                            |      |  |

|                            | Proces              | Process line    |                                |                    | LM1(2) | LM2(3) |                                                                  |      |  |

## Table 9 G3 to G3 operating sequence (with paper size conversion)

| Data I/O       | Operating mode      | line pixel<br>count | Coding/<br>decoding |                                | Operating sequence |        |        |        |        |        |        |        |        |        |         |

|----------------|---------------------|---------------------|---------------------|--------------------------------|--------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------|

| G3 data input  | G3 to G2 conversion | B4                  | Decoding            | 0 line<br>(All white<br>image) | 1 line             | 2 line | 3 line | 4 line | 5 line | 6 line | -      | 7 line | 8 line | 9 line | 10 line |

| G3 data output | G2 to G3 conversion | B4→A4               | Coding              | _                              | 1 line             | 2 line | 3 line | 4 line | _      | _      | 6 line | 7 line | 8 line | 9 line | _       |

|                | Line men            | ory cycle           | ,                   | 2                              | 0                  | 1      | 2      | 0      | 1      | 2      | 6      | 0      | 1      | 2      | 0       |

| line memory    | Transf              | er line             |                     | LM3(-)                         | LM1()              | LM2(0) | LM3(1) | LM1(2) | LM2(3) | LM3(4) | LM1(5) | LM1(5) | LM2(6) | LM3(7) | LM1(8)  |

| mie memory     | Refere              | nce line            |                     |                                |                    |        | LM1(2) |        |        |        |        |        |        |        |         |

|                | Proces              | ss line             |                     | LM2(0)                         | LM3(1)             | LM1(2) | LM2(3) | LM3(4) | LM1(5) | LM2(6) | LM2(6) | LM3(7) | LM1(8) | LM2(9) | LM3(10) |

(to be continued)

|         |         |         |         |         |         |         | 0       | perating | sequenc | 9       |         |         |         |         |         | ,       |         |

|---------|---------|---------|---------|---------|---------|---------|---------|----------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| 11 line | _       | 12 line | 13 line | 14 line | 15 line | 16 line | 17 line | _        | 18 line | 19 line | 20 line | 21 line | 22 line | _       | 23 line | 24 line | 25 line |

| -       | 11 line | 12 line | 13 line | 14 line | 15 line | _       | -       | 17 line  | 18 line | 19 line | 20 line |         | _       | 22 line | 23 line | 24 line | 25 line |

| 1       | 5       | 2       | 0       | 1       | 2       | 0       | 1       | 5        | 2       | 0       | 1       | 2       | 0       | 4       | 1       | 2       | 0       |

| LM2(9)  | LM3(10) | LM3(10) | LM1(11) | LM2(12) | LM3(13) | LM1(14) | LM2(15) | LM3(16)  | LM3(16) | LM1(17) | LM2(18) | LM3(19) | LM1(20) | LM2(21) | LM2(21) | LM3(22) | LM1(23  |

| LM3(10) | LM2(9)  | LM1(11) | LM2(12) | LM3(13) | LM1(14) | LM2(15) | LM3(16) | LM2(15)  | LM1(17) | LM2(18) | LM3(19) | LM1(20) | LM2(21) | LM1(20) | LM3(22) | LM1(23) | LM2(24) |

| LM1(11) | LM1(11) | LM2(12) | LM3(13) | LM1(14) | LM2(15) | LM3(16) | LM1(17) | LM1(17)  | LM2(18) | LM3(19) | LM1(20) | LM2(21) | LM3(22) | LM3(22) | LM1(23) | LM2(24) | LM3(25  |

(to be continued)

|          | Operating sequence |          |         |          |          |         |          |         |          |                                                            |         |

|----------|--------------------|----------|---------|----------|----------|---------|----------|---------|----------|------------------------------------------------------------|---------|

| 26 line  | 27 line            | 28 line  |         | 29 line  | 30 line  | 31 line | 22 line  | 33 line |          |                                                            | Last    |

| 20 11110 | 27 11110           | 20 11116 |         | 29 11110 | 30 line  | Jime    | 32 11110 | 33 1116 | _        |                                                            | line    |

| 26 line  |                    |          | 28 line | 29 line  | 30 line  | 31 iine |          |         | 33 line  |                                                            | Last    |

| 20 line  | _                  | _        | 26 line | 29 line  | 30 IIIIe | 31 ane  | _        | _       | 33 IIIIe |                                                            | line    |

| 1        | 2                  | 0        | 4       | 1        | 2        | 0       | 1        | 2       | 6        |                                                            |         |

| LM2(24)  | LM3(25)            | LM1(26)  | LM2(27) | LM2(27)  | LM3(28)  | LM1(29) | LM2(30)  | LM3(31) | LM1(32)  | Repeat the same line memory cycle as 1st line to 33rd line | to last |

| LM3(25)  | LM1(26)            | LM2(27)  | LM1(26) | LM3(28)  | LM1(29)  | LM2(30) | LM3(31)  | LM1(32) | LM3(31)  | line.                                                      |         |

| LM1(26)  | LM2(27)            | LM3(28)  | LM3(28) | LM1(29)  | LM2(30)  | LM3(31) | LM1(32)  | LM2(33) | LM2(33)  |                                                            |         |

## **DATA FLOW**

The following describes the data flow in each operating mode. Line memory cycle 0 is used for the examples.

#### (1) Copy mode

In the copy mode, image data input from the scanner is output to the recorder via line memory.

| Line memory    | Address counter               | Role                     |  |  |

|----------------|-------------------------------|--------------------------|--|--|

| Transfer line  | Transfer line address counter | Data buffer for scanner  |  |  |

| Reference line | Process line address counter  | -                        |  |  |

| Process line   | Process line address counter  | Data buffer for recorder |  |  |

#### (2) G2 send mode

In the G2 send mode, image data input from the scanner is output to the MPU bus.

| Line memory    | Address counter               | Role                       |  |  |

|----------------|-------------------------------|----------------------------|--|--|

| Transfer line  | Transfer line address counter | Data buffer for scanner    |  |  |

| Reference line | D                             | _                          |  |  |

| Process line   | Process line address counter  | Data buffer for MPU output |  |  |

#### (3) G2 receive mode

In the G2 receive mode, image data input via the MPU bus is output to the recorder via line memory. This mode allows the recording of journals and data transfer when recording receiver identification.

| Line memory    | Address counter               | Role                      |  |  |

|----------------|-------------------------------|---------------------------|--|--|

| Transfer line  | Transfer line address counter | Data buffer for MPU input |  |  |

| Reference line | B                             | -                         |  |  |

| Process line   | Process line address counter  | Data buffer for recorder  |  |  |

## (4) G3 send mode

In the G3 send mode, image data input from the scanner is coded and output as G3 data (coded data 1 to 3) to the MPU bus.

| Line memory    | Address counter               | Role                           |  |  |  |  |

|----------------|-------------------------------|--------------------------------|--|--|--|--|

| Transfer line  | Transfer line address counter | Data buffer for scanner        |  |  |  |  |

| Reference line | Process line address counter  | Reference line data for coding |  |  |  |  |

| Process line   | 1                             | Line data to be coded          |  |  |  |  |

#### (5) G3 receive mode

In the G3 receive mode, image data is regenerated in line memory using the G3 data (decoded data 1 to 3) input from the MPU bus.

This image data is then output to the recorder.

| Line memory    | Address counter               | Role                           |  |  |  |

|----------------|-------------------------------|--------------------------------|--|--|--|

| Transfer line  | Transfer line address counter | Data buffer for scanner        |  |  |  |

| Reference line | Process line address counter  | Reference line data for coding |  |  |  |

| Process line   |                               | Line data to be coded          |  |  |  |

#### (6) G2 to G3 conversion mode

In the G2 to G3 conversion mode, image data input from the MPU bus is coded, then output as G3 data (coded data 1 to 3) to the MPU bus.

This mode is used for data transfer of sender identification.

| Line memory    | Address counter               | Role                           |  |  |  |  |  |

|----------------|-------------------------------|--------------------------------|--|--|--|--|--|

| Transfer line  | Transfer line address counter | Data buffer for MPU input      |  |  |  |  |  |

| Reference line | Process line address counter  | Reference line data for coding |  |  |  |  |  |

| Process line   |                               | Line data to be coded          |  |  |  |  |  |

#### (7) G3 to G2 conversion mode

In the G3 to G2 conversion mode, image data is regenerated in line memory from the G3 data (coded data 1 to 3) input from the MPU bus. This image data is then output again to the MPU bus.

| Line memory    | Address counter               | Role                             |  |  |  |

|----------------|-------------------------------|----------------------------------|--|--|--|

| Transfer line  | Transfer line address counter | Data buffer for MPU output       |  |  |  |

| Reference line | Process line address counter  | Reference line data for decoding |  |  |  |

| Process line   | 1                             | Decoded line data                |  |  |  |

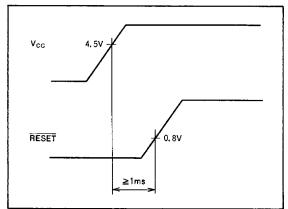

## RESET CIRCUIT

Requirements for reset circuit is shown in Figure 16.

Fig. 16 Requirements for power on reset

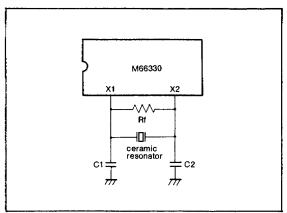

## **CLOCK GENERATOR**

Clock generator circuit for the ceramic resonator is shown in Figure 17.

Fig. 17 Clock generator

| 0             | Tune            | frequency | C1         | C2         | Rf   |

|---------------|-----------------|-----------|------------|------------|------|

| Supplier      | Туре            | (MHz)     | (pF)       | (pF)       | (MΩ) |

|               | CSA4. 00 MG 040 | 4.0       | 100        | 100        | 1.0  |

| l             | CST4, 00 MGW040 | 4.0       | 100        | 100        | 1.0  |

| Murata        |                 |           | (included) | (Included) | 1.0  |

| Manufacturing | CSA8. 00 MT     | 8.0       | 30         | 30         | 1.0  |

| Co., Ltd.     | CST8, 00 MTW    |           | 30         | 30         | 1.0  |

|               | C318.00 WITW    | 8. 0      | (Included) | (Included) | 1,0  |

# ELECTRICAL CHARACTERISTICS ABSOLUTE MAXIMUM RATINGS

| Symbol         | Parameter           | Conditions | Ratings                   | Unit |

|----------------|---------------------|------------|---------------------------|------|

| Vcc            | Supply voltage      |            | -0.3~+7.0                 | V    |

| V <sub>1</sub> | Input voltage       |            | -0.3~V <sub>cc</sub> +0.3 | V    |

| Vo             | Output voltage      |            | 0~V <sub>CC</sub>         | V    |

| Tstg           | Storage temperature |            | <del>-65~+150</del>       | °C   |

## **RECOMMENDED OPERATING CONDITIONS**

| Symbol | Parameter                   |      | 11-11 |      |      |

|--------|-----------------------------|------|-------|------|------|

|        | Parameter                   | Min. | Тур.  | Max. | Unit |

| Vcc    | Supply voltage              | 4.5  | 5.0   | 5.5  | V    |

| GND    | Ground voltage              |      | 0.    |      | V    |

| Vı     | Input voltage               | 0    |       | Vcc  | ٧    |

| Topr   | Operating temperature range | -20  |       | 75   | ొ    |

## ELECTRICAL CHARACTERISTICS (Ta=-20~75°C and Vcc=5V±10%, unless otherwise noted)

| Symbol          | Parameter                       |                                           | Test conditions                                                |                      | Limits |             |      |

|-----------------|---------------------------------|-------------------------------------------|----------------------------------------------------------------|----------------------|--------|-------------|------|

| Oyillboi        | raimietei                       |                                           | Test conditions                                                | Min.                 | Тур.   | Max.        | Unit |

| ViH             | "H" input voltage               | RESET, WR, RD,                            |                                                                | 2. 0                 |        |             | ٧    |

| VIL             | "L" input voltage               | D7~D0, RRDY,<br>SVID, STIM, DAK,<br>STNBY |                                                                |                      | -      | 0.8         | ٧    |

| V <sub>IH</sub> | "H" input voltage               | - x1                                      |                                                                | V <sub>CC</sub> ×0.8 |        |             | V    |

| $V_{iL}$        | "L" input voltage               | _^'                                       |                                                                |                      |        | VccX0.2     | · V  |

| VT+             | Positive threshold voltage      |                                           |                                                                |                      |        | 2.4         | V    |

| VT-             | Negative threshold voltage      | SCLK, RCLK                                |                                                                | 0.6                  |        |             | ٧    |

| Vн              | Hysteresis width                | ]                                         |                                                                |                      | 0. 2   |             | V    |

| VoH             | "H" output voltage              | D7~D0, ERCLK,                             | I <sub>OH</sub> =-12mA                                         | V <sub>CC</sub> -0,8 |        |             | V    |

| VoL             | "L" output voltage              | RVID                                      | I <sub>OL</sub> =12mA                                          |                      |        | 0.55        | V    |

| VoH             | "H" output voltage              | RTIM, SRDY,                               | I <sub>OH</sub> =4mA                                           | V <sub>cc</sub> -0.8 |        |             | V    |

| VoL             | "L" output voltage              | DRQ, INT                                  | I <sub>OL</sub> =4mA                                           |                      |        | 0.55        | V    |

| Іін             | "H" input current               | RESET, WR, RD, CS, A3~A0, STNBY, SVID,    | V <sub>I</sub> =V <sub>CC</sub>                                |                      |        | 1.0         | μΑ   |

| l <sub>IL</sub> | "L" input current               | STIM, SCLK, RCLK,<br>RRDY, DAK            | V <sub>I</sub> =GND                                            |                      |        | -1.0        | μΑ   |

| lozh            | "H" output current in OFF state | D7~D0                                     | v <sub>o</sub> =v <sub>cc</sub>                                |                      |        | 5.0         | μА   |

| lozL            | "L" output current in OFF state | D7~D0                                     | V <sub>O</sub> =GND                                            |                      |        | <b>-5.0</b> | μА   |

|                 | Static consumption (standby)    |                                           | STNBY=V <sub>CC</sub> Other input=V <sub>CC</sub> , GND        |                      |        | 100         | μА   |

| lcc             | Static consumption (active)     |                                           | STNBY=GND Other input=V <sub>CC</sub> , GND                    |                      |        | 60          | mA   |

|                 | Dynamic consumption             |                                           | V <sub>I</sub> =V <sub>CC</sub> , GND<br>f <sub>X1</sub> =8MHz |                      | 35     |             | mA   |

#### TIMING REQUIREMENTS ( $T_a = -20 \sim 75^{\circ}$ and $V_{cc} = 5V \pm 10\%$ , unless otherwise noted)

| Symbol                              | Parameter                                     | Test conditions | Limits |       |      | Unit |

|-------------------------------------|-----------------------------------------------|-----------------|--------|-------|------|------|

| Эунцоі                              |                                               | rest conditions | Min.   | Тур.  | Max. |      |

| t <sub>C(X1)</sub>                  | Clock cycle                                   |                 |        | 125   |      | ns   |

| t <sub>w+(×1)</sub>                 | Clock "H" pulse width                         |                 |        | 62. 5 |      | ns   |

| t <sub>w-(x1)</sub>                 | Clock "L" pulse width                         |                 |        | 62.5  |      | ns   |

| t <sub>r(x1)</sub>                  | Clock rise time                               |                 |        |       | 20   | ns   |

| र्ष(x1)                             | Clock fall time                               |                 |        |       | 20   | ns   |

| t <sub>SU(A-RD)</sub>               | Address setup time before read                |                 | 0      |       |      | ns   |

| th(RD-A)                            | Address hold time after read                  |                 | 0      |       |      | ns   |

| t <sub>W(RD)</sub>                  | Read pulse width                              |                 | 100    |       |      | ns   |

| t <sub>SU(A-WR)</sub>               | Address setup time before write               |                 | 0      |       |      | ns   |

| th(WA-A)                            | Address hold time after write                 |                 | 0      |       |      | ns   |

| t <sub>W(WA)</sub>                  | Write pulse width                             |                 | 100    |       |      | ns   |

| t <sub>Su(D</sub> — <del>WA</del> ) | Data setup time before write                  |                 | 50     |       |      | ns   |

| th( <del>wa</del> -b)               | Data hold time after write                    |                 | 0      |       |      | ns   |

| t <sub>C(SCLK)</sub>                | Scanning clock cycle                          |                 | 250    |       |      | пѕ   |

| tw+(sclk)                           | Scanning clock "H" pulse width                |                 | 100    |       |      | ns   |

| tw-(sclk)                           | Scanning clock "L" pulse width                |                 | 100    |       |      | ns   |

| tr(sclk)                            | Scanning clock rise time                      |                 |        |       | 20   | ns   |

| tf(sclk)                            | Scanning clock fall time                      |                 |        |       | 20   | ns   |

| t <sub>su(STIM</sub> _sclk)         | Clock enable setup time before scanning clock |                 | 0      |       |      | ns   |

| th(sclk-stim)                       | Clock enable hold time after scanning clock   |                 | 10     |       |      | ns   |

| tsu(svid-sclk)                      | Scanned data setup time before scanning clock |                 | 50     |       |      | กร   |

| th(sclk-svid)                       | Scanned data hold time after scanning clock   |                 | 50     |       |      | ns   |

| tsu(RTIM_RCLK)                      | Enable setup time before recording clock      |                 | 50     |       |      | ns   |

| th(RTIM_RRDY)                       | Recording ready hold time after print enable  |                 | 0      |       |      | ns   |

| t <sub>C</sub> (RCLK)               | Recording clock cycle                         |                 | 250    |       |      | ns   |

| tw+(BOLK)                           | Recording clock "H" pulse width               |                 | 100    |       |      | ns   |

| tw-(RCLK)                           | Recording clock "L" pulse width               | 7               | 100    |       |      | ns   |

| tr(ROLK)                            | Recording clock rise time                     |                 |        |       | 20   | ns   |

| tf(RGLK)                            | Recording clock fall time                     |                 |        |       | 20   | ns   |

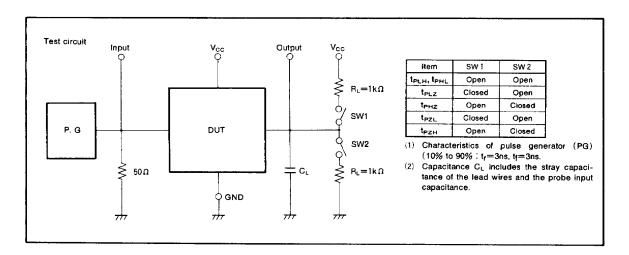

## **SWITCHING CHARACTERISTICS** ( $T_a = -20 \sim 75\%$ and $V_{cc} = 5V \pm 10\%$ , unless otherwise noted)

| Symbol                       | Parameter                                     | Test conditions       | Limits |      |      | Unit |

|------------------------------|-----------------------------------------------|-----------------------|--------|------|------|------|

|                              |                                               |                       | Min.   | Тур. | Max. | Unit |

| t <sub>PZL(RD-0)</sub>       | Data output enable time after read            |                       |        |      | 100  | ns   |

| t <sub>PZH</sub> (RD-D)      | Data output enable time after read            | C <sub>L</sub> =150pF |        |      |      | 113  |

| t <sub>PLZ</sub> (RD-D)      | Data output disable time after read           | C[_130p1              | 10     | 85   | ns   |      |

| t <sub>PHZ</sub> (AD-D)      | Data output disable time after read           |                       |        |      | 55   |      |

| t <sub>PHL</sub> (RD−INT)    | INT output propagation time after read        |                       |        |      | 150  | ns   |

| t <sub>PHL</sub> (WA-INT)    | INT output propagation time after write       |                       |        |      | 150  | ns   |

| PHL(RD-DRQ)                  | DRQ output propagation time after read        |                       |        |      | 150  | ns   |

| t <sub>PHL</sub> (WA-DRQ)    | DRQ output propagation time after write       |                       |        |      | 150  | ns   |

| PLH(STIM-SHOY)               | SRDY output propagation time after STIM input | C <sub>L</sub> =50pF  |        |      | 50   | ns   |

| tplh(RRDY-INT)               | INT output propagation time after RRDY input  |                       |        |      | 50   | ns   |

| t <sub>PHL</sub> (RRDY-INT)  | in output propagation time after AND1 input   |                       |        | :    |      | 113  |

| t <sub>PLH</sub> (RCLK-RTIM) | RTIM output propagation time after RCLK input |                       |        |      | 50   | ns   |

| tphL(RCLK-RVID)              | RVID output propagation time after RCLK input | C <sub>L</sub> =150pF |        |      | 100  | ns   |

| ta(ACLK-RVID)                | RVID output propagation time after RCLK input | GL 130pr              |        |      | 50   | ns   |

## TIMING CHARTS

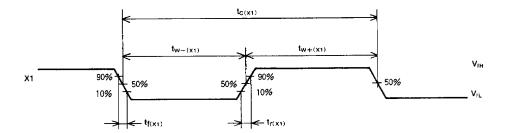

Clock timing

#### MPU bus interface timing

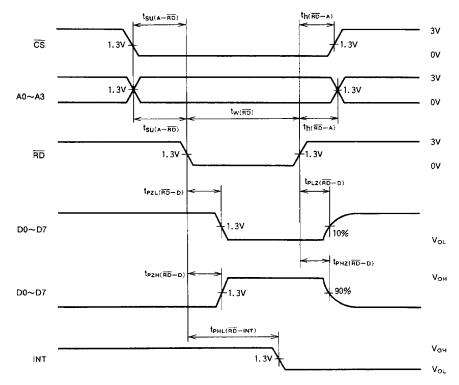

Read operation timing (M66330 to MPU)

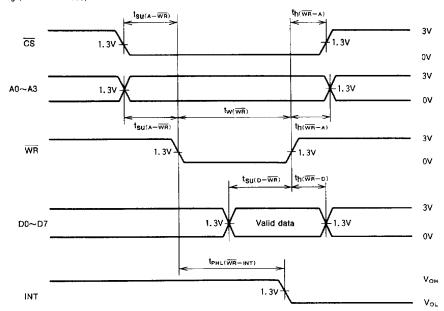

Write operation timing (MPU to M66330)

#### MPU bus DMA timing

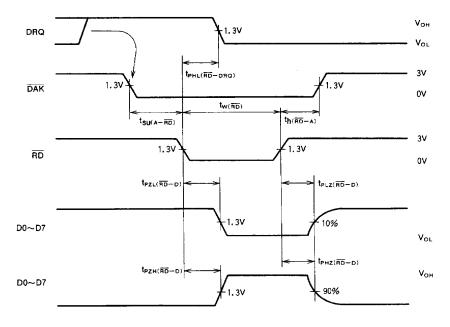

Read operation timing (M66330 to system bus)

Write operation timing (System bus to M66330)

## Serial bus timing for scanning

#### Serial bus timing for recording

(\*) fercuk=fxt/4 When using ERCLK output, connect the ERCLK output to the RCLK input.

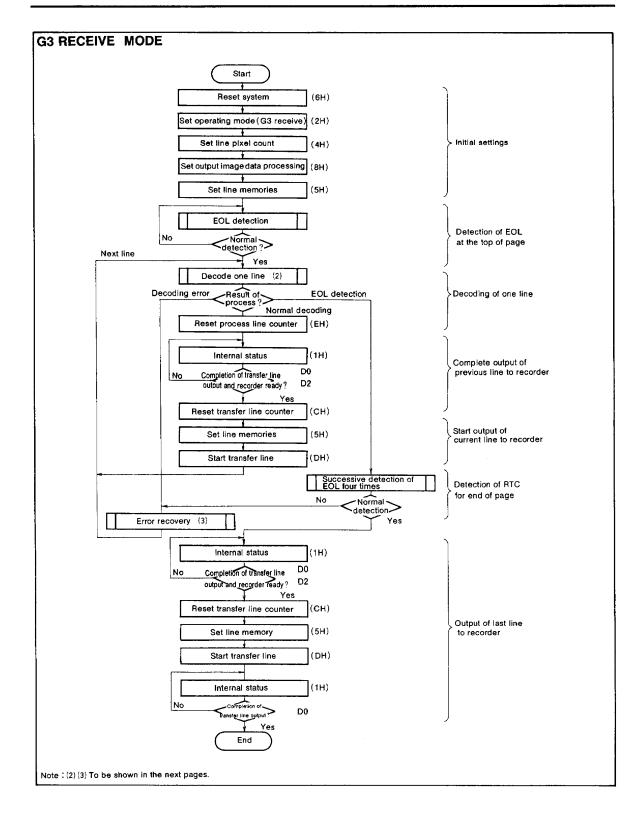

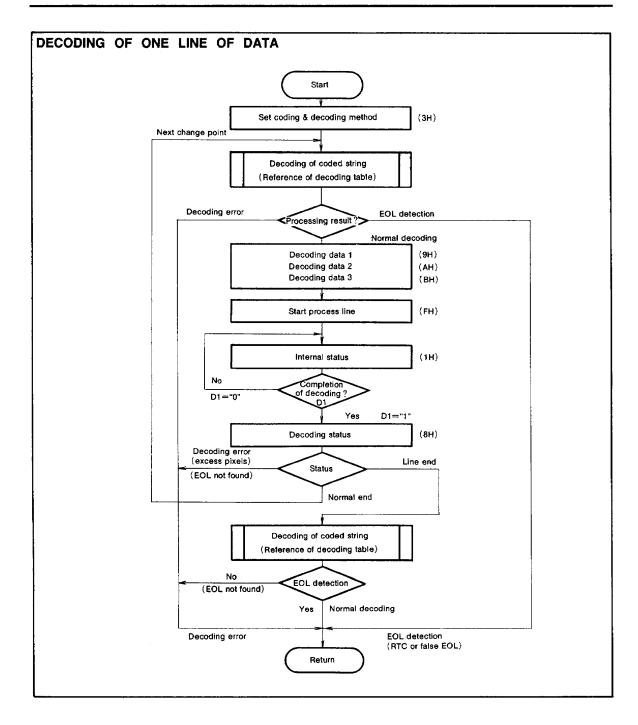

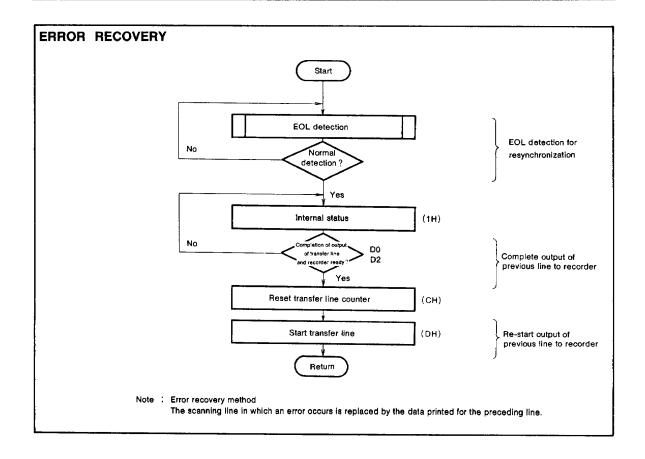

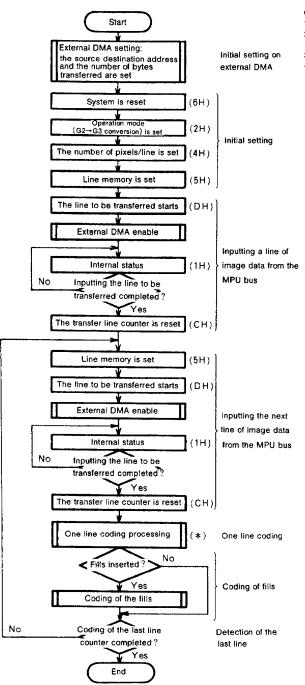

## CODING AND DECODING SOFTWARE FLOW CHARTS G3 SEND MODE Start Reset system (6H) Set operating mode (G3 send) (2H) Initial settings Set line pixel count (4H) Set line memories (5H) Start transfer line (DH) Internal status (1H) First line of data from scanner Is transfer line. input complete? D0="0" Reset transfer line counter (CH) Next line Set line memories (5H) Start of next line Start transfer line (DH) Code one line Νo Insert fill ? Coding of one line Yes Coding fill Yes End of page No Internal status (1H) Is transfer of line input complete? No End of input of next line from D0="0" Yes Reset transfer line counter (CH) RTC coding End of page End Note: (1) To be shown in the next page.

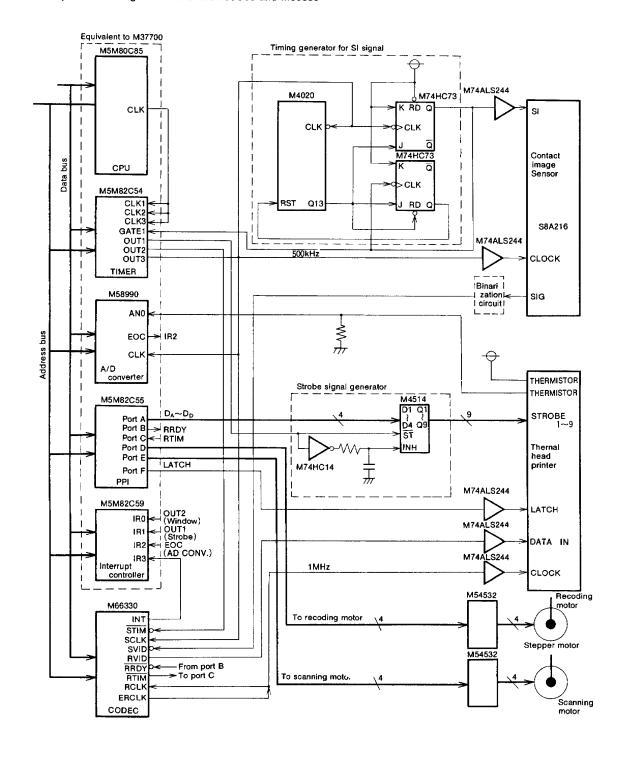

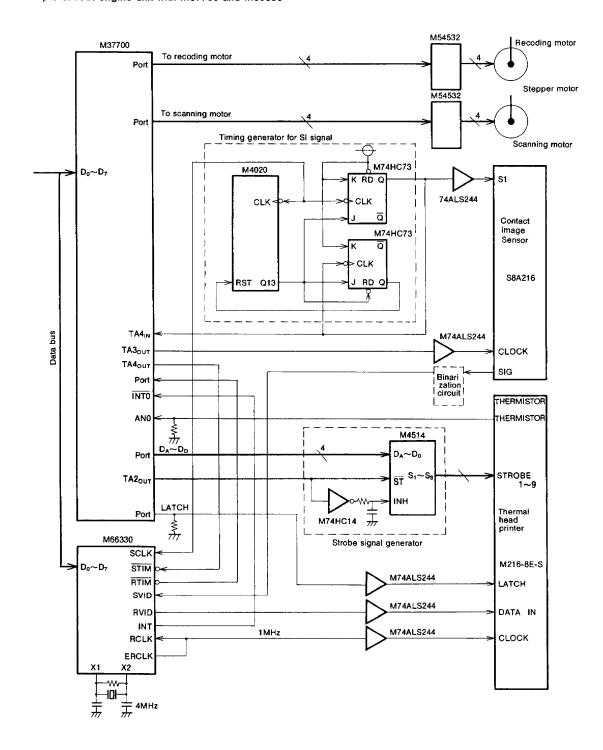

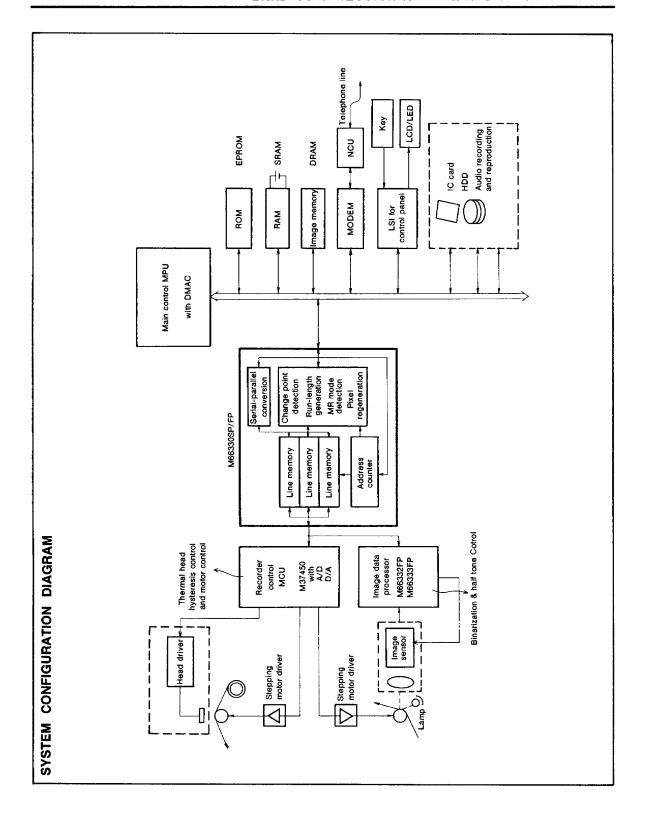

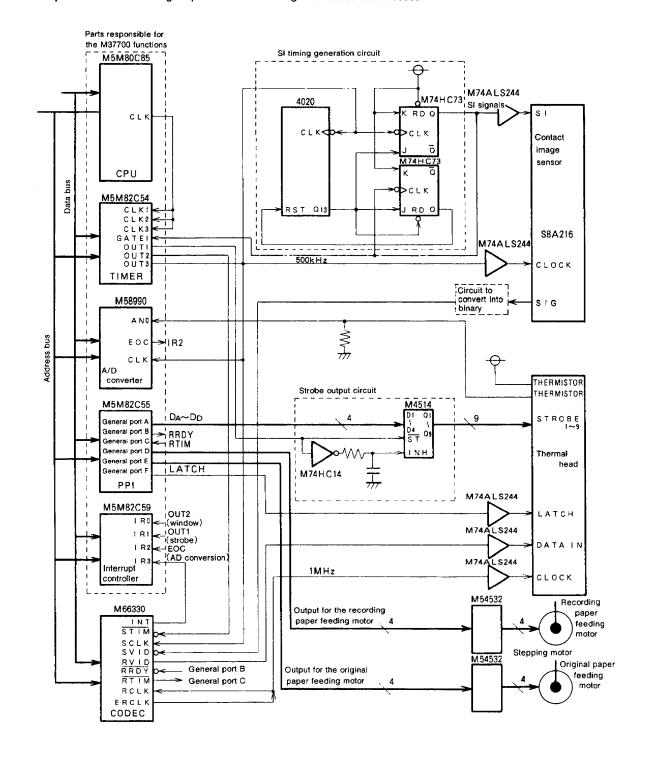

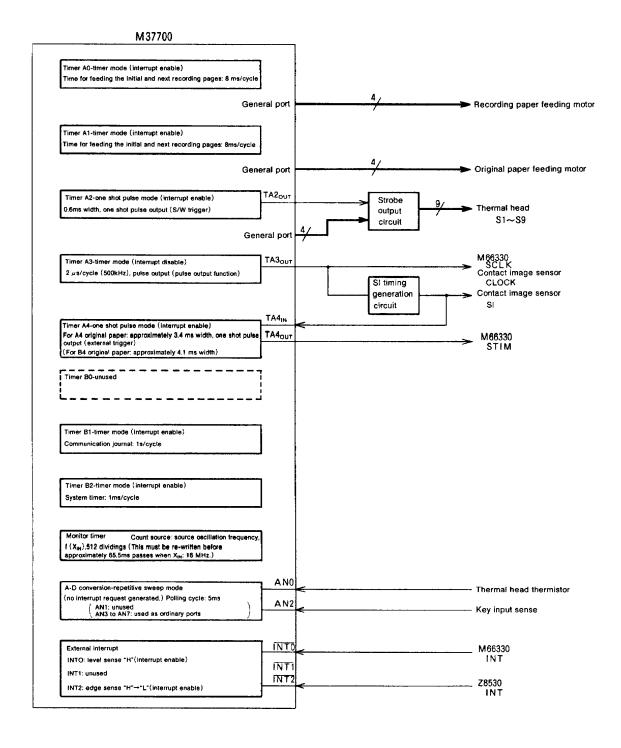

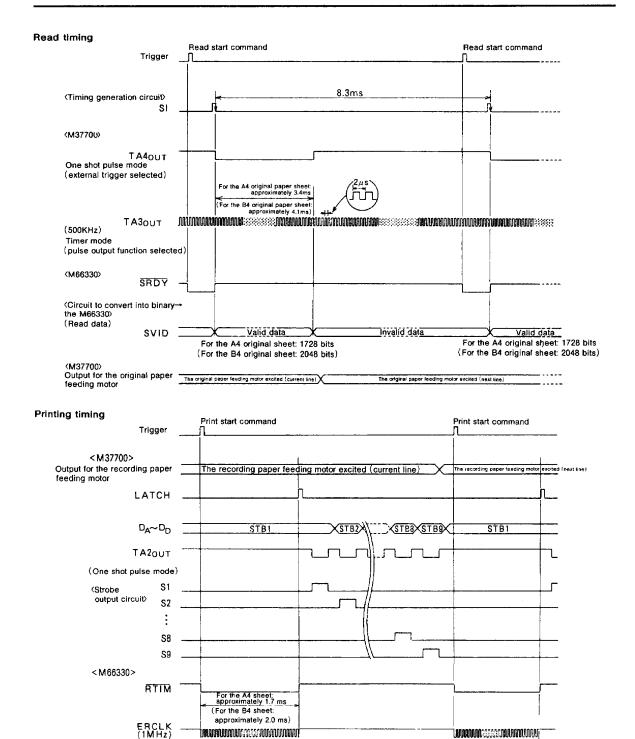

## Example of FAX engine unit with M5M80C85 and M66330

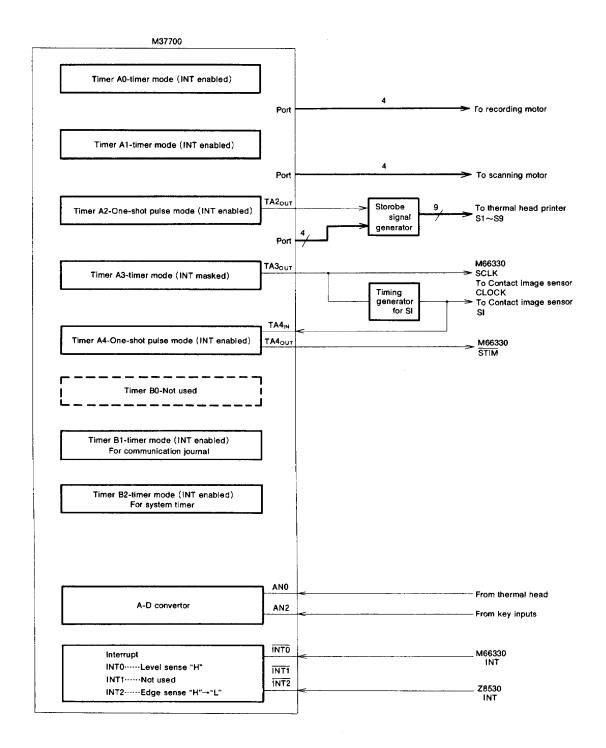

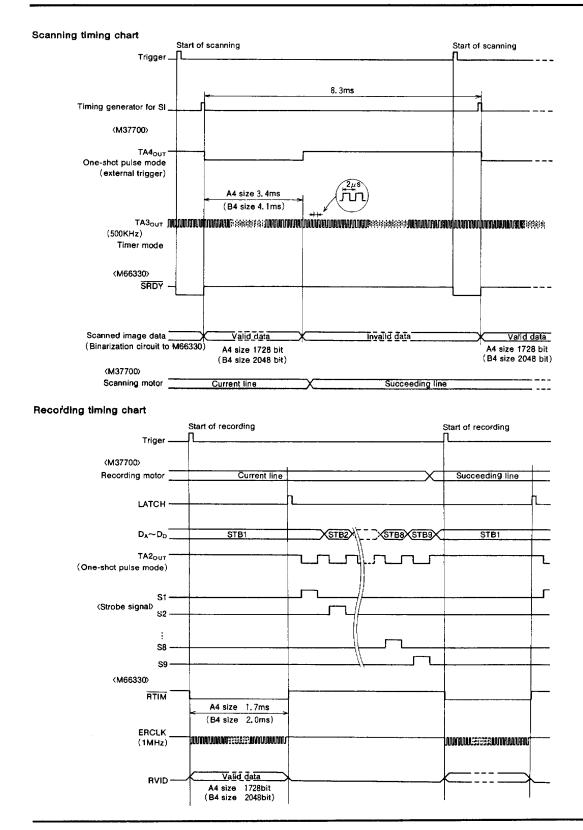

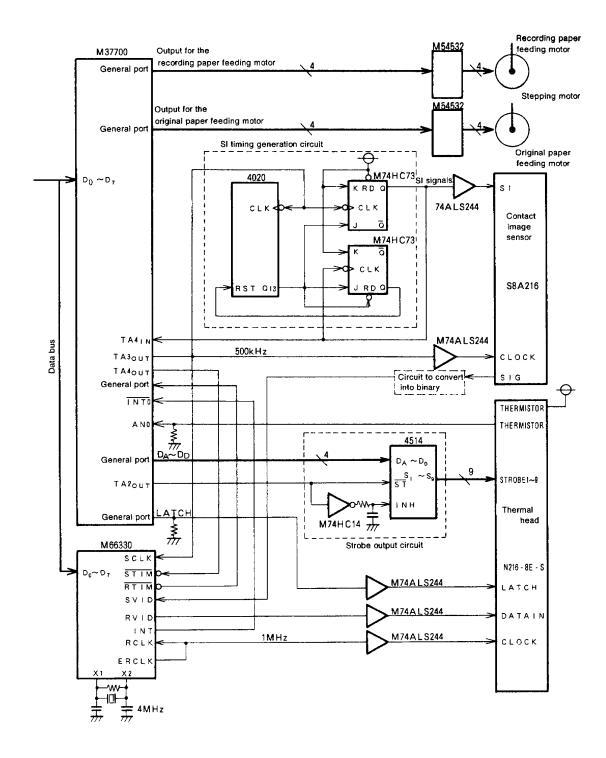

Example of FAX engine unit with M37700 and M66330

#### Example of M37700 functions

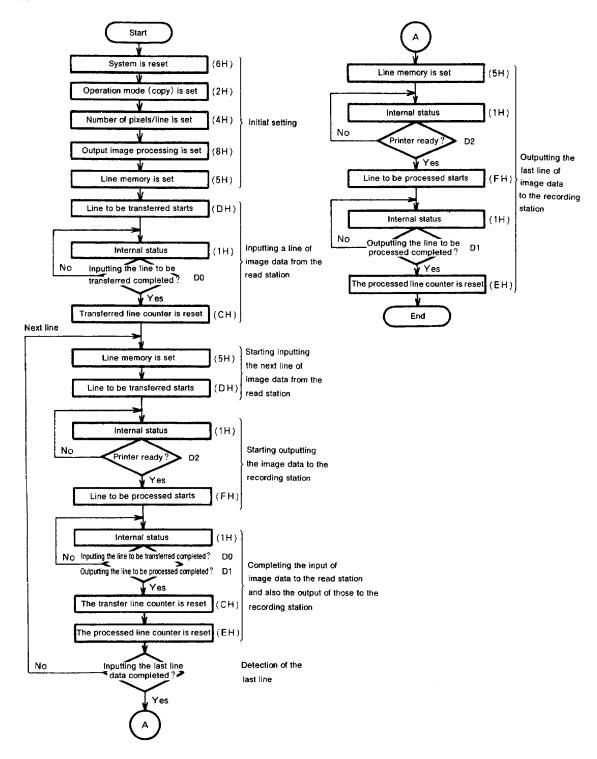

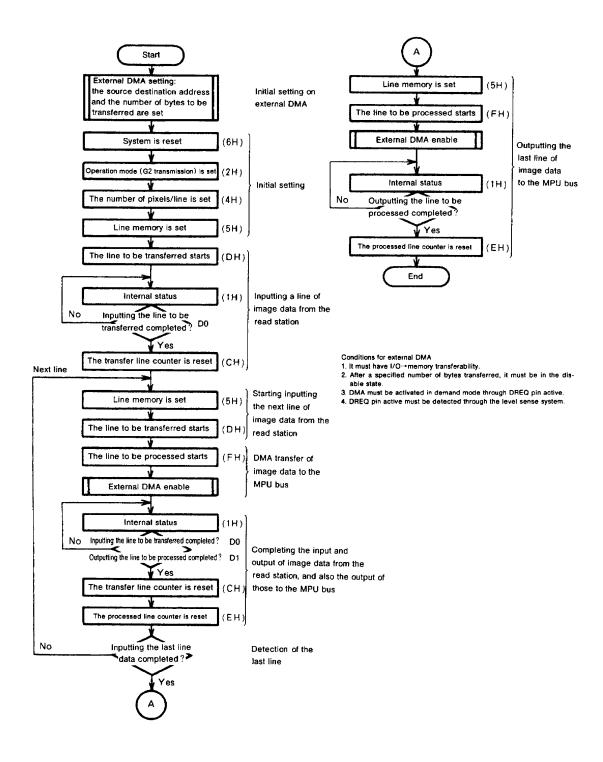

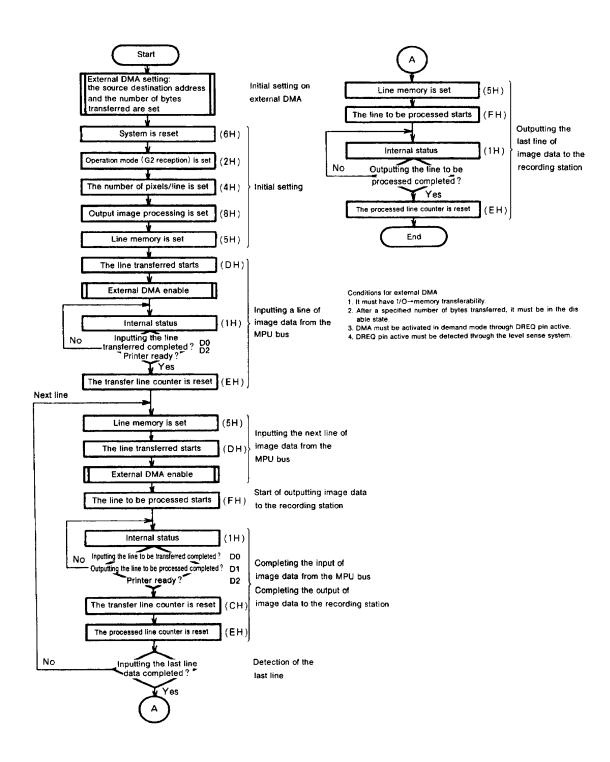

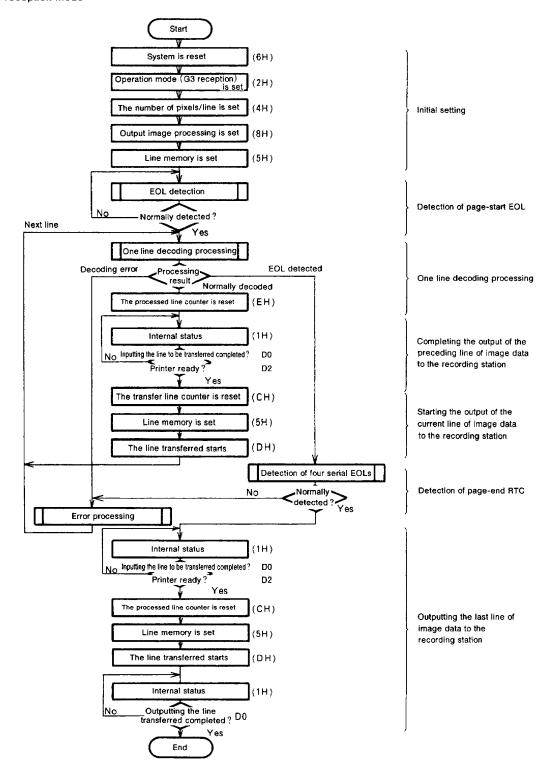

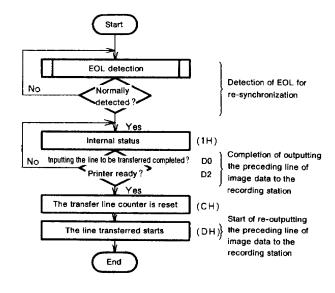

# **Flowcharts for Various Operations**

#### (1) Copy mode

#### (2) G2 transmission mode (DMA transfer mode)

(3) G2 reception mode (journal recording) (DMA transfer mode)