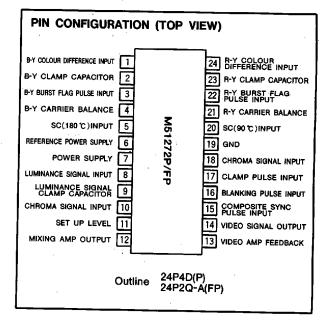

## M51272P/FP

NTSC/PAL ENCODER

### **DESCRIPTION**

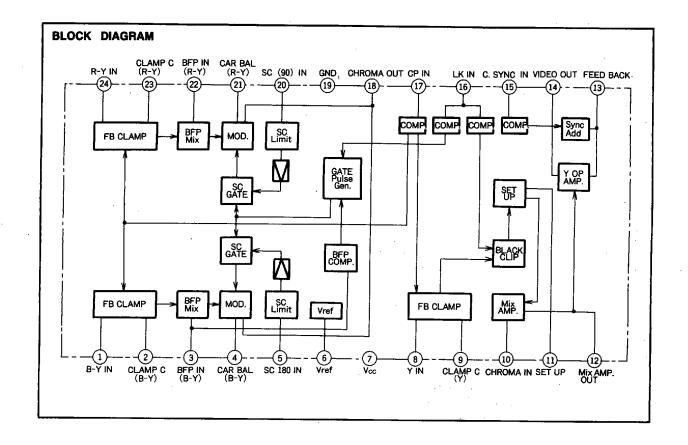

The M51272P/FP is a semiconductor integrated circuit designed for color signal modulation. It consists of R-Y and B-Y input signal clamp circuits, burst signal mixing, chroma modulator, Y/C mixing amplifier, sync adder and video signal output amplifier.

### **FEATURES**

- Low power dissipation(Vcc=5.0V, lcc=30mA typ.)

- Suitable for both NTSC and PAL.

- Adjustable carrier balance.

- able to mute luminance signal and color individually.

- Built-in 75 ohm load driver.

### **APPLICATION**

NTSC/PAL color TV sets and VCR.

### RECOMMENDED OPERATING CONDITION

### ABSOLUTE MAXIMUM RATINGS

| Symbol                           | Parameter             | Ratings         | Unit |  |

|----------------------------------|-----------------------|-----------------|------|--|

| Vcc                              | Supply voltage        | 6               | V    |  |

| Pd Power consumption             |                       | 1000(P)/500(FP) | mW   |  |

| Topr                             | Operating temperature | -20~75          | TC.  |  |

| Tstg Storing ambient temperature |                       | -40~125         | 7    |  |

| Kθ                               | Heat reduction rate   | 10.0(P)/5(FP)   | mW/° |  |

# **ELECTRICAL CHARACTERISTICS** (Ta=25°C, unless otherwise noted) **DC CHARACTERISTICS**

| Symbol | Parameter              | Test conditions | Test circuit | Limits |      |      |             |

|--------|------------------------|-----------------|--------------|--------|------|------|-------------|

|        |                        |                 | Tost circuit | Min.   | Тур. | Max. | Unit        |

| Icc    | Circuit current        | DC bias alone   |              | 20     | 30   | 40   | mA          |

| VI     | Voltage at terminal 1  | DC bias alone   |              | 2.1    | .2.3 | 2.5  |             |

| V2     | Voltage at terminal 2  | DC bias alone   |              | 1.6    | 1.8  | 2.0  | <u>_</u>    |

| V3     | Voltage at terminal 3  | DC bias alone   |              | 2. 7   | 2.9  |      | <u>v</u>    |

| V5     | Voltage at terminal 5  | DC bias alone   |              | 3.4    | 3.6  | 3.1  | <u>v</u>    |

| V6     | Voltage at terminal 6  | DC bias alone   |              | 2.8    | 3.0  | 3.8  | V           |

| V8     | Voltage at terminal 8  | DC bias alone   |              | 2. 1   |      | 3.2  | V           |

| V9     | Voltage at terminal 9  | DC bias alone   |              |        | 2.3  | 2.5  | V           |

| V10    | Voltage at terminal 10 | DC bias alone   | A            | 1.6    | 1.8  | 2.0  |             |

| V12    | Voltage at terminal 12 | DC bias alone   |              | 2.8    | 3.0  | 3. 2 | v           |

| V14    | Voltage at terminal 14 | DC bias alone   |              | 1.9    | 2, 2 | 2.5  |             |

| V18    | Voltage at terminal 18 |                 | _            | 1.7    | 2.0  | 2.3  |             |

| V20    | Voltage at terminal 20 | DC bias alone   |              | 2.8    | 3.1  | 3. 4 | V           |

| V22    |                        | DC bias alone   |              | 3. 4   | 3.6  | 3.8  | V           |

|        | Voltage at terminal 22 | DC bias alone   |              | 2.7    | 2.9  | 3.1  | V           |

| V23    | Voltage at terminal 23 | DC bias alone   |              | 1.6    | 1.8  | 2.0  | v           |

| V24    | Voltage at terminal 24 | DC bias alone   |              | 2. 1   | 2.3  | 2.5  | <del></del> |

### INPUT TERMINAL CHARACTERISTICS

| Pin No,    | Input from            | Internal bias<br>voltage<br>(standard) | Test conditions | Input res                                         | Input resistance or current<br>standard value |          |            |

|------------|-----------------------|----------------------------------------|-----------------|---------------------------------------------------|-----------------------------------------------|----------|------------|

|            |                       |                                        |                 | Min.                                              | Тур.                                          | Max.     | Unit       |

| <u> </u>   | Resistor              | 2. 3V                                  |                 | 15                                                | 20                                            | 25       | ΚΩ         |

| <u> </u>   | Resistor              | 2. 9V                                  |                 | 1.5                                               | 2                                             | 2, 5     | ΚΩ         |

| <u> </u>   | Open base (NPN)       | Not specified                          | V4=3V           |                                                   | 1                                             | 2        | μA         |

| (5)        | Resistor              | 3. 6V                                  |                 | 7, 5                                              | 10                                            | 12.5     | KΩ         |

| 8          | Resistor              | 2. 3V                                  |                 | 15                                                | 20                                            | 25       |            |

| 0          | Resistor              | 3. 0V                                  |                 | 4,5                                               |                                               |          | ΚΩ         |

| 10         | Open base (NPN)       | Not specified                          | V11=5V          | 4, 5                                              | 6                                             | 7.5      | ΚΩ         |

| <b>①</b>   | Open base (NPN)       | Not specified                          | V15=5V          | <del>-                                     </del> | 3                                             | 6        | μA         |

| 16         | Complete (DND) (ND)   |                                        | V16=5V          |                                                   | 0.5                                           | - 2      | μΑ         |

| - W        | Open base (PNP) (NPN) | Not specified                          | V16=0V          | -4                                                | -2                                            | <u>'</u> | μΑ         |

| 00         | Open base (NPN)       | Not specified                          | V17=5V          | <del></del>                                       |                                               | 2        |            |

| 20         | Resistor              | 3. 6V                                  |                 | 7.5                                               | 10                                            |          | <u>μ</u> Α |

| <b>2</b> D | Open base (NPN)       | Not specified                          | V21=3V          | 7.5                                               | - 10                                          | 12, 5    | ΚΩ         |

| 22         | Resistor              | 2.9V                                   | 451-34          |                                                   | <u></u>                                       | 2        | μА         |

| 20         | Resistor              | 2, 3V                                  | <del>_</del>    | 1.5                                               | 2                                             | 2.5      | κΩ         |

| ~          | 1.10010101            |                                        | <del>-</del>    | 15                                                | 20                                            | 25       | ΚΩ         |

## OUTPUT TERMINAL CHARACTERISTICS

| Pin No. | Output from            | Test conditions                | Bias current |      |      |      |

|---------|------------------------|--------------------------------|--------------|------|------|------|

| 120     | E-Marketta - /NBN      |                                | Min.         | Тур. | Max. | Unit |

|         |                        | Ammeter between 12 pin and Vcc | 160          | 200  | 240  | μА   |

|         | Emitter follower (NPN) | Ammeter between 18 pin and Vcc | 1.3          | 1.6  | 1.9  | mA   |

**■** 6249826 0021132 907 **■**

### **AC CHARACTERISTICS**

| مناها  | Parameter                                                                        |                                                                 | Test conditions                                                                       | Test circuit | Limits       |              |            | Unit              |

|--------|----------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------|--------------|--------------|------------|-------------------|

| Symbol |                                                                                  | Parameter                                                       | Test conditions                                                                       | Test circuit | Min.         | Тур.         | Max.       | UM                |

| VccR   | Operating supply voltage range                                                   |                                                                 | There Shall not be any abnor-<br>mal operation in the standard<br>application circuit |              | 4.0          | 5. 0         | 6.0        | ٧                 |

| СВЬ    |                                                                                  | Carrier balance DC voltage                                      | Pin4 terminal voltage shall be<br>variable. Carrier leakage shall<br>be minimum.      |              | 2.9          | 3. 0         | 3. 1       | v                 |

| Gmb    | }.                                                                               | Demodulation output                                             | SG1 200mV <sub>P-P</sub> input                                                        |              | 500          | 600          | 700        | mV <sub>P-P</sub> |

| Lb     | Input linearity characteristics. SG1 200mV <sub>P-P</sub> , 400mV <sub>P-P</sub> |                                                                 |                                                                                       | <b>-</b> 5   | 0            | . 5          | %          |                   |

| Swb    |                                                                                  | Sub-carrier input range                                         | SG2 output level shall be variable.                                                   |              |              | _            | 0.1        | V <sub>P-P</sub>  |

| CBr    |                                                                                  | Carrier balance DC voltage                                      | Pin21 terminal voltage shall be variable. Carrier leakage shall be minimum.           |              | 2.9          | 3.0          | 3.1        | ٧                 |

| Gmr    | <b> </b>                                                                         | Demodulation output                                             | SG1 200mV <sub>P-P</sub> input                                                        |              | 500          | 600          | 700        | mV <sub>P-P</sub> |

| Lr     | <b>~</b>                                                                         | Input linearity characteristics                                 | SG1 200mVp-p, 400mVp-p                                                                | В            | -5           | 0            | 5          | %                 |

| Swr    |                                                                                  | Sub-carrier input range                                         | SG2 output level shall be variable.                                                   | ·            | _            | <del>-</del> | 0.1        | V <sub>P-P</sub>  |

| B/R    | B-Y, I                                                                           | R-Y demodulation gain ratio                                     | .1                                                                                    |              | 0.8          | 11           | 1.2        | _                 |

| △R     | B-Y, F                                                                           | R-Y sub-carrier orthogonality                                   | Difference of sub-carrier phase delay                                                 |              | _            | 0            | ±10        | deg               |

| Gbb    | gui                                                                              | B-Y burst gain                                                  | Burst output level when BFP is 1V <sub>P-P</sub> .                                    |              | 200          | 300          | 400        | mV <sub>P-P</sub> |

| Gbr    | Burst mixing                                                                     | R-Y burst gain                                                  | Burst output level when BFP is 1V <sub>P-P</sub> .                                    |              | 200          | 300          | 400        | тV₽-₽             |

| SCth   | Bar                                                                              | B-Y burst input SC GATE threshold                               | Pin3 voltage shall be variable.                                                       |              | _            | -            | 0.7        | v                 |

| Gγ     | نے                                                                               | Gain                                                            | SG3 APL 100% input 200mV <sub>P-P</sub>                                               |              | 7            | 9            | 11         | d₿                |

| LY     | ≺<br>MIX AMP.                                                                    | Input linearity characteristics                                 | SG3 200mV <sub>P-P</sub> , 400mV <sub>P-P</sub>                                       | c            | <b>-5</b>    | 0            | 5          | <u>%</u>          |

| BWY    | Σ                                                                                | Frequency characteristics                                       | Frequency which changes GY to -3dB.                                                   |              | 10           | _            | _          | MHz               |

| Gc     | ڀ                                                                                | Gain                                                            | SG4 1MHz, 200mV <sub>P-P</sub>                                                        |              | 7            | 9            | 11         | dB                |

| Lc     | CAMP                                                                             | Input linearity characteristics                                 |                                                                                       |              | -5           | 0            | 5          | %                 |

| BWc    | Σ                                                                                | Frequency characteristics                                       | Frequency which changes GC to -3dB.                                                   |              | 10           | _            | _          | MHz               |

| Gv     | 8 6                                                                              | Gain                                                            | SG3 APL 100%, 200mV <sub>P-P</sub>                                                    |              | -2           | . 0          | 2          | dB                |

| DLv    | Video<br>Op-amp                                                                  | Output dynamic range                                            | SG3 APL 100% Output level shall be variable.                                          | D            | 1.0          | _            |            | V <sub>P-P</sub>  |

| SL     | Set u                                                                            | p level                                                         | Pin11 terminal voltage shall be variable. APL 100%, 200mV <sub>P-P</sub>              |              | 2.8          | 3. 0         | 3. 2       | V                 |

| SYth   | Add                                                                              | C. SYNC pulse threshold                                         | Pin15 terminal voltage shall be variable, pin14 output                                |              | 2.3          | 2.5          | 2. 7       | ٧                 |

| SYL    | 15                                                                               | Synchronizing level                                             | 15 Pin synchronizing pulse input                                                      |              | 450          | 600          | 750        | mV                |

| SYt1   | Syn                                                                              | Delay time 1                                                    | 15 Pin synchronizing pulse input                                                      | С            | _            |              | 200        | ns                |

| SYt2   |                                                                                  | Delay time 2                                                    | 15 Pin synchronizing pulse input                                                      |              | _            |              | 200        | ns                |

| BLKyth |                                                                                  | Blanking pulse Y system<br>threshold                            | Pin16 terminal voltage shall be variable.                                             |              | 1.3          | 1.5          | 1.7        | ٧                 |

| BLKcth | C blanking                                                                       | Blanking pulse C system threshold                               | Pin16 terminal voltage shall be variable.                                             |              | 3.3          | 3.5          | 3. 7       | ٧                 |

| △Vcb   | O .                                                                              | R-Y blanking carrier leakage   Sub-carrier input, 16pin: 0V, 5V |                                                                                       | -1           |              |              | -25        | dB ·              |

| △Vcr   | >                                                                                |                                                                 |                                                                                       |              | <del>-</del> |              | -25        | dB                |

| △Vsb   | ]                                                                                | B-Y blanking signal leakage                                     | Signal input, 16pin: 0V, 5V                                                           |              | _            |              | <b>-25</b> | dB                |

| △Vsr   |                                                                                  | R-Y blanking signal leakage                                     | Signal input, 16pin: 0V, 5V                                                           |              |              |              | 25         | dB                |

| CPth   | Clam                                                                             | ping pulse threshold                                            | Pin17 terminal voltage shall be variable.                                             | С            | 1.8          | 2.0          | 2. 2       | ٧                 |

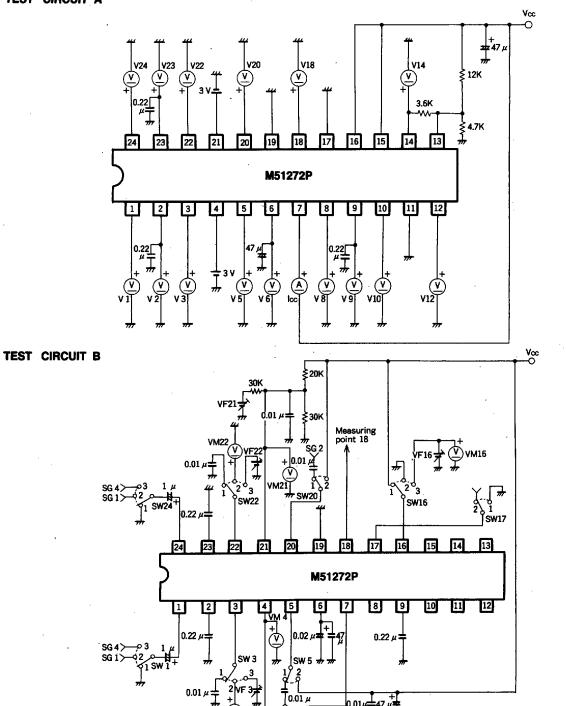

## ELECTRICAL CHARACTERISTICS TEST METHOD loc, $V_1 \sim V_{24}$

Each value read by ammeter or voltmeter is the measured value each measuring point.

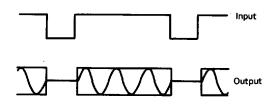

### INPUT SIGNAL

| SG No. | Waveform | Standard                                                       | Remarks                                                                 |

|--------|----------|----------------------------------------------------------------|-------------------------------------------------------------------------|

| SG1    | 10 μ s   | Level variable                                                 | Unless otherwise<br>specified, level shall<br>be 200mV <sub>P-P</sub> . |

| SG2    |          | 4. 4336MHz, square<br>wave, duty 50%,<br>output level variable | Unless otherwise specified, output shall be 1 Vp-p.                     |

| SG3    |          | APL100% signal,<br>òutput level variable                       |                                                                         |

| SG4    |          | Sine wave, frequency output level variable                     |                                                                         |

| СР     | 5V<br>0V | Shall be synchronous with SG1 and 3.                           | Shall be close to burst position.                                       |

| C.SYNC | 5 V 0 V  | Shall be<br>synchronous with<br>SG1 and 3.                     |                                                                         |

| BLK    | 5v       | Shall be<br>synchronous with<br>SG1 and 3.                     | Horizontal blanking<br>interval                                         |

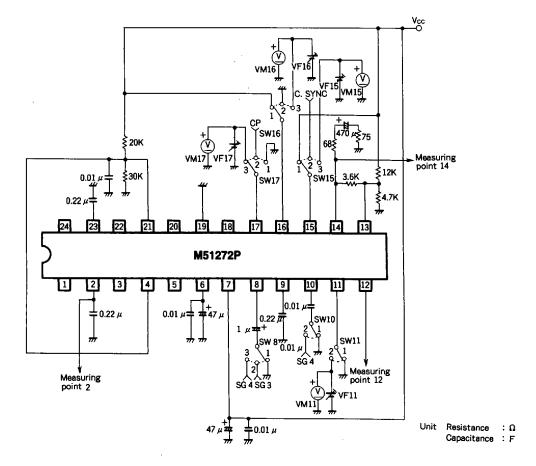

### TEST CIRCUIT A

20K

Unless otherwise specified, set SWs to 1

$\begin{array}{ccc} \text{Unit} & \text{Resistance} & : \Omega \\ & \text{Capacitance} & : F \end{array}$

### B-Y,R-Y CARRIER BALANCE ADJUSTMENT

B-Y: Set SW20 to 2.Adjust VF21 so that VM21 indicates approximately 3V.Input a square wave of 4.4MHz, 1Vp-p and duty 50% from SG2.Adjust VF4 so that 4.4MHz component output at measuring point 18 reads minimum value.

R-Y: Set SW5 to 2. Input a signal from SG2.Adjust VF21 so that 4.4MHz component output at measuring point 18reads minimum value.

#### CBb and CBr

CBb and CBr represent readings of VM4 and 21 when carrier balance of each B-Y and R-Y is adjusted.

### Gmb and Gmr

With carrier balance adjusted, set SW1,17 and 20 to 2.Gmb (mVp-p) represents the output value at measuring point 18 when inputting 200mVp-p from SG1.

Set SW5,17 and 24 to 2. Gmr (mVp-p) represents the output value at measuring point 18 when inputting 200mVp-p from SG1.

#### Lb and Lr

With carrier balance adjusted, set SW1,17 and 20 to 2. In the following equation, A (mVp-p) represents output value at measuring point 18 when inputting 200mVp-p from SG-1C (mVp-p)represents output value when inputting 400mV.

Set SW5,17 and 24 to 2. Determine BmBp-p(input 200mVp-p) and DmVp-p(input 400mV)according to above procedure. The following equation is obtained.

Lr=(D-2B)/2B(%)

#### Swb and Swr

With the conditions as in 2) above, vary input level from SG2. Swb and Swr represent the input level range in which each A and B satisfies the standard.

#### R/R

From A and B obtained in 2), we get;

#### B/R=A/B

#### ⊿R

Set SW20 to 2. Adjust VF4 so that VM4 indicates approximately 3.5V(VM21:approximately 3V). Thus E(deg) represents the phase difference between SG2 input phase and output phase of measuring point 18. Set SW5 to 2(with other SWs at 1). Adjust VF21 so that VM21 indicates approximately 2.5V (VM4:approximately 3V).

In the same manner determine the phase difference F(deg) between input and output. We then get;

#### Gbb and Gbr

Adjust carrier balance and set SW3 and 20 to 2.V3(V) represents the VM3 voltage reading at pin 3 terminal. Set SW3 to 3. Adjust VF3 so that VM3 reads V3+1V. Gbb(mVp-p)represents output level at measuring point 18.

Set SW5 and 22 to 2. V22(V) represents the voltage reading of VM22 at pin 22 terminal.Set SW 22 to 3. Adjust VF22 so that VM22 reads V22+1V. Follow the same procedure to determine Gbr(mVp-p).

Adjust carrier balance and set SW3,5,16,17 and 24 to 2. V3(V) represents the voltage reading of VM3 at pin 3 terminal. Set

Apply increasing voltage higher than V3 to pin 3. Obseve measuring point 18. In the following equation, V3a(V)represents the voltage at pin 3 when the output level of measuring point 18 satisfies Gmr standard.

### SCth=V3a-V3(V)

### **BLKcth**

Adjust carrier balance and set SW1,17 and 20 to 2.input 200mVp-p from SG1. Observe output at measuring point 18. Set SW 16 to 3. Decrease terminal voltage at pin 6 slowly from 5V. Set SW 16 to 3.BLKcth(V) represents the reading of VM16 when output of measuring point 18 stops.

### △Vcb and △Vcr

Set SW 20 to 2. Adjust VF4 so that VM4 indicates approximately 2V. (VM21 shall be in a carrier balance state). In the following equation, Vcb1 represents output level at measuring point 18 when SW16 is set to 1. Vcb2 represents that of measuring point 18 when SW16 is set to 2.

4Vcb=20 log Vcb2/Vcb1(dB)

Set SW 5 to 2. Adjust VF21 so that VM21 indicates approximately 2V. (VM4 shall be in a carrier balance state). The resulting equation is;

△Vcr=20 log Vcr2/Vcr1(dB)

### △Vsb and △Vsr

Set SW1 to 3;SW5 and 20 to 2 adjusting carrier balance. Input 4.4336MHz, 200mVp-p from SG4.In the following equation, Vsb1 represents output level at measuring point 18 when SW16 is set to 1.Vsb2 represents that of measuring point 18 when SW16 is set to 2.

4Vsb=20 log Vsb<sub>2</sub>/Vsb<sub>1</sub>(dB)

Set SW 24 at 3;SW5 and 20 at 2. The resulting equation is;

√ Vsr=20 log Vsr₂/Vsr₁(dB)

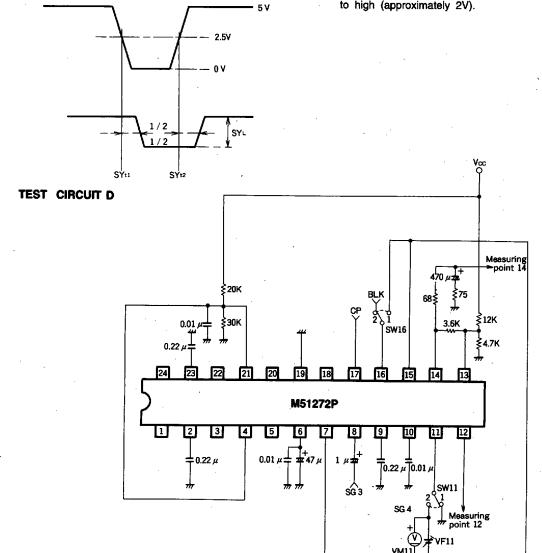

### TEST CIRCUIT C

Unless otherwise specified, SWs shall be set to 1.

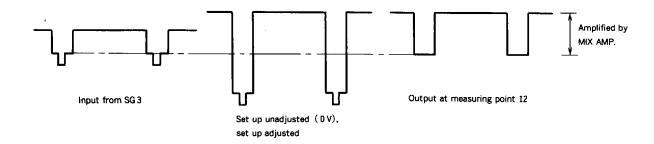

#### Gy

Set SW8 and 17 to 2. Input an APL100% signal at SG3. In the following equation, G(mVp-p) represents the output level at measuring point 12.

### Gy=20 log G/200(dB)

### Ly

as in 1),vary input level from SG3 into 400mVp-p. In the following equation, H (mVp-p) represents the output level at measuring point 12.

### **BWy**

Set SW8 to 3;input 200mVp-p from SG4 and vary frequency. BWr represents the frequency by which gain at measuring point 12 becomes -3dB compared to Gy.

#### Gc

Set SW10 to 2;input 200mVp-p,1MHz from SG4.In the following equation, I (mVp-p) represents the output level at measuring point 12.

#### Lc

as in 4),vary input level from SG4 into 400mVp-p. In the following equation, J (mVp-p) represents the output level at measuring point 12.

### **BWc**

Set SW10 to 2;input 200mVp-p from SG4 and vary frequency. BWc represents the frequency by which gain at measuring point 12 becomes -3dB compared to Gc.

#### SYth

Set SW15 to 3.Slowly decrease pin (5) terminal voltage from 5V by adjusting VF15. Observe measuring point 14.SYth(V) represents the VM15 reading when DC voltage at measuring point 14 decreases from 2V to approximately 1.5V.

### SYL,SYt1 and SYt2

Set SW15 to 2.Input C. Sync pulse. Determine SYL, SYt1 and SYt2 at measuring point 14 as follows.(SW11 shall be set to 2. VF11=3V)

### **BLKyth**

Set SW16 to 3. Slowly decrease pin (6) terminal voltage from 5V by adjusting VF16. Observe measuring point 12. BLKyth(V), represents the VM16 reading when pin (2) terminal voltage decreases from high (approximately 2.2V) to low (approximately 1V).

### **CPth**

Set SW17 to 3. Slowly decrease pin ⑦ terminal voltage from 5V using VF17. CPth represents the VM17 reading when voltage at measuring point 2 increases from low (approximately 0V) to high (approximately 2V).

Unit Resistance : Ω Capacitance : F

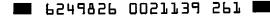

Unless otherwise specified, SWs shall be set to 1.

### Measurement of Gv

Input APL100%, 200mVp-p from SG3.In this state, Gv<sub>1</sub> and Gv<sub>2</sub> represent output levels at measuring points 12 and 14 respectively. The resulting equation is;

Gv=20 log Gv2/Gv1(dB)

### Measurement of DLv

Input APL100% from SG3.Increase the input signal level while observing measuring point 14.

DLv(Vp-p) represents the output level read just before the output signal begins to show non-linear change.

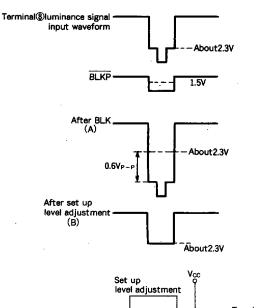

### Measurement of SL

Set SW11 and 16 to 2.Input APL100%, 200mVp-p from SG3. Adjust VF11 so that output signal pedestal level becomes equal to the input signal level.In this condition, SL(V) represents the VM11 value.

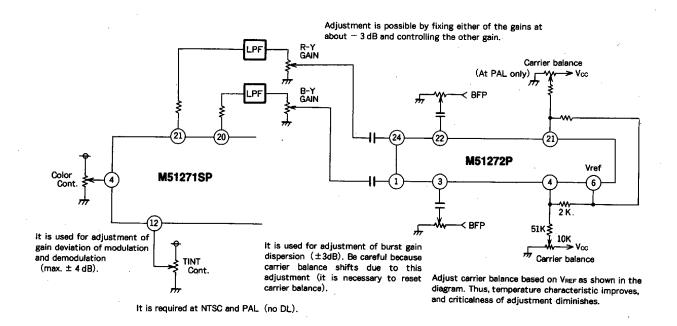

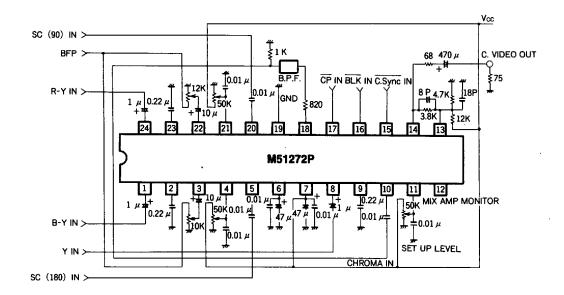

### APPLICATION EXAMPLE

Unit Resistance : Ω Capacitance : F

### PRECAUTIONS FOR APPLICATION

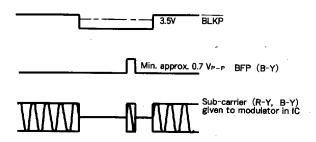

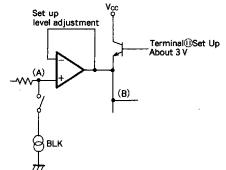

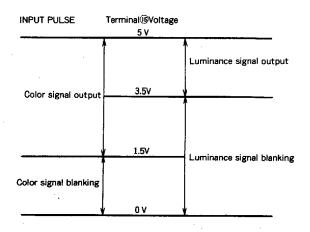

### INPUT PULSE

### 1. Blanking pulse (BLKP)

BLKP input is at pin ® with threshold for color signal and luminance signal.

a. For color signal, threshold is 3.5V. When LO is at "3.5 V - GND," sub-carrier supply for R-Y, B-Y demodulator is stopped. When burst flag pulse is inputted at B-Y, subcarrier is supplied during the period.

b. Threshold is about 1.5 V for luminance signal. When LO is at "1.5V - GND," blanking is done to luminance signal.

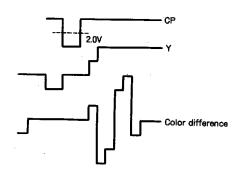

### 2. Clamping pulse (CP)

CP input is at pin ® with threshold of 2.0V. When LO is at "2.0 - GND," clamping function works. B-Y and R-Y can be set at any part of horizontal retrace line part as long as blanking is conducted to this part. In this case, when luminance signal has sync, set CP at back porch.

#### 3. Sync pulse (C. Sync)

C. Sync input is at pin (15) with threshold of 2.5V. When LO is "2.5V - GND," sync is added to C.VIDEO signal. In case of luminance signal with sync inputted is outputted, set pin áN at "2.5V - VCC." In such case, input luminance signal without blanking, and set Set Up level pin (pin (10)) to GND.

### 4. Burst flag pulse (BFP)

BFP input is at pin  $\mathfrak{D}(B-Y)$  and pin  $\mathfrak{D}(B-Y)$ . 1/9 of input level BFP is superimposed on color difference signal in the IC (input impedance  $2k\Omega$ ). When BFP is encoded to NTSC and into PAL, input only to B-Y (pin  $\mathfrak{D}$ ) and to R-Y (pin  $\mathfrak{D}$ ) respectively.

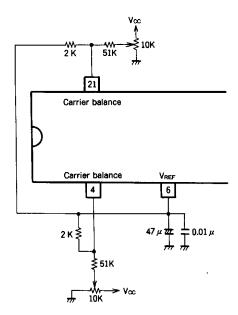

### **CARRIER BALANCE OPTIMUM ADJUSTMENT CIRCUIT**

Points 1. To apply adjusting voltage based on **(S)** pin VREF voltage.

2. To allow fine adjustment.

Improvement by the circuit above

- Carrier balance shift against temperature change is eliminated.

- 2. Adjustment range is widened allowing easy adjustment.

### Carrier balance

Ground pin  $\widehat{\mathbb{O}}$ , set clamp, set pin  $\widehat{\mathbb{O}}$  to Vcc, and then remove blanking.

Input proper burst flag pulse (NTSC→B-Y, PAL→B-Y, R-Y) and sub-carrier. Then, observing pin ® chroma output, adjust pin ④ and ② voltage so that carrier leakage becomes minimum. (Burst is outputted.)

To input sub-carrier (pin (5), (20)), input rectangular wave of (0.2 - 2) VP-P at duty (50)%.

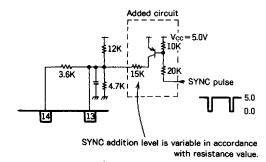

### SYNC EXTERNAL ADDITION METHOD

In the circuit above, sync dispersion is only that of external resistance dispersion.

Quantity of sync addition of the IC is uneven because it is determined by the external resistance (3.6k  $\Omega$ ) and the IC internal current.

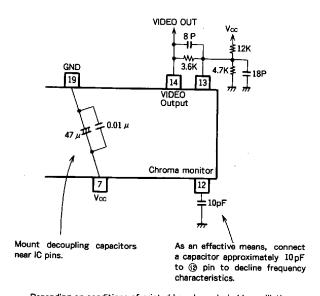

## COUNTERMEASURE FOR OSCILLATION AT OUTPUT STAGE

Depending on conditions of printed board, undesirable oscillation may be generated. In that case, refer to the information above for countermeasures.

### BLOCK DIAGRAM OF M51271 and M51272 (ENCODER)