## **Electronic Volume and Tone Control for Car Stereos**

#### Overview

The LC75374E is an electronic volume and tone control circuit that provides volume, balance, fader, bass and treble, super bass, input switching, and input and output level controls and requires a minimal number of external components to implement these functions.

#### **Functions**

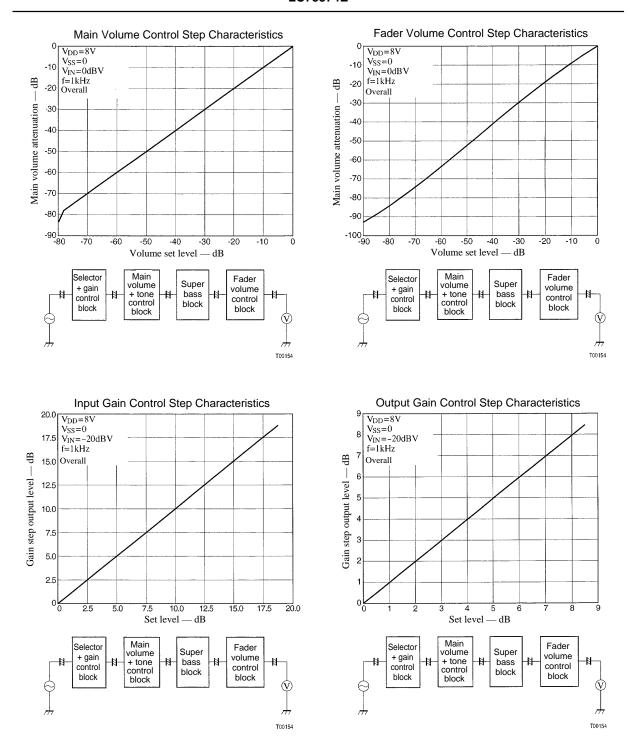

• Volume: 0dB to −79dB (in 1-dB steps) and −∞dB for a total of 81 positions.

A balance function can be implemented by controlling the left and right channels independently.

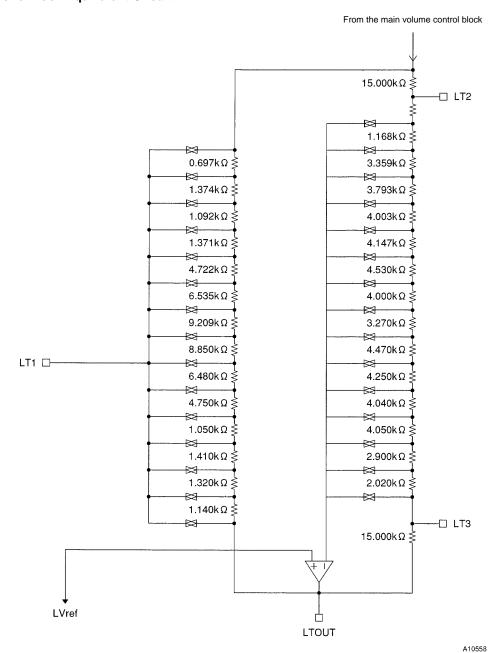

- Fader: Allows either the rear or the front channel outputs to be attenuated over 16 positions.

- (0 to −20dB in 2dB steps, −20 to −25dB in a 5dB step, −25 to −45dB in 10dB steps, −60dB, and −∞dB for a total of 16 positions.)

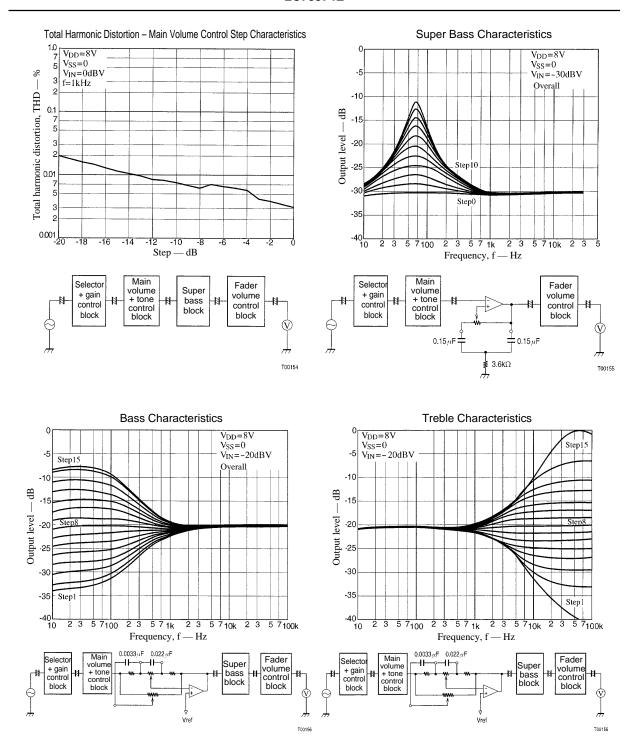

- Bass and treble: NF-type tone control circuits are formed using external CR circuits. The bass and treble can be controlled from 0dB to +11.9dB (in 1.7dB steps) for a total of 15 positions.

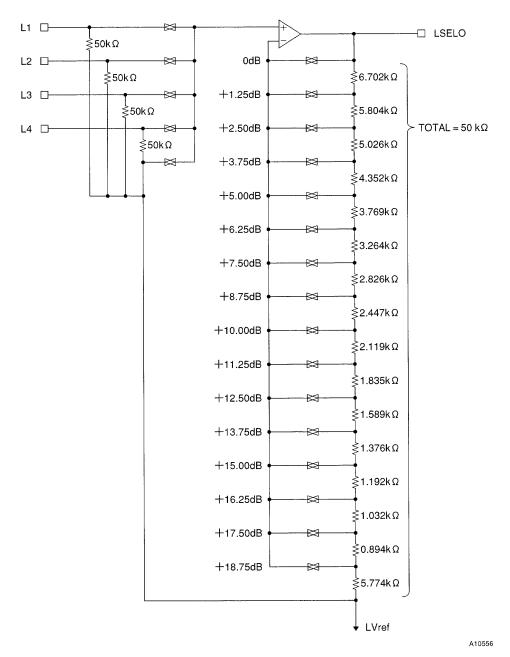

- Input gain: The input signal can be amplified by 0dB to +18.75dB (in 1.25dB steps).

- Output gain: The fader output can be set to one of three settings: 0dB, +6.5dB, or +8.5dB.

- Input switching: Both the left and right channels can be selected from one of four inputs.

- Super bass: This circuit provides peaking characteristics (T type characteristics) and 11 position settings.

#### **Features**

- On-chip buffer amplifiers minimizes the number of external components.

- Built-in reference voltage generator for the analog ground.

- All controls can be set using the serial data input circuit (CCB).

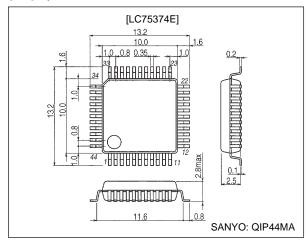

#### **Package Dimensions**

unit: mm

#### 3148-QIP44MA

- CCB is a trademark of SANYO ELECTRIC CO., LTD.

- CCB is SANYO's original bus format and all the bus addresses are controlled by SANYO.

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained berein

SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

# Specifications Absolute Maximum Ratings at $\mathrm{Ta}=25^{\circ}\mathrm{C},\,V_{SS}=0~V$

| Parameter                   | Symbol              | Conditions                                            | Ratings                          | Unit |

|-----------------------------|---------------------|-------------------------------------------------------|----------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max | V <sub>DD</sub>                                       | 11                               | V    |

| Maximum input voltage       | V <sub>IN</sub> max | CL, DI, CE                                            | $V_{SS} - 0.3$ to $V_{DD} + 0.3$ | V    |

| Allowable power dissipation | Pd max              | When Ta ≤ 85°C and mounted on a printed circuit board | 720                              | mW   |

| Operating temperature       | Topr                |                                                       | -40 to +85                       | °C   |

| Storage temperature         | Tstg                |                                                       | -50 to +125                      | °C   |

# Allowable Operating Ranges at $Ta=-40~to~+85^{\circ}C,~V_{SS}=0~V$

| Parameter                | Cumbal                      | Conditions                                                           | Ratings         |     |                 | - Unit |

|--------------------------|-----------------------------|----------------------------------------------------------------------|-----------------|-----|-----------------|--------|

| Parameter                | Parameter Symbol Conditions |                                                                      | min             | typ | max             | Oill   |

| Supply voltage           | V <sub>DD</sub>             | V <sub>DD</sub>                                                      | 7.5             |     | 9.7             | V      |

| High-level input voltage | V <sub>IH</sub>             | CL, DI, CE                                                           | 4.0             |     | $V_{DD}$        | V      |

| Low-level input voltage  | V <sub>IL</sub>             | CL, DI, CE                                                           | V <sub>SS</sub> |     | 1.0             | V      |

| Input voltage amplitude  | V <sub>IN</sub>             | CL, DI, CE, LVRIN, RVRIN, L1 to L4, R1 to R4, LFIN, RFIN, LSIN, RSIN | V <sub>SS</sub> |     | V <sub>DD</sub> | Vp-p   |

| Input pulse width        | tφ W                        | CL                                                                   | 1               |     |                 | μs     |

| Setup time               | t <sub>setup</sub>          | CL, DI, CE                                                           | 1               |     |                 | μs     |

| Hold time                | t <sub>hold</sub>           | CL, DI, CE                                                           | 1               |     |                 | μs     |

| Operating frequency      | fopg                        | CL                                                                   |                 |     | 500             | kHz    |

# Electrical Characteristics at Ta = 25°C, $V_{DD}$ = 8 V, $V_{SS}$ = 0 V

| Parameter                       | Symbol         | Conditions                                                                                             | Ratings |        |     | Unit |  |

|---------------------------------|----------------|--------------------------------------------------------------------------------------------------------|---------|--------|-----|------|--|

| Parameter                       | Symbol         | Conditions                                                                                             | min     | typ    | max | Unit |  |

| [Input Block]                   |                |                                                                                                        |         |        |     |      |  |

| Maximum input gain              | Gin max        |                                                                                                        |         | +18.75 |     | dB   |  |

| Step resolution                 | Gstep          |                                                                                                        |         | +1.25  |     | dB   |  |

| Output load resistance          | RL             |                                                                                                        | 10      |        |     | kΩ   |  |

| Output impedance                | Ro             | LSEL0, RSEL0 : $R_L = 10 \text{ k}\Omega$ , $f = 1 \text{ kHz}$ , $V_{IN} = 1 \text{ Vrms}$            |         | 46     |     | Ω    |  |

| [Output Block]                  |                |                                                                                                        | •       |        |     |      |  |

| Maximum output gain             | Gout max       |                                                                                                        |         | +8.5   |     | dB   |  |

| Output load resistance          | R <sub>L</sub> |                                                                                                        | 10      |        |     | kΩ   |  |

| Output impedance                | Ro             | LFOUT, LROUT, RFOUT, RROUT : $R_L$ = 10 k $\Omega$ , f = 1 kHz, $V_{IN}$ = 1 Vrms                      |         | 35     |     | Ω    |  |

| [Volume Control Block]          |                |                                                                                                        | •       |        |     |      |  |

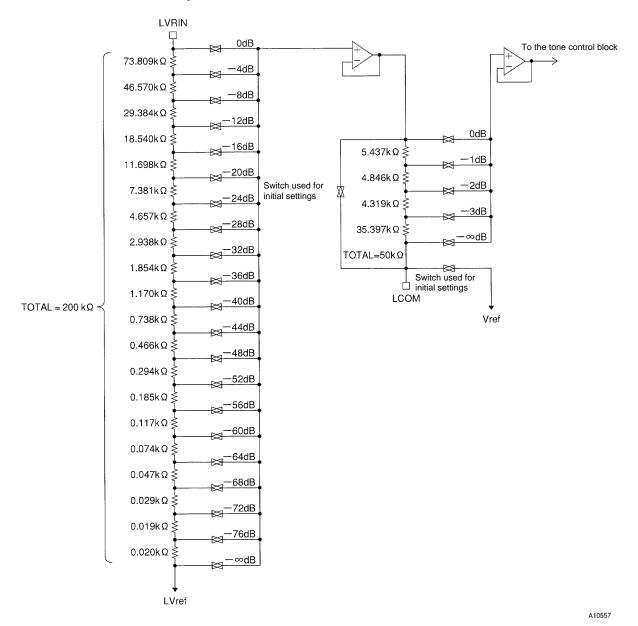

| Step resolution                 | ATstep         |                                                                                                        |         | 1      |     | dB   |  |

| Step error                      | ATerr          | STEP = 0 dB to -20 dB                                                                                  | -1      | 0      | +1  | dB   |  |

| Step entor                      | Aleii          | STEP = -20 dB to -50 dB                                                                                | -3      | 0      | +3  | dB   |  |

| Output load resistance          | R <sub>L</sub> |                                                                                                        | 10      |        |     | kΩ   |  |

| Output impedance                | R <sub>O</sub> | LTOUT, RTOUT : $R_L = 10 \text{ k}\Omega$ , $f = 1 \text{ kHz}$ , $V_{IN} = 1 \text{ Vrms}$            |         | 46     |     | Ω    |  |

| [Fader Volume Control Block]    |                |                                                                                                        |         |        |     |      |  |

|                                 |                | STEP = 0 dB to -20 dB                                                                                  |         | 2      |     | dB   |  |

| Step resolution                 | ATstep         | STEP = -20 dB to -25 dB                                                                                |         | 5      |     | dB   |  |

|                                 |                | STEP = -25 dB to -45 dB                                                                                |         | 10     |     | dB   |  |

| Step error                      | ATerr          | STEP = 0 dB to -45 dB                                                                                  | -2      | 0      | +2  | dB   |  |

| Otop ciror                      | Aich           | STEP = -45 dB to -60 dB                                                                                | -3      | 0      | +3  | dB   |  |

| Output load resistance          | R <sub>L</sub> |                                                                                                        | 10      |        |     | kΩ   |  |

| Output impedance                | R <sub>O</sub> | LFOUT, LROUT, RFOUT, RROUT : $R_L$ = 10 k $\Omega$ , f = 1 kHz, $V_{IN}$ = 1 Vrms                      |         | 46     |     | Ω    |  |

| [Bass and Treble Control Block] |                |                                                                                                        |         |        |     |      |  |

| Bass control range              | Gbass          | Max. Boost/Cut                                                                                         | ±8      | ±11.9  | ±13 | dB   |  |

| Treble control range            | Gtre           | Max. Boost/Cut                                                                                         | ±8      | ±11.9  | ±13 | dB   |  |

| Output load resistance          | R <sub>L</sub> |                                                                                                        | 10      |        |     | kΩ   |  |

| Output impedance                | R <sub>O</sub> | LTOUT, RTOUT : $R_L = 10 \text{ k}\Omega$ , $f = 1 \text{ k}\Omega$ , $V_{\text{IN}} = 1 \text{ Vrms}$ |         | 46     |     | Ω    |  |

Continued on next page.

Continued from preceding page.

# Electrical Characteristics at $Ta=25^{\circ}C,\,V_{DD}$ = $8~V,\,V_{SS}$ = 0~V

| Parameter                     | Comme hand       | Canalitiana                                                                               | Ratings |       |      | l lait |

|-------------------------------|------------------|-------------------------------------------------------------------------------------------|---------|-------|------|--------|

| Parameter                     | Symbol           | Conditions                                                                                | min     | typ   | max  | Unit   |

| [Super-Bass Block] (T type)   |                  |                                                                                           |         |       |      |        |

| Control range                 | Crange           | Max. Boost                                                                                |         | +20   |      | dB     |

| Step resolution               | ATstep           |                                                                                           |         | +2.0  |      | dB     |

| Output load resistance        | $R_L$            |                                                                                           | 10      |       |      | kΩ     |

| Output impedance              | Ro               | LSB2, RSB2 : $R_L = 10 \text{ k}\Omega$ , $f = 1 \text{ kHz}$ , $V_{IN} = 1 \text{ Vrms}$ |         | 70    |      | Ω      |

| [Overall]                     |                  |                                                                                           |         |       |      |        |

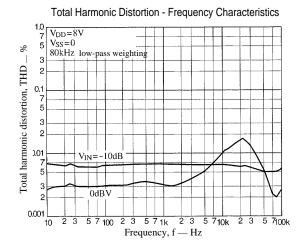

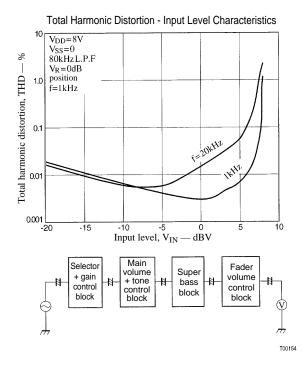

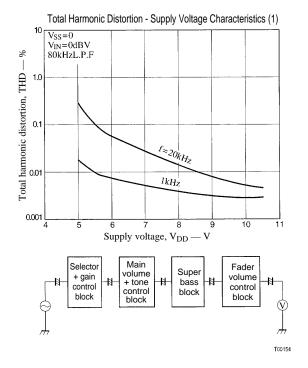

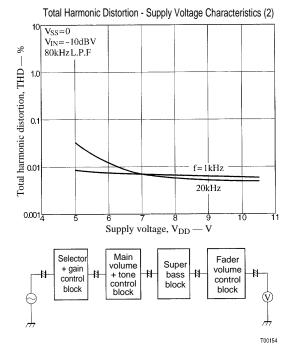

| Total harmonic distortion     | THD              | V <sub>IN</sub> = 1 Vrms, f = 1 kHz, All controls flat overall                            |         | 0.003 | 0.01 | %      |

| Crosstalk                     | CT               | $V_{IN}$ = 1 Vrms, f = 1 kHz, All controls flat overall, Rg = 1 k $\Omega$                |         | 80.5  |      | dB     |

| Output at maximum attenuation | Vo min           | V <sub>IN</sub> = 1 Vrms, f = 1 kHz, Main volume setting: -∞                              |         | -80   |      | dB     |

| Output noise voltage          | V <sub>N</sub> 1 | All controls flat overall, (IHF-A), Rg = 1 kΩ                                             |         | 8     |      | μV     |

| Output hoise voltage          | V <sub>N</sub> 2 | All controls flat overall, (DIN-AUDIO), Rg = 1 k $\Omega$                                 |         | 10    |      | μV     |

| High-level input voltage      | I <sub>IH</sub>  | CL, DI, CE, V <sub>IN</sub> = 8 V                                                         |         |       | 10   | μA     |

| Low-level input voltage       | I <sub>IL</sub>  | CL, DI, CE, V <sub>IN</sub> = 0 V                                                         | -10     |       |      | μΑ     |

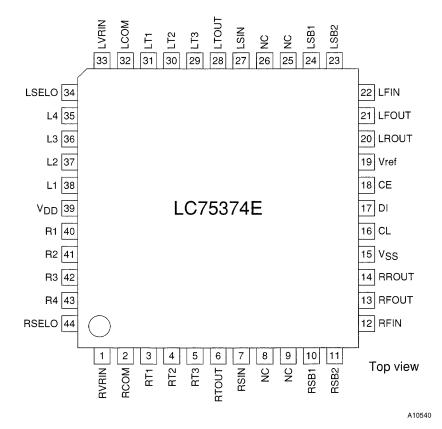

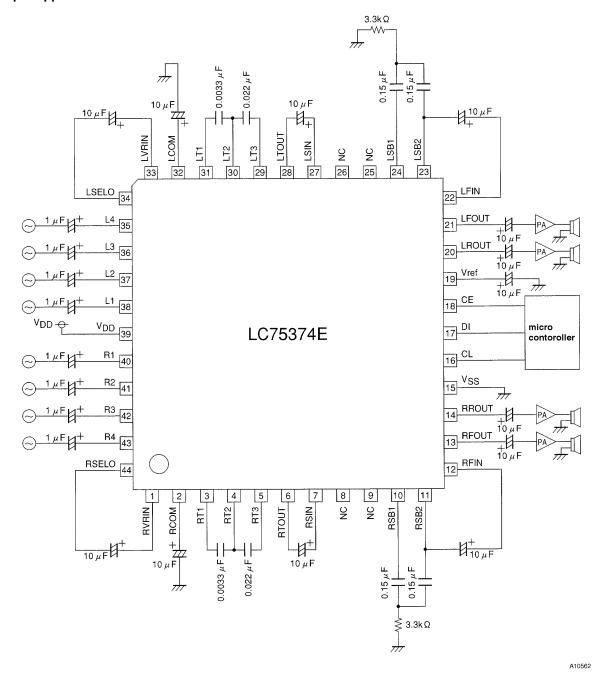

### **Pin Assignment**

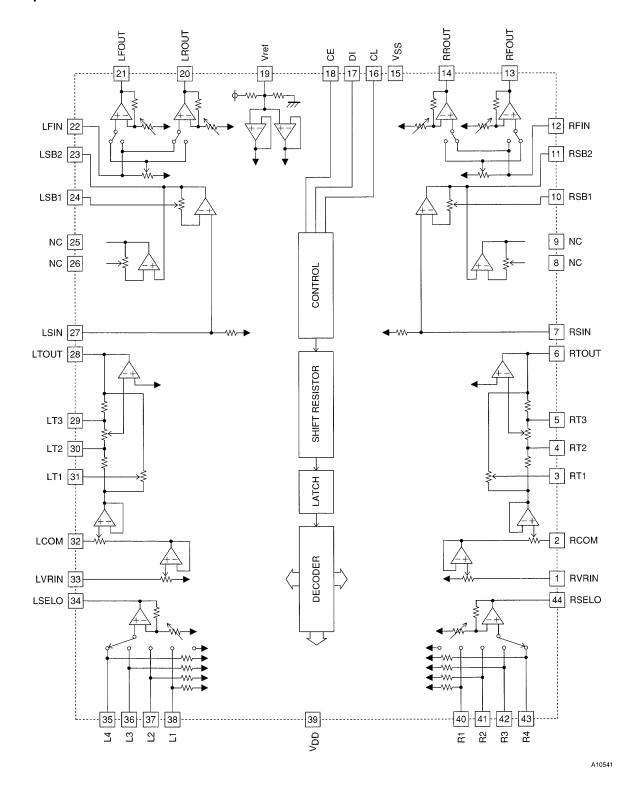

# **Equivalent Circuit**

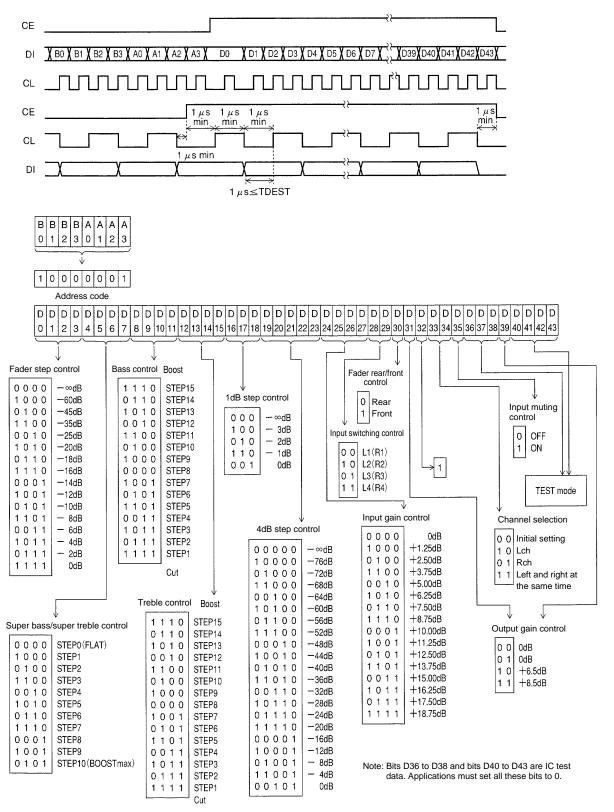

#### **Control System Timing and Data Format**

Applications must input the stipulated serial data to the CE, CL, and DI pins to control the LC75374E. The data consists of a total of 52 bits, of which 8 bits are address and 44 bits are data.

# LC75374E

# **Pin Functions**

| Pin No.              | Pin                              | Description                                                                                                                                                                                                                                                                 | Notes                  |

|----------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 19                   | Vref                             | • Supply voltage generator (0.525 $\times$ V <sub>DD</sub> ) used for the analog ground. A capacitor must be connected between Vref and V <sub>SS</sub> to remove power supply ripple.                                                                                      | LVref RVref A10543     |

| 20<br>21<br>14<br>13 | LROUT<br>LFOUT<br>RROUT<br>RFOUT | Fader outputs. The front and rear outputs can be attenuated independently.                                                                                                                                                                                                  | A10544                 |

| 22<br>12             | LFIN<br>RFIN                     | Fader inputs     These inputs must be driven by low-impedance circuits.                                                                                                                                                                                                     | VDD → VDD → A10545     |

| 24<br>23<br>10<br>11 | LSB1<br>LSB2<br>RSB1<br>RSB2     | Left channel super bass compensation capacitor connection     Left channel super bass output and compensation capacitor connection     Right channel super bass compensation capacitor connection     Right channel super bass output and compensation capacitor connection | SB1 SIN SIN SIN A10547 |

| 22<br>7              | LSIN<br>RSIN                     | Super bass input     These inputs must be driven by low-impedance circuits.                                                                                                                                                                                                 | VDD A10548             |

| 28<br>6              | LTOUT<br>RTOUT                   | Tone control outputs                                                                                                                                                                                                                                                        | LVref<br>RVref A10549  |

Continued on next page.

# LC75374E

### Continued from preceding page.

| Pin No.                                      | Pin                                          | Description                                                                                                                                                                         | Notes             |

|----------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|                                              |                                              |                                                                                                                                                                                     | ∘ V <sub>DD</sub> |

| 31<br>30<br>29<br>3                          | LT1<br>LT2<br>LT3<br>RT1                     | Tone control circuit bass and treble compensation capacitor connections.  Connect the high band compensation capacitors between the pins T1 and T2.                                 | → T1  → VDD       |

| 5                                            | RT2<br>RT3                                   | Connect the low band compensation capacitors between the pins T2 and T3.                                                                                                            | T2,T3             |

| 32<br>2                                      | LCOM<br>RCOM                                 | 1dB volume control common connections                                                                                                                                               | VDD<br>A10551     |

| 33<br>1                                      | LVRIN<br>RVRIN                               | 4dB volume control inputs     These inputs must be driven by low-impedance circuits.                                                                                                | LVref<br>RVref    |

| 34<br>44                                     | LSELO<br>RSELO                               | Input selector outputs                                                                                                                                                              | A10553            |

| 38<br>37<br>36<br>35<br>40<br>41<br>42<br>43 | L1<br>L2<br>L3<br>L4<br>R1<br>R2<br>R3<br>R4 | Signal inputs                                                                                                                                                                       | LVref<br>RVref    |

| 39                                           | V <sub>DD</sub>                              | Power supply                                                                                                                                                                        |                   |

| 15                                           | V <sub>SS</sub>                              | Ground                                                                                                                                                                              |                   |

| 16                                           | CL                                           | Serial data and clock inputs used for transferring control data                                                                                                                     | o ∧DD             |

| 18                                           | DI<br>CE                                     | Chip enable input. Data is written into the internal latches and the analog switches operate when this pin goes from high to low. Data transfers are enabled when this pin is high. | A10555            |

| 8, 26<br>9, 25                               | NC                                           | <ul> <li>Unused pins. These pins must be connected to V<sub>SS</sub>.</li> <li>Unused pins. These pins must be left open.</li> </ul>                                                |                   |

|                                              |                                              |                                                                                                                                                                                     |                   |

### **Input Block Equivalent Circuit**

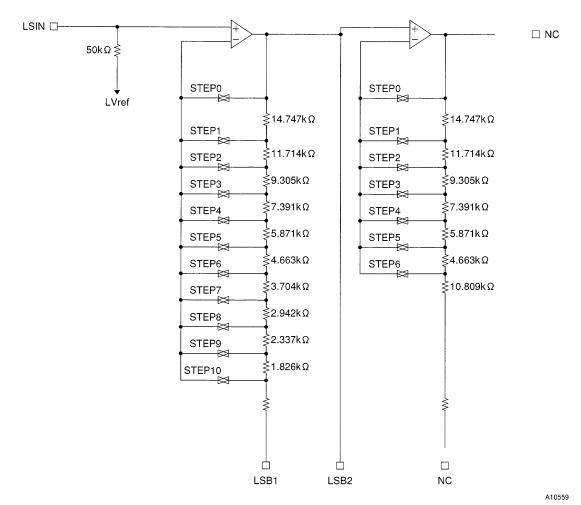

# **Main Volume Control Block Equivalent Circuit**

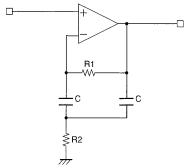

### **Tone Block Equivalent Circuit**

### **Super Bass Block Equivalent Circuit**

#### Sample external constant calculations for the super bass (T type) circuit when full boost is used

The external constants required when full boost is used with the super bass block (T type) are calculated as follows.

• Super bass (T type) equivalent circuit

A10560

- Calculation

- (1) Center frequency

$$f0 = \frac{1}{2 \times \pi \times \sqrt{R1 \times R2 \times C \times C}}$$

(2) Gain

$$G = 20\log \left(1 + \frac{R1}{2 \times R2}\right)$$

(3) Q

$$Q = \frac{C \times C \times R1}{2 \times C} \times \frac{1}{\sqrt{R1 \times R2 \times C \times C}}$$

Sample calculation

Assume:

$R1 = 64.5 \text{ k}\Omega$ , and

G = 20.65 dB, and

f0 = 72.7 Hz.

• Determine R2

Determine R2 from formula (2).

R2 =

$$\frac{64.5}{2 \times (10.78 - 1)}$$

≈ 3.3 (kΩ)

• Determine C

Determine C from formula (1).

$$C = \frac{1}{\sqrt{R1 \times R2 \times (2 \times \pi \times f0) \times (2 \times \pi \times f0)}} \approx 0.15 \,(\mu \text{F})$$

• Determine Q

Determine Q from formula (3).

Here, Q will be 2.21.

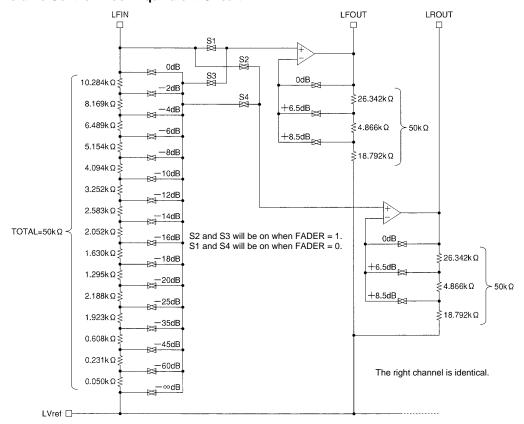

#### **Fader Volume Control Block Equivalent Circuit**

At the point that data corresponding to −∞ is transferred to the 1dB –step main volume control block, S1 and S2 will go to the open state. S3 and S4 will go to the on state at the same time.

#### **Sample Application Circuit**

## **Usage Notes**

- The internal analog switches are in undefined states when power is first applied. Applications must therefore use external circuits to mute the output until control data has been transferred.

- When setting up the initial data after power is first applied, applications must first transfer a set of IC initialization data. This initialization data consists of an address field of (10000001) and a data field of all zeros (D0 to D43 = 0). Applications must only send the actual initial data after this initialization data has been sent.

- Applications must either cover the CL, DI, and CE lines with the ground pattern or use shielded cables for these lines to prevent the high-frequency digital signals that are transmitted over these lines from entering the analog signal system.

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of November, 1998. Specifications and information herein are subject to change without notice.