LC75396NE

# Single-Chip Electronic Volume Control System

## Overview

The LC75396NE is an electronic volume control system providing control over volume, balance, 5-band equalizer, and input switching based on serial inputs.

## **Functions**

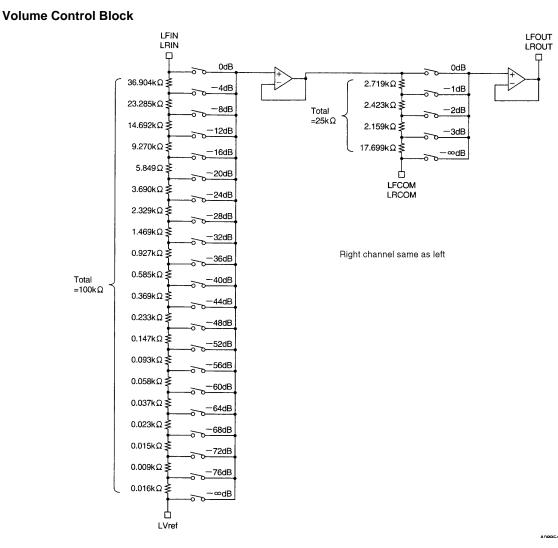

• Volume control:

The chip provides 81 levels of volume attenuation: in 1-dB step between 0 dB and -79 dB and  $-\infty$ .

Independent control over left front/rear and right front/rear channels provides balance control.

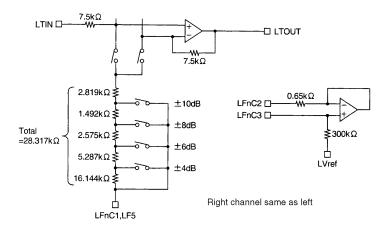

• Equalizer:

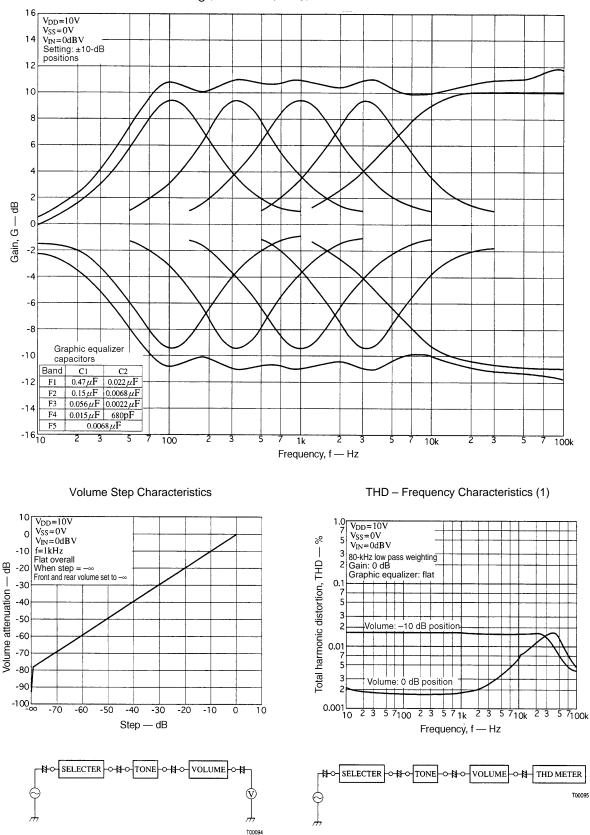

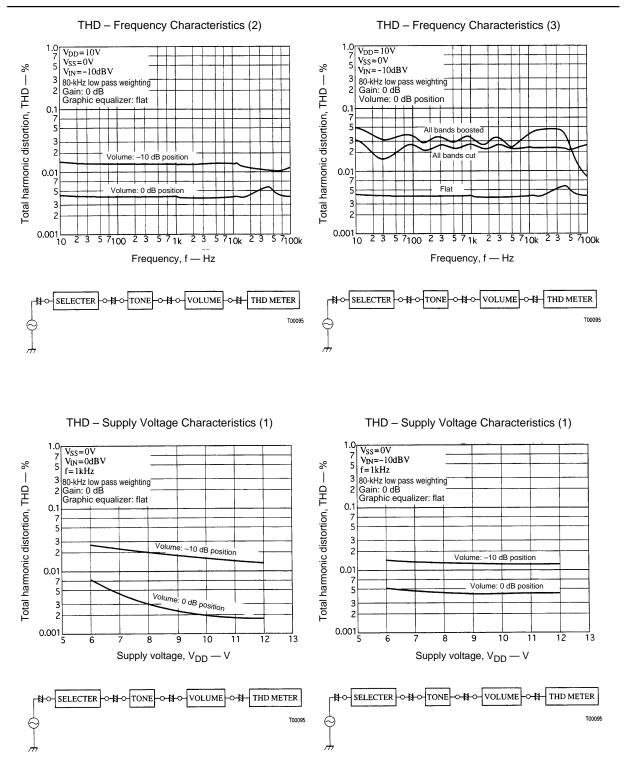

The chip provides control in 2-dB steps over the range between +10 dB and -10 dB. Four of the five bands have peaking equalization; the remaining one, shelving equalization.

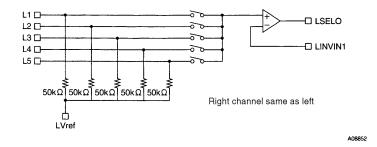

• Selector:

The left and right channels each offer a choice of five inputs. The L5 and R5 inputs can be turned on and off independently. An external constant determines the amplification for the input signal.

- Serial data input

- Supports CCB\* format communication with the system controller.

# Features

- Built-in buffer amplifiers reduce the number of external parts required.

- Silicon gate CMOS process reduces the noise of built-in switch.

- $V_{DD}/2$  reference voltage generation circuit built in.

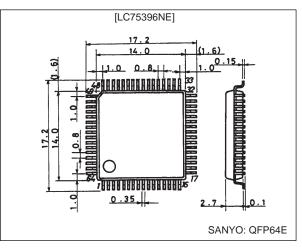

# **Package Dimensions**

unit: mm

### 3159-QFP64E

- CCB is a trademark of SANYO ELECTRIC CO., LTD.

- CCB is SANYO's original bus format and all the bus addresses are controlled by SANYO.

| Specifications                                                  |  |

|-----------------------------------------------------------------|--|

| Absolute Maximum Ratings at $Ta = 25^{\circ}C$ , $V_{SS} = 0$ V |  |

| Parameter                   | Symbol              | Conditions                                                         | Ratings                                           | Unit |

|-----------------------------|---------------------|--------------------------------------------------------------------|---------------------------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max | V <sub>DD</sub>                                                    | 11                                                | V    |

| Maximum input voltage       | V <sub>IN</sub> max | CL, DI, CE, L1 to L5, R1 to R5, LTIN, RTIN, LFIN, RFIN, LRIN, RRIN | V <sub>SS</sub> – 0.3 to<br>V <sub>DD</sub> + 0.3 | V    |

| Allowable power dissipation | Pd max              | $Ta \le 75^{\circ}C$ , with PC board                               | 550                                               | mW   |

| Operating temperature       | Topr                |                                                                    | -30 to +75                                        | °C   |

| Storage temperature         | Tstg                |                                                                    | -40 to +125                                       | °C   |

SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

| Parameter                | Symbol             | Conditions                                                            |                 | Ratings |                 |        |  |  |

|--------------------------|--------------------|-----------------------------------------------------------------------|-----------------|---------|-----------------|--------|--|--|

| Parameter                | Symbol             | Conditions                                                            | min             | typ     | max             | - Unit |  |  |

| Supply voltage           | V <sub>DD</sub>    | V <sub>DD</sub>                                                       | 6.0             |         | 10.5            | V      |  |  |

| Input high level voltage | VIH                | CL, DI, CE                                                            | 4.0             |         | V <sub>DD</sub> | V      |  |  |

| Input low level voltage  | V <sub>IL</sub>    | CL, DI, CE                                                            | V <sub>SS</sub> |         | 1.0             | V      |  |  |

| Input voltage amplitude  | V <sub>IN</sub>    | CL, DI, CE, L1 to L5, R1 to R5, LTIN, RTIN,<br>LFIN, RFIN, LRIN, RRIN | V <sub>SS</sub> |         | V <sub>DD</sub> | Vp-р   |  |  |

| Input pulse width        | t <sub>øW</sub>    | CL                                                                    | 1.0             |         |                 | μs     |  |  |

| Setup time               | t <sub>SETUP</sub> | CL, DI, CE                                                            | 1.0             |         |                 | μs     |  |  |

| Hold time                | t <sub>HOLD</sub>  | CL, DI, CE                                                            | 1.0             |         |                 | μs     |  |  |

| Operating frequency      | fopg               | CL                                                                    |                 |         | 500             | kHz    |  |  |

# Allowable Operating Ranges at Ta=- 30 to + 75°C, $V_{SS}$ = 0 V

# Electrical Characteristics at Ta = 25°C, $V_{DD}$ = 10 V, $V_{SS}$ = 0 V

| Deservator                    | Currents al        | Conditions                                                                   |     | Ratings |      |        |  |

|-------------------------------|--------------------|------------------------------------------------------------------------------|-----|---------|------|--------|--|

| Parameter Symbol (            |                    | Conditions                                                                   | min | typ     | max  | – Unit |  |

| [Input block]                 | •                  |                                                                              |     |         |      |        |  |

| Input resistance              | Rin                | L1 to L5, R1 to R5                                                           |     | 50      |      | kΩ     |  |

| Clipping level                | Vcl                | LSELO, RSELO: THD = 1.0%                                                     |     | 3.00    |      | Vrms   |  |

| Output load resistance        | RL                 | LSELO, RSELO                                                                 | 10  |         |      | kΩ     |  |

| [Volume control block]        | •                  |                                                                              |     |         |      |        |  |

| Input resistance              | Rin                | LFIN, LRIN, RFIN, RRIN                                                       |     | 100     |      | kΩ     |  |

| [Equalizer control block]     | •                  |                                                                              |     |         |      |        |  |

| Control range                 | Geq                | Max, boost/cut                                                               | ±8  | ±10     | ±12  | dB     |  |

| Step resolution               | Estep              |                                                                              | 1   | 2       | 3    | dB     |  |

| Internal feedback resistance  | Rfeed              |                                                                              | 17  | 28      | 39   | kΩ     |  |

| [Overall characteristics]     | •                  |                                                                              |     |         |      |        |  |

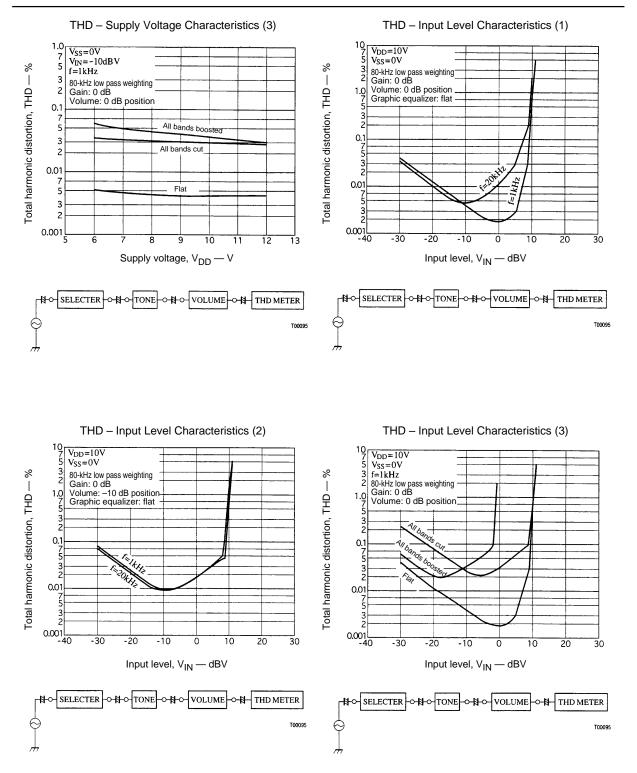

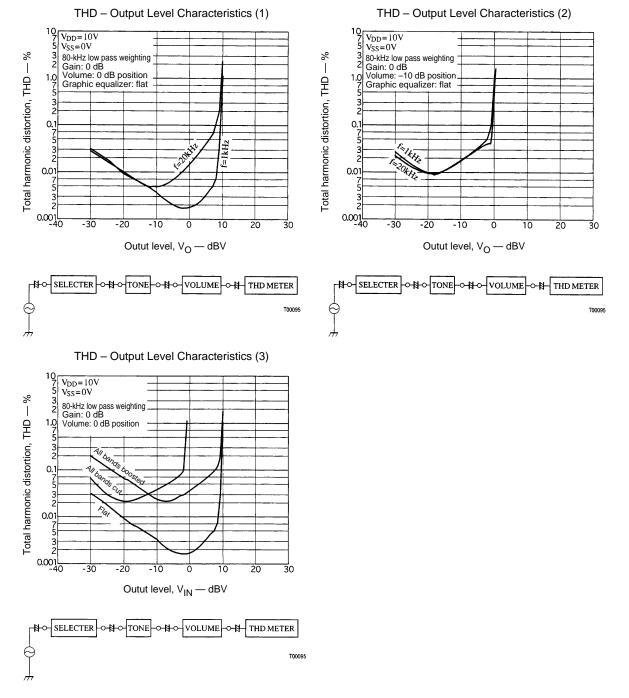

| Total harmonic distortion     | THD                | V <sub>IN</sub> = 1 Vrms, f = 1 kHz, with all controls flat overall          |     |         | 0.01 | %      |  |

| Crosstalk                     | СТ                 | $V_{IN}$ = 1 Vrms, f = 1 kHz, with all controls flat overall, Rg = 1 k\Omega | 80  |         |      | dB     |  |

| Output noise voltage          | V <sub>N</sub> 1   | With all controls flat overall, BW = 20 to 20kHz                             |     | 2.9     |      | μV     |  |

| Output hoise voltage          | V <sub>N</sub> 2   | GEQ F1 Band = +10dB, With all controls overall, BW = 20 to 20kHz             |     | 17      |      | μV     |  |

| Output at maximum attenuation | V <sub>O</sub> min | $V_{IN} = 1$ Vrms, f = 1 kHz, main volume $-\infty$                          |     | -90     |      | dB     |  |

| Current drain                 | I <sub>DD</sub>    | $V_{DD} - V_{SS} = 10.5 V$                                                   |     | 46.5    | 55.8 | mA     |  |

| Input high level current      | I <sub>IH</sub>    | CL, DI, CE, V <sub>IN</sub> = 10.5 V                                         |     |         | 10   | μA     |  |

| Input low level current       | Ι <sub>ΙL</sub>    | CL, DI, CE, V <sub>IN</sub> = 0 V                                            | -10 |         |      | μA     |  |

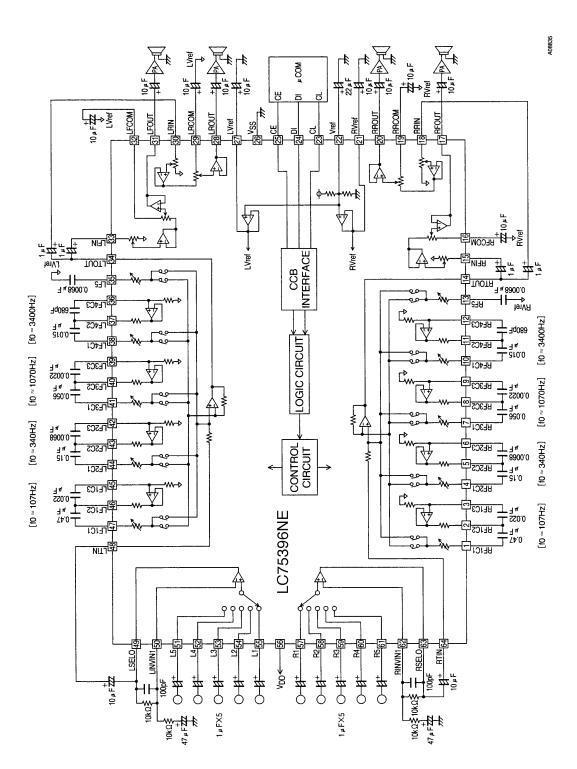

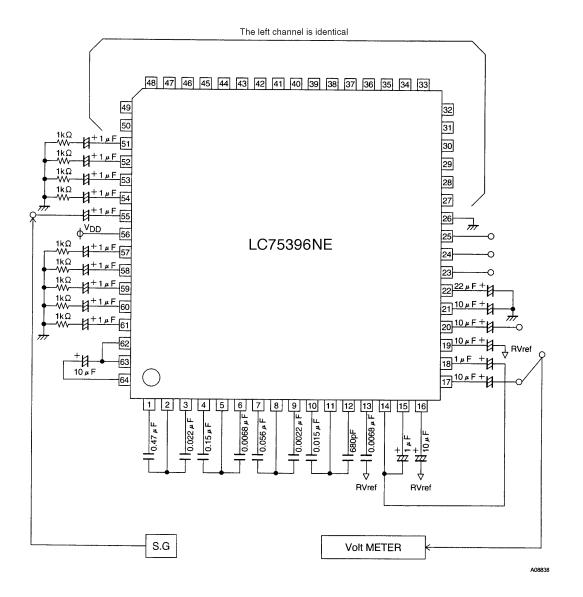

### **Sample Application Circuit**

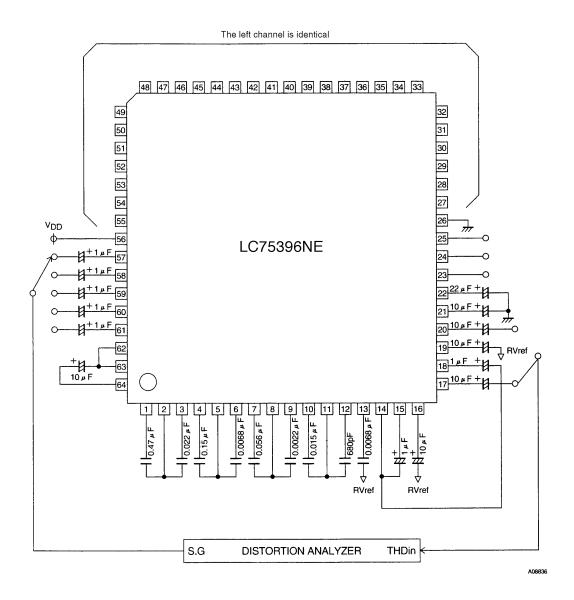

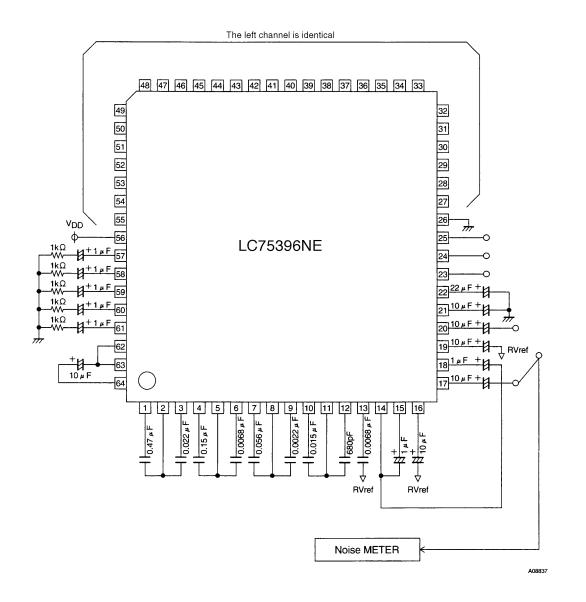

## **Test Circuits**

Total Harmonic Distortion

Output Noise Voltage

### Crosstalk

A08839

### **Pin Functions**

| Pin No.  | Pin            | Function                                                               | Equivalent circuit                      |

|----------|----------------|------------------------------------------------------------------------|-----------------------------------------|

| 55       | L1             |                                                                        |                                         |

| 54       | L2             |                                                                        | ۶۷ <sub>DD</sub>                        |

| 53       | L3             |                                                                        |                                         |

| 52       | L4             |                                                                        |                                         |

| 51       | L5             | Signal inputs                                                          |                                         |

| 57       | R1             | Signal inputs                                                          |                                         |

| 58       | R2             |                                                                        |                                         |

| 59       | R3             |                                                                        | INVIN1 Vref                             |

| 60       | R4             |                                                                        |                                         |

| 61       | R5             |                                                                        |                                         |

|          |                |                                                                        | ץ v <sub>DD</sub>                       |

|          |                |                                                                        |                                         |

| 50       | LINVIN1        | Inverting inputs to the operational amplifier that sets the input      |                                         |

| 62       | RINVIN1        | gain                                                                   |                                         |

|          |                |                                                                        | L                                       |

|          |                |                                                                        | 7777 A08841                             |

|          |                |                                                                        |                                         |

| 49       | LSELO          |                                                                        |                                         |

| 63       | RSELO          | Input selector outputs                                                 |                                         |

|          |                |                                                                        | Vref 777 A08842                         |

|          |                |                                                                        | 6 Vref /// A08842                       |

|          |                |                                                                        | ę V <sub>DD</sub>                       |

| 48       | LTIN           |                                                                        | W <b>*</b>                              |

| 40<br>64 | RTIN           | Equalizer inputs                                                       |                                         |

| 04       | KTIN .         |                                                                        | ···· <b>"</b>                           |

|          |                |                                                                        | A08843                                  |

| 47       | LF1C1          |                                                                        |                                         |

| 46       | LF1C2          | Connections for the capacitors that form the equalizer F1 band filters |                                         |

| 45       | LF1C3          |                                                                        | ⊥vdd                                    |

| 1        | RF1C1          | Capacitors must be connected between:                                  |                                         |

| 2        | RF1C2          | LF1C1 (RF1C1) and LF1C2 (RF1C2), and between                           |                                         |

| 3        | RF1C3          | LF1C2 (RF1C2) and LF1C3 (RF1C3).                                       |                                         |

|          |                |                                                                        | ≰ <u></u> v <sub>DD</sub>               |

| 44       | LF2C1          | Connections for the capacitors that form the equalizer F2              | Vref2                                   |

| 43       | LF2C2          | band filters                                                           | *                                       |

| 42       | LF2C3          | Capacitors must be connected between:                                  | <i>m</i>                                |

| 4        | RF2C1          | LF2C1 (RF2C1) and LF2C2 (RF2C2), and between                           | ŶVDD                                    |

| 5        | RF2C2          | LF2C2 (RF2C2) and LF2C3 (RF2C3).                                       |                                         |

| 6        | RF2C3          |                                                                        |                                         |

| 41       | LF3C1          |                                                                        |                                         |

| 40       | LF3C2          | Connections for the capacitors that form the equalizer F3 band filters | 777                                     |

| 39       | LF3C3          | Capacitors must be connected between:                                  | k ⊥vdd                                  |

| 7        | RF3C1          | LF3C1 (RF3C1) and LF3C2 (RF3C2), and between                           |                                         |

| 8        | RF3C2          |                                                                        | │ ▲                                     |

| 9        | RF3C3          | LF3C2 (RF3C2) and LF3C3 (RF3C3).                                       | <i>m</i>                                |

| 38       | LF4C1          |                                                                        | <sup>Ŷ</sup> <sup>V</sup> DD            |

| 30<br>37 | LF4C1<br>LF4C2 | · Connections for the capacitors that form the equalizer F4            | Uvref2                                  |

|          | LF4C2<br>LF4C3 | band filters                                                           | ▲ · · · · · · · · · · · · · · · · · · · |

| 36<br>10 |                | Capacitors must be connected between:                                  | 777<br>A08844                           |

| 10       | RF4C1          | LF4C1 (RF4C1) and LF4C2 (RF4C2), and between                           |                                         |

| 11       | RF4C2          | LF4C2 (RF4C2) and LF4C3 (RF4C3).                                       |                                         |

| 12       | RF4C3          |                                                                        |                                         |

Continued on next page.

Continued from preceding page.

| Pin No.              | Pin                              | Function                                                                                                                                                                                                                                                                                                       | Equivalent circuit |

|----------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 35<br>13             | LF5<br>RF5                       | Connections for the capacitors that form the equalizer F5<br>band filters<br>Connections for external capacitors                                                                                                                                                                                               |                    |

| 33<br>30<br>15<br>18 | LFIN<br>LRIN<br>RFIN<br>RRIN     | <ul> <li>Input to the left channel front 4-dB step volume control.</li> <li>Input to the left channel rear 4-dB step volume control.</li> <li>Input to the right channel front 4-dB step volume control.</li> <li>Input to the right channel rear 4-dB step volume control.</li> </ul>                         |                    |

| 32<br>29<br>16<br>19 | LFCOM<br>LRCOM<br>RFCOM<br>RRCOM | <ul> <li>Common pin for the left channel front 1-dB step volume control.</li> <li>Common pin for the left channel rear 1-dB step volume control.</li> <li>Common pin for the right channel front 1-dB step volume control.</li> <li>Common pin for the right channel rear 1-dB step volume control.</li> </ul> | A08846             |

| 31<br>28<br>17<br>20 | LFOUT<br>LROUT<br>RFOUT<br>RROUT | Left channel front volume control output     Left channel rear volume control output     Right channel front volume control output     Right channel rear volume control output                                                                                                                                | AD6647             |

| 34<br>14             | LTOUT<br>RTOUT                   | Equalizer outputs                                                                                                                                                                                                                                                                                              |                    |

| 22                   | Vref                             | • A capacitor of a few tens of $\mu$ F must be inserted between Vref and AV <sub>SS</sub> (V <sub>SS</sub> ) to handle power supply ripple in the V <sub>DD</sub> /2 voltage generation circuit.                                                                                                               | Vref ZZZ A08849    |

| 27<br>21             | LVref<br>RVref                   | Internal analog system grounds                                                                                                                                                                                                                                                                                 | Vref ADR850        |

| 56                   | V <sub>DD</sub>                  | Power supply                                                                                                                                                                                                                                                                                                   |                    |

| 26                   | V <sub>SS</sub>                  | • Ground                                                                                                                                                                                                                                                                                                       |                    |

| 25                   | CE                               | • Chip enable<br>When this pin goes from high to low, data is written to an<br>internal latch and the analog switches operate. Data<br>transfers are enabled when this pin is at the high level.                                                                                                               |                    |

| 24<br>23             | DI<br>CL                         | Serial data and clock inputs for chip control.                                                                                                                                                                                                                                                                 | ////<br>A08851     |

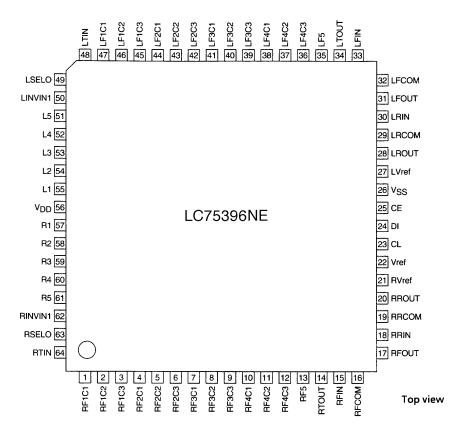

## Equivalent Circuit Diagram

## Selector Control Block

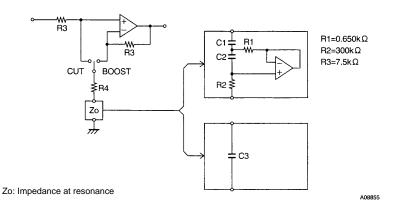

### Equalizer Control Block

A08853

#### **Calculating the Size of External Capacitors**

The LC75396NE supports four bands with peaking characteristics and one band with shelving characteristics

1. Peaking Characteristics (bands F1 to F4)

The external capacitor functions as the structural element of a simulated inductor. The equivalent circuit and the calculations required to achieve the desired center frequency are shown below.

• Equivalent circuit for the simulated inductor

Calculation example

Specifications: Central frequency,  $F_0 = 107 \text{ Hz}$

Q factor at maximum boost,  $Q_{+10 \text{ dB}} = 0.8$

- Calculate Q<sub>0</sub>, the sharpness of the simulated inductance itself.

$Q_0 = (R1 + R4)/R1 \times Q_{+10dB}$

Note: R4 is from the separately issued internal block diagram.

≠ 4.270 — Calculate C1

C1 =  $1/2\pi F_0 R 1 Q_0 \neq 0.536 (\mu F)$ -- Calculate C2

$$C2 = Q_0/2\pi F_0 R2 \neq 0.021 \ (\mu F)$$

```

• Sample results

```

| Central frequency<br>F <sub>O</sub> (Hz) | C1<br>(F) | C2<br>(F)         |

|------------------------------------------|-----------|-------------------|

| 107                                      | 0.536 µ   | 0.021 µ           |

| 340                                      | 0.169 µ   | 6663 <sub>P</sub> |

| 1070                                     | 0.054 µ   | 2117 <sub>P</sub> |

| 3400                                     | 0.017 µ   | 666 <sub>P</sub>  |

2. Shelving characteristics (Band F5)

Achieving the desired control of 2-dB steps over the range between +10 dB to -10 dB requires choosing a capacitor, C3, with an impedance of 650  $\Omega$ .

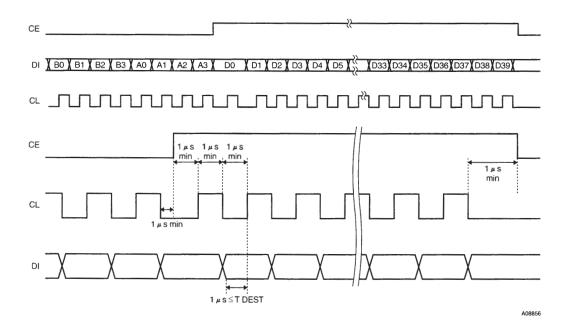

### **Control System Timing and Data Formats**

To control the LC75396NE, specified sequences are required to be input through the pins CE, CL, and DI. Each sequence consists of 48 bits: an 8-bit address followed by 40 bits of data.

### 1. Address Code (B0 to A3)

This product uses an 8-bit address code, and supports the same specifications as other Sanyo CCB serial bus products.

| Address code (LSB) | B0 | B1 | B2 | <b>B</b> 3 | A0 | A1 | A2 | A3 |         |

|--------------------|----|----|----|------------|----|----|----|----|---------|

|                    | 0  | 1  | 0  | 0          | 0  | 0  | 0  | 1  | (82HEX) |

### 2. Control Code Allocations

Input switching control

| D0 | D1 | D2 | Operation |     |  |  |

|----|----|----|-----------|-----|--|--|

| 0  | 0  | 0  | L1 (R1)   | ON  |  |  |

| 1  | 0  | 0  | L2 (R2)   | ON  |  |  |

| 0  | 1  | 0  | L3 (R3)   | ON  |  |  |

| 1  | 1  | 0  | L4 (R4)   | ON  |  |  |

| 0  | 0  | 1  |           | OFF |  |  |

| 1  | 0  | 1  |           | OFF |  |  |

| 0  | 1  | 1  |           | OFF |  |  |

| 1  | 1  | 1  | OFF       |     |  |  |

Input switching control

| D3 |         | Operation |  |

|----|---------|-----------|--|

| 0  | L5 (R5) | OFF       |  |

| 1  | L5 (R5) | ON        |  |

Five band equalizer control

| D4  | D5  | D6  | D7  | Band f1 |

|-----|-----|-----|-----|---------|

| D8  | D9  | D10 | D11 | Band f2 |

| D12 | D13 | D14 | D15 | Band f3 |

| D16 | D17 | D18 | D19 | Band f4 |

| D20 | D21 | D22 | D23 | Band f5 |

| 1   | 0   | 1   | 0   | +10dB   |

| 0   | 0   | 1   | 0   | +8dB    |

| 1   | 1   | 0   | 0   | +6dB    |

| 0   | 1   | 0   | 0   | +4dB    |

| 1   | 0   | 0   | 0   | +2dB    |

| 0   | 0   | 0   | 0   | 0dB     |

| 1   | 0   | 0   | 1   | -2dB    |

| 0   | 1   | 0   | 1   | -4dB    |

| 1   | 1   | 0   | 1   | -6dB    |

| 0   | 0   | 1   | 1   | -8dB    |

| 1   | 0   | 1   | 1   | -10dB   |

|  | 0 | 0 | 1 | 0 | 0 | 0 | -16dB |

|--|---|---|---|---|---|---|-------|

|  | 1 | 0 | 1 | 0 | 0 | 0 | -20dB |

|  | 0 | 1 | 1 | 0 | 0 | 0 | -24dB |

|  | 1 | 1 | 1 | 0 | 0 | 0 | -28dB |

|  | 0 | 0 | 0 | 1 | 0 | 0 | -32dB |

|  | 1 | 0 | 0 | 1 | 0 | 0 | -36dB |

|  | 0 | 1 | 0 | 1 | 0 | 0 | -40dB |

|  | 1 | 1 | 0 | 1 | 0 | 0 | -44dB |

|  | 0 | 0 | 1 | 1 | 0 | 0 | -48dB |

|  | 1 | 0 | 1 | 1 | 0 | 0 | -52dB |

|  | 0 | 1 | 1 | 1 | 0 | 0 | -56dB |

|  | 1 | 1 | 1 | 1 | 0 | 0 | -60dB |

-64dB

-68dB -72dB

-76dB

### LC75396NE

D26

D24

D25

D27

D28

D30

D31

Operation

1dB STEP

0dB

-1dB

-2dB

-3dB 4dB STEP

0dB -4dB

-8dB

-12dB

D29

|                                               | _          |           |                   |     |            |                                                                                  |                                   |   |       |  |

|-----------------------------------------------|------------|-----------|-------------------|-----|------------|----------------------------------------------------------------------------------|-----------------------------------|---|-------|--|

|                                               |            |           |                   |     |            |                                                                                  |                                   |   | MUTE  |  |

|                                               |            |           | 1                 | 1   | 1          | 1                                                                                | 1                                 | 0 | -∞    |  |

| Channel selection control                     |            |           |                   |     |            |                                                                                  |                                   |   |       |  |

|                                               | D32        | D33       | D33 Operation     |     |            |                                                                                  |                                   |   |       |  |

|                                               | 0          | 0         | ) Initial setting |     |            |                                                                                  |                                   |   |       |  |

|                                               | 1          | 0         | RCH               |     |            |                                                                                  |                                   |   |       |  |

|                                               | 0          | 1         | LCH               |     |            |                                                                                  |                                   |   |       |  |

|                                               | 1          | 1         | Simulata          | t   |            |                                                                                  |                                   |   |       |  |

| Left channel volume rear/front                |            |           |                   |     |            |                                                                                  |                                   |   |       |  |

| control                                       | D34        |           | Operation         |     |            |                                                                                  | Control is enabled when $D33 = 1$ |   |       |  |

|                                               | 0          | Rear      | Rear              |     |            |                                                                                  |                                   |   |       |  |

|                                               | 1          | Front     |                   |     |            |                                                                                  |                                   |   |       |  |

| Pight shannal volume rear/front               |            |           |                   |     |            |                                                                                  |                                   |   |       |  |

| Right channel volume rear/front control       | D35        | Operation |                   |     |            | C                                                                                | Control is enabled when $D32 = 1$ |   |       |  |

|                                               | 0          | Rear      | Rear              |     |            |                                                                                  |                                   |   |       |  |

|                                               | 1          | Front     |                   |     |            |                                                                                  |                                   |   |       |  |

| Test mode control                             | <b></b>    | ·····     |                   |     |            |                                                                                  |                                   |   |       |  |

|                                               | D36        | D37       | D38               | D39 |            |                                                                                  | Operation                         |   |       |  |

|                                               | 0          | 0         | 0                 | 0   | These bits | These bits are for chip testing and must all be set to 0 in application systems. |                                   |   |       |  |

| es: After power is first applied, application | ons must i | 1         |                   |     |            |                                                                                  |                                   |   | ····· |  |

Initial data ... (1) Address 01000001

Data: (Set the volume to -----set both D34 and D35 to 1, and set all other data to 0) (2) Address 01000001

Data: (Set the volume to  $-\infty$ , set both D34 and D35 to 0, and set all other data to 0) After transferring that data, set the left and right channel initial settings before turning off the mute function.

Volume control

#### LC75396NE

### Usage Notes

- When the power is first applied, the internal analog switches are in indeterminate states. The chip therefore requires muting or other external measures until it has received the proper data.

- After power is first applied, applications must initialize this chip by sending the initial data (1) and (2) described below. Initial data ... (1) Address 01000001

- Data: (Set the volume to  $-\infty$ , set both D34 and D35 to 0, and set all other data to 0) (2) Address 01000001

Data: (Set the volume to  $-\infty$ , set both D34 and D35 to 1, and set all other data to 0)

After transferring that data, set the left and right channel initial settings before turning off the mute function.

• Provide grounding patterns or shielding for the lines to the CL, DI, and CE pins so as to prevent their high-frequency digital signals from interfering with the operation of nearby analog circuits.

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- Intersection of the second second

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of May, 1998. Specifications and information herein are subject to change without notice.