New Product

DG2301 Vishay Siliconix

# High-Speed, Low r<sub>ON</sub>, SPST Analog Switch (1-Bit Bus Switch)

### **FEATURES**

- SC-70 5-Lead Package

- 5- $\Omega$  Switch Connection Between Two Ports

- Minimal Propagation Delay Through The Switch

- Low I<sub>CC</sub>

- Zero Bounce In Flow-Through Mode

- Control Inputs Compatible with TTL Level

### DESCRIPTION

The DG2301 is a high-speed, 1-bit, low power, TTL-compatible bus switch. Using sub-micron CMOS technology, DG2301 achieves low on-resistance and negligible propagation delay.

The DG2301 consist of a bi-directional input/output pins A and

B. When the output enable  $(\overline{OE})$  is low, the input/output pins are connected. When the  $\overline{OE}$  is high, the switch is open and a high-impedance state exists between input/output pins A and B.

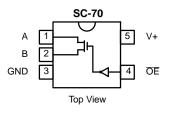

### FUNCTIONAL BLOCK DIAGRAM AND PIN CONFIGURATION

Device Marking: E4

| TRUTH TABLE |           |            |  |

|-------------|-----------|------------|--|

| OE          | В         | Function   |  |

| L           | A         | Connect    |  |

| Н           | HiZ State | Disconnect |  |

| ORDERING INFORMATION |         |             |  |

|----------------------|---------|-------------|--|

| Temp Range           | Package | Part Number |  |

| -40 to 85°C          | SC70-5  | DG2301DL    |  |

## DG2301

## **Vishay Siliconix**

## **New Product**

### ABSOLUTE MAXIMUM RATINGS

### Reference to GND

| V+                                | -0.3 to +6 V           |

|-----------------------------------|------------------------|

| OE, A, B <sup>a</sup> 0.3 to      | (V+ + 0.3 V)           |

| Continuous Current (Any terminal) | $\pm 50 \text{ mA}$    |

| Peak Current                      | . $\pm 200 \text{ mA}$ |

| (Pulsed at 1 ms, 10% duty cycle)  |                        |

| Storage Temperature (D Suffix)    | 65 to 150°C            |

Power Dissipation (Packages)<sup>b</sup>

Notes:

- Signals on A, or B or OE exceeding V+ will be clamped by internal a.

- diodes. Limit forward diode current to maximum current ratings. b. All leads welded or soldered to PC Board.

- Derate 3.1 mW/°C above 70°C

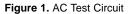

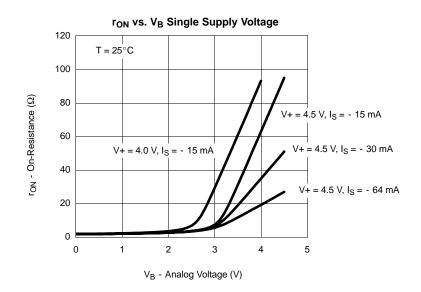

### SPECIFICATIONS (V+ = 5.0 V) **Test Conditions** Limits **Otherwise Unless Specified** -40 to 85°C V+ = 4.0 V to 5.5 V, $V_{OE}$ = 0.8 or 2.0 V<sup>e</sup> Min<sup>b</sup> Typc Max<sup>b</sup> Unit Parameter Symbol Tempa **DC** Characteristics V+ = 4.5 V, V<sub>A</sub> = 0 V, I<sub>B</sub> = 64 mA Full 7 V+ = 4.5 V, $V_A$ = 0 V, $I_B$ = 30 mA Full 7 Ω On-Resistance **I**ON V+ = 4.5 V, $V_A$ = 2.4 V, $I_B$ = 15 mA Full 15 V+ = 4.0 V, V<sub>A</sub> = 2.4 V, I<sub>B</sub> = 15 mA Full 20 V+ = 5.5 V, $V_A$ = 1 V/4.5 V, $V_B$ = 4.5 V/1 V Switch Off Leakage Current Full -10 10 I<sub>(off)</sub> μA 10 V+ = 5.5 V, $V_A = V_B = 1 V/4.5 V$ -10 Switchl-On Leakage Current I<sub>(on)</sub> Full 2.0 Full Input High Voltage VIH v Input Low Voltage VIL Full 0.8 Input Current IIL or IIH $V_{OE} = 0 \text{ or } V+$ Full -1 1 μΑ **Dynamic Characteristics** Full 1 t<sub>PHL</sub> Prop Delay Bus-to-Bus<sup>f</sup> V<sub>LD</sub> = Open (Figure 1 and 2) Full 1 t<sub>PLH</sub> V<sub>LD</sub> = 7 V, V+ = 4.5 V to 5.5 V (Figure 1 and 2) Full 3.9 t<sub>PZL</sub> $V_{LD} = 7 V, V_{+} = 4.0 V$ (Figure 1 and 2) Full 4.5 Output Enable Timed $V_{LD}$ = Open, V+ = 4.5 V to 5.5 V (Figure 1 and 2) 3.7 Full t<sub>PZH</sub> ns $V_{LD}$ = Open, V+ = 4.0 V (Figure 1 and 2) Full 4.5 V<sub>LD</sub> = 7 V, V+ = 4.5 V to 5.5 V (Figure 1 and 2) Full 40 t<sub>PLZ</sub> $V_{LD} = 7 V, V_{+} = 4.0 V$ (Figure 1 and 2) 4.2 Full Output Disable Timed $V_{ID}$ = Open, V+ = 4.5 V to 5.5 V (Figure 1 and 2) Full 1.0 t<sub>PHZ</sub> $V_{LD}$ = Open, V+ = 4.0 V (Figure 1 and 2) Full 1.0 Cin 3.5 Input Capacitance Room C<sub>(off)</sub> Channel-Off Capacitanced Room 5 pF $V_{OE} = 0$ or V+, f = 1 MHz Channel-On Capacitanced Room 11 CON **Power Supply** Power Supply Range V+ 4.0 5.5 V Power Supply Current $V_{OE} = 0 \text{ or } V+$ 0.01 1+ 1.0 μΑ

Notes:

Room = 25°C, Full = as determined by the operating suffix. a.

The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

Typical values are for design aid only, not guaranteed nor subject to production testing.

d. Guarantee by design, nor subjected to production test.

$V_{IN}$  = input voltage to perform proper function.

Guaranteed by design and not production tested. The bus switch propagation delay is a function of the RC time constant contributed by the on-resistance and f. the specified load capacitance with an ideal voltage source (zero output impedance) driving the switch.

www.vishay.com 2

## **New Product**

# DG2301

# Vishay Siliconix

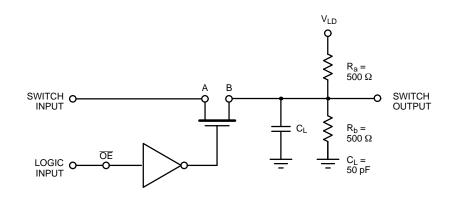

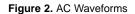

### AC LOADING AND WAVEFORMS

Input driven by 50- $\Omega$  source terminated in 50  $\Omega$ C<sub>L</sub> includes load and stray capacitance Input PRR = 1.0 MHz, t<sub>W</sub> = 50 ns

## DG2301

# **Vishay Siliconix**

## **New Product**

## TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.