# M5232P: Multiple RS-232 Drivers and Receivers

#### 1. Features

- Drivers

- Current Limited Output ... 10mA Typical

- Power-off Output impedance ... 300ohm Min.

- Slew rate control by load capacitor

- Flexible Supply Voltage Range

- Input compatible with most TTL and DTL circuits

#### Receivers

- Input resistance ..... 3kohm to 7kohm

- Input signal range .... ± 30V

- Built-in Input Hysteresis

### 2. Description

The ALi's M5232P combines three drivers and five receivers from ASP trade standard AP232 bipolar quadruple drivers and receivers, respectively. The pinout matches the flow through design of the AP232 to decrease the part count, reduce the board space required, and allow easy interconnection of the UART and serial-port connector of IBM PC/AT and compatibles. The bipolar circuits and processing of the M5232P provides a rugged low-cost solution for this function at the expense of quiescent power and external passive components relative to the AP232.

The M5232P complies with the requirements of the EIA/TIA 232-D and ITU (formally CCITT) v.28 standards. These standards are for data interchange between a host computer and peripheral at signalling rates up to 20k bits/sec. The switching speeds of the M5232P are fast enough to support rates up to 120 kbps with lower capacitive loads (shorter cables). Interoperability at the higher signalling rates cannot be assured unless the designer has design control of the cable and the interface circuits at both ends. For compatibility with signalling rates to 120 kbps, use of EIA/ITA-423-B (ITU v.10) and EIA/ITA-422-B (ITU v.11) standards are recommended.

The M5232P is operable at the temperature range of 0°C to 75°C.

06-28-1997, Document Number: 5232DS02.doc

Downloaded from Elcodis.com electronic components distributor

Acer Labs: 7F, 115 Tung Hsing Street, Taipei 110, Taiwan, R.O.C. Tel: 886-(02) 762-8800 Fax: 762-6060

M5232P: RS-232 Chip

# 3. Pin Diagram

| VDD □1             | 20 □Vcc       |

|--------------------|---------------|

| RA1 □2             | 19            |

| RA2□3              | 18 □RY2       |

| RA3□4              | 17 PRY3       |

| DY1 □5             | 16            |

| DY2 <sup>□</sup> 6 | 15 PDA2       |

| RA4 <sup>□</sup> 7 | 14            |

| DY3⊟8              | 13 ⊟DA3       |

| RA5⊟ <sup>9</sup>  | <sup>12</sup> |

| Vss □10            | 11 □GND       |

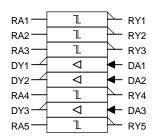

# 5. Functional Block Diagram

## 4. Pin Description Table

| Pin Name | Description      |

|----------|------------------|

| RAx      | Receiver inputs  |

| RYx      | Receiver outputs |

| DAx      | Driver inputs    |

| DYx      | Driver outputs   |

|          | ·                |

|          |                  |

|          |                  |

|          |                  |

|          |                  |

|          |                  |

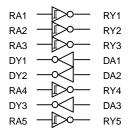

## 6. Logic Diagram